# **DP80390**

# Pipelined High Performance 8-bit Microcontroller ver 4.02

# OVERVIEW

DP80390 is an ultra high performance, speed optimized soft core of a single-chip 8-bit embedded controller dedicated for operation with fast (typically on-chip) and slow (off-chip) memories. It supports up to 8 MB of linear code and 16 MB of linear data spaces. The core has been designed with a special concern about performance to power consumption ratio. This ratio is extended by an advanced power management unit PMU.

DP80390 soft core is 100% binary-compatible with the industry standard 80390 & 8051 8-bit microcontrollers. There are two configurations of DP80390: Harward where internal data and program buses are separated, and von Neumann with common program and external data bus. DP80390 has Pipelined RISC architecture 10 times faster compared to standard architecture and executes 85-200 million instructions per second. This performance can also be exploited to great advantage in low power applications where the core can be clocked over ten times more slowly than the original implementation for no performance penalty.

DP80390 is delivered with **fully automated testbench** and **complete set of tests** allowing easy package validation at each stage of SoC design flow.

# **CPU FEATURES**

- 100% software compatible with industry standard 80390 & 8051

- LARGE mode 8051 instruction set

- FLAT mode 80390 instruction set

- Pipelined RISC architecture enables to execute instructions 10 times faster compared to standard 8051

- 24 times faster multiplication

- 12 times faster addition

- Up to 256 bytes of internal (on-chip) Data Memory

- Up to 8M bytes of linear Program Memory

64 kB of internal (on-chip) Program Memory

8 MB external (off-chip) Program Memory

- Up to 16M bytes of external (off-chip) Data Memory

- User programmable Program Memory Wait States solution for wide range of memories speed

- User programmable External Data Memory Wait States solution for wide range of memories speed

- De-multiplexed Address/Data bus to allow easy connection to memory

- Dedicated signal for Program Memory writes.

http://www.DigitalCoreDesign.com http://www.dcd.pl

All trademarks mentioned in this document are trademarks of their respective owners.

- Interface for additional Special Function Registers

- Fully synthesizable, static synchronous design with positive edge clocking and no internal tri-states

- Scan test ready

- 2.0 GHz virtual clock frequency in a 0.25u technological process

### PERIPHERALS

- DoCD™ debug unit

- Processor execution control Run

Halt

Step into instruction

Skip instruction

Read-write all processor contents

Program Counter (PC)

Program Memory

Internal (direct) Data Memory

Special Function Registers (SFRs)

External Data Memory

- Code execution breakpoints one real-time PC breakpoint unlimited number of real-time OPCODE breakpoints

- Hardware execution watch-point one at Internal (direct) Data Memory one at Special Function Registers (SFRs) one at External Data Memory

- Hardware watch-points activated at a certain address by any write into memory address by any read from memory address by write into memory a required data address by read from memory a required data

- Unlimited number of software watch-points Internal (direct) Data Memory Special Function Registers (SFRs) External Data Memory

- Unlimited number of software breakpoints Program Memory(PC)

- Automatic adjustment of debug data transfer speed rate between HAD and Silicon

- JTAG Communication interface

- Power Management Unit

- Power management mode

- Switchback feature

- Stop mode

- Interrupt Controller

- 2 priority levels

- 2 external interrupt sources

- o 3 interrupt sources from peripherals

- Four 8-bit I/O Ports

- o Bit addressable data direction for each line

- Read/write of single line and 8-bit group

- Two 16-bit timer/counters

- Timers clocked by internal source

- Auto reload 8-bit timers

All trademarks mentioned in this document are trademarks of their respective owners.

- Externally gated event counters

- Full-duplex serial port

- Synchronous mode, fixed baud rate

- o 8-bit asynchronous mode, fixed baud rate

- o 9-bit asynchronous mode, fixed baud rate

- o 9-bit asynchronous mode, variable baud rate

# CONFIGURATION

The following parameters of the DP80390 core can be easy adjusted to requirements of dedicated application and technology. Configuration of the core can be prepared by effortless changing appropriate constants in package file. There is no need to change any parts of the code.

Internal Program Memory - synchronous type - asynchronous

Internal Program ROM - 0 - 64kB

Internal Program RAM

Memory size

- 0 - 64kB

Internal Program Memory - true fixed size - false

• Interrupts - subroutines location

Power Management Mode

used

unused

Stop mode- used- unused

DoCD™ debug unit

used

unused

Besides mentioned above parameters all available peripherals and external interrupts can be excluded from the core by changing appropriate constants in package file.

## **DELIVERABLES**

- Source code:

- ♦ VHDL Source Code or/and

- ♦ VERILOG Source Code or/and

- ♦ Encrypted, or plain text EDIF netlist

- VHDL & VERILOG test bench environment

- ♦ Active-HDL automatic simulation macros

- ♦ ModelSim automatic simulation macros

- Tests with reference responses

- Technical documentation

- ♦ Installation notes

- ♦ HDL core specification

- ♦ Datasheet

- Synthesis scripts

- Example application

- Technical support

- ♦ IP Core implementation support

- 3 months maintenance

- Delivery the IP Core updates, minor and major versions changes

- Delivery the documentation updates

- Phone & email support

# LICENSING

Comprehensible and clearly defined licensing methods without royalty fees make using of IP Core easy and simply.

<u>Single Design</u> license allows using IP Core in single FPGA bitstream and ASIC implementation. It also permits FPGA prototyping before ASIC production.

<u>Unlimited Designs</u> license allows using IP Core in unlimited number of FPGA bitstreams and ASIC implementations.

In all cases number of IP Core instantiations within a design, and number of manufactured chips are unlimited. There is no time of use limitations.

- Single Design license for

- VHDL, Verilog source code called <u>HDL Sour-ce</u>

- Encrypted, or plain text EDIF called Netlist

- Unlimited Designs license for

- HDL Source

- Netlist

- Upgrade from

- Netlist to HDL Source

- o Single Design to Unlimited Designs

# **DESIGN FEATURES**

#### PROGRAM MEMORY:

The DP80390 soft core is dedicated for operation with Internal and External Program Memory. It maximal linear size is equal to 8 MB. Internal Program Memory can be implemented as:

- ROM located in address range between 0000h ÷ (ROM<sub>size</sub>-1)

- RAM located in address range between (64kB-RAM<sub>size</sub>) ÷ FFFFh

External Program Memory can be implemented as ROM or RAM located in address range between  $ROM_{size} \div 8$  MB excluding area occupied by  $RAM_{size}$ .

#### ♦ INTERNAL DATA MEMORY:

The DP80390 can address Internal Data Memory of up to 256 bytes The Internal Data Memory can be implemented as Single-Port synchronous RAM.

#### ♦ EXTERNAL DATA MEMORY:

The DP80390 soft core can address up to 16 MB of External Data Memory. Extra DPX (*Data Pointer eXtended*) register is used for segments swapping.

#### USER SPECIAL FUNCTION REGISTERS:

Up to 104 External (user) Special Function Registers (ESFRs) may be added to the DP80390 design. ESFRs are memory mapped into Direct Memory between addresses 0x80 and 0xFF in the same manner as core SFRs and may occupy any address that is not occupied by a core SFR.

#### WAIT STATES SUPPORT:

The DP80390 soft core is dedicated for operation with wide range of Program and Data memories. Slow Program and External Data memory may assert a memory Wait signal to hold up CPU activity.

All trademarks mentioned in this document are trademarks of their respective owners.

| PIN            | TYPE   | DESCRIPTION                           |

|----------------|--------|---------------------------------------|

| ready          | input  | External memory data ready            |

| ramdatai[7:0]  | input  | Data bus from internal data memory    |

| sfrdatai[7:0]  | input  | Data bus from user SFR's              |

| int0           | input  | External interrupt 0                  |

| int1           | input  | External interrupt 1                  |

| t0             | input  | Timer 0 input                         |

| t1             | input  | Timer 1 input                         |

| gate0          | input  | Timer 0 gate input                    |

| gate1          | input  | Timer 1 gate input                    |

| rxdi           | input  | Serial receiver input                 |

| tdi            | input  | DoCD™ TAP data input                  |

| tck            | input  | DoCD™ TAP clock input                 |

| tms            | input  | DoCD™ TAP mode select input           |

| rsto           | output | Reset output                          |

| port0o[7:0]    | output | Port 0 output                         |

| port1o[7:0]    | output | Port 1 output                         |

| port2o[7:0]    | output | Port 2 output                         |

| port3o[7:0]    | output | Port 3 output                         |

| prgaddr[15:0]  | output | Internal program memory address bus   |

| prgdatao[7:0]  | output | Data bus for internal program memory  |

| prgramwr       | output | Internal program memory write         |

| sxdmaddr[15:0] | output | Sync XDATA memory address bus (SXDM)  |

| sxdmdatao[7:0] | output | Data bus for Sync XDATA memory (SXDM) |

| sxdmoe         | output | Sync XDATA memory read (SXDM)         |

| sxdmwe         | output | Sync XDATA memory write (SXDM)        |

| xaddr[23:0]    | output | Address bus for external memories     |

| xdatao[7:0]    | output | Data bus for external memories        |

| xdataz         | output | Turn xdata bus into 'Z' state         |

| xprgrd         | output | External program memory read          |

| xprgwr         | output | External program memory write         |

| xdatard        | output | External data memory read             |

| xdatawr        | output | External data memory write            |

| ramaddr[7:0]   | output | Internal Data Memory address bus      |

| ramdatao[7:0]  | output | Data bus for internal data memory     |

| ramoe          | output | Internal data memory output enable    |

| ramwe          | output | Internal data memory write enable     |

| sfraddr[6:0]   | output | Address bus for user SFR's            |

| sfrdatao[7:0]  | output | Data bus for user SFR's               |

| sfroe          | output | User SFR's read enable                |

| sfrwe          | output | User SFR's write enable               |

| tdo            | output | DoCD™ TAP data output                 |

| rtck           | output | DoCD™ return clock line               |

| debugacs       | output | DoCD™ accessing data                  |

| coderun        | output | CPU is executing an instruction       |

| pmm            | output | Power management mode indicator       |

| stop           | output | Stop mode indicator                   |

| rxdo           | output | Serial receiver output                |

| txd            | output | Serial transmitter output             |

All trademarks mentioned in this document are trademarks of their respective owners.

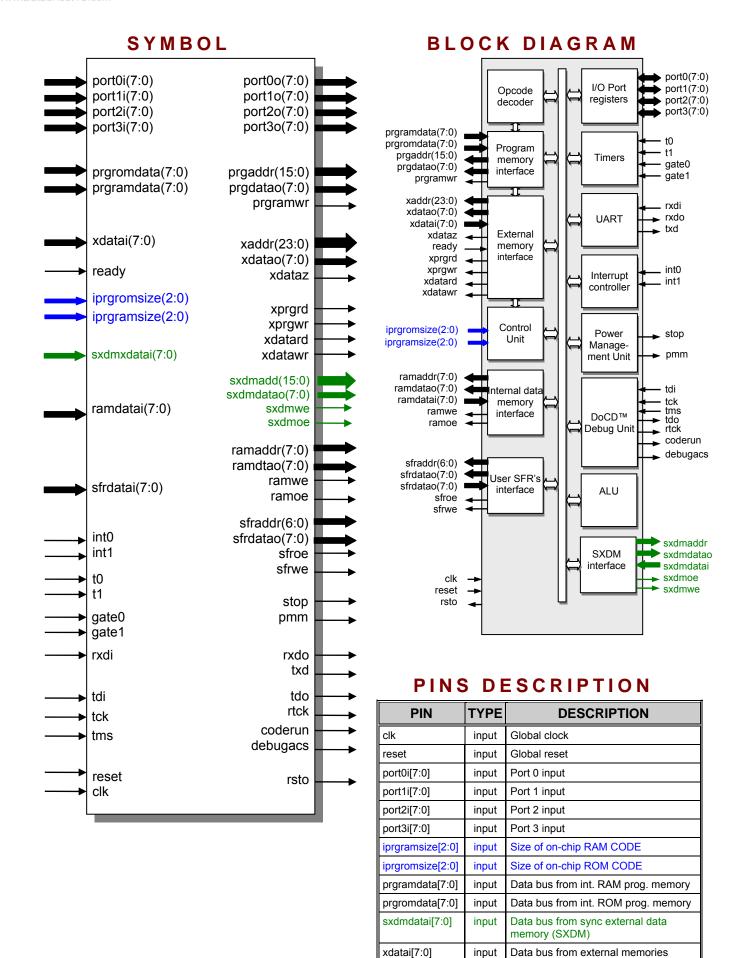

# UNITS SUMMARY

**ALU** – Arithmetic Logic Unit performs the arithmetic and logic operations during execution of an instruction. It contains accumulator (ACC), Program Status Word (PSW), (B) registers and related logic such as arithmetic unit, logic unit, multiplier and divider.

**Opcode Decoder** – Performs an instruction opcode decoding and the control functions for all other blocks.

**Control Unit** – Performs the core synchronization and data flow control. This module is directly connected to Opcode Decoder and manages execution of all microcontroller tasks.

**Program Memory Interface** – Contains Program Counter (PC) and related logic. It performs the instructions code fetching. Program Memory can be also written. This feature allows usage of a small boot loader loading new program into RAM, EPROM or FLASH EEPROM storage via UART, SPI, I2C or DoCD™ module.

**External Memory Interface** - Contains memory access related registers such as Data Page High (DPH), Data Page Low (DPL) and Data Pointer eXtended (DPX) registers. It performs the external Program and Data Memory addressing and data transfers. Program fetch cycle length can be programmed by user. This feature is called Program Memory Wait States, and allows core to work with different speed program memories.

Synchronous eXternal Data Memory (SXDM) Interface – contains XDATA memory access related logic allowing fast access to synchronous memory devices. It performs the external Data Memory addressing and data transfers. This memory can be used to store large variables frequently accessed by CPU, improving overall performance of application.

Internal Data Memory Interface – Internal Data Memory interface controls access into the internal 256 bytes memory. It contains 8-bit Stack Pointer (SP) register and related logic.

**User SFRs Interface** – Special Function Registers interface controls access to the special registers. It contains standard and used defined registers and related logic. User defined external devices can be quickly accessed (read, written, modified) using all direct addressing mode instructions.

Interrupt Controller – Interrupt control module is responsible for the interrupt manage system for the external and internal interrupt sources. It contains interrupt related registers such as Interrupt Enable (IE), Interrupt Priority (IP) and (TCON) registers.

Timers – System timers module. Contains two 16 bits configurable timers: Timer 0 (TH0, TL0), Timer 1 (TH1, TL1) and Timers Mode (TMOD) registers. In the timer mode, timer registers are incremented every 12 CLK periods when appropriate timer is enabled. In the counter mode the timer registers are incremented every falling transition on their corresponding input pins (T0, T1), if gates are opened (GATE0, GATE1). T0, T1 input pins are sampled every CLK period. It can be used as clock source for UARTs.

UARTO – Universal Asynchronous Receiver & Transmitter module is full duplex, meaning it can transmit and receive concurrently. Includes Serial Configuration register (SCON), serial receiver and transmitter buffer (SBUF) registers. Its receiver is double-buffered, meaning it can commence reception of a second byte before a previously received byte has been read from the receive register. Writing to SBUFO loads the transmit register, and reading SBUFO reads a physically separate receive register. Works in 3 asynchronous and 1 synchronous modes. UARTO can be synchronized by Timer 1.

**Ports** - Block contains 8051's general purpose I/O ports. Each of port's pin can be read/write as a single bit or as a 8-bit bus P0, P1, P2, P3.

Power Management Unit – Block contains advanced power saving mechanisms with switchback feature, allowing external clock control logic to stop clocking (Stop mode) or run core in lower clock frequency (Power Management Mode) to significantly reduce power consumption. Switchback feature allows UARTs, and interrupts to be processed in full speed mode if enabled. It is very desired when microcontroller is planned to use in portable and power critical applications.

**DoCD™ Debug Unit** — it's a real-time hardware debugger provides debugging capability of a whole SoC system. In contrast to other onchip debuggers DoCD™ provides non-intrusive debugging of running application. It can halt, run, step into or skip an instruction, read/write any contents of microcontroller including all

All trademarks mentioned in this document are trademarks of their respective owners.

registers, internal, external, program memories, all SFRs including user defined peripherals. Hardware breakpoints can be set and controlled on program memory, internal and external data memories, as well as on SFRs. Hardware breakpoint is executed if any write/read occurred at particular address with certain data pattern or without pattern. Two additional pins CODERUN. DEBUGACS indicate the sate of the debugger and CPU. CODERUN is active when CPU is executing an instruction. DE-BUGACS pin is active when any access is performed by DoCD™ debugger. The DoCD™ system includes JTAG interface and complete set of tools to communicate and work with core in real time debugging. It is built as scalable unit and some features can be turned off to save silicon and reduce power consumption. A special care on power consumption has been taken, and when debugger is not used it is automatically switched in power save mode. Finally whole debugger is turned off when debug option is no longer used.

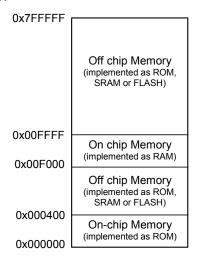

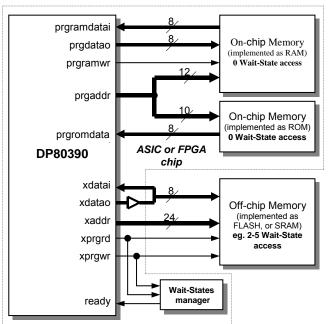

# PROGRAM CODE SPACE IMPLEMENTATION

The figure below shows an example Program Memory space implementation in systems with DP80390 Microcontroller core. The On-chip Program Memory located in address space between 0kB and 1kB is typically used for BOOT code with system initialization functions. This part of the code is typically implemented as ROM. The On-chip Program Memory located in address space between 60kB and 64kB is typically used for timing critical part of the code e.g. interrupt subroutines, arithmetic functions etc. This part of the code is typically implemented as RAM and can be loaded by the BOOT code during initialization phase from off-chip memory or through RS232 interface from external device. From the two mentioned above spaces program code is executed without wait-states and can achieve a top performance up to 200 million instructions per second (many instructions executed in one clock cycle). The off-chip Program Memory located in address space between 1kB and 60kB, and above 64 kB is typically used for main code and constants. This part of the code is usually implemented as ROM, SRAM or FLASH device. Because of relatively long access time the program code executed from mentioned above devices must be fetched with additional Wait-States. Number of

required Wait-States depends on memory access time and DP80390 clock frequency. In most cases the proper number of Wait-States cycles is between 2-5. The READY pin can be also dynamically modulated e.g. by SDRAM controller.

The figure below shows a typical Program Memories connections in system with DP80390 Microcontroller core.

The described above implementation should be treated as an example. All Program Memory spaces are fully configurable. For timing-critical applications whole program code can be implemented as on-chip ROM and (or) RAM and executed without Wait-States, but for some other applications whole program code can be implemented as off-chip ROM or FLASH and executed with required number Wait-State cycles.

All trademarks mentioned in this document are trademarks of their respective owners.

## PERFORMANCE

The following tables give a survey about the Core area and performance in Programmable Logic Devices after Place & Route (CPU features and peripherals have been included):

| Device     | Speed grade | F <sub>max</sub> |

|------------|-------------|------------------|

| FLEX10KE   | -1          | 57 MHz           |

| ACEX1K     | -1          | 57 MHz           |

| APEX20K    | -1          | 50 MHz           |

| APEX20KE   | -1          | 66 MHz           |

| APEX20KC   | -7          | 78 MHz           |

| APEX-II    | -7          | 76 MHz           |

| MERCURY    | -5          | 100 MHz          |

| CYCLONE    | -6          | 91 MHz           |

| CYCLONE-II | -6          | 93 MHz           |

| STRATIX    | -5          | 90 MHz           |

| STRATIX-II | -3          | 160 MHz          |

Core performance in ALTERA® devices

For a user the most important is application speed improvement. The most commonly used arithmetic functions and theirs improvement are shown in table below. Improvement was computed as {80C51 clock periods} divided by {DP80390 clock periods} required to execute an identical function. More details are available in core documentation.

| Function                                | Improvement |

|-----------------------------------------|-------------|

| 8-bit addition (immediate data)         | 9,00        |

| 8-bit addition (direct addressing)      | 9,00        |

| 8-bit addition (indirect addressing)    | 9,00        |

| 8-bit addition (register addressing)    | 12,00       |

| 8-bit subtraction (immediate data)      | 9,00        |

| 8-bit subtraction (direct addressing)   | 9,00        |

| 8-bit subtraction (indirect addressing) | 9,00        |

| 8-bit subtraction (register addressing) | 12,00       |

| 8-bit multiplication                    | 16,00       |

| 8-bit division                          | 9,60        |

| 16-bit addition                         | 12,00       |

| 16-bit subtraction                      | 12,00       |

| 16-bit multiplication                   | 13,60       |

| 32-bit addition                         | 12,00       |

| 32-bit subtraction                      | 12,00       |

| 32-bit multiplication                   | 12,60       |

| Average speed improvement:              | 11,12       |

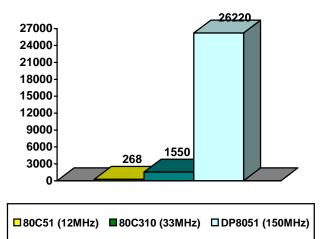

Dhrystone Benchmark Version 2.1 was used to measure Core performance. The following table gives a survey about the DP80390 performance in terms of Dhrystone/sec and VAX MIPS rating.

| Device | Target     | Clock<br>fre-<br>quency | Dhry/sec<br>(VAX MIPS) |

|--------|------------|-------------------------|------------------------|

| 80C51  | -          | 12 MHz                  | 268 (0.153)            |

| 80C310 | -          | 33 MHz                  | 1550 (0.882)           |

| DP8051 | STRATIX-II | 150 MHz                 | 26220 (14.924)         |

Core performance in terms of Dhrystones

Area utilized by the each unit of DP80390 core in vendor specific technologies is summarized in table below.

| Component             | Area |       |  |  |  |  |  |

|-----------------------|------|-------|--|--|--|--|--|

| Component             | [LC] | [FFs] |  |  |  |  |  |

| CPU*                  | 1790 | 315   |  |  |  |  |  |

| Interrupt Controller  | 150  | 40    |  |  |  |  |  |

| Power Management Unit | 10   | 5     |  |  |  |  |  |

| I/O ports             | 100  | 35    |  |  |  |  |  |

| Timers                | 160  | 50    |  |  |  |  |  |

| UART0                 | 210  | 60    |  |  |  |  |  |

| Total area            | 2420 | 505   |  |  |  |  |  |

\*CPU – consisted of ALU, Opcode Decoder, Control Unit, Program & Internal & External Memory Interfaces, User SFRs Interface Core components area utilization in all technologies except STRATIX-II

| Component             | Area | 3     |

|-----------------------|------|-------|

| Component             | [LC] | [FFs] |

| CPU*                  | 1380 | 315   |

| Interrupt Controller  | 115  | 40    |

| Power Management Unit | 10   | 5     |

| I/O ports             | 75   | 35    |

| Timers                | 125  | 50    |

| UART0                 | 160  | 60    |

| Total area            | 1865 | 505   |

\*CPU – consisted of ALU, Opcode Decoder, Control Unit, Program & Internal & External Memory Interfaces, User SFRs Interface

\*Core components area utilization in STRATIX-II

The main features of each DP80390 family member have been summarized in table below. It gives a briefly member characterization helping user to select the most suitable IP Core for its application. User can specify its own peripheral set (including listed below and the others) and requests the core modifications.

| Design     | speed grade     | Program<br>Memory<br>space |             |          | ize             | Memory          | Memory         | / Program<br>States           | ment Unit        | S                             | sə              |                  |               | S              |      |          | ure             |          |                             |                                          |              |                            |                            |

|------------|-----------------|----------------------------|-------------|----------|-----------------|-----------------|----------------|-------------------------------|------------------|-------------------------------|-----------------|------------------|---------------|----------------|------|----------|-----------------|----------|-----------------------------|------------------------------------------|--------------|----------------------------|----------------------------|

|            | Architecture sp | on-chip RAM                | on-chip ROM | off-chip | Stack space siz | าal Data I<br>e | rnal Data<br>e | External Data / Memory Wait S | Power Management | Interface for additional SFRs | Interrupt sourc | Interrupt levels | Data Pointers | Timer/Counters | UART | NO Ports | Compare/Capture | Watchdog | ır I <sup>2</sup> (<br>olle | Slave I <sup>2</sup> C Bus<br>Controller | SPI          | Fixed Point<br>Coprocessor | Floating Point Coprocessor |

| DP80390CPU | 10              | 64k                        | 64k         | 8M       | 256             | 256             | 16M            | <b>√</b>                      | ✓                | <b>√</b>                      | 2               | 2                | 1             | -              | -    | -        | -               | -        | -                           | -                                        | -            | -                          | -                          |

| DP80390    | 10              | 64k                        | 64k         | 8M       | 256             | 256             | 16M            | <b>√</b>                      | <b>✓</b>         | ✓                             | 5               | 2                | 1             | 2              | 1    | 4        | -               | -        | -                           | -                                        | -            | -                          | -                          |

| DP80390XP  | 10              | 64k                        | 64k         | 8M       | 256             | 256             | 16M            | ✓                             | <b>√</b>         | ✓                             | 15              | 2                | 2             | 3              | 2    | 4        | $\checkmark$    | <b>√</b> | $\checkmark$                | $\checkmark$                             | $\checkmark$ | $\checkmark$               | $\checkmark$               |

DP80390 family of Pipelined High Performance Microcontroller Cores

The main features of each DP8051 family member have been summarized in table below. It gives a briefly member characterization helping user to select the most suitable IP Core for its application. User can specify its own peripheral set (including listed below and the others) and requests the core modifications.

| Design    | Architecture speed grade | Program<br>Memory<br>space |             |          | ize | Memory                   | Memory   | / Program<br>States   | ment Unit    | S                             | es              |                  |               | S              |      |           | ure             |              |                                           |                                          |              |                            |                            |

|-----------|--------------------------|----------------------------|-------------|----------|-----|--------------------------|----------|-----------------------|--------------|-------------------------------|-----------------|------------------|---------------|----------------|------|-----------|-----------------|--------------|-------------------------------------------|------------------------------------------|--------------|----------------------------|----------------------------|

|           |                          | on-chip RAM                | on-chip ROM | off-chip | S   | Internal Data M<br>space | nal Data | rnal Data<br>ory Wait | Σ            | Interface for additional SFRs | Interrupt sourc | Interrupt levels | Data Pointers | Timer/Counters | UART | I\O Ports | Compare/Capture | Watchdog     | Master I <sup>2</sup> C Bus<br>Controller | Slave I <sup>2</sup> C Bus<br>Controller | SPI          | Fixed Point<br>Coprocessor | Floating Point Coprocessor |

| DP8051CPU | 10                       | 64k                        | 64k         | 64k      | 256 | 256                      | 16M      | <b>√</b>              | $\checkmark$ | <b>√</b>                      | 2               | 2                | 1             | -              | -    | -         | -               | -            | -                                         | -                                        | -            | -                          | -                          |

| DP8051    | 10                       | 64k                        | 64k         | 64k      | 256 | 256                      | 16M      | ✓                     | <b>√</b>     | <b>\</b>                      | 5               | 2                | 1             | 2              | 1    | 4         | -               | -            | -                                         | -                                        | -            | -                          | -                          |

| DP8051XP  | 10                       | 64k                        | 64k         | 64k      | 256 | 256                      | 16M      | ✓                     | $\checkmark$ | ✓                             | 15              | 2                | 2             | 3              | 2    | 4         | ✓               | $\checkmark$ | $\checkmark$                              | $\checkmark$                             | $\checkmark$ | $\checkmark$               | $\checkmark$               |

DP8051 family of Pipelined High Performance Microcontroller Cores

# CONTACTS

For any modification or special request contact to DCD.

# **Headquarters:**

Wroclawska 94

41-902 Bytom, POLAND

e-mail: info@dcd.pl

tel. : +48 32 282 82 66

fax : +48 32 282 74 37

## **Distributors:**

Please check http://www.dcd.pl/apartn.php