# DP83816 10/100 Mb/s Integrated PCI Ethernet Media Access Controller and Physical Layer (MacPHYTER-II™)

### **General Description**

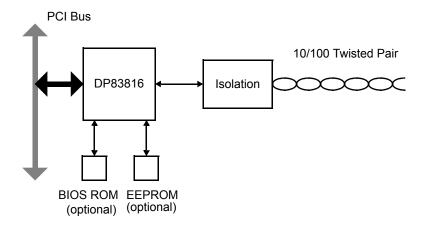

DP83816 is a single-chip 10/100 Mb/s Ethernet Controller for the PCI bus. It is targeted at low-cost, high volume PC motherboards, adapter cards, and embedded systems. The DP83816 fully implements the V2.2 33 MHz PCI bus interface for host communications with power management support. Packet descriptors and data are transferred via bus-mastering, reducing the burden on the host CPU. The DP83816 can support full duplex 10/100 Mb/s transmission and reception, with minimum interframe gap.

The DP83816 device is an integration of an enhanced version of the National Semiconductor PCI MAC/BIU (Media Access Controller/Bus Interface Unit) and a 3.3V CMOS physical layer interface.

#### **Features**

- IEEE 802.3 Compliant, PCI V2.2 MAC/BIU supports traditional data rates of 10 Mb/s Ethernet and 100 Mb/s Fast Ethernet (via internal phy)

- Bus master burst sizes of up to 128 dwords (512 bytes)

- BIU compliant with PC 97 and PC 98 Hardware Design Guides, PC 99 Hardware Design Guide draft, ACPI v1.0, PCI Power Management Specification v1.1, OnNow Device Class Power Management Reference Specification - Network Device Class v1.0a

- Wake on LAN (WOL) support compliant with PC98, PC99, SecureOn, and OnNow, including directed packets, Magic Packet™, VLAN packets, ARP packets, pattern match packets, and Phy status change

- Clkrun function for PCI Mobile Design Guide

- Virtual LAN (VLAN) and long frame support

- Support for IEEE 802.3x Full duplex flow control

- Extremely flexible Rx packet filtration including: single address perfect filter with MSb masking, broadcast, 512 entry multicast/unicast hash table, deep packet pattern matching for up to 4 unique patterns

- Statistics gathered for support of RFC 1213 (MIB II), RFC 1398 (Ether-like MIB), IEEE 802.3 LME, reducing CPU overhead for management

- Internal 2 KB Transmit and 2 KB Receive data FIFOs

- Serial EEPROM port with auto-load of configuration data from EEPROM at power-on

- Flash/PROM interface for remote boot support

- Fully integrated IEEE 802.3/802.3u 3.3V CMOS physical layer

- IEEE 802.3 10BASE-T transceiver with integrated filters

- IEEE 802.3u 100BASE-TX transceiver

- Fully integrated ANSI X3.263 compliant TP-PMD physical sublayer with adaptive equalization and Baseline Wander compensation

- IEEE 802.3u Auto-Negotiation advertised features configurable via EEPROM

- Full Duplex support for 10 and 100 Mb/s data rates

- Single 25 MHz reference clock

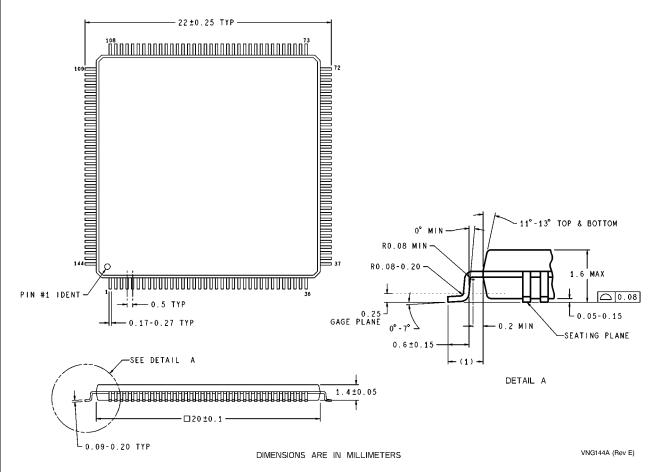

- 144-pin LQFP package

- Low power 3.3V CMOS design with typical consumption of 383 mW operating, 297 mW during WOL and 53 mW during sleep mode

- IEEE 802.3u MII for connecting alternative external Physical Layer Devices

- 3.3V signalling with 5V tolerant I/O.

### System Diagram

MacPHYTER-II™ is a trademark of National Semiconductor Corporation. Magic Packet™ is a trademark of Advanced Micro Devices, Inc.

#### **Table of Contents** Connection Diagram . . . . . . . . . . . . . . . 4 1.0 3.12.4 Serial Management Access Protocol ......... 28 144 LQFP Package (VNG) . . . . . . . . . . 4 1.1 3.12.5 Nibble-wide MII Data Interface . . . . . . . . . . . . 28 Pin Description ...... 5 3.0 4.1.1 Configuration Identification Register . . . . . . . . . . . . 30 4.1.2 Configuration Command and Status Register . . . 31 4.1.3 Configuration Revision ID Register .................... 32 4.1.5 Configuration I/O Base Address Register . . . . . . 33 4.1.6 Configuration Memory Address Register . . . . . . 34 4.1.7 Configuration Subsystem Identification Register . 34 3.3.2 Boot PROM ......14 4.1.11 Power Management Capabilities Register . . . . 36 4.1.12 Power Management Control and Status Register 37 3.4.2 Auto-Negotiation Register Control . . . . . . . . . . . . . . . . 16 4.2.2 Configuration and Media Status Register . . . . . . 40 3.4.3 Auto-Negotiation Parallel Detection . . . . . . . . . . . . . . 16 4.2.3 EEPROM Access Register . . . . . . . . . . . 42 3.4.5 Enabling Auto-Negotiation via Software .......17 4.2.5 PCI Test Control Register . . . . . . . . . . . . . . . . . . 43 4.2.7 Interrupt Mask Register . . . . . . . . . . . . . . . . . 45 4.2.8 Interrupt Enable Register . . . . . . . . . . . . . . 47 3.6 Half Duplex vs. Full Duplex . . . . . . . . . . . 18 4.2.9 Interrupt Holdoff Register . . . . . . . . . . . . . . . . . . 47 3.7 4.2.10 Transmit Descriptor Pointer Register . . . . . . . 48 3.8 4.2.11 Transmit Configuration Register . . . . . . . . . . 48 100BASE-TX TRANSMITTER . . . . . . . . . . 18 4.2.12 Receive Descriptor Pointer Register . . . . . . . . 50 4.2.13 Receive Configuration Register . . . . . . . . . 51 3.9.1 Code-group Encoding and Injection .....................19 4.2.14 CLKRUN Control/Status Register . . . . . . . . . . 52 4.2.15 Wake Command/Status Register . . . . . . . . 54 3.9.4 Binary to MLT-3 Convertor / Common Driver . . . . 20 4.2.16 Pause Control/Status Register . . . . . . . . . . . . . 56 4.2.17 Receive Filter/Match Control Register . . . . . . . 57 3.10 100BASE-TX Receiver . . . . . . . . . . . . 21 4.2.18 Receive Filter/Match Data Register . . . . . . . . . 58 3.10.1 Input and Base Line Wander Compensation . . . . 21 4.2.20 Boot ROM Address Register . . . . . . . . . . 63 4.2.23 Management Information Base Control Register 64 4.2.24 Management Information Base Registers . . . . . 65 4.3.1 Basic Mode Control Register . . . . . . . . . . . . 66 4.3.2 Basic Mode Status Register . . . . . . . . . 67 4.3.5 Auto-Negotiation Advertisement Register . . . . . 68 3.11 10BASE-T Transceiver Module . . . . . . . 26 4.3.6 Auto-Negotiation Link Partner Ability Register . . . 69 4.3.7 Auto-Negotiate Expansion Register . . . . . . . . 70 4.3.8 Auto-Negotiation Next Page Transmit Register . . 70 3.11.4 Normal Link Pulse Detection/Generation . . . . . . 26 4.3.11 MII Interrupt Status and Misc. Control Register . 73 4.3.12 False Carrier Sense Counter Register . . . . . . . 74 3.11.6 Automatic Link Polarity Detection . . . . . . . . . . . . . . . . . 27 4.3.14 100 Mb/s PCS Configuration and Status Register 74 4.3.16 10BASE-T Status/Control Register . . . . . . . . . 76

| 5.1.2 Multin           | ole Descriptor Packets                                                                                               |

|------------------------|----------------------------------------------------------------------------------------------------------------------|

|                        | · · · · · · · · · · · · · · · · · · ·                                                                                |

|                        |                                                                                                                      |

|                        | 3                                                                                                                    |

|                        | "D                                                                                                                   |

|                        | Architecture 04                                                                                                      |

|                        | ive State Machine                                                                                                    |

|                        | ive Data Flow                                                                                                        |

| 6.0 Power N            | Alanagement and Wake-On-LAN 87 7.2.1 PCI Clock Timing 91 7.2.2 X1 Clock Timing 91                                    |

|                        | Juction         87         7.2.2 × 1 Glock Hilling         92           7.2.3 Power On Reset (PCI Active)         92 |

| 6.2 Definit            | ions (for this document only) 87 7.2.4 Non Power On Reset                                                            |

| 6.3 Packet             | t Filtering                                                                                                          |

|                        | Management                                                                                                           |

|                        | tate 88 7.2.7 EEPROM Auto-Load                                                                                       |

|                        | 88 7.2.8 Boot PROM/FLASH                                                                                             |

| 6.4.3 D2 St            | tate                                                                                                                 |

|                        | 1 State                                                                                                              |

|                        | 10 State                                                                                                             |

|                        | On-LAN (WOL) Mode                                                                                                    |

|                        | ring WOL Mode                                                                                                        |

|                        | e Events                                                                                                             |

| 0.5.3 EXILIII          |                                                                                                                      |

| Figure 3-1             | List of Figures  DP83816 Functional Block Diagram11                                                                  |

| Figure 3-1             | MAC/BIU Functional Block Diagram                                                                                     |

| Figure 3-2             | Ethernet Packet Format                                                                                               |

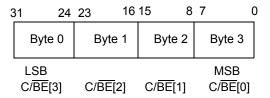

| Figure 3-4             | DSP Physical Layer Block Diagram                                                                                     |

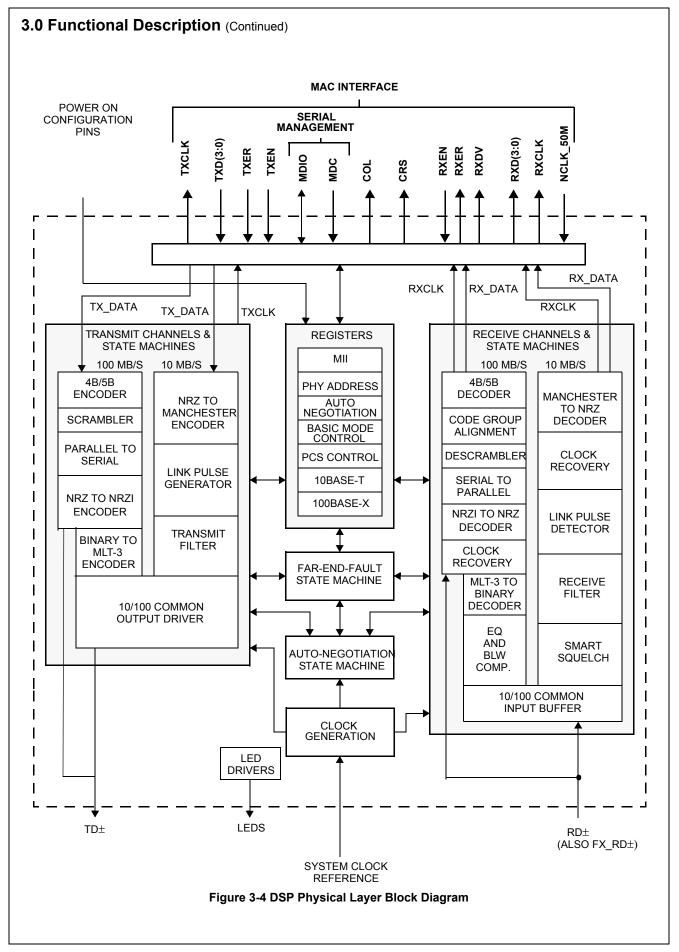

| Figure 3-5             | LED Loading Example                                                                                                  |

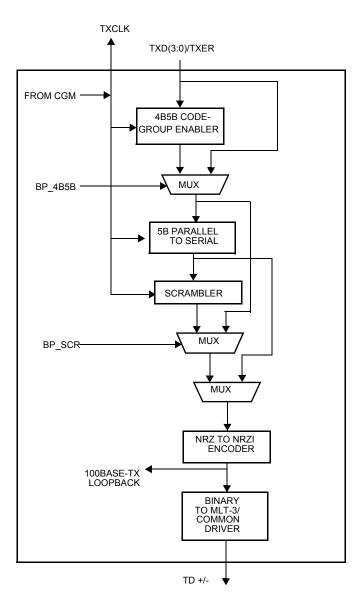

| Figure 3-6             | 100BASE-TX Transmit Block Diagram                                                                                    |

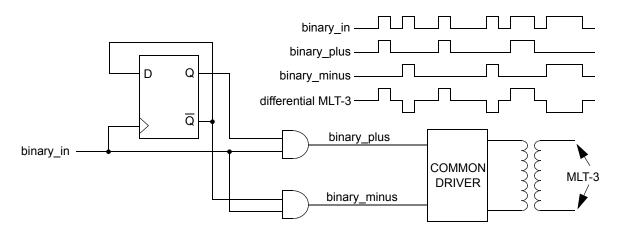

| Figure 3-7             | Binary to MLT-3 conversion                                                                                           |

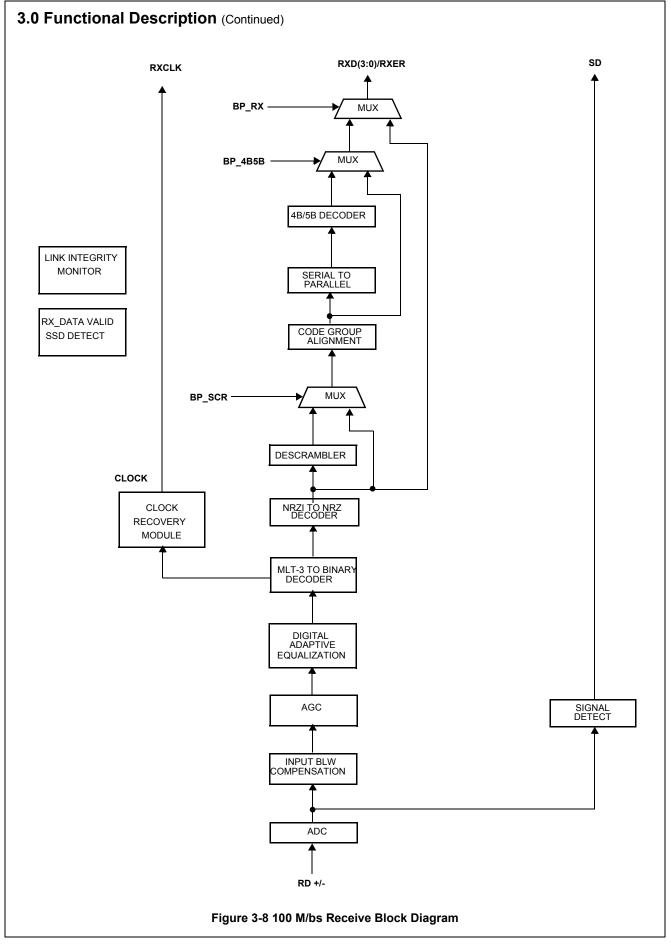

| Figure 3-8             | 100 M/bs Receive Block Diagram                                                                                       |

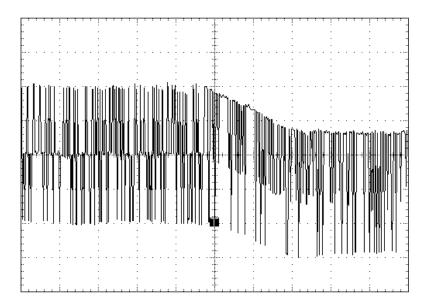

| Figure 3-9             | 100BASE-TX BLW Event Diagram                                                                                         |

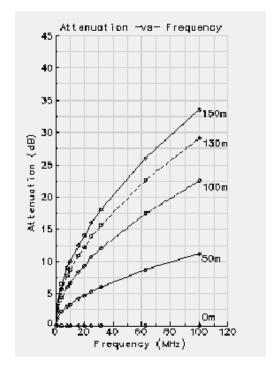

| Figure 3-10            | EIA/TIA Attenuation vs. Frequency for 0, 50, 100, 130 & 150 meters of CAT V cable                                    |

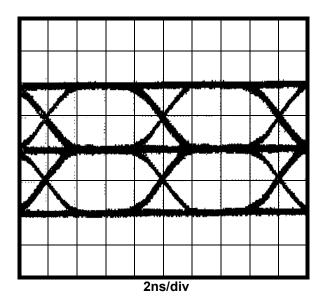

| Figure 3-11            | MLT-3 Signal Measured at All after 0 meters of CAT V cable                                                           |

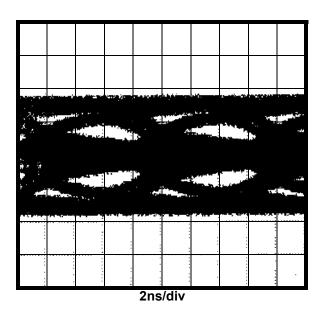

| Figure 3-12            | MLT-3 Signal Measured at All after 50 meters of CAT V cable24                                                        |

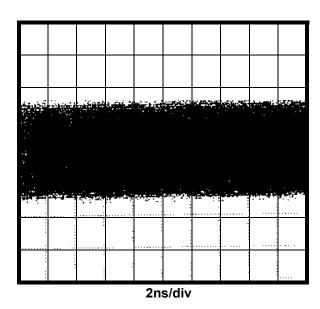

| Figure 3-13            | MLT-3 Signal Measured at All after 100 meters of CAT V cable24                                                       |

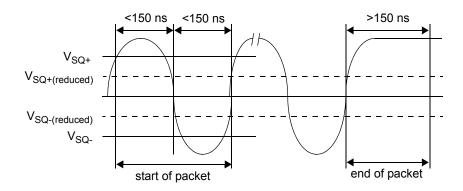

| Figure 3-14            | 10BASE-T Twisted Pair Smart Squelch Operation                                                                        |

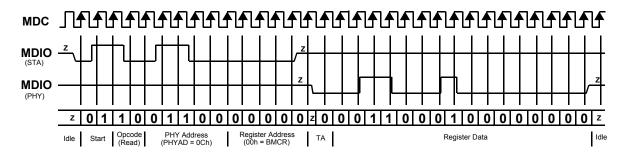

| Figure 3-15            | Typical MDC/MDIO Read Operation                                                                                      |

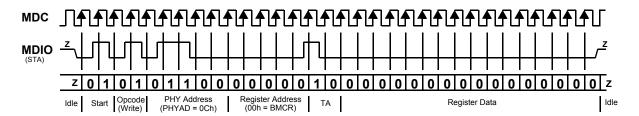

| Figure 3-16            | Typical MDC/MDIO Write Operation                                                                                     |

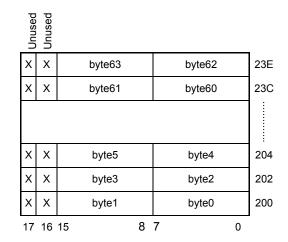

| Figure 4-1             | Pattern Buffer Memory - 180h words (word = 18bits)                                                                   |

| Figure 4-2             | Hash Table Memory - 40h bytes addressed on word boundaries                                                           |

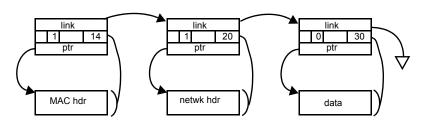

| Figure 5-1             | Single Descriptor Packets                                                                                            |

| Figure 5-2             | Multiple Descriptor Packets                                                                                          |

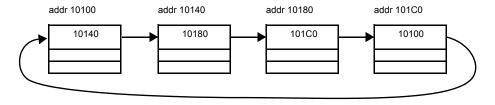

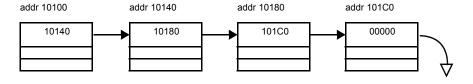

| Figure 5-3             | List and Ring Descriptor Organization                                                                                |

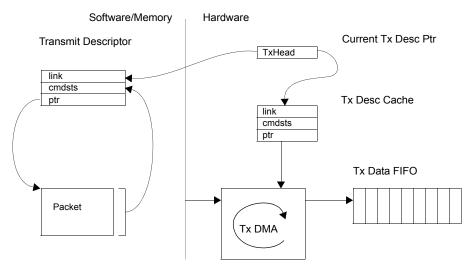

| Figure 5-4             | Transmit Architecture81                                                                                              |

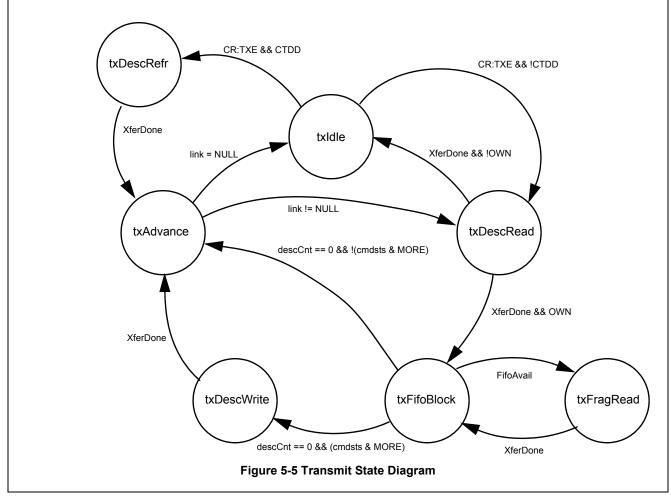

| Figure 5-5             | Transmit State Diagram82                                                                                             |

| Figure 5-6             | Receive Architecture                                                                                                 |

| Figure 5-7             | Receive State Diagram                                                                                                |

|                        | List of Tables                                                                                                       |

| Table 3-1              | 4B5B Code-Group Encoding/Decoding                                                                                    |

| Table 3-2              | Typical MDIO Frame Format                                                                                            |

| Table 4-1              | Configuration Register Map                                                                                           |

| Table 4-2              | Operational Register Map                                                                                             |

| Table 4-3              | MIB Registers                                                                                                        |

| Table 5-1              | DP83816 Descriptor Format                                                                                            |

| Table 5-2              | cmdsts Common Bit Definitions                                                                                        |

| Table 5-3<br>Table 5-4 |                                                                                                                      |

| Table 5-4<br>Table 5-5 | Receive Status Bit Definitions                                                                                       |

| Table 5-5              | Receive State Tables                                                                                                 |

| Table 5-6              | Power Management Modes                                                                                               |

| Table 6-1              | PM Pin Configuration                                                                                                 |

| I abic U-Z             | 1 W. F. III Ootinguration                                                                                            |

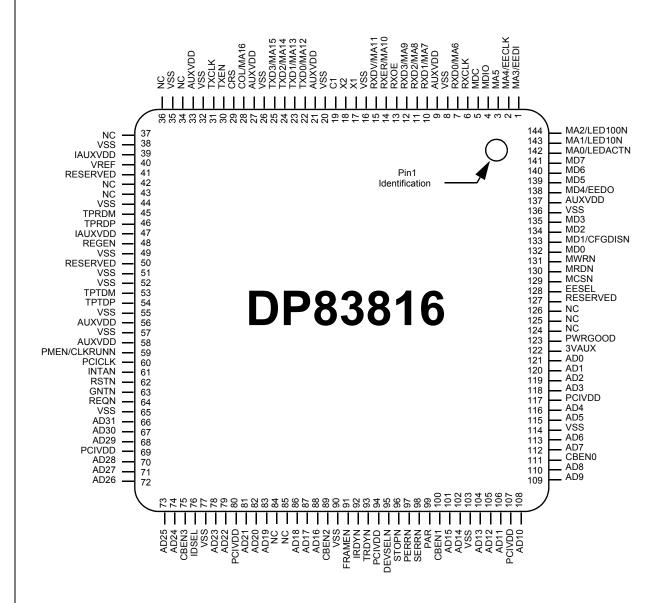

### 1.0 Connection Diagram

### 1.1 144 LQFP Package (VNG)

For Normal Operating Temperature - Order Number DP83816AVNG

See NS Package Number VNG144A

# 2.0 Pin Description

### **PCI Bus Interface**

| Symbol    | LQFP Pin<br>No(s)                                                                                                                                                  | Dir | Description                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD[31-0]  | 66, 67, 68, 70,<br>71, 72, 73, 74,<br>78, 79, 81, 82,<br>83, 86, 87, 88,<br>101, 102, 104,<br>105, 106, 108,<br>109, 110, 112,<br>113, 115, 116,<br>118, 119, 120, | I/O | Address and Data: Multiplexed address and data bus. As a bus master, the DP83816 will drive address during the first bus phase. During subsequent phases, the DP83816 will either read or write data expecting the target to increment its address pointer. As a bus target, the DP83816 will decode each address on the bus and respond if it is the target being addressed.                                                                |

| CBEN[3-0] | 75,<br>89,<br>100,<br>111                                                                                                                                          | I/O | Bus Command/Byte Enable: During the address phase these signals define the "bus command" or the type of bus transaction that will take place. During the data phase these pins indicate which byte lanes contain valid data. CBEN[0] applies to byte 0 (bits 7-0) and CBEN[3] applies to byte 3 (bits 31-24) in the Little Endian Mode. In Big Endian Mode, CBEN[3] applies to byte 0 (bits 31-24) and CBEN[0] applies to byte 3 (bits 7-0). |

| PCICLK    | 60                                                                                                                                                                 | I   | Clock: This PCI Bus clock provides timing for all bus phases. The rising edge defines the start of each phase. The clock frequency ranges from 0 to 33 MHz.                                                                                                                                                                                                                                                                                  |

| DEVSELN   | 95                                                                                                                                                                 | I/O | <b>Device Select:</b> As a bus master, the DP83816 samples this signal to insure that the destination address for the data transfer is recognized by a PCI target. As a target, the DP83816 asserts this signal low when it recognizes its address after FRAMEN is asserted.                                                                                                                                                                 |

| FRAMEN    | 91                                                                                                                                                                 | I/O | Frame: As a bus master, this signal is asserted low to indicate the beginning and duration of a bus transaction. Data transfer takes place when this signal is asserted. It is de-asserted before the transaction is in its final phase. As a target, the device monitors this signal before decoding the address to check if the current transaction is addressed to it.                                                                    |

| GNTN      | 63                                                                                                                                                                 | I   | <b>Grant:</b> This signal is asserted low to indicate to the DP83816 that it has been granted ownership of the bus by the central arbiter. This input is used when the DP83816 is acting as a bus master.                                                                                                                                                                                                                                    |

| IDSEL     | 76                                                                                                                                                                 | I   | Initialization Device Select: This pin is sampled by the DP83816 to identify when configuration read and write accesses are intended for it.                                                                                                                                                                                                                                                                                                 |

| INTAN     | 61                                                                                                                                                                 | 0   | Interrupt A: This signal is asserted low when an interrupt condition occurs as defined in the Interrupt Status Register, Interrupt Mask, and Interrupt Enable registers.                                                                                                                                                                                                                                                                     |

| IRDYN     | 92                                                                                                                                                                 | I/O | Initiator Ready: As a bus master, this signal will be asserted low when the DP83816 is ready to complete the current data phase transaction. This signal is used in conjunction with the TRYDN signal. Data transaction takes place at the rising edge of PCICLK when both IRDYN and TRDYN are asserted low. As a target this signal indicates that the master has put the data on the bus.                                                  |

| PAR       | 99                                                                                                                                                                 | I/O | <b>Parity:</b> This signal indicates even parity across AD[31-0] and CBEN[3-0] including the PAR pin. As a master, PAR is asserted during address and write data phases. As a target, PAR is asserted during read data phases.                                                                                                                                                                                                               |

| PERRN     | 97                                                                                                                                                                 | I/O | Parity Error: The DP83816 as a master or target will assert this signal low to indicate a parity error on any incoming data (except for special cycles). As a bus master, it will monitor this signal on all write operations (except for special cycles).                                                                                                                                                                                   |

| REQN      | 64                                                                                                                                                                 | 0   | <b>Request:</b> The DP83816 will assert this signal low to request ownership of the bus from the central arbiter.                                                                                                                                                                                                                                                                                                                            |

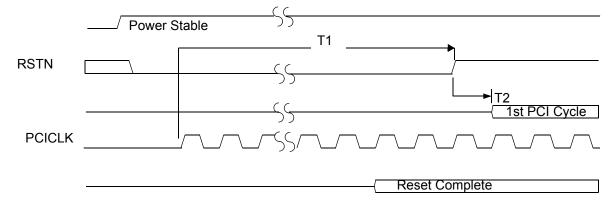

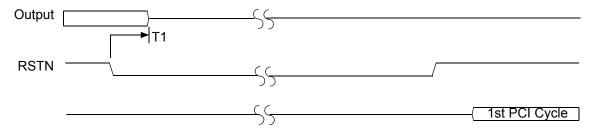

| RSTN      | 62                                                                                                                                                                 | I   | Reset: When this signal is asserted all PCI bus outputs of DP83816 will be in TRI-<br>STATE® and the device will be put into a known state.                                                                                                                                                                                                                                                                                                  |

### **PCI Bus Interface**

| Symbol           | LQFP Pin<br>No(s) | Dir | Description                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|-------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SERRN            | 98                | I/O | System Error: This signal is asserted low by DP83816 during address parity errors and system errors if enabled.                                                                                                                                                                                                                                                                                                                                       |

| STOPN            | 96                | I/O | <b>Stop:</b> This signal is asserted low by the target device to request the master device to stop the current transaction.                                                                                                                                                                                                                                                                                                                           |

| TRDYN            | 93                | I/O | Target Ready: As a master, this signal indicates that the target is ready for the data during write operation and with the data during read operation. As a target, this signal will be asserted low when the (target) device is ready to complete the curren data phase transaction. This signal is used in conjunction with the IRDYN signal. Data transaction takes place at the rising edge of PCICLK when both IRDYN and TRDYN are asserted low. |

| PMEN/<br>CLKRUNN | 59                | I/O | Power Management Event/Clock Run Function: This pin is a dual function pin. The function of this pin is determined by the CLKRUN_EN bit 0 of the CLKRUN Control and Status register (CCSR). Default operation of this pin is PMEN.                                                                                                                                                                                                                    |

|                  |                   |     | <b>Power Management Event:</b> This signal is asserted low by the DP83816 to indicate that a power management event has occurred. For pin connection please refer to Section 6.7.                                                                                                                                                                                                                                                                     |

|                  |                   |     | Clock Run Function: In this mode, this pin is used to indicate when the PCICLK will be stopped.                                                                                                                                                                                                                                                                                                                                                       |

| 3VAUX            | 122               | I   | <b>PCI Auxiliary Voltage Sense:</b> This pin is used to sense the presence of a 3.3V auxiliary supply in order to define the PME Support available. For pin connection please refer to Section 6.7.                                                                                                                                                                                                                                                   |

|                  |                   |     | This pin has an internal weak pull down.                                                                                                                                                                                                                                                                                                                                                                                                              |

| PWRGOOD          | 123               | I   | PCI bus power good: Connected to PCI bus 3.3V power, this pin is used to sense the presence of PCI bus power during the D3 power management state.                                                                                                                                                                                                                                                                                                    |

|                  |                   |     | This pin has an internal weak pull down.                                                                                                                                                                                                                                                                                                                                                                                                              |

### Media Independent Interface (MII)

| Symbol                                 | LQFP Pin<br>No(s) | Dir | Description                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------|-------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COL                                    | 28                | I   | Collision Detect: The COL signal is asserted high asynchronously by the externa PMD upon detection of a collision on the medium. It will remain asserted as long as the collision condition persists.                                                                                                                               |

| CRS                                    | 29                | Ι   | Carrier Sense: This signal is asserted high asynchronously by the external PMD upon detection of a non-idle medium.                                                                                                                                                                                                                 |

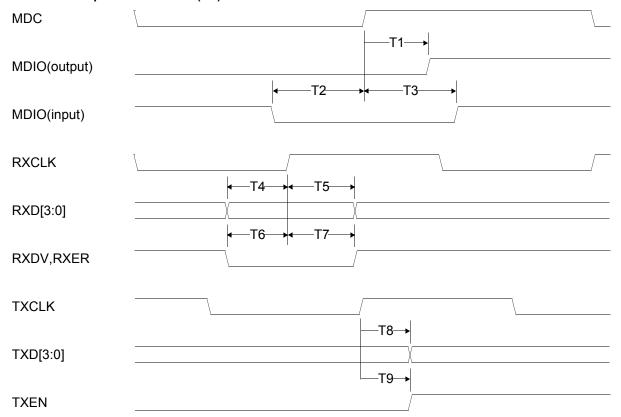

| MDC                                    | 5                 | 0   | Management Data Clock: Clock signal with a maximum rate of 2.5 MHz used to transfer management data for the external PMD on the MDIO pin.                                                                                                                                                                                           |

| MDIO                                   | 4                 | I/O | Management Data I/O: Bidirectional signal used to transfer management information for the external PMD. (See Section 3.12.4 for details on connections when MII is used.)                                                                                                                                                           |

| RXCLK                                  | 6                 | I   | <b>Receive Clock:</b> A continuous clock, sourced by an external PMD device, that is recovered from the incoming data. During 100 Mb/s operation RXCLK is 25 MHz and during 10 Mb/s this is 2.5 MHz.                                                                                                                                |

| RXD3/MA9,<br>RXD2/MA8,<br>RXD1/MA7,    | 12,<br>11,<br>10, | I   | Receive Data: Sourced from an external PMD, that contains data aligned on nibble boundaries and are driven synchronous to RXCLK. RXD[3] is the most significant bit and RXD[0] is the least significant bit.                                                                                                                        |

| RXD0/MA6                               | 7                 | 0   | <b>BIOS ROM Address:</b> During external BIOS ROM access, these signals become part of the ROM address.                                                                                                                                                                                                                             |

| RXDV/MA11                              | 15                | I   | Receive Data Valid: Indicates that the external PMD is presenting recovered and decoded nibbles on the RXD signals, and that RXCLK is synchronous to the recovered data in 100 Mb/s operation. This signal will encompass the frame, starting with the Start-of-Frame delimiter (JK) and excluding any End-of-Frame delimiter (TR). |

|                                        |                   | 0   | BIOS ROM Address: During external BIOS ROM access, this signal becomes pa of the ROM address.                                                                                                                                                                                                                                       |

| RXER/MA10                              | 14                | I   | Receive Error: Asserted high synchronously by the external PMD whenever it detects a media error and RXDV is asserted in 100 Mb/s operation.                                                                                                                                                                                        |

|                                        |                   | 0   | <b>BIOS ROM Address:</b> During external BIOS ROM access, this signal becomes part of the ROM address.                                                                                                                                                                                                                              |

| RXOE                                   | 13                | 0   | Receive Output Enable: Used to disable an external PMD while the BIOS ROM i being accessed.                                                                                                                                                                                                                                         |

| TXCLK                                  | 31                | I   | <b>Transmit Clock:</b> A continuous clock that is sourced by the external PMD. During 100 Mb/s operation this is 25 MHz +/- 100 ppm. During 10 Mb/s operation this cloc is 2.5 MHz +/- 100 ppm.                                                                                                                                     |

| TXD3/MA15,<br>TXD2/MA14,<br>TXD1/MA13, | 25,<br>24,<br>23, | 0   | <b>Transmit Data:</b> Signals which are driven synchronous to the TXCLK for transmission to the external PMD. TXD[3] is the most significant bit and TXD[0] is the least significant bit.                                                                                                                                           |

| TXD0/MA12                              | 22                | 0   | <b>BIOS ROM Address:</b> During external BIOS ROM access, these signals become part of the ROM address.                                                                                                                                                                                                                             |

| TXEN                                   | 30                | 0   | <b>Transmit Enable:</b> This signal is synchronous to TXCLK and provides precise framing for data carried on TXD[3-0] for the external PMD. It is asserted when TXD[3-0] contains valid data to be transmitted.                                                                                                                     |

Note: MII is normally in TRI-STATE, unless enabled by CFG:EXT\_PHY. See Section 4.2.2.

### 100BASE-TX/10BASE-T Interface

| Symbol       | LQFP Pin<br>No(s) | Dir | Description                                                                                                                                                        |

|--------------|-------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TPTDP, TPTDM | 54, 53            | A-O | <b>Transmit Data:</b> Differential common output driver. This differential common output is configurable to either 10BASE-T or 100BASE-TX signaling:               |

|              |                   |     | 10BASE-T: Transmission of Manchester encoded 10BASE-T packet data as well as Link Pulses (including Fast Link Pulses for Auto-Negotiation purposes).               |

|              |                   |     | 100BASE-TX: Transmission of ANSI X3T12 compliant MLT-3 data.                                                                                                       |

|              |                   |     | The DP83816 will automatically configure this common output driver for the proper signal type as a result of either forced configuration or Auto-Negotiation.      |

| TPRDP, TPRDM | 46, 45            | A-I | Receive Data: Differential common input buffer. This differential common input car be configured to accept either 100BASE-TX or 10BASE-T signaling:                |

|              |                   |     | 10BASE-T: Reception of Manchester encoded 10BASE-T packet data as well as normal Link Pulses and Fast Link Pulses for Auto-Negotiation purposes.                   |

|              |                   |     | 100BASE-TX: Reception of ANSI X3T12 compliant scrambled MLT-3 data.                                                                                                |

|              |                   |     | The DP83816 will automatically configure this common input buffer to accept the proper signal type as a result of either forced configuration or Auto-Negotiation. |

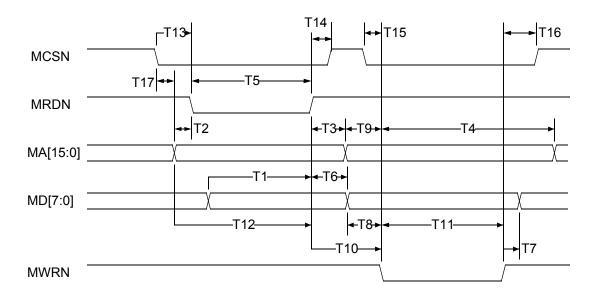

### **BIOS ROM/Flash Interface**

| Symbol                                                                           | LQFP Pin<br>No(s)                                  | Dir | Description                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------|----------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCSN                                                                             | 129                                                | 0   | BIOS ROM/Flash Chip Select: During a BIOS ROM/Flash access, this signal is used to select the ROM device.                                                                                                                    |

| MD7, MD6, MD5,<br>MD4/EEDO, MD3,<br>MD2,<br>MD1/CFGDISN,<br>MD0                  | 141, 140, 139,<br>138, 135,<br>134,<br>133,<br>132 | I/O | BIOS ROM/Flash Data Bus: During a BIOS ROM/Flash access these signals are used to transfer data to or from the ROM/Flash device.  MD[5:0] pins have internal weak pull ups.  MD6 and MD7 pins have internal weak pull downs. |

| MA5,<br>MA4/EECLK,<br>MA3/EEDI,<br>MA2/LED100LNK,<br>MA1/LED10LNK,<br>MA0/LEDACT | 3,<br>2,<br>1,<br>144,<br>143,<br>142              | 0   | BIOS ROM/Flash Address: During a BIOS ROM/Flash access, these signals are used to drive the ROM/Flash address.                                                                                                               |

| MWRN                                                                             | 131                                                | 0   | BIOS ROM/Flash Write: During a BIOS ROM/Flash access, this signal is used to enable data to be written to the Flash device.                                                                                                  |

| MRDN                                                                             | 130                                                | 0   | BIOS ROM/Flash Read: During a BIOS ROM/Flash access, this signal is used to enable data to be read from the Flash device.                                                                                                    |

Note: DP83816 supports NM27LV010 for the BIOS ROM interface device.

### **Clock Interface**

| Symbol | LQFP Pin<br>No(s) | Dir | Description                                                                                                                                                                                                                                                                                                                    |

|--------|-------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

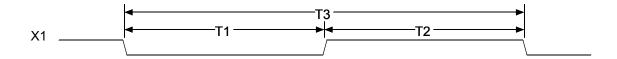

| X1     | 17                | I   | Crystal/Oscillator Input: This pin is the primary clock reference input for the DP83816 and must be connected to a 25 MHz 0.005% (50ppm) clock source. The DP83816 device supports either an external crystal resonator connected across pins X1 and X2, or an external CMOS-level oscillator source connected to pin X1 only. |

| X2     | 18                | 0   | <b>Crystal Output:</b> This pin is used in conjunction with the X1 pin to connect to an external 25 MHz crystal resonator device. This pin must be left unconnected if an external CMOS oscillator clock source is utilized. For more information see the definition for pin X1.                                               |

#### **LED Interface**

| Symbol      | LQFP Pin<br>No(s) | Dir | Description                                                                                                                                                                                                                                                                               |

|-------------|-------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LEDACTN/MA0 | 142               | 0   | <b>TX/RX Activity:</b> This pin is an output indicating transmit/receive activity. This pin is driven low to indicate active transmission or reception, and can be used to drive a low current LED (<6 mA). The activity event is stretched to a minimum duration of approximately 50 ms. |

| LED100N/MA2 | 144               | 0   | <b>100 Mb/s Link:</b> This pin is an output indicating the 100 Mb/s Link status. This pin is driven low to indicate Good Link status for 100 Mb/s operation, and can be used to drive a low current LED (<6 mA).                                                                          |

| LED10N/MA1  | 143               | 0   | 10 Mb/s Link: This pin is an output indicating the 10 Mb/s Link status. This pin is driven low to indicate Good Link status for 10 Mb/s operation, and can be used to drive a low current LED (<6 mA).                                                                                    |

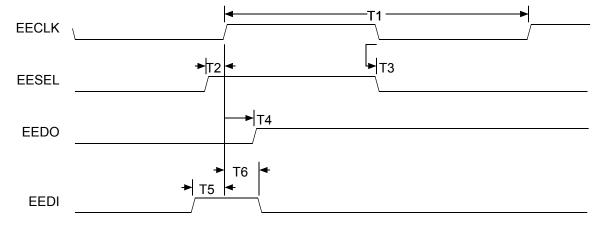

### **Serial EEPROM Interface**

| Symbol      | LQFP Pin<br>No(s) | Dir | Description                                                                                                                                                              |

|-------------|-------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

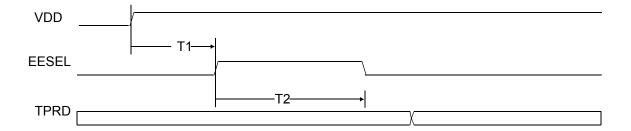

| EESEL       | 128               | 0   | <b>EEPROM Chip Select:</b> This signal is used to enable an external EEPROM device.                                                                                      |

| EECLK/MA4   | 2                 | 0   | <b>EEPROM Clock:</b> During an EEPROM access (EESEL asserted), this pin is an output used to drive the serial clock to an external EEPROM device.                        |

| EEDI/MA3    | 1                 | 0   | <b>EEPROM Data In:</b> During an EEPROM access (EESEL asserted), this pin is an output used to drive opcode, address, and data to an external serial EEPROM device.      |

| EEDO/MD4    | 138               | I   | <b>EEPROM Data Out:</b> During an EEPROM access (EESEL asserted), this pin is an input used to retrieve EEPROM serial read data.  This pin has an internal weak pull up. |

| MD1/CFGDISN | 133               | I/O | Configuration Disable: When pulled low at power-on time, disables load of configuration data from the EEPROM. Use 1 K $\Omega$ to ground to disable configuration load.  |

Note: DP83816 supports NMC93C46 for the EEPROM device.

### **External Reference Interface**

| Symbol | LQFP Pin<br>No(s) | Dir | Description                                                                                                                                                                                                                                   |

|--------|-------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VREF   | 40                | I   | <b>Bandgap Reference:</b> External current reference resistor for internal Phy bandgap circuitry. The value of this resistor is $10K\Omega$ 1% metal film (100 ppm/ $^{\circ}$ C) which must be connected from the VREF pin to analog ground. |

### No Connects and Reserved

| Symbol   | LQFP Pin<br>No(s)                               | Dir | Description                                                                                             |

|----------|-------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------|

| NC       | 34, 42, 43, 36,<br>37, 84, 85,<br>124, 125, 126 |     | No Connect                                                                                              |

| RESERVED | 41, 50, 127                                     |     | These pins are reserved and cannot be connected to any external logic or net.                           |

| REGEN    | 48                                              |     | Reserved and cannot be connected to any external logic or net  This pin has an internal weak pull down. |

### **Supply Pins**

| Symbol  | LQFP Pin<br>No(s)                                                                        | Dir | Description                                                            |

|---------|------------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------|

| C1      | 19                                                                                       | S   | Connect to GND through 10uF and 0.1uF external capacitors in parallel. |

| IAUXVDD | 39, 47                                                                                   | S   | Connect to isolated Aux 3.3V supply VDD                                |

| AUXVDD  | 9, 21, 27, 33,<br>56, 58, 137                                                            | S   | Connect to Aux 3.3V supply VDD                                         |

| PCIVDD  | 69, 80, 94,<br>107, 117                                                                  | S   | PCI VDD - connect to PCI bus 3.3V VDD                                  |

| VSS     | 8, 16, 20, 26,<br>32, 35, 38, 44,<br>49, 51, 52, 55,<br>57, 65, 77, 90,<br>103, 114, 136 | S   | VSS                                                                    |

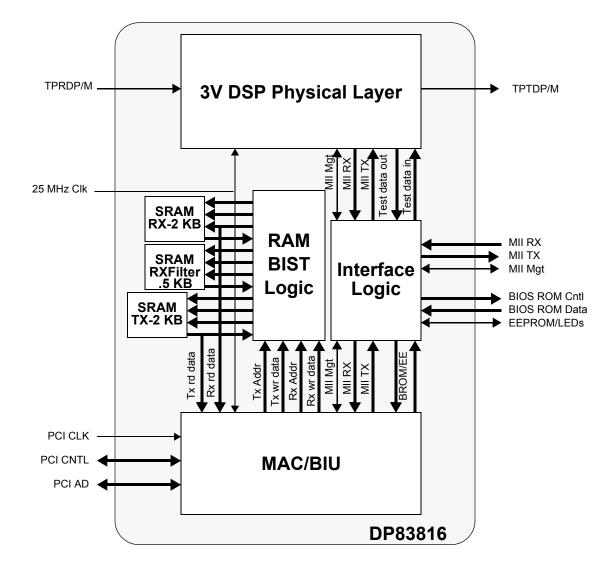

### 3.0 Functional Description

DP83816 consists of a MAC/BIU (Media Access Controller/Bus Interface Unit), a physical layer interface, SRAM, and miscellaneous support logic. The MAC/BIU includes the PCI bus, BIOS ROM and EEPROM interfaces,

and an 802.3 MAC. The physical layer interface used is a single-port version of the 3.3V DsPhyterII. Internal memory consists of one - 0.5 KB and two - 2 KB SRAM blocks.

Figure 3-1 DP83816 Functional Block Diagram

Figure 3-2 MAC/BIU Functional Block Diagram

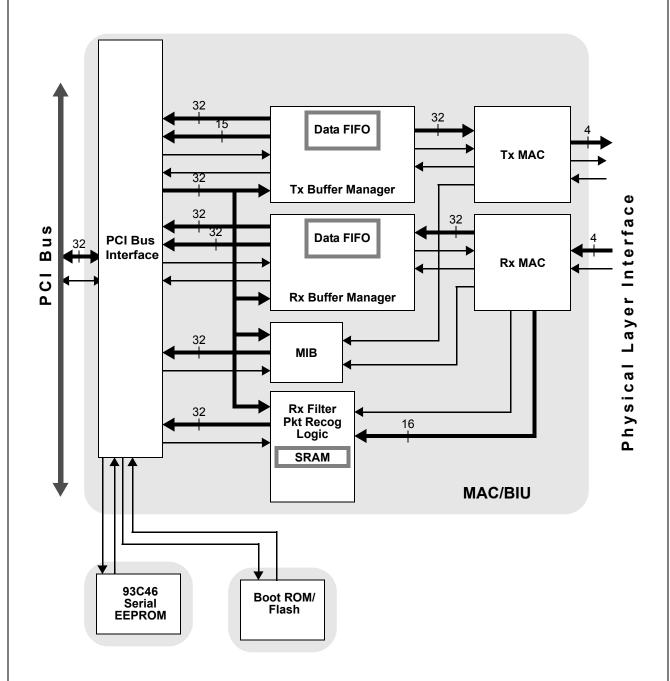

#### 3.1 MAC/BIU

The MAC/BIU is a derivative design from the DP83810 (Euphrates). The original MAC/BIU design has been optimized to improve logic efficiency and enhanced to add features consistent with current market needs and specification compliance. The MAC/BIU design blocks are discussed in this section.

#### 3.1.1 PCI Bus Interface

This block implements PCI v2.2 bus protocols, and configuration space. Supports bus master reads and writes to CPU memory, and CPU access to on-chip register space. Additional functions provided include: configuration

control, serial EEPROM access with auto configuration load, interrupt control, power management control with support for PME or CLKRUN function.

### 3.1.1.1 Byte Ordering

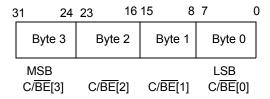

The DP83816 can be configured to order the bytes of data on the AD[31:0] bus to conform to little endian or big endian ordering through the use of the Configuration Register, bit 0 (CFG:BEM). By default, the device is in little endian ordering. Byte ordering only affects data FIFOs. Register information remains bit aligned (i.e. AD[31] maps to bit 31 in any register space, AD[0] maps to bit 0, etc.).

**Little Endian (CFG:BEM=0):** The byte orientation for receive and transmit data in system memory is as follows:

**Big Endian (CFG:BEM=1):** The byte orientation for receive and transmit data in system memory is as follows:

#### 3.1.1.2 PCI Bus Interrupt Control

PCI bus interrupts for the DP83816 are asynchronously performed by asserting pin INTAN. This pin is an open drain output. The source of the interrupt can be determined by reading the Interrupt Status Register (ISR). One or more bits in the ISR will be set, denoting all currently pending interrupts. **Caution:** Reading of the ISR clears ALL bits. Masking of specified interrupts can be accomplished by using the Interrupt Mask Register (IMR).

#### 3.1.1.3 Timer

The Latency Timer described in CFGLAT:LAT defines the minimum number of bus clocks that the device will hold the bus. Once the device gains control of the bus and issues FRAMEN, the Latency Timer will begin counting down. If GNTN is de-asserted before the DP83816 has finished with the bus, the device will maintain ownership of the bus until the timer reaches zero (or has finished the bus transfer). The timer is an 8-bit counter.

#### 3.1.2 Tx MAC

This block implements the transmit portion of 802.3 Media Access Control. The Tx MAC retrieves packet data from the Tx Buffer Manager and sends it out through the transmit portion. Additionally, the Tx MAC provides MIB control information for transmit packets.

#### 3.1.3 Rx MAC

This block implements the receive portion of 802.3 Media Access Control. The Rx MAC retrieves packet data from the receive portion and sends it to the Rx Buffer Manager. Additionally, the Rx MAC provides MIB control information and packet address data for the Rx Filter.

#### 3.2 Buffer Management

The buffer management scheme used on the DP83816 allows quick, simple and efficient use of the frame buffer memory. Frames are saved in similar formats for both

transmit and receive. The buffer management scheme also uses separate buffers and descriptors for packet information. This allows effective transfers of data from the receive buffer to the transmit buffer by simply transferring the descriptor from the receive queue to the transmit queue.

The format of the descriptors allows the packets to be saved in a number of configurations. A packet can be stored in memory with a single descriptor per single packet, or multiple descriptors per single packet. This flexibility allows the user to configure the DP83816 to maximize efficiency. Architecture of the specific system's buffer memory, as well as the nature of network traffic, will determine the most suitable configuration of packet descriptors and fragments. Refer to the Buffer Management Section (Section 5.0) for more information.

#### 3.2.1 Tx Buffer Manager

This block DMAs packet data from PCI memory space and places it in the 2 KB transmit FIFO, and pulls data from the FIFO to send to the Tx MAC. Multiple packets (4) may be present in the FIFO, allowing packets to be transmitted with minimum interframe gap. The way in which the FIFO is emptied and filled is controlled by the FIFO threshold values in the TXCFG register: FLTH (Tx Fill Threshold) and DRTH (Tx Drain Threshold). These values determine how full or empty the FIFO must be before the device requests the bus. Additionally, once the DP83816 requests the bus, it will attempt to empty or fill the FIFO as allowed by the MXDMA setting in the TXCFG register.

#### 3.2.2 Rx Buffer Manager

This block retrieves packet data from the Rx MAC and places it in the 2 KB receive data FIFO, and pulls data from the FIFO for DMA to PCI memory space. The Rx Buffer Manager maintains a status FIFO, allowing up to 4 packets to reside in the FIFO at once. Similar to the transmit FIFO, the receive FIFO is controlled by the FIFO threshold value in the RXCFG register: DRTH (Rx Drain Threshold). This value determines the number of long words written into the FIFO from the MAC unit before a DMA request for system memory access occurs. Once the DP83816 gets the bus, it will continue to transfer the long words from the FIFO until the data in the FIFO is less than one long word, or has reached the end of the packet, or the max DMA burst size is reached (RXCFG:MXDMA).

#### 3.2.3 Packet Recognition

The Receive packet filter and recognition logic allows software to control which packets are accepted based on destination address and packet type. Address recognition logic includes support for broadcast, multicast hash, and unicast addresses. The packet recognition logic includes support for WOL, Pause, and programmable pattern recognition.

The standard 802.3 Ethernet packet consists of the following fields: Preamble (PA), Start of Frame Delimiter (SFD), Destination Address (DA), Source Address (SA), Length (LEN), Data and Frame Check Sequence (FCS). All fields are fixed length except for the data field. During reception, the PA, SFD and FCS are stripped. During transmission, the DP83816 generates and appends the PA, SFD and FCS.

| PA  | SFD | DA | SA | LEN | Data      | FCS |

|-----|-----|----|----|-----|-----------|-----|

| 60b | 4b  | 6B | 6B | 2B  | 46B-1500B | 4B  |

Note: B = Bytes b = bits

**Figure 3-3 Ethernet Packet Format**

#### 3.2.4 MIB

The MIB block contains counters to track certain media events required by the management specifications RFC 1213 (MIB II), RFC 1398 (Ether-like MIB), and IEEE 802.3 LME. The counters provided are for events which are either difficult or impossible to be intercepted directly by software. Not all counters are implemented, however required counters can be calculated from the counters provided.

#### 3.3 Interface Definitions

#### 3.3.1 PCI System Bus

This interface allows direct connection of the DP83816 to a 33 MHz PCI system bus. The DP83816 supports zero wait state data transfers with burst sizes up to 128 dwords. The

DP83816 conforms to 3.3V AC/DC specifications, but has 5V tolerant inputs.

#### 3.3.2 Boot PROM

The BIOS ROM interface allows the DP83816 to read from and write data to an external ROM/Flash device.

#### **3.3.3 EEPROM**

The DP83816 supports the attachment of an external EEPROM. The EEPROM interface provides the ability for the DP83816 to read from and write data to an external serial EEPROM device. The DP83816 will auto-load values from the EEPROM to certain fields in PCI configuration space and operational space and perform a checksum to verify that the data is valid. Values in the external EEPROM allow default fields in PCI configuration space and I/O space to be overridden following a hardware reset. If the EEPROM is not present, the DP83816 initialization uses default values for the appropriate Configuration and Operational Registers. Software can read and write to the EEPROM using "bit-bang" accesses via the EEPROM Access Register (MEAR).

#### 3.3.4 Clock

The clock interface provides the 25 MHz clock reference input for the DP83816 IC. The X1 input signal amplitude should be approximately 1V. This interface supports operation from a 25 MHz, 50 ppm CMOS oscillator, or a 25 MHz, 50 ppm, parallel, 20 pF load, < 40  $\Omega$  ESR crystal resonator. A 20pF crystal resonator would require C1 and

### 3.4 Physical Layer

The DP83816 has a full featured physical layer device with integrated PMD sub-layers to support both 10BASE-T and 100BASE-TX Ethernet protocols. The physical layer is designed for easy implementation of 10/100 Mb/s Ethernet home or office solutions. It interfaces directly to twisted pair media via an external transformer. The physical layer utilizes on chip Digital Signal Processing (DSP) technology and digital PLLs for robust performance under all operating conditions, enhanced noise immunity, and lower external component count when compared to analog solutions.

#### 3.4.1 Auto-Negotiation

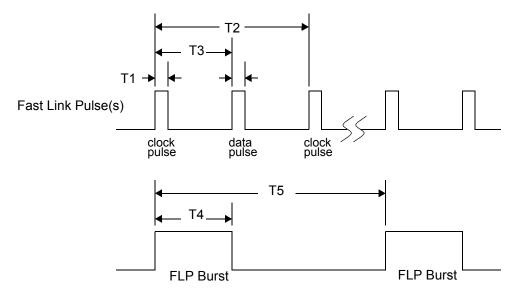

The Auto-Negotiation function provides a mechanism for exchanging configuration information between two ends of a link segment and automatically selecting the highest performance mode of operation supported by both devices. Fast Link Pulse (FLP) Bursts provide the signalling used to communicate Auto-Negotiation abilities between two devices at each end of a link segment. For further detail regarding Auto-Negotiation, refer to Clause 28 of the IEEE 802.3u specification. The DP83816 supports four different Ethernet protocols (10 Mb/s Half Duplex, 10 Mb/s Full Duplex, 100 Mb/s Half Duplex, and 100 Mb/s Full Duplex), so the inclusion of Auto-Negotiation ensures that the highest performance protocol will be selected based on the advertised ability of the Link Partner. The Auto-Negotiation function within the DP83816 is controlled by internal register access. Auto-Negotiation will be set at powerup/reset, and also when a link status (up/valid) change occurs.

### 3.4.2 Auto-Negotiation Register Control

When Auto-Negotiation is enabled, the DP83816 transmits the abilities programmed into the Auto-Negotiation Advertisement register (ANAR) via FLP Bursts. Any combination of 10 Mb/s, 100 Mb/s, Half-Duplex, and Full Duplex modes may be selected. The default setting of bits [8:5] in the ANAR and bit 12 in the BMCR register are determined at power-up.

The BMCR provides software with a mechanism to control the operation of the DP83816. Bits 1 & 2 of the PHYSTS register are only valid if Auto-Negotiation is disabled or after Auto-Negotiation is complete. The Auto-Negotiation protocol compares the contents of the ANLPAR and ANAR registers and uses the results to automatically configure to the highest performance protocol common to the local and far-end port. The results of Auto-Negotiation may be accessed in register C0h (PHYSTS), bit 4: Auto-Negotiation Complete, bit 2: Duplex Status and bit 1: Speed Status.

Auto-Negotiation Priority Resolution:

- (1) 100BASE-TX Full Duplex (Highest Priority)

- (2) 100BASE-TX Half Duplex

- (3) 10BASE-T Full Duplex

- (4) 10BASE-T Half Duplex (Lowest Priority)

The Basic Mode Control Register (BMCR) provides control for enabling, disabling, and restarting the Auto-Negotiation process. When Auto-Negotiation is disabled the Speed Selection bit in the BMCR (bit 13) controls switching between 10 Mb/s or 100 Mb/s operation, and the Duplex Mode bit (bit 8) controls switching between full duplex operation and half duplex operation. The Speed Selection and Duplex Mode bits have no effect on the mode of

operation when the Auto-Negotiation Enable bit (bit 12) is set

The Basic Mode Status Register (BMSR) indicates the set of available abilities for technology types, Auto-Negotiation ability, and Extended Register Capability. These bits are permanently set to indicate the full functionality of the DP83816 (only the 100BASE-T4 bit is not set since the DP83816 does not support that function).

The BMSR also provides status on:

- Auto-Negotiation complete (bit 5)

- Link Partner advertising that a remote fault has occurred (bit 4)

- Valid link has been established (bit 2)

- Support for Management Frame Preamble suppression (bit 6)

The Auto-Negotiation Advertisement Register (ANAR) indicates the Auto-Negotiation abilities to be advertised by the DP83816. All available abilities are transmitted by default, but any ability can be suppressed by writing to the ANAR. Updating the ANAR to suppress an ability is one way for a management agent to change (force) the technology that is used.

The Auto-Negotiation Link Partner Ability Register (ANLPAR) is used to receive the base link code word as well as all next page code words during the negotiation. Furthermore, the ANLPAR will be updated to either 0081h or 0021h for parallel detection to either 100 Mb/s or 10 Mb/s respectively.

The Auto-Negotiation Expansion Register (ANER) indicates additional Auto-Negotiation status. The ANER provides status on:

- Parallel Detect Fault occurrence (bit 4)

- Link Partner support of the Next Page function (bit 3)

- DP83816 support of the Next Page function (bit 2). The DP83816 supports the Next Page function.

- Current page being exchanged by Auto-Negotiation has been received (bit1)

- Link Partner support of Auto-Negotiation (bit 0)

#### 3.4.3 Auto-Negotiation Parallel Detection

The DP83816 supports the Parallel Detection function as defined in the IEEE 802.3u specification. Parallel Detection requires both the 10 Mb/s and 100 Mb/s receivers to monitor the receive signal and report link status to the Auto-Negotiation function. Auto-Negotiation uses this information to configure the correct technology in the event that the Link Partner does not support Auto-Negotiation yet is transmitting link signals that the 100BASE-TX or 10BASE-T PMAs (Physical Medium Attachments) recognize as valid link signals.

If the DP83816 completes Auto-Negotiation as a result of Parallel Detection, bits 5 and 7 within the ANLPAR register will be updated to reflect the mode of operation present in the Link Partner. Note that bits 4:0 of the ANLPAR will also be set to 00001 based on a successful parallel detection to indicate a valid 802.3 selector field. Software may determine that negotiation completed via Parallel Detection by reading the ANER (98h) register with bit 0, Link Partner Auto-Negotiation Able bit, being reset to a zero, once the Auto-Negotiation Complete bit, bit 5 of the BMSR (84h) register is set to a one. If configured for parallel detect

mode, and any condition other than a single good link occurs, then the parallel detect fault bit will set to a one, bit 4 of the ANER register (98h).

The LED100N pin indicates a good link at 100 Mb/s data occurs, then the parallel detect fault bit will set to a one, bit occurs. In 100BASE-T mode, link is established as a result

#### 3.4.4 Auto-Negotiation Restart

Once Auto-Negotiation has completed, it may be restarted at any time by setting bit 9 (Restart Auto-Negotiation) of the BMCR to one. If the mode configured by a successful Auto-Negotiation loses a valid link, then the Auto-Negotiation process will resume and attempt to determine the configuration for the link. This function ensures that a valid configuration is maintained if the cable becomes disconnected.

A renegotiation request from any entity, such as a management agent, will cause the DP83816 to halt any transmit data and link pulse activity until the break\_link\_timer expires (~1500 ms). Consequently, the Link Partner will go into link fail and normal Auto-Negotiation resumes. The DP83816 will resume Auto-Negotiation after the break\_link\_timer has expired by issuing FLP (Fast Link Pulse) bursts.

### 3.4.5 Enabling Auto-Negotiation via Software

It is important to note that if the DP83816 has been initialized upon power-up as a non-auto-negotiating device (forced technology), and it is then required that Auto-Negotiation or re-Auto-Negotiation be initiated via software, bit 12 (Auto-Negotiation Enable) of the Basic Mode Control Register must first be cleared and then set for any Auto-Negotiation function to take effect.

### 3.4.6 Auto-Negotiation Complete Time

Parallel detection and Auto-Negotiation take approximately 2-3 seconds to complete. In addition, Auto-Negotiation with next page should take approximately 2-3 seconds to complete, depending on the number of next pages sent.

Refer to Clause 28 of the IEEE 802.3u standard for a full description of the individual timers related to Auto-Negotiation.

#### 3.5 LED Interfaces

The DP83816 has parallel outputs to indicate the status of Activity (Transmit or Receive), 100 Mb/s Link, and 10 Mb/s Link.

The LEDACTN pin indicates the presence of transmit or receive activity. The standard CMOS driver goes low when RX or TX activity is detected in either 10 Mb/s or 100 Mb/s operation.

The LED100N pin indicates a good link at 100 Mb/s data rate. The standard CMOS driver goes low when this occurs. In 100BASE-T mode, link is established as a result of input receive amplitude compliant with TP-PMD specifications which will result in internal generation of signal detect. This signal will assert after the internal Signal Detect has remained asserted for a minimum of 500 us. The signal will de-assert immediately following the deassertion of the internal signal detect.

The LED10N pin indicates a good link at 10 Mb/s data rate. The standard CMOS driver goes low when this occurs. 10 Mb/s Link is established as a result of the reception of at least seven consecutive normal Link Pulses or the reception of a valid 10BASE-T packet. This will cause the assertion of this signal. the signal will de-assert in accordance with the Link Loss Timer as specified in IEEE 802.3.

The DP83816 LED pins are capable of 6 mA. Connection of these LED pins should ensure this is not overloaded. Using 2 mA LED devices the connection for the LEDs could be as shown in Figure 3-5.

Figure 3-5 LED Loading Example

### 3.6 Half Duplex vs. Full Duplex

The DP83816 supports both half and full duplex operation at both 10 Mb/s and 100 Mb/s speeds.

Half-duplex is the standard, traditional mode of operation which relies on the CSMA/CD protocol to handle collisions and network access. In Half-Duplex mode, CRS responds to both transmit and receive activity in order to maintain compliance with IEEE 802.3 specification.

Since the DP83816 is designed to support simultaneous transmit and receive activity it is capable of supporting full-duplex switched applications with a throughput of up to 200 Mb/s per port when operating in 100BASE-TX mode. Because the CSMA/CD protocol does not apply to full-duplex operation, the DP83816 disables its own internal collision sensing and reporting functions.

It is important to understand that while full Auto-Negotiation with the use of Fast Link Pulse code words can interpret and configure to support full-duplex, parallel detection can not recognize the difference between full and half-duplex from a fixed 10 Mb/s or 100 Mb/s link partner over twisted pair. Therefore, as specified in 802.3u, if a far-end link partner is transmitting forced full duplex 100BASE-TX for example, the parallel detection state machine in the receiving station would be unable to detect the full duplex capability of the far-end link partner and would negotiate to a half duplex 100BASE-TX configuration (same scenario for 10 Mb/s).

For full duplex operation, the following register bits must also be set:

- TXCFG:CSI (Carrier Sense Ignore)

- TXCFG:HBI (HeartBeat Ignore)

- RXCFG:ATX (Accept Transmit Packets)

Additionally, the Auto-Negotiation Select bits in the Configuration register must show full duplex support:

- CFG:ANEG SEL

#### 3.7 Phy Loopback

The DP83816 includes a Phy Loopback Test mode for easy board diagnostics. The Loopback mode is selected through bit 14 (Loopback) of the Basic Mode Control Register (BMCR). Writing 1 to this bit enables transmit data to be routed to the receive path early in the physical layer cell. Loopback status may be checked in bit 3 of the PHY Status Register (C0h). While in Loopback mode the data will not be transmitted onto the media. This is true for either 10 Mb/s as well as 100 Mb/s data.

In 100BASE-TX Loopback mode the data is routed through the PCS and PMA layers into the PMD sublayer before it is looped back. Therefore, in addition to serving as a board diagnostic, this mode serves as quick functional verification of the device.

Note: A Mac Loopback can be performed via setting bit 29 (Mac Loopback) in the Tx Configuration Register.

#### 3.8 Status Information

There are 3 pins that are available to convey status information to the user through LEDs to indicate the speed (10 Mb/s or 100 Mb/s) link status and receive or transmit activity.

10 Mb/s Link is established as a result of the reception of at least seven consecutive Normal Link Pulses or the reception of a valid 10BASE-T packet. LED10N will deassert in accordance with the Link Loss Timer specified in IEEE 802.3.

100BASE-T Link is established as a result of an input receive amplitude compliant with TP-PMD specifications which will result in internal generation of Signal Detect. LED100N will assert after the internal Signal Detect has remained asserted for a minimum of 500  $\mu s$ . LED100N will de-assert immediately following the de-assertion of the internal Signal Detect.

Activity LED status indicates Receive or Transmit activity.

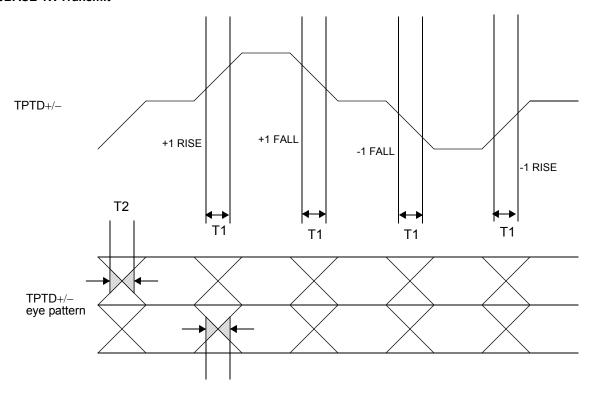

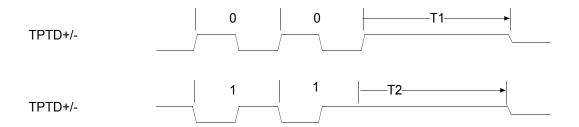

#### 3.9 100BASE-TX TRANSMITTER

The 100BASE-TX transmitter consists of several functional blocks which convert synchronous 4-bit nibble data, to a scrambled MLT-3 125 Mb/s serial data stream. Because the 100BASE-TX TP-PMD is integrated, the differential output pins, TD $\pm$ , can be directly routed to the magnetics.

The block diagram in Figure 3-6 provides an overview of each functional block within the 100BASE-TX transmit section.

The Transmitter section consists of the following functional blocks:

- Code-group Encoder and Injection block (bypass option)

- Scrambler block (bypass option)

- NRZ to NRZI encoder block

- Binary to MLT-3 converter / Common Driver

The bypass option for the functional blocks within the 100BASE-TX transmitter provides flexibility for applications such as 100 Mb/s repeaters where data conversion is not always required. The DP83816 implements the 100BASE-TX transmit state machine diagram as specified in the IEEE 802.3u Standard, Clause 24.

Figure 3-6 100BASE-TX Transmit Block Diagram

### 3.9.1 Code-group Encoding and Injection

The code-group encoder converts 4-bit (4B) nibble data generated by the MAC into 5-bit (5B) code-groups for transmission. This conversion is required to allow control data to be combined with packet data code-groups. Refer to Table 3-1 for 4B to 5B code-group mapping details.

The code-group encoder substitutes the first 8-bits of the MAC preamble with a J/K code-group pair (11000 10001) upon transmission. The code-group encoder continues to replace subsequent 4B preamble and data nibbles with corresponding 5B code-groups. At the end of the transmit packet, upon the de-assertion of Transmit Enable signal from the MAC, the code-group encoder injects the T/R code-group pair (01101 00111) indicating the end of frame.

After the T/R code-group pair, the code-group encoder continuously injects IDLEs into the transmit data stream until the next transmit packet is detected (re-assertion of Transmit Enable).

### 3.9.2 Scrambler

The scrambler is required to control the radiated emissions at the media connector and on the twisted pair cable (for 100BASE-TX applications). By scrambling the data, the total energy launched onto the cable is randomly distributed over a wide frequency range. Without the scrambler, energy levels at the PMD and on the cable could peak beyond FCC limitations at frequencies related to repeating 5B sequences (i.e., continuous transmission of IDLEs).

The scrambler is configured as a closed loop linear feedback shift register (LFSR) with an 11-bit polynomial. The output of the closed loop LFSR is X-ORd with the serial NRZ data from the code-group encoder. The result is a scrambled data stream with sufficient randomization to decrease radiated emissions at certain frequencies by as much as 20 dB.

#### 3.9.3 NRZ to NRZI Encoder

After the transmit data stream has been serialized and scrambled, the data must be NRZI encoded in order to comply with the TP-PMD standard for 100BASE-TX transmission over Category-5 un-shielded twisted pair cable. There is no ability to bypass this block within the DP83816.

### 3.9.4 Binary to MLT-3 Convertor / Common Driver

The Binary to MLT-3 conversion is accomplished by converting the serial binary data stream output from the NRZI encoder into two binary data streams with alternately phased logic one events. These two binary streams are then fed to the twisted pair output driver which converts the voltage to current and alternately drives either side of the transmit transformer primary winding, resulting in a minimal current (20 mA max) MLT-3 signal. Refer to Figure 3-7

Figure 3-7 Binary to MLT-3 conversion

Table 3-1 4B5B Code-Group Encoding/Decoding

| Name          | PCS 5B Code-group | Description/4B Value          |  |  |  |  |

|---------------|-------------------|-------------------------------|--|--|--|--|

| DATA CODES    | DATA CODES        |                               |  |  |  |  |

| 0             | 11110             | 0000                          |  |  |  |  |

| 1             | 01001             | 0001                          |  |  |  |  |

| 2             | 10100             | 0010                          |  |  |  |  |

| 3             | 10101             | 0011                          |  |  |  |  |

| 4             | 01010             | 0100                          |  |  |  |  |

| 5             | 01011             | 0101                          |  |  |  |  |

| 6             | 01110             | 0110                          |  |  |  |  |

| 7             | 01111             | 0111                          |  |  |  |  |

| 8             | 10010             | 1000                          |  |  |  |  |

| 9             | 10011             | 1001                          |  |  |  |  |

| Α             | 10110             | 1010                          |  |  |  |  |

| В             | 10111             | 1011                          |  |  |  |  |

| С             | 11010             | 1100                          |  |  |  |  |

| D             | 11011             | 1101                          |  |  |  |  |

| Е             | 11100             | 1110                          |  |  |  |  |

| F             | 11101             | 1111                          |  |  |  |  |

| IDLE AND CONT | ROL CODES         |                               |  |  |  |  |

| Н             | 00100             | HALT code-group - Error code  |  |  |  |  |

| 1             | 11111             | Inter-Packet IDLE - 0000      |  |  |  |  |

| J             | 11000             | First Start of Packet - 0101  |  |  |  |  |

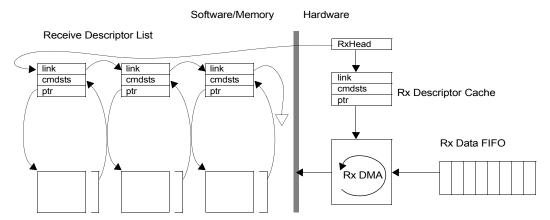

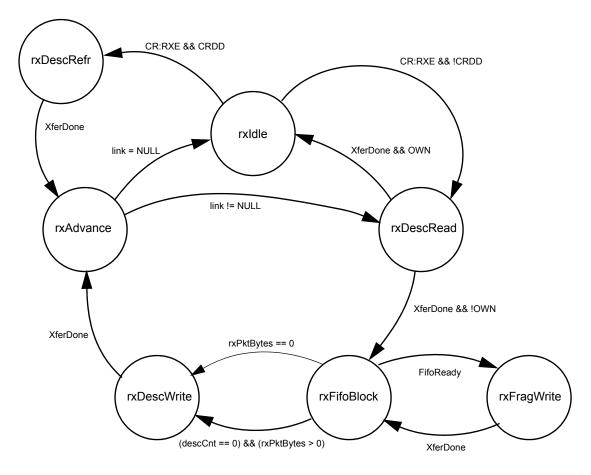

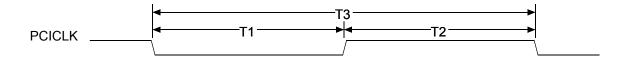

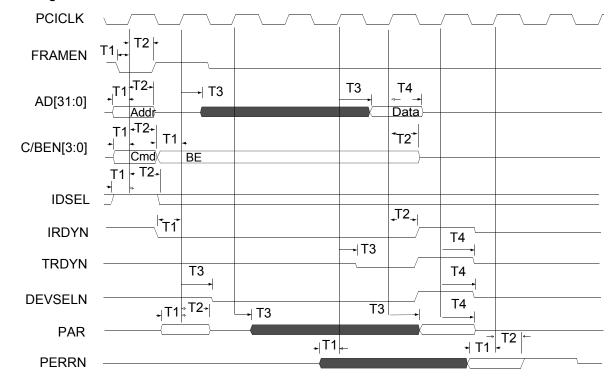

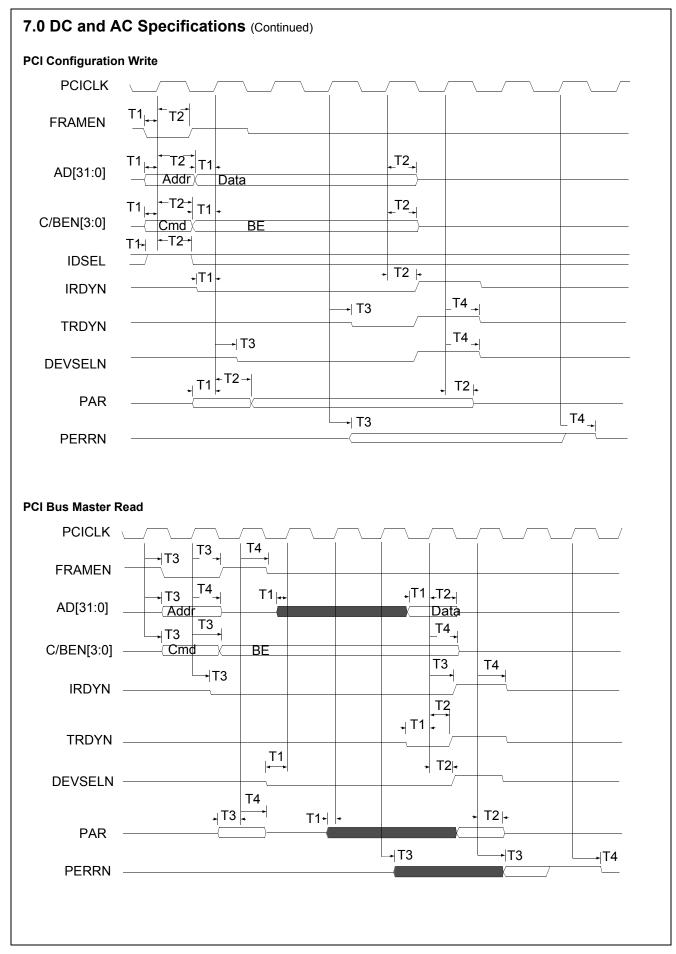

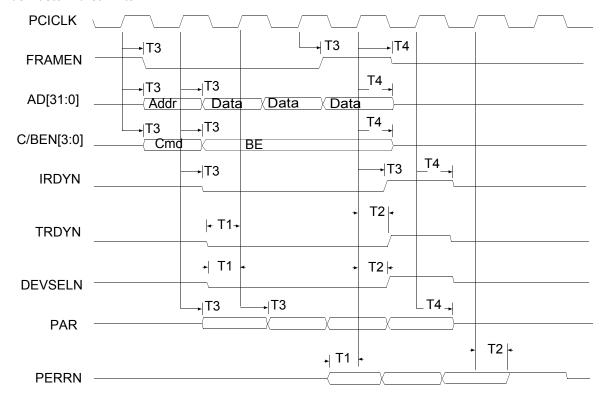

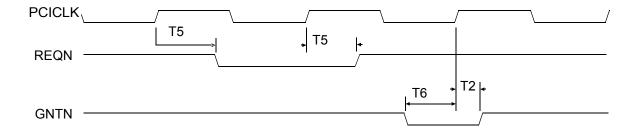

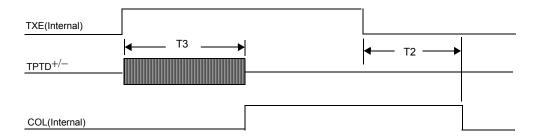

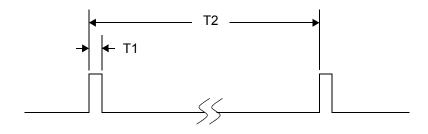

| K             | 10001             | Second Start of Packet - 0101 |  |  |  |  |