## DPS9245 High-Resolution ADC with PGA

Datasheet

LSI LOGIC

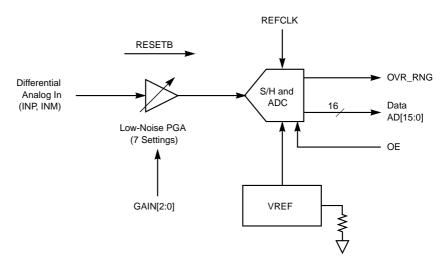

The DPS9245 is a versatile, analog front end that combines a highresolution 5 megasamples per second (MS/s) 16-bit Analog-to-Digital Converter (ADC), a built-in reference, and a Programmable Gain Amplifier (PGA) with resistive input impedance in a 44-pin package.

#### Figure 1 DPS9245 Block Diagram

The chip includes a digitally-calibrated, pipeline ADC that is calibrated upon assertion of a simple reset signal. The combination of a low-noise, high-linearity, high-input impedance buffer (with programmable gain), wideband S/H, on-board voltage references, and simple digital interface (16-bit parallel output word synchronous with the master sampling clock), makes the chip extremely easy to use in a wide variety of systems. The analog inputs should be driven differentially, and can be AC-coupled or DC-coupled to a source. Typical applications include high-performance data acquisition systems, automatic test equipment, and wideband digital communications receivers present in systems such as wireless basestations. The performance of the device with respect to linearity and noise should be considered separately, as indicated by the THD and SNR specifications provided in this document.

November 2000 Copyright © 1999, 2000 by LSI Logic Corporation. All rights reserved.

www.DataSheet4U.com

## **Features**

- 16-bit 5 MS/s ADC with on-board voltage reference, programmable gain amplifier and S/H

- Minimal external components: one precision resistor and decoupling capacitors

- 5 V peak-to-peak differential input range

- Resistive inputs > 1 kΩ easy to drive, without any switchedcapacitor kickback transient

- Low-frequency DNL: ±0.5 LSB at 16 bits

- Low-frequency INL: ±1.25 LSB at 16 bits

- Programmable gain amplifier preceding ADC with up to 20 dB of gain (7 settings: 0dB, +3dB, +6dB, +12dB, +15dB, +18dB, +20dB)

- PGA input-referred noise floor at peak gain: 8 nV/√Hz

- Higher performance upgrade from AD9260, AD9240, AD9241, or AD9243

- 5 V 5% power supply; 3.3-V supply for all digital I/O

- User-programmable power dissipation depending on sample rate and linearity required

- 230 mW at 2.5 MS/s

- 465 mW at 5 MS/s

- 44-pin LQFP plastic package

- Operating temperature range: -40 °C to +85 °C

### **Electrical Specifications**

Table 1 provides the electrical specifications for the DPS9245. Unless otherwise stated, the following conditions apply:

- Operating temperature range: -40 °C to +85 °C

- VDD\_ADC = VDDD\_ADC = 5.0 V

- VDD\_ADIO = 3.3 V

- 5.0 MS/s

- REXT = 1.43 kW

### Table 1 Electrical Specifications

| Parameter                                 | Min  | Тур         | Max  | Units            | Notes/Conditions                                                   |

|-------------------------------------------|------|-------------|------|------------------|--------------------------------------------------------------------|

| Resolution                                | 15.9 | _           | _    | bits             | See "Digital Code Range and<br>Out-of-Range Detection,"<br>page 17 |

| Maximum conversion rate                   | 5.0  | _           | -    | MS/s             |                                                                    |

| Power Supplies                            |      |             |      |                  | 1                                                                  |

| VDD_ADC, VDDD_ADC <sup>1</sup>            | 4.75 | 5.0         | 5.25 | V                |                                                                    |

| VDD_ADIO <sup>1</sup>                     | 3.0  | 3.3         | 5.25 | V                | Supply for the ADC digital outputs                                 |

| VDD_ADC, VDDD_ADC combined supply current | -    | 93          | 103  | mA               | With REXT = 1.43 k $\Omega$                                        |

| PGA Specifications <sup>2</sup>           |      |             |      |                  |                                                                    |

| Input-referred noise floor                | -    | 45.0<br>8.0 | -    | nV/√Hz<br>nV/√Hz | PGA gain = 0dB<br>PGA gain = 20dB<br>At frequencies > 300 kHz      |

| PGA gain                                  |      | 0.0         | _    | dB               | GAIN[2:0] = 000                                                    |

|                                           | _    | 2.9         | _    | dB               | GAIN[2:0] = 001                                                    |

|                                           | _    | 5.8         | -    | dB               | GAIN[2:0] = 010                                                    |

|                                           | _    | 11.8        | -    | dB               | GAIN[2:0] = 011                                                    |

|                                           | _    | 14.8        | -    | dB               | GAIN[2:0] = 100                                                    |

|                                           | _    | 17.5        | _    | dB               | GAIN[2:0] = 101                                                    |

|                                           | -    | 19.5        | -    | dB               | GAIN[2:0] = 110                                                    |

| PGA gain accuracy                         | -0.3 | 0           | +0.3 | dB               |                                                                    |

| Input resistance <sup>1</sup>             | 1    | -           | -    | kΩ               | On pins INP, INM                                                   |

| Input capacitance <sup>1</sup>            | _    | _           | 15   | pF               | On pins INP, INM                                                   |

#### Table 1 Electrical Specifications (Cont.)

| Parameter                                 | Min                             | Тур   | Max   | Units | Notes/Conditions                                                                                                                                                                                                                                                                    |  |  |  |

|-------------------------------------------|---------------------------------|-------|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| DC Specifications                         |                                 |       |       |       |                                                                                                                                                                                                                                                                                     |  |  |  |

| ADC differential reference                | 2.375                           | 2.5   | 2.625 | V     | Voltage between ADC_REFP<br>(pin 37) and ADC_REFM<br>(pin 36)                                                                                                                                                                                                                       |  |  |  |

| ADC positive reference                    | -                               | 3.65  | -     | V     | Voltage between ADC_REFP<br>(pin 37) and GND                                                                                                                                                                                                                                        |  |  |  |

| ADC negative reference                    | -                               | 1.15  | -     | V     | Voltage between ADC_REFM (pin 36) and GND                                                                                                                                                                                                                                           |  |  |  |

| Input common mode refer-<br>ence (RXCMIN) | 2.275                           | 2.400 | 2.525 | V     | Minimum load 50 k $\Omega$ to ground                                                                                                                                                                                                                                                |  |  |  |

| Gain Accuracy Specificati                 | ons                             |       |       |       |                                                                                                                                                                                                                                                                                     |  |  |  |

| Gain error                                | -7.5                            | _     | +7.5  | %FSR  | Total gain error of PGA and<br>ADC (using internal references)<br>compared to ideal quantizer<br>with perfect 5.0 V full-scale<br>range preceded by an ideal<br>PGA with gain equal to the<br>nominal values (i.e., 0 dB,<br>2.9 dB, 5.8 dB, 11.8 dB,<br>14.8 dB, 17.5 dB, 19.5 dB) |  |  |  |

| Static Linearity Specificati              | Static Linearity Specifications |       |       |       |                                                                                                                                                                                                                                                                                     |  |  |  |

| DNL                                       | _                               | ±0.5  | _     | LSB   | At 16-bit level                                                                                                                                                                                                                                                                     |  |  |  |

| INL                                       | _                               | ±1.25 | _     | LSB   | At 16-bit level                                                                                                                                                                                                                                                                     |  |  |  |

1. Not tested in production, but guaranteed by design or characterization.

In the remainder of this document, the PGA gains are often rounded to the nearest integer value. For example, the GAIN[2:0] = 110 setting is referred to as 15 dB even though its typical value is 14.8 dB.

#### Table 2 Digital I/O DC Electrical Characteristics

| Parameter                                   | Min     | Тур | Мах | Units | Notes/Conditions            |

|---------------------------------------------|---------|-----|-----|-------|-----------------------------|

| V <sub>OH</sub> (High-level output voltage) | VDD-0.5 | _   | _   | V     | At $I_{OH} = -2 \text{ mA}$ |

| V <sub>OL</sub> (Low-level output voltage)  | -       | -   | 0.5 | V     | At I <sub>OL</sub> = 2 mA   |

| I <sub>IL</sub> (Input leakage current)     | -10     | -   | +10 | μA    |                             |

| V <sub>IH</sub> (High-level input voltage)  | 2.4     | -   | -   | V     |                             |

| V <sub>IL</sub> (Low-level input voltage)   | _       | _   | 0.8 | V     |                             |

<u>Note:</u> For all digital outputs, the V<sub>OH</sub> specification of VDD-0.5V refers to the VDD\_ADIO supply (pin 6). The exception is the BUSYB output (pin 33), whose output HIGH level is referenced to the VDDD\_ADC power supply (pins 3, 4).

# Dynamic Linearity Specifications for Sinusoidal Differential Analog (SDA) Input

Table 3 provides the dynamic linearity specifications for SDA input. The conditions are:

- VDD\_ADC = VDDD\_ADC = 5.0 V

- VDD\_ADIO = 3.3 V

- REXT = 1.43 kΩ.

The following notes apply:

- The signal level relative to full-scale (dBFS) is given at the ADC input

that is, *after* the PGA in order to show the dependence on PGA gain.

- 2. 0 dBFS is 5.0V peak-to-peak differential.

- Second harmonic distortion (HD2), 3rd harmonic distortion (HD3), total harmonic distortion up to and including the 9th harmonic (THD\_9), and spurious free dynamic range (SFDR), are given in dB below the fundamental (carrier).

| Sample<br>Rate<br>[MS/s] | Signal<br>Frequency<br>[kHz] | PGA<br>Setting<br>[dB] | Composite<br>Signal<br>Level at<br>ADC Input<br>[dBFS] <sup>1</sup> | HD2         | HD3        | THD_9      | SFDR      |

|--------------------------|------------------------------|------------------------|---------------------------------------------------------------------|-------------|------------|------------|-----------|

| 5.0                      | 70                           | 0                      | -0.5                                                                | –94 dB max  | –85 dB max | -84 dB max | 85 dB min |

| 5.0                      | 70                           | 0                      | -0.5                                                                | -103 dB typ | –97 dB typ | –92 dB typ | 94 dB typ |

| 5.0                      | 70                           | 20                     | -0.5                                                                | –101 dB typ | –93 dB typ | –90 dB typ | 92 dB typ |

| 8.8                      | 60                           | 0                      | -0.5                                                                | –103 dB typ | –97 dB typ | –92 dB typ | 94 dB typ |

| 5.0                      | 900                          | 12                     | -11.0                                                               | –104 dB typ | –97 dB typ | –94 dB typ | 97 dB typ |

| 5.0                      | 900                          | 15                     | -8.1                                                                | –104 dB typ | –94 dB typ | –91 dB typ | 94 dB typ |

| 5.0                      | 900                          | 18                     | -5.4                                                                | –103 dB typ | –88 dB typ | –88 dB typ | 88 dB typ |

| 5.0                      | 900                          | 20                     | -3.4                                                                | –101 dB typ | –85 dB typ | –84 dB typ | 85 dB typ |

| 5.0                      | 900                          | 20                     | -1.1                                                                | –99 dB typ  | –84 dB typ | –82 dB typ | 84 dB typ |

#### Table 3 Dynamic Linearity Specifications for Sinusoidal Differential Analog Input

1. dBFS is dB below full scale signal level, which is 5 V peak-to-peak differential.

### **Dynamic Linearity Specifications for Two-Tone Differential Analog Input**

Table 4 provides the dynamic linearity specifications for two-tone differential analog input. The following conditions apply:

- VDD\_ADC = VDDD\_ADC = 5.0 V

- VDD\_ADIO = 3.3 V

- REXT = 1.43 kΩ

The following notes apply:

- 1. The composite signal level relative to full-scale (dBFS) is given at the ADC input that is, *after* the PGA in order to show the dependence on PGA gain.

- 2. 0 dBFS is 5.0V peak-to-peak differential.

3. Third-order and 5th-order intermodulation distortion, IM3 and IM5 respectively, are given in dB below carrier – that is, dB below one tone of the two-tone signal.

| Sample<br>Rate<br>[MS/s] | Signal<br>Frequencies | PGA<br>Setting<br>[dB] | Composite<br>Signal Level at<br>ADC Input<br>[dBFS] | IM3        | IM5         |

|--------------------------|-----------------------|------------------------|-----------------------------------------------------|------------|-------------|

| 4.4                      | 100 kHz, 110 kHz      | 6                      | -0.8                                                | –98 dB typ | –101 dB typ |

| 4.4                      | 100 kHz, 110 kHz      | 20                     | -0.3                                                | –96 dB typ | –99 dB typ  |

| 8.8                      | 100 kHz, 110 kHz      | 6                      | -1.8                                                | –97 dB typ | –97 dB typ  |

| 8.8                      | 100 kHz, 110 kHz      | 20                     | -1.3                                                | –96 dB typ | –98 dB typ  |

| 4.4                      | 400 kHz, 410 kHz      | 6                      | -0.7                                                | –94 dB typ | –95 dB typ  |

| 4.4                      | 400 kHz, 410 kHz      | 20                     | -0.2                                                | –92 dB typ | –95 dB typ  |

| 8.8                      | 400 kHz, 410 kHz      | 6                      | -1.8                                                | –93 dB typ | –96 dB typ  |

| 8.8                      | 400 kHz, 410 kHz      | 20                     | -1.3                                                | –93 dB typ | –96 dB typ  |

| 4.4                      | 890 kHz, 900 kHz      | 0                      | -1.9                                                | –89 dB typ | –97 dB typ  |

| 8.8                      | 890 kHz, 900 kHz      | 6                      | -3.0                                                | –89 dB typ | –98 dB typ  |

| 8.8                      | 890 kHz, 900 kHz      | 20                     | -1.4                                                | –87 dB typ | –94 dB typ  |

| 5.0                      | 1.03 MHz, 1.04 MHz    | 6                      | -2.4                                                | –82 dB max | –89 dB max  |

| 5.0                      | 1.03 MHz, 1.04 MHz    | 6                      | -2.4                                                | –87 dB typ | –97 dB typ  |

| 5.0                      | 1.03 MHz, 1.04 MHz    | 20                     | -0.8                                                | –84 dB typ | –95 dB typ  |

#### Table 4 Dynamic Linearity Specifications for Two-Tone Differential Analog Input

### SNR Specifications for Balanced Differential Analog Input

Table 5 provides SNR specifications for balanced differential analoginput. The following conditions apply:

- 5 MS/s

- VDD = 5.0 V

- VDD\_ADIO = 3.3 V

- REXT = 1.43 kΩ.

- <u>Note:</u> In Table 5, the signal level is given both at the PGA input (the chip input) and at the ADC input – that is, *after* the PGA – in order to show the dependence on PGA gain or input signal level.

*Extrapolated Dynamic Range (EDR)* is a measure of overall converter sensitivity. It is obtained from a plot of SNR versus signal amplitude at the chip input, extrapolated to 0 dB. EDR can also be calculated for a given scenario by adding the SNR to the amount in dB by which signal level is below full scale.

#### Table 5 SNR Specifications for Balanced Differential Analog Input

| Signal<br>Type | Signal<br>Frequency<br>[kHz} | PGA<br>Gain<br>[dB] | Composite<br>Signal Level<br>at PGA Input<br>[dBFS] | Composite<br>Signal Level<br>at ADC Input<br>[dBFS] | SNR         | Extrapolated<br>Dynamic<br>Range |

|----------------|------------------------------|---------------------|-----------------------------------------------------|-----------------------------------------------------|-------------|----------------------------------|

| Sinusoid       | 75                           | 0                   | -1                                                  | -1                                                  | 78 dB min   | 79 dB min                        |

| Sinusoid       | 75                           | 0                   | -1                                                  | -1                                                  | 81 dB typ   | 82 dB typ                        |

| Sinusoid       | 75                           | 19.5                | -20.5                                               | -1                                                  | 76 dB typ   | 96.5 dB typ                      |

| Sinusoid       | 75                           | 0                   | -59.5                                               | -59.5                                               | 25 dB typ   | 84.5 dB typ                      |

| Sinusoid       | 75                           | 19.5                | -60                                                 | -40.5                                               | 38.5 dB typ | 98.5 dB typ                      |

| Sinusoid       | 900                          | 0                   | -1                                                  | -1                                                  | 80 dB typ   | 81 dB typ                        |

| Sinusoid       | 900                          | 0                   | -40                                                 | -40                                                 | 45.5 dB typ | 85.5 dB typ                      |

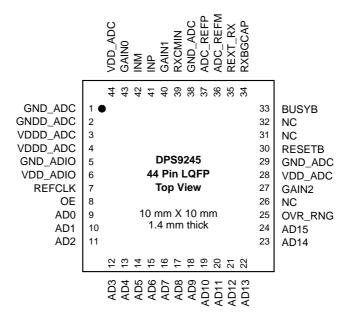

## **DPS9245** Pinouts

Figure 2 provides a pinout diagram of the DPS9245.

#### Figure 2 DPS9245 Pinout Diagram

## **Pin Descriptions**

Table 6 provides a functional definition of each signal pin listed in numerical order.

| Pin Number                          | Pin Name              | Type <sup>1</sup> | Pin Function Description                                         |

|-------------------------------------|-----------------------|-------------------|------------------------------------------------------------------|

| 1, 29, 38                           | GND_ADC               | S                 | Analog ground                                                    |

| 2                                   | GNDD_ADC              | S                 | Digital ground                                                   |

| 3,4                                 | VDDD_ADC              | S                 | Digital +5.0 V supply                                            |

| 5                                   | GND_ADIO              | S                 | Ground for digital I/O                                           |

| 6                                   | VDD_ADIO              | S                 | Power supply for ADC outputs (+3.3 V or +5 V)                    |

| 7                                   | REFCLK                | DI                | Master reference clock                                           |

| 8                                   | OE                    | DI                | Output enable (active HIGH)                                      |

| 9-24                                | AD0-AD15              | DO                | Data output bits<br>AD0 is LSB; AD15 is MSB                      |

| 25                                  | OVR_RNG               | DO                | Over range indicator bit (active HIGH)                           |

| 26                                  | NC                    |                   | No connect                                                       |

| 27, 40, 43,                         | GAIN[2:0]             | DI                | 3-bit PGA gain control                                           |

| 28, 44                              | VDD_ADC               | S                 | Analog +5.0 V supply                                             |

| 30                                  | RESETB                | DI                | Resets internal state of chip (active LOW)                       |

| 31, 32                              | NC                    |                   | No connects                                                      |

| 33                                  | BUSYB                 | DO                | Initialization in progress indicator (active LOW)                |

| 34                                  | RXBGCAP               | AO                | External bias capacitor connection                               |

| 35                                  | REXT_RX               | AO                | External bias resistor connection                                |

| 36, 37                              | ADC_REFM,<br>ADC_REFP | AO                | ADC reference voltage outputs                                    |

| 39                                  | RXCMIN                | AO                | Common-mode reference voltage output                             |

| 41, 42                              | INP, INM              | AI                | Analog inputs to the ADC                                         |

| AI = analog inputDAIO = analog I/OD |                       |                   | jital input<br>ligital I/O<br>igital output<br>oply (VDD or GND) |

#### Table 6Pin Signal Functions

## **IC Operation and Functionality**

The following sections describe in greater detail the individual blocks and functions of the DPS9245:

- Overview

- Chip Startup/Initialization Sequence

- Analog Input Interfacing

- External Connections

- ADC Digital Output Timing

- ADC References

- Other ADC Functions

- Programmable Gain Amplifier

#### **Overview**

The incoming analog differential signal (maximum level 5 V peak-to-peak differential) enters the chip at the INP/INM pins. The analog signal path is partitioned into a programmable gain amplifier (PGA) and an ADC. The PGA has maximum gain of +20 dB; the gain is set by the digital control signals GAIN[2:0]. The output of the PGA is fed directly to the ADC, which samples at a rate equal to the REFCLK frequency and outputs a 16-bit wide parallel word.

The ADC uses a pipeline multistage architecture. Latency is 6 clock cycles.

The chip requires a single low-jitter clock to be applied at the REFCLK pin, with nominal 50% duty cycle. All clock generation is performed internally and all converter and S/H clocks in the ADC path are directly derived from REFCLK.

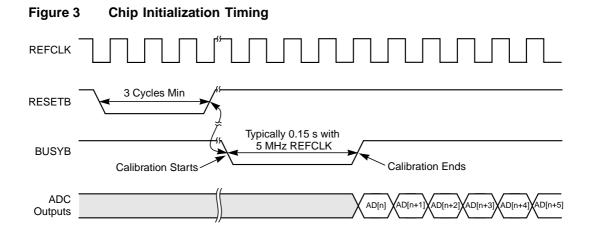

#### Chip Startup/Initialization Sequence

<u>Warning:</u> This initialization sequence is *required*. Without it, the chip will not work.

Note that the analog blocks on the chip require significant time to power on and come up to their quiescent dc states; for example, the voltage reference power-on time depends on the value of the external reference decoupling capacitance. Allowance may also be needed for thermal time constants associated with the package/board.

On power-up, RESETB should be held LOW for at least three cycles of the clock signal, REFCLK, as shown in Figure 3 below. The power supply voltages applied to the chip must be stable during this time. REFCLK must be running for at least three clock cycles prior to the rising edge of RESETB, and must continue running.

The initialization phase begins on the rising edge of RESETB. No more than two full REFCLK cycles after the rising edge of RESETB, BUSYB, an active LOW signal (pin 33), is driven LOW. An internal sequencer performs the ADC calibration while BUSYB is LOW. When the initialization is complete, BUSYB is driven HIGH and the chip is ready for normal operation. The duration of the initialization phase, (the time BUSYB is LOW) is 150 ms, assuming a 5 MS/s sampling rate.

Notes:

- The digital output BUSYB cannot be 3-stated: it is always driven either HIGH or LOW.

- The REFCLK clock must be constantly running throughout the initialization phase until BUSYB goes HIGH.

- Initialization will restart whenever RESETB is cycled; thus, for initialization to complete correctly, RESETB should not be cycled while BUSYB is LOW.

- Although typically the chip is initialized when power is first applied, the initialization only occurs when the RESETB is cycled. There is no "power-on-reset" circuitry on the chip.

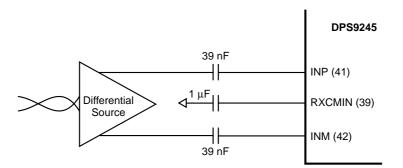

#### **Analog Input Interfacing**

The differential analog inputs (INP, INM) have a resistive input impedance of  $1 k\Omega$  minimum. For best performance, the input source should be capacitively coupled into the chip, as shown below in Figure 4. To avoid clipping, signal swing at the inputs should not exceed 5 V peak-to-peak differential (2.5 V peak-to-peak single ended). The chip provides its own common-mode voltage (on the pin marked RXCMIN), and the input common mode is established internally.

# Figure 4 Recommended Analog Input Interface – Using An AC-Coupling Approach

Alternatively, the inputs may be dc-coupled by using an external network to reference the input common mode to the voltage on pin RXCMIN.

Output drive capability of RXCMIN is a maximum of 47  $\mu$ A (50 k $\Omega$  to ground). Output impedance of the RXCMIN voltage reference is typically 1 k $\Omega$ , and hence the 1  $\mu$ F decoupling capacitor should always be present, as shown in Figure 4.

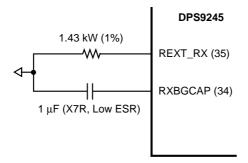

#### **External Connections**

The connections to the two pins {REXT\_RX, RXBGCAP} are critical and should be routed very carefully on the board. The connections are as shown in Figure 5 below. The traces to/from these pins should be as short as possible.

#### Figure 5 Recommended Connection for Pins 34–35

#### **External Resistor (REXT)**

REXT, shown in Figure 5 above, sets the power dissipation of the chip and may be used to trade off power dissipation against linearity at high sample rates, and/or at high input frequencies. Nominally, at 5 MS/s, REXT=1.43 k $\Omega$  is recommended. If linearity for large signal levels at an analog bandwidth of 2 MHz is critical, the value should be decreased to REXT=1.24 k $\Omega$ ; and for even higher-frequency analog inputs, REXT=1.0 k $\Omega$  can be used. At lower sample rates (for example 2 MS/s), and lower analog input frequencies, the value may be increased to REXT=2 k $\Omega$ . The section, "Typical Performance Characteristics" (on page 18) contains performance characteristics that show how dynamic linearity depends on the REXT value. As a general guideline, REXT should always be in the range 800  $\Omega$  to 2.5 k $\Omega$ . Contact LSI Logic for the most up-to-date recommended values for a given application.

#### **External Capacitor (CEXT)**

CEXT is used only for noise filtering of an internal voltage associated with the references. Its value is not critical. 1  $\mu$ F is recommended.

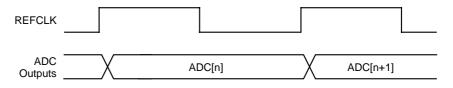

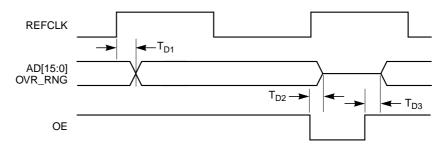

#### ADC Digital Output Timing

The chip implements a simple interface: the 16 ADC outputs appear on the pins AD[15:0] as a parallel word synchronous with the ADC sampling clock. AD0 is the LSB and AD15 is the MSB. The timing diagram for the ADC digital outputs is shown in Figure 6. The ADC sampling clock is at the same frequency as REFCLK.

#### Figure 6 Waveform for ADC Outputs

The data changes on the rising edge of REFCLK and can be latched by a DSP on the falling edge. The latency through the ADC from the PGA output to the digital outputs is 6 clock cycles of the ADC clock. The voltage levels on the AD[15:0] lines are CMOS levels. The HIGH level is determined by the power supply voltage on the VDD\_ADIO pin, which can be set independently of the other supply pins on the chip over the range from 3.0 V to 5.25 V. Typically, VDD\_ADIO should be +3.3 V, which ensures that the ADC outputs are both TTL-compatible and 3.3 V-CMOS compatible.

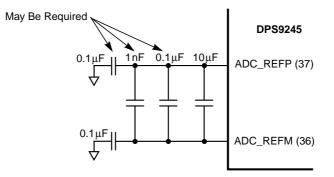

#### **ADC References**

The ADC full scale range is set by reference voltages generated on chip. These two reference voltages appear on pins ADC\_REFP and ADC\_REFM; nominally their difference is 2.5 V. The references are not designed to be overdriven. The ADC\_REFP and ADC\_REFM pins should be very carefully decoupled on the board using a 10  $\mu$ F low-ESR capacitor and as short a trace as possible. Some optimization of the decoupling may be required, as shown in Figure 7.

# Figure 7 Recommended Decoupling of ADC\_REFP and ADC\_REFM Pins

#### **Other ADC Functions**

#### **Output Enable**

The ADC digital outputs are enabled by the active HIGH output enable pin (OE).

OE = 1, ADC digital outputs AD[15:0] are enabled

OE = 0, ADC digital outputs AD[15:0] are high-impedance (3-stated)

#### **Output Format**

The output format of the ADC digital data is offset binary. Therefore, for the nominal differential range of 5 V peak-to-peak differential, the following values apply:

| Output | Corresponds to      |

|--------|---------------------|

| 0000H  | -2.5 V differential |

| 8000H  | 0 V differential    |

| FFFFH  | +2.5 V differential |

#### Digital Code Range and Out-of-Range Detection

Due to the calibration algorithm used, there is a slight loss in digital code range from the ADC. So, instead of FFFFH and 0000H at the extremes of the range, the actual maximum and minimum codes are less than that by a few percentage points, and vary from chip to chip. Effectively, this is a loss in dynamic range of a few tenths of a dB, and is negligible in many applications. The out-of-range function is defined accordingly, and sets the state of the active HIGH digital output, OVR\_RNG, as follows:

OVR\_RNG is HIGH if the ADC digital code is greater-than-or-equal-to FC00H or less-than-or-equal-to 03FFH.

#### **Programmable Gain Amplifier**

From the block diagram in Figure 1, there is a programmable gain amplifier (PGA), that precedes the ADC inputs. The differential inputs, which are resistive, are at pins INP and INM. The maximum input range is 5V peak-to-peak differential (2.5 V peak-to-peak single ended). To achieve maximum overall system noise performance, the source driving these inputs needs to be as low-noise as possible, while maintaining the required distortion performance.

The internal 0 dB analog signal level and ADC full-scale reference level is 5 V peak-to-peak differential (2.5 V peak-to-peak single ended). Thus, if the ADC input level does not exceed 5 V peak-to-peak differential, the PGA may be used to provide gain.

The gain of the PGA can be programmed using a three bit control, available at pins GAIN[2:0]. Table 7 provides a gain chart.

**Important:** The GAIN[2:0] = 111 setting is not allowed. Note that the input resistance is a function of the gain setting.

| GAIN2 | GAIN1 | GAIN0 | Nominal PGA<br>Gain [dB] | Input<br>Resistance<br>[kΩ] | Comments  |

|-------|-------|-------|--------------------------|-----------------------------|-----------|

| 0     | 0     | 0     | 0                        | 5.57                        | Min. gain |

| 0     | 0     | 1     | 3                        | 4.65                        |           |

| 0     | 1     | 0     | 6                        | 3.97                        |           |

| 0     | 1     | 1     | 12                       | 2.23                        |           |

| 1     | 0     | 0     | 15                       | 1.66                        |           |

| 1     | 0     | 1     | 18                       | 1.25                        |           |

| 1     | 1     | 0     | 20                       | 1.00                        | Max. gain |

| 1     | 1     | 1     | _                        | _                           | Forbidden |

Table 7PGA Gain Control

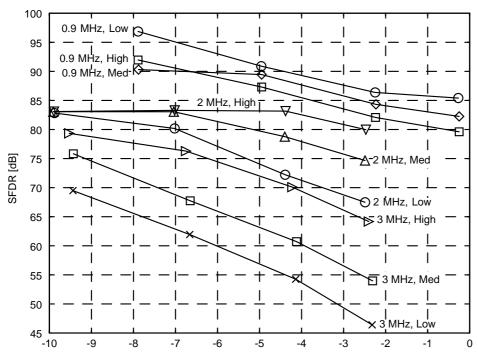

## **Typical Performance Characteristics**

Figure 8 shows the Spurious Free Dynamic Range (SFDR), in dB below the carrier, plotted as a function of ADC input amplitude, (post-PGA), in dB below full scale, at 5 V and 25 °C. *The ADC sample rate is 10 MS/s throughout.* The data is given for sinusoidal inputs at 3 frequencies: 0.9 MHz, 2 MHz, and 3 MHz. For each frequency, the SFDR is given for 3 bias conditions: (i) low, using REXT = 1.43 k $\Omega$ ; (ii) medium, using REXT = 1.24 k $\Omega$ , and (iii) high, using REXT = 1 k $\Omega$ . The corresponding chip power supply currents for these three bias conditions are 96 mA, 109 mA, and 129 mA, respectively. Note that 0 dBFS corresponds to 5.0 V peak-to-peak differential.

Figure 8 Spurious Free Dynamic Range (SFDR)

Composite Level at ADC Input [dBFS]

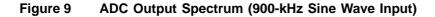

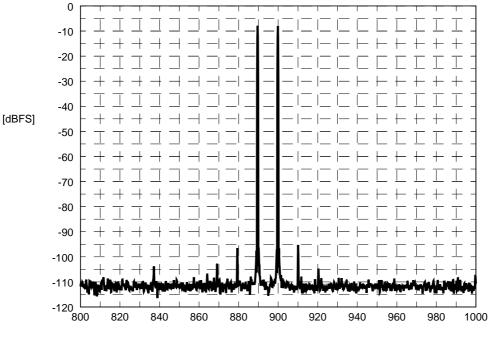

Figure 9 shows the ADC output spectrum for a 900 kHz sine wave input, at 25 °C. The sample rate is 10 MS/s; signal level at ADC input is –5.0 dBFS (i.e., post PGA); REXT = 1.43 k $\Omega$ ; the PGA is set to 15 dB. The spectrum is generated by averaging multiple FFTs in order to indicate clearly the distortion harmonics.

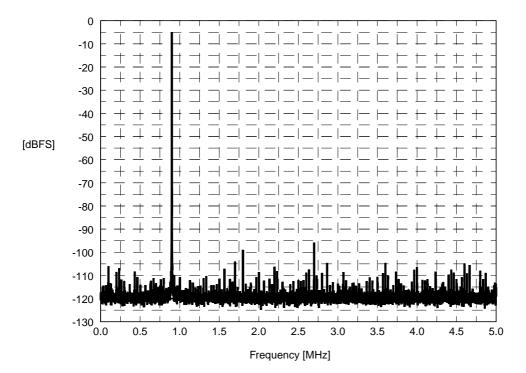

Figure 10 shows the ADC output spectrum for a 2 MHz sine wave input, at 25 °C. The sample rate is 4.4 MS/s; signal level at ADC input is –5.4 dBFS (i.e., post PGA); REXT = 1.08 k $\Omega$ ; the PGA is set to 18 dB. The spectrum is generated by averaging multiple FFTs in order to indicate clearly the distortion harmonics.

DPS9245 High-Resolution ADC with PGA

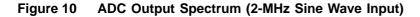

Figure 11 shows a zoomed-in portion of the ADC output spectrum for a 890 kHz/900 kHz two-tone input, at 25 °C. The sample rate is 4.4 MS/s; at the ADC input (i.e., post PGA) the signal level of each tone is -8.0 dBFS and the composite signal level is -2.0 dBFS; REXT = 1.43 k $\Omega$ ; the PGA is set to 6 dB. The spectrum is generated by averaging multiple FFTs in order to indicate clearly the intermodulation distortion products.

Figure 11 Zoomed-in Portion of ADC Output Spectrum (890/900 kHz Two-Tone Input)

Frequency [kHz]

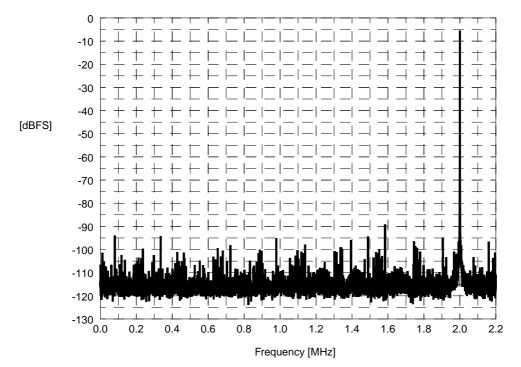

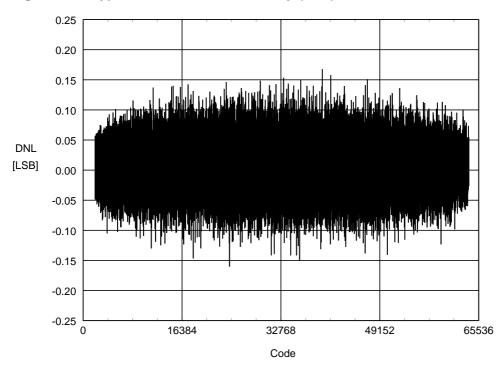

Figure 12 shows the typical Differential Nonlinearity (DNL), at the 16-bit level, measured using a histogram test with a near-full-scale 75 kHz sinusoid input, at 25  $^{\circ}$ C. The sample rate is 4.4 MS/s, and the PGA is set to 0 dB.

Figure 12 Typical Differential Nonlinearity (DNL) – 16-Bit Level

## **Timing Specifications**

Figure 13 and Table 8 provide timing specifications for the various digital interfaces on the chip.

#### Figure 13 ADC Timing

#### Table 8 ADC Timing

| Parameter                 | Symbol          | Min | Тур | Max             | Units |

|---------------------------|-----------------|-----|-----|-----------------|-------|

| REFCLK HIGH to Data Valid | T <sub>D1</sub> | 18  | 24  | 40 <sup>1</sup> | ns    |

| OE inactive to HiZ        | T <sub>D2</sub> | 10  | 16  | 30              | ns    |

| OE active to Data Valid   | T <sub>D3</sub> | 10  | 16  | 30              | ns    |

1. Conditions: load capacitance = 20 pF, VOH = 3.3 V

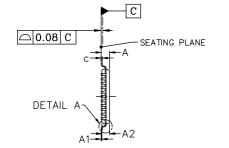

## **Package Drawing**

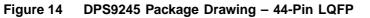

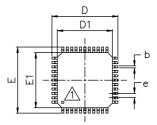

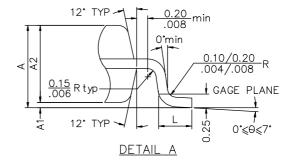

Figure 14 provides the DPS9245 package drawing.

|        | м     | ILLIMETE | ĒR    | INCH       |      |      |  |

|--------|-------|----------|-------|------------|------|------|--|

| SYMBOL | MIN   | NOM      | MAX   | MIN        | NOM  | MAX  |  |

| Α      | 1.40  | 1.50     | 1.60  | .055       | .059 | .063 |  |

| A1     | 0.05  | 0.10     | 0.15  | .002       | .004 | .006 |  |

| A2     | 1.35  | 1.40     | 1.45  | .053       | .055 | .057 |  |

| D      | 11.80 | 12.00    | 12.20 | .465       | .472 | .480 |  |

| D1     | 9.90  | 10.00    | 10.10 | .390       | .394 | .398 |  |

| E      | 11.80 | 12.00    | 12.20 | .465       | .472 | .480 |  |

| E1     | 9.90  | 10.00    | 10.10 | .390       | .394 | .398 |  |

| L      | 0.45  | 0.60     | 0.75  | .018       | .024 | .030 |  |

| е      | 0.8   | 80 BS    | C.    | .0315 BSC. |      |      |  |

| b      | 0.30  | 0.37     | 0.45  | .012       | .015 | .018 |  |

| с      | 0.13  | 0.16     | 0.20  | .005       | .006 | .008 |  |

NOTE: A PIN 1 INDICATOR.

- 2. REFER TO JEDEC MS-026 BCB FOR DATUMS, FEATURES AND DIMENSIONS NOT SHOWN.

- 3. CONTROLLING DIMENSION IN MM.

## Notes

#### Sales Offices and Design Resource Centers

LSI Logic Corporation Corporate Headquarters Tel: 408.433.8000 Fax: 408.433.8989

#### NORTH AMERICA

California Irvine ♦ Tel: 949.809.4600 Fax: 949.809.4444

> Pleasanton Design Center Tel: 925.730.8800 Fax: 925.730.8700

San Diego Tel: 858.467.6981 Fax: 858.496.0548

Silicon Valley ◆ Tel: 408.433.8000 Fax: 408.954.3353

Wireless Design Center Tel: 858.350.5560 Fax: 858.350.0171

Colorado Boulder ♦ Tel: 303.447.3800 Fax: 303.541.0641

Colorado Springs Tel: 719.533.7000 Fax: 719.533.7020

Fort Collins Tel: 970.223.5100 Fax: 970.206.5549

Florida Boca Raton Tel: 561.989.3236

Fax: 561.989.3237 Georgia

Alpharetta Tel: 770.753.6146 Fax: 770.753.6147 Illinois Oakbrook Terrace Tel: 630.954.2234 Fax: 630.954.2235

**Kentucky** Bowling Green Tel: 270.793.0010 Fax: 270.793.0040

Maryland Bethesda Tel: 301.897.5800 Fax: 301.897.8389

Massachusetts Waltham ♦ Tel: 781.890.0180 Fax: 781.890.6158

Burlington - Mint Technology Tel: 781.685.3800 Fax: 781.685.3801

Minneapolis ♦ Tel: 612.921.8300 Fax: 612.921.8399

New Jersey Red Bank Tel: 732.933.2656 Fax: 732.933.2643

Cherry Hill - Mint Technology Tel: 856.489.5530 Fax: 856.489.5531

New York Fairport Tel: 716.218.0020 Fax: 716.218.9010

North Carolina Raleigh Tel: 919.785.4520 Fax: 919.783.8909

Oregon Beaverton Tel: 503.645.0589 Fax: 503.645.6612 **Texas** Austin Tel: 512.388.7294 Fax: 512.388.4171

Plano ◆ Tel: 972.244.5000 Fax: 972.244.5001

> Houston Tel: 281.379.7800 Fax: 281.379.7818

Canada Ontario Ottawa ♦ Tel: 613.592.1263 Fax: 613.592.3253

#### INTERNATIONAL

France Paris LSI Logic S.A. Immeuble Europa ♦ Tel: 33.1.34.63.13.13

Fax: 33.1.34.63.13.19

Germany Munich LSI Logic GmbH ♦ Tel: 49.89.4.58.33.0

Fax: 49.89.4.58.33.0

Stuttgart ♦ Tel: 49.711.13.96.90 Fax: 49.711.86.61.428

Italy Milan LSI Logic S.P.A.

♦ Tel: 39.039.687371 Fax: 39.039.6057867

Japan Tokyo LSI Logic K.K. ♦ Tel: 81.3.5463.7821 Fax: 81.3.5463.7820

Osaka ♦ Tel: 81.6.947.5281 Fax: 81.6.947.5287 Korea Seoul LSI Logic Corporation of Korea Ltd Tel: 82.2.528.3400 Fax: 82.2.528.2250

The Netherlands Eindhoven LSI Logic Europe Ltd Tel: 31.40.265.3580 Fax: 31.40.296.2109

Singapore Singapore LSI Logic Pte Ltd Tel: 65.334.9061 Fax: 65.334.4749

Sweden Stockholm LSI Logic AB ♦ Tel: 46.8.444.15.00 Fax: 46.8.750.66.47

Taiwan Taipei LSI Logic Asia, Inc. Taiwan Branch Tel: 886.2.2718.7828 Fax: 886.2.2718.8869

United Kingdom Bracknell LSI Logic Europe Ltd ◆ Tel: 44.1344.426544

Fax: 44.1344.426544

Sales Offices with Design Resource Centers

To receive product literature, visit us at http://www.lsilogic.com

RM Printed in USA Order No. R15009 Doc. No. DB08-000152-00

The LSI Logic logo design is a registered trademark of LSI Logic Corporation. All other brand and product names may be trademarks of their respective companies.

ISO 9000 Certified

LSI Logic Corporation reserves the right to make changes to any products and services herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase, lease, or use of a product or service from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or of third parties.