Sample &

Buv

SLVSCU7A - FEBRUARY 2016 - REVISED MARCH 2016

## DRV10970 Three-Phase Brushless DC Motor Driver

Technical

Documents

## 1 Features

- Wide Power Supply Voltage Range: 5 to 18 V

- Integrated FETs: 1-A RMS, 1.5-A Peak Output Phase/Winding Current

- Total Driver H + L R<sub>DSON</sub>: 400 mΩ

- Embedded 180° Sine-Wave and Trapezoidal Commutations

- Ultra-Low Power Consumption in Sleep Mode (35 µA)

- Adaptive Drive Angle Adjustment

- Three or Single Hall Sensor Option to Minimize

System Cost

- Motor Spin Direction Control

- Configurable for 30° Hall Placement or 0° Hall Placement

- Adjustable Retry Timing after Motor Lock

- Programmable Current-Limit Function

- Tachometer Motor Speed Information on Open-Drain FG Pin

- Motor Lock Report on Open-Drain RD Pin

- Protection Features

- Supply (VM) Undervoltage Lockout

- Cycle-by-Cycle Current Limit

- Overcurrent Protection (OCP)

- Thermal Shutdown

- Motor Lock Detect and Report

## 2 Applications

- Cooling Fans

- Small Appliances

- General-Purpose BLDC Motor Driver

## 3 Description

Tools &

Software

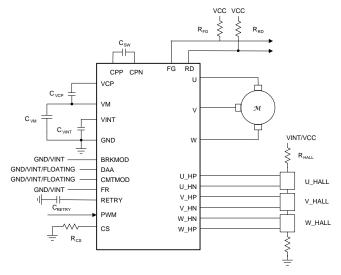

The DRV10970 is an integrated three-phase BLDC motor driver for home appliance, cooling fans, and other general-purpose motor control applications. The embedded intelligence, small form factor, and simple pinout structure reduce the design complexity, board space, and system cost. The integrated protections improve the system robustness and reliability.

Support &

Community

20

The output stage of DRV10970 consists of three halfbridges with R<sub>DSON</sub> of 400 m $\Omega$  (H + L). Each halfbridge is capable of driving up to 1-A RMS and 1.5-A peak output current. When the device enters sleep mode, it consumes typical 35  $\mu$ A of current.

The advanced 180° sine-wave commutation algorithm is embedded into the device and achieves high efficiency, low torque ripple, and superior acoustic performance. The adaptive driving angle adjustment function achieves the most optimized efficiency regardless of the motor parameters and load conditions.

The DRV10970 is designed for either differential or single-ended Hall sensor based applications. The differential Hall signal inputs are detected by the integrated comparators. The device supports three Hall and single Hall based applications; the single Hall sensor mode reduces the system cost by eliminating two Hall sensors.

#### **Device Information**<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |

|-------------|------------|-------------------|

| DRV10970    | TSSOP (24) | 7.80 mm × 6.40 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

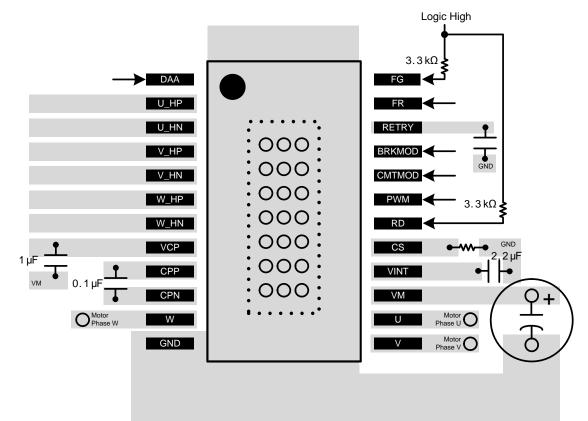

#### **Application Circuit**

## **Table of Contents**

| Feat | tures 1                            |    |

|------|------------------------------------|----|

| Арр  | lications 1                        |    |

|      | cription1                          | 9  |

| Rev  | ision History 2                    |    |

| Des  | cription (continued) 3             |    |

|      | Configuration and Functions        | 10 |

| Spe  | cifications                        | 11 |

| 7.1  | Absolute Maximum Ratings 5         |    |

| 7.2  | ESD Ratings 5                      |    |

| 7.3  | Recommended Operating Conditions 5 | 12 |

| 7.4  | Thermal Information 6              |    |

| 7.5  | Electrical Characteristics 6       |    |

| 7.6  | Typical Characteristics 9          |    |

| Deta | ailed Description 11               |    |

| 8.1  | Overview                           | 13 |

| 8.2  | Functional Block Diagram 12        |    |

|   | 8.3  | Feature Description 1             | 3 |

|---|------|-----------------------------------|---|

|   | 8.4  | Device Functional Modes1          | 6 |

| ) | Арр  | lication and Implementation2      | 1 |

|   | 9.1  | Application Information 2         | 1 |

|   | 9.2  | Typical Application 2             | 8 |

| 0 | Pov  | ver Supply Recommendations        | 0 |

| 1 | Lay  | out                               | 0 |

|   | 11.1 | Layout Guidelines3                | 0 |

|   | 11.2 | Layout Example 3                  | 0 |

| 2 | Dev  | ice and Documentation Support     | 1 |

|   | 12.1 | Community Resources               | 1 |

|   | 12.2 | Trademarks 3                      | 1 |

|   | 12.3 | Electrostatic Discharge Caution 3 | 1 |

|   | 12.4 | Glossary                          | 1 |

| 3 | Mec  | hanical, Packaging, and Orderable |   |

|   | Info | rmation 3                         | 2 |

|   |      |                                   |   |

## 4 Revision History

1 2

3

4

5

6

7

8

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Original (February 2016) to Revision A

www.ti.com

Page

## **5** Description (continued)

The device implements a standard control interface which includes PWM input (speed command), FG output (speed feedback), FR input (forward and reverse direction control), and RD output (motor lock indicator).

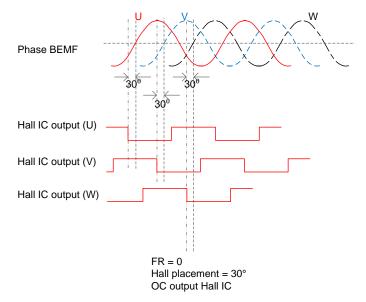

The DRV10970 device supports both 30° and 0° Hall placements (with respect to the corresponding phase BEMF). The device implements trapezoidal drive mode to address higher power requirement.

The DRV10970 device determines the rotor lock condition based on the absence of Hall input switching. The device will try again to spin the motor after an adjustable auto-retry time which can be configured by a capacitor connected to the RETRY pin.

The device incorporates multiple protection features: overcurrent, undervoltage, overtemperature, and locked rotor conditions to improve the system robustness.

The DRV10970 is packaged in a thermally-enhanced 24-pin TSSOP package (eco-friendly: RoHS and no Sb/Br).

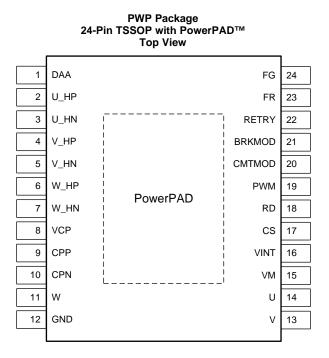

## 6 Pin Configuration and Functions

#### **Pin Functions**

| PIN       |        | ТҮРЕ |                                                 | DESCRIPTION                                                                                                                                                              |  |

|-----------|--------|------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME      | NO.    | ITPE |                                                 | DESCRIPTION                                                                                                                                                              |  |

| POWER AND | GROUND |      |                                                 |                                                                                                                                                                          |  |

| CPN       | 10     |      | Charge nump quitabing node                      | Connect a 0.1-µF X7R capacitor rated for VM between CPN                                                                                                                  |  |

| CPP       | 9      | _    | <ul> <li>Charge pump switching node</li> </ul>  | and CPP                                                                                                                                                                  |  |

| GND       | 12     | PWR  | Device ground Must be connected to board ground |                                                                                                                                                                          |  |

| VCP       | 8      | _    | Charge pump output                              | Charge pump output Connect a 16-V, 1-µF ceramic capacitor to VM                                                                                                          |  |

| VINT      | 16     | PWR  | Integrated regulator output                     | Integrated regulator (typical voltage 5 V) mainly for internal circuits; Provide external power for less than 20 mA. Bypass to GND with a 10-V, 2.2-µF ceramic capacitor |  |

| VM        | 15     | PWR  | Power supply                                    | Connect to motor supply voltage; bypass to GND with a 10- $\mu F$ ceramic capacitor rated for VM                                                                         |  |

DRV10970 SLVSCU7A-FEBRUARY 2016-REVISED MARCH 2016

www.ti.com

STRUMENTS

**EXAS**

## Pin Functions (continued)

| PII        | PIN TYPE |      |                                                 |                                                                                                                                                                                                                                             |  |

|------------|----------|------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME       | NO.      | TYPE |                                                 | DESCRIPTION                                                                                                                                                                                                                                 |  |

| CONTROL    |          |      |                                                 |                                                                                                                                                                                                                                             |  |

| CS         | 17       | _    | Current limit setting pin                       | Connect a resistor to adjust the current limit.                                                                                                                                                                                             |  |

| DAA        | 1        | I    | Drive angle adjustment configuration pin        | Low: 10° drive angle adjustment<br>High: 5° drive angle adjustment<br>Floating: adaptive drive angle adjustment                                                                                                                             |  |

| FG         | 24       | 0    | Frequency indication pin                        | Open drain Electrical Frequency Output pin. One toggle per electrical cycle. Requires an external pull-up of $3.3$ -k $\Omega$ .                                                                                                            |  |

| FR         | 23       | I    | Motor direction control                         | Direction Control Input.<br>When low, phase driving sequence is $U \rightarrow V \rightarrow W$ ( U phase is leading V phase by 120°).<br>When high, the phase driving sequence is $U \rightarrow W \rightarrow V$ .                        |  |

| BRKMOD     | 21       | I    | Brake mode setting                              | Low: Coasting mode (phases are tri-stated)<br>High: Brake mode (phases are driven low)                                                                                                                                                      |  |

| PWM        | 19       | I    | Variable duty cycle PWM input for speed control | Connect to PWM signal.                                                                                                                                                                                                                      |  |

| RD         | 18       | 0    | Lock indication pin                             | Pulled logic low with lock condition; open-drain output requires an external pull-up of 3.3-k $\!\Omega$                                                                                                                                    |  |

| RETRY      | 22       | I    | Auto retry timing configure                     | Timing adjustable by capacitor                                                                                                                                                                                                              |  |

| CMTMOD     | 20       | I    | Commutation mode setting                        | Low: Sinusoidal operation mode with 0° Hall placement<br>High: Sinusoidal operation mode with 30° Hall placement<br>Floating: Trapezoidal operation mode with 30° Hall placement                                                            |  |

| U_HN       | 3        | I    | U-phase negative Hall input                     | Differential Hall Sensor negative input for U-phase. Connect to hall sensor negative output. When logic level hall IC is used, tie this pin to VINT/2 level. In single Hall mode, the device uses U-phase hall inputs to drive the motor.   |  |

| U_HP       | 2        | I    | U-phase positive Hall input                     | Differential Hall Sensor positive input for U-phase. Connect to hall sensor positive output. When logic level hall IC is used, connect this to hall IC output. In single Hall mode, the device uses U-phase hall inputs to drive the motor. |  |

| V_HN       | 5        | I    | V-phase negative Hall input                     | Differential Hall Sensor negative input for V-phase. Connect to hall sensor negative output. When logic level hall sensor is used, tie this pin to VINT/2 level. In single hall mode, ground this pin.                                      |  |

| V_HP       | 4        | I    | V-phase positive Hall input                     | Differential Hall Sensor positive input for V-phase. Connect to hall sensor positive output. When logic level hall IC is used, connect this to hall IC output. Leave this pin floating to enable single Hall operation.                     |  |

| W_HN       | 7        | I    | W-phase negative Hall input                     | Differential Hall Sensor negative input for W-phase. Connect to hall sensor negative output. When logic level hall sensor is used, tie this pin to VINT/2 level. In single hall mode, ground this pin.                                      |  |

| W_HP       | 6        | I    | W-phase positive Hall input                     | Differential Hall Sensor positive input for W-phase. Connect to hall sensor positive output. When logic level hall IC is used, connect this to hall IC output. In single hall mode, ground this pin.                                        |  |

| OUTPUT STA | GE       |      |                                                 | ·                                                                                                                                                                                                                                           |  |

| U          | 14       | 0    | U phase output                                  | Connect to motor terminal U                                                                                                                                                                                                                 |  |

| V          | 13       | 0    | V phase output                                  | Connect to motor terminal V                                                                                                                                                                                                                 |  |

| W          | 11       | 0    | W phase output                                  | Connect to motor terminal W                                                                                                                                                                                                                 |  |

## **External Components**

| COMPONENT        | PIN 1 | PIN 2 | RECOMMENDED                                                                                                                       |

|------------------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------|

| C <sub>VM</sub>  | VM    | GND   | 10- $\mu$ F ceramic capacitor rated for VM (if VM = 12 V, 25-V capacitor is suggested, if VM = 18 V, 35-V capacitor is suggested) |

| C <sub>VCP</sub> | VCP   | VM    | 16-V, 1-µF ceramic capacitor                                                                                                      |

| C <sub>SW</sub>  | CPP   | CPN   | 0.1-µF X7R capacitor rated for VM                                                                                                 |

Copyright © 2016, Texas Instruments Incorporated

#### **External Components (continued)**

| COMPONENT          | PIN 1              | PIN 2 | RECOMMENDED                                                                           |  |

|--------------------|--------------------|-------|---------------------------------------------------------------------------------------|--|

| C <sub>VINT</sub>  | VINT               | GND   | 10-V, 2.2-µF ceramic capacitor Rotor Lock Detection and Retry                         |  |

| C <sub>RETRY</sub> | RETRY              | GND   | See Equation 2 for capacitor value                                                    |  |

| R <sub>CS</sub>    | CS                 | GND   | See Current Limit and OCP for resistor value                                          |  |

| R <sub>RD</sub>    | VCC <sup>(1)</sup> | RD    | >1 k $\Omega$ , RD is open-drain output. This component must be pulled up externally. |  |

| R <sub>FG</sub>    | VCC <sup>(1)</sup> | FG    | >1 k $\Omega$ , FG is open-drain output. This component must be pulled up externally. |  |

(1) VCC is not a pin on the DRV10970. It can be VINT or any other system voltage (for example the 3.3-V or 5-V supply voltage powering the microcontroller). A VCC supply voltage pull-up is required for open-drain outputs RD and FG

## 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1) (2)

|                                                           | MIN  | MAX        | UNIT |

|-----------------------------------------------------------|------|------------|------|

| Power supply voltage (VM)                                 | -0.3 | 20         | V    |

| Power supply voltage ramp rate (VM)                       |      | 2          | V/µs |

| Charge pump voltage (VCP, CPP)                            | -0.3 | 25         | V    |

| Charge pump negative switching pin (CPN)                  | -0.3 | 20         | V    |

| Internal logic regulator voltage (VINT)                   | -0.3 | 5.5        | V    |

| Control pin voltage (PWM, FR, RETRY, CMTMOD, BRKMOD, DAA) | -0.3 | VINT + 0.3 | V    |

| Open drain output current (RD, FG)                        | 0    | 10         | mA   |

| Open drain output voltage (RD, FG)                        | -0.3 | 20         | V    |

| Output voltage (U,V,W)                                    | -1   | 20         | V    |

| Output current (U,V,W)                                    | 0    | 2          | A    |

| Hall input voltage (U_HP, U_HN, V_HP, V_HN, W_HP, W_HN)   | 0    | 6          | V    |

| Current limit adjust pin voltage (CS)                     | -0.3 | 3.6        | V    |

| Operating junction temperature, T <sub>JMAX</sub>         | -40  | 150        | °C   |

| Storage temperature, T <sub>stg</sub>                     | -65  | 150        | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Referenced with respect to GND.

## 7.2 ESD Ratings

|  |                                            |                                                                                |       | VALUE | UNIT |

|--|--------------------------------------------|--------------------------------------------------------------------------------|-------|-------|------|

|  | V <sub>(ESD)</sub> Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | M     |      |

|  |                                            | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V     |      |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                    |                                        | MIN | MAX  | UNIT |

|------------------------------------|----------------------------------------|-----|------|------|

| Power supply voltage               | VM .                                   | 5   | 18   | V    |

|                                    | PWM, FR, CMTMOD, BRKMOD,<br>DAA, RETRY | 0   | VINT | V    |

| Open drain output pullup voltage F | FG, RD                                 | 0   | 18   | V    |

|                                    | J_HP, U_HN, V_HP, V_HN, W_HP,<br>N_HN  | 0   | 5    | V    |

| I <sub>OUT</sub> Output current    |                                        | 0   | 1.5  | А    |

## **Recommended Operating Conditions (continued)**

over operating free-air temperature range (unless otherwise noted)

|                   |                                | MIN | MAX               | UNIT |

|-------------------|--------------------------------|-----|-------------------|------|

| f <sub>PWM</sub>  | Applied PWM signal             | 15  | 100               | kHz  |

| I <sub>VINT</sub> | VINT external load current     |     | 20 <sup>(1)</sup> | mA   |

| T <sub>JOPR</sub> | Operating junction temperature | -40 | 125               | °C   |

(1) VINT is mainly for internal use. For external, it is only suggested to provide bias current for hall circuit.

## 7.4 Thermal Information

|                       |                                              | DRV10970    |      |

|-----------------------|----------------------------------------------|-------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PWP (TSSOP) | UNIT |

|                       |                                              | 24 PINS     |      |

| $R_{	extsf{	heta}JA}$ | Junction-to-ambient thermal resistance       | 36.1        | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 17.4        | °C/W |

| $R_{	extsf{	heta}JB}$ | Junction-to-board thermal resistance         | 14.8        | °C/W |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | 0.4         | °C/W |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 14.5        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.1         | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

## 7.5 Electrical Characteristics

$T_A = 25^{\circ}C$ , over recommended operating conditions unless otherwise noted.

|                         | PARAMETER                                                       | TEST CONDITIONS                        | MIN | TYP | MAX  | UNIT |

|-------------------------|-----------------------------------------------------------------|----------------------------------------|-----|-----|------|------|

| POWER SUP               | PPLIES (VM, VINT)                                               |                                        |     |     |      |      |

| VM                      | VM operating voltage                                            |                                        | 5   |     | 18   | V    |

| I <sub>VM</sub>         | VM operating supply current                                     | VM = 12 V, no external load on<br>VINT |     | 3   | 5    | mA   |

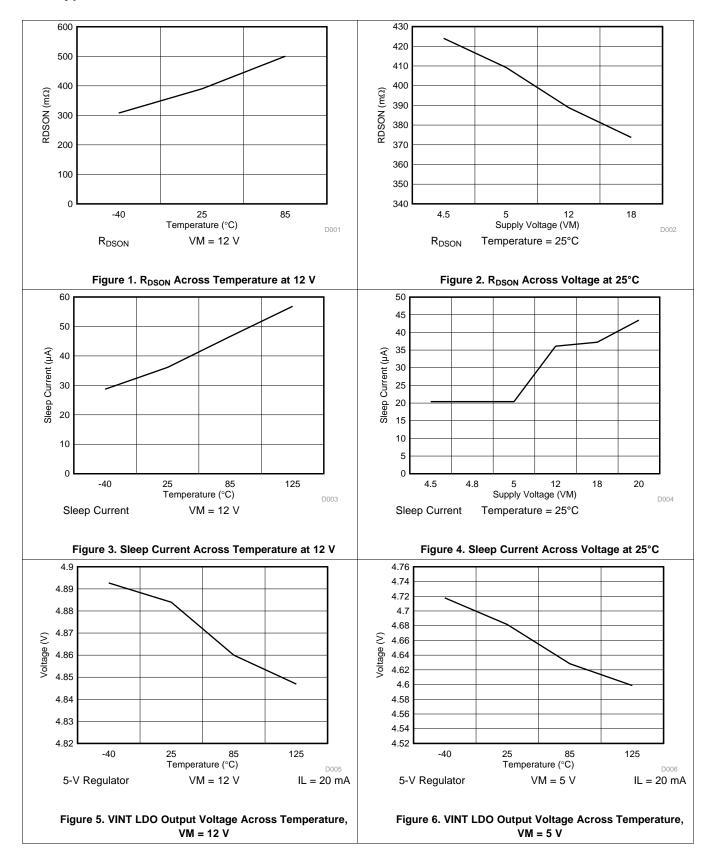

| I <sub>VM_SLEEP</sub>   | VM supply current during<br>sleep mode                          | VM = 5 and 12 V                        |     | 35  | 50   | μA   |

|                         |                                                                 | VM = 12 V, 0-mA external load          | 4.5 | 5   | 5.5  | V    |

|                         | late meterical as sulpter usite as                              | VM = 12 V, 20-mA external load         | 4.5 | 5   | 5.5  | V    |

| VINT                    | Integrated regulator voltage                                    | VM = 5 V, 0-mA external load           | 4.5 | 4.8 | 5    | V    |

|                         |                                                                 | VM = 5 V, 20-mA external load          | 4.5 | 4.8 | 5    | V    |

| V <sub>GND-BGND</sub>   | Ground potential difference<br>between GND pin to PCB<br>ground |                                        |     |     | 300  | mV   |

| CHARGE PL               | JMP (VCP, CPP, CPN)                                             |                                        |     |     |      |      |

|                         |                                                                 | VM = 5 V, less than 1-mA load          | 9   | 10  | 11   | V    |

| VCP                     | VCP operating voltage                                           | VM = 12 V, less than 1-mA load         | 16  | 18  | 19.5 | V    |

|                         |                                                                 | VM = 18 V, less than 1-mA load         | 22  | 24  | 25.5 | V    |

| CONTROL I               | NPUTS (PWM)                                                     |                                        |     |     | L    |      |

| V <sub>IL-PWM</sub>     | PWM Input logic low voltage                                     | VM = 5 V and $VM = 12 V$               | 0   |     | 0.8  | V    |

| V <sub>IH-PWM</sub>     | PWM Input logic high voltage                                    | VM = 5 V and VM = 12 V                 | 2.4 |     | 5.3  | V    |

| V <sub>HYS-PWM</sub>    | PWM Input logic hysteresis                                      | VM = 5 V and VM = 12 V                 | 400 |     |      | mV   |

| R <sub>PU-PWM</sub>     | Internal pullup resistance                                      | VM = 5 V and VM = 12 V                 | 70  | 100 | 120  | kΩ   |

| R <sub>PU-PWM-SL</sub>  | Internal pullup resistance in sleep mode                        | VM = 5 V and VM = 12 V, sleep mode     | 1   | 2   | 2.5  | MΩ   |

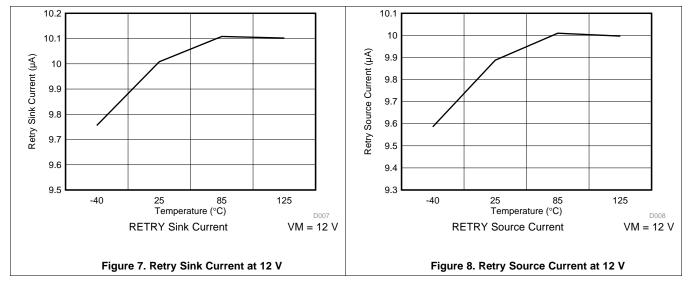

| CONTROL I               | NPUTS (RETRY)                                                   |                                        |     |     |      |      |

| I <sub>RETRY-SINK</sub> | Retry timing set sinking<br>current                             | VM = 5 V and 12 V                      | 9   | 10  | 11   | μA   |

## **Electrical Characteristics (continued)**

| $T_A = 25^{\circ}C$ , over recommended operating conditions unless otherwise note |

|-----------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------|

|                                | PARAMETER                                  | TEST CONDITIONS                                                            | MIN        | ТҮР        | MAX   | UNIT |

|--------------------------------|--------------------------------------------|----------------------------------------------------------------------------|------------|------------|-------|------|

| I <sub>RETRY-</sub><br>SOURCE  | Retry timing set sourcing<br>current       | VM = 5 V and 12 V                                                          | 9          | 10         | 11    | μA   |

| V <sub>RETRY_H</sub>           | Retry comparator high threshold            | VM = 5 V and 12 V                                                          | 1.1        | 1.2        | 1.3   | V    |

| V <sub>RETRY_L</sub>           | Retry comparator low threshold             | VM = 5 V and 12 V                                                          | 0.55       | 0.6        | 0.65  | V    |

| CONTROL IN                     | PUTS (FR, DAA, CMTMOD, BR                  | KMOD)                                                                      | -          |            |       |      |

| V <sub>IL</sub>                | Digital input logic low voltage            | VM = 5 V and 12 V                                                          | 0          |            | 0.8   | V    |

| V <sub>IH</sub>                | Digital input logic high voltage           | VM = 5 V and 12 V                                                          | 2.2        |            | 5.3   | V    |

| VIFLOATING                     | Digital input floating voltage             | VM = 5 V and 12 V                                                          | 24% × VINT | 36% × VINT |       | V    |

| R <sub>PD-FR</sub>             | FR pin Internal pulldown resistance        | VM = 5 V and 12 V                                                          | 160        | 200        | 240   | kΩ   |

| R <sub>PD-BRKMOD</sub>         | BRKMOD pin Internal<br>pulldown resistance |                                                                            |            | 240        | kΩ    |      |

| CONTROL OU                     | JTPUTS (RD, FG)                            |                                                                            |            |            |       |      |

| I <sub>OSINK</sub>             | OD output pin sink current                 | VO = 0.3 V                                                                 | 3.5        |            |       | mA   |

| IOSHORT                        | OD output pin short current limit          | VO = 12 V                                                                  |            | 10         | 25    | mA   |

| HALL INPUT                     | COMPARATOR                                 |                                                                            | •          |            |       |      |

| V <sub>HR</sub>                | Hall input rising                          | Zero to positive peak including offset. $T_A = -40^{\circ}C$ , 25°C, 125°C | 0          | 5          | 10    | mV   |

| V <sub>HF</sub>                | Hall input falling                         | Zero to negative peak including offset $T_A = -40^{\circ}$ C, 25°C, 125°C  | -10        | -5         | 0     | mV   |

| V <sub>HALL_HYS</sub>          | Hall input hysteresis                      | VHP-VHN T <sub>A</sub> = −40°C, 25°C,<br>125°C                             | 5          |            | 12    | mV   |

| N /                            | O                                          | VM = 5.5 V - 18 V                                                          | 0.3        |            | 4.3   | V    |

| Vcom                           | Common mode voltage                        | VM = 5 V - 5.5 V                                                           | 0.3        |            | 3.8   | V    |

| Finput                         | Input frequency range                      |                                                                            | 0          |            | 1000  | Hz   |

| UVLO                           |                                            |                                                                            |            |            |       |      |

| V <sub>UVLO-VM-THR</sub>       | UVLO threshold voltage on VM, rising       |                                                                            | 3.8        | 4          | 4.5   | V    |

| V <sub>UVLO-VM</sub> -THF      | UVLO threshold voltage on VM, falling      |                                                                            | 3.6        | 3.8        | 4.25  | V    |

| V <sub>UVLO-VM-HYS</sub>       | VM UVLO comparator<br>hysteresis           |                                                                            | 40         |            | 200   | mV   |

| V <sub>UVLO-VINT-</sub><br>THR | VINT UVLO rise threshold                   |                                                                            | 4.1        | 4.2        | 4.5   | V    |

| V <sub>UVLO-VINT-</sub><br>THF | VINT UVLO fall threshold                   |                                                                            | 3.8        | 4          | 4.2   | V    |

| V <sub>UVLO-VINT-</sub><br>HYS | VINT UVLO comparator<br>hysteresis         |                                                                            | 100        |            | 300   | mV   |

| INTEGRATED                     | MOSFET                                     |                                                                            |            |            |       |      |

| R <sub>DSON</sub>              | Series resistance (H + L)                  | VM = 12 V, VCP = 19 V, I <sub>OUT</sub> = 1.5 A                            |            | 0.4        | 0.6   | Ω    |

| CURRENT LI                     | MIT AND OVER CURRENT PRO                   | TECTION (OCP)                                                              |            |            | · · · |      |

| I <sub>LIM</sub>               | Current limit threshold                    | $VM = 12 V, Rcs = 20 k\Omega$                                              | 1.3        | 1.5        | 1.7   | А    |

| V <sub>ILIM_THR</sub>          | Current limit circuit comparator threshold | VM = 12 V                                                                  | 1.15       | 1.2        | 1.25  | V    |

| A <sub>CL</sub>                | Current limit attenuation factor           | VM = 12 V                                                                  | 22000      | 25000      | 28000 | A/A  |

## **Electrical Characteristics (continued)**

$T_A = 25^{\circ}C$ , over recommended operating conditions unless otherwise noted.

|                       | PARAMETER                                                                                                                          | TEST CONDITIONS                  | MIN | TYP | MAX      | UNIT |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----|-----|----------|------|

| I <sub>OCP</sub>      | Over current protection<br>threshold. Magnitude of phase<br>current at which driver stage<br>is disabled to protect the<br>device. | VM = 5 V and 12 V                | 3   |     | 5        | A    |

| SLEEP MOD             | DE TIMING                                                                                                                          |                                  |     |     |          |      |

| T <sub>SLEEP_EN</sub> | Minimum PWM low time to recognize a sleep command.                                                                                 | VM = 12 V                        | 1.2 |     |          | ms   |

| T <sub>SLEEP_EX</sub> | Minimum PWM high to exit from sleep mode.                                                                                          | VM = 12 V                        | 2   |     |          | μs   |

| THERMAL S             | SHUTDOWN                                                                                                                           |                                  |     |     |          |      |

| T <sub>SDN_TR</sub>   | Shut down temperature threshold                                                                                                    | Shut down triggering temperature | 150 | 160 | 170      | °C   |

| T <sub>SDN_RS</sub>   | Shut down resume temperature                                                                                                       | Shut down resume temperature     | 140 | 150 | 160      | °C   |

| T <sub>SDN_HYS</sub>  | Shut down temperature<br>hysteresis                                                                                                | Shut down temperature hysteresis | 5   | 10  | 15       | °C   |

| LOCK DETE             | СТ                                                                                                                                 |                                  |     |     | <u> </u> |      |

| t <sub>LOCK_EN</sub>  | Lock detect time                                                                                                                   |                                  | 0.6 | 0.7 | 0.8      | S    |

| t <sub>LOCK_EX</sub>  | Lock release time                                                                                                                  | Retry capacitor = 0.33 uF        | 4   | 5   | 6        | S    |

## 7.6 Typical Characteristics

DRV10970 SLVSCU7A-FEBRUARY 2016-REVISED MARCH 2016

www.ti.com

## **Typical Characteristics (continued)**

## 8 Detailed Description

### 8.1 Overview

The DRV10970 device controls three-phase brushless DC motors using a speed command (PWM) and direction (FR) interface and Hall signals from the motor. The device is capable of driving up to 1-A RMS and 1.5-A peak current per phase.

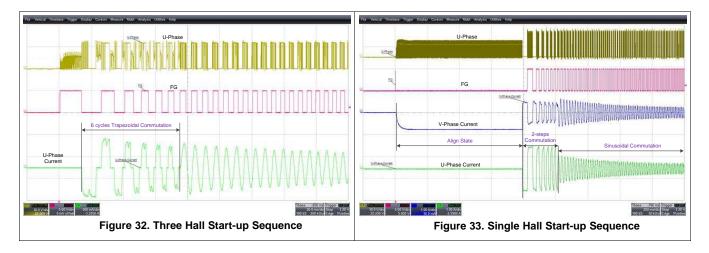

When the DRV10970 powers up, it starts to drive the motor in trapezoidal communication mode based on the Hall sensor information. If all three Hall sensors are connected, commutation logic relies on all three Hall sensors. If only the U phase Hall sensor is connected (V\_HP is floating), DRV10970 starts to drive the motor in single Hall sensor mode.

After 6 electrical cycles, the device switches to sinusoidal drive mode if the CMTMOD pin is not floating. If the motor has Hall sensor 0° placement (set on the CMTMOD pin accordingly), the DRV10970 device automatically adjusts the driving angle based on the feedback from the motor; it optimizes the efficiency regardless of the motor parameters and the load conditions.

The adaptive driving angle adjustment function can be disabled by the DAA pin, in which case, fixed driving angle is available for user to optimize the motor drive efficiency.

The steady-state motor speed is commanded by the PWM input duty cycle, which converts to an average output voltage of VM multiplied by the duty cycle. Floating PWM pin is considered as 100% speed command. Motor rotating direction can be controlled by FR input. Rotational direction can be changed while motor is spinning. The device takes  $t_{LOCK EX}$  time before reversing the direction.

The FG output is aligned with U phase Hall sensor signal which indicates the motor speed. And if the motor is locked by external force for  $t_{LOCK\_EN}$ , RD output will be asserted to indicate the rotor lock condition, and DRV10970 retries after  $t_{LOCK\_EX}$  period which is determined by the capacitor on the RETRY pin.

When the motor is stopped, either in lock condition or PWM equals zero, the state of the phases is selected by BRKMOD pin; coasting (phases are floating) or braking (phases are pulled down to GND).

DRV10970 enters sleep mode when PWM is driven low for  $t_{SLEEP}$  time and motor comes to a standstill (no FG), internal circuits including regulators are turned off and the power consumption is less than  $I_{VM SLEEP}$ .

Overcurrent, current limit, thermal shutdown and undervoltage protection circuits prevent the system components from being damaged during extreme conditions.

DRV10970 SLVSCU7A-FEBRUARY 2016-REVISED MARCH 2016 TEXAS INSTRUMENTS

www.ti.com

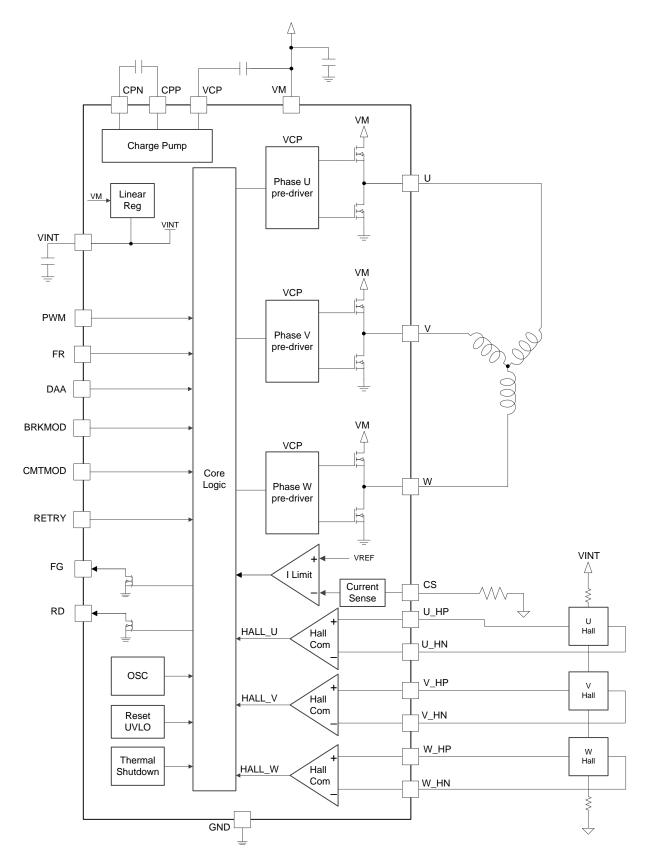

## 8.2 Functional Block Diagram

#### 8.3 Feature Description

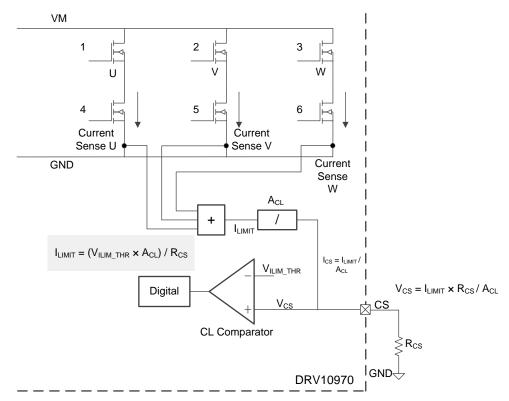

### 8.3.1 Current Limit and OCP

DRV10970 provides two stages of current control, cycle-by-cycle current limit and OCP.

The current limit function limits the motor phase current during the motor operation: during startup, acceleration, sudden load change, and rotor lock condition while spinning. The application specific threshold is achieved by choosing the value of the external resistor connected to the CS pin. Figure 9 shows the simplified circuitry of the current limit circuit using the CS pin. The voltage generated on the CS pin is proportional to the value of the external resistor value is chosen based on the current limit to be achieved (see Equation 1).

Figure 9. Current Limit Function Simplified Circuitry

Current limit threshold is set by Equation 1.

$$I_{\text{LIMIT}} = (V_{\text{ILIM}_{\text{THR}}} \times A_{\text{CL}}) / R_{\text{CS}}$$

(1)

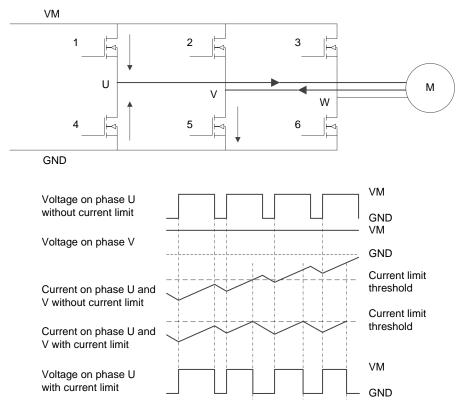

In trapezoidal operation mode, motor phase current is restricted by means of cycle-by-cycle limit, as shown in Figure 10. If the current limit is triggered, one of the conducting MOSFETs is disabled and the complementary side MOSFET is activated until the beginning of the next PWM cycle. In the example shown in Figure 10, MOSFET 1 and MOSFET 5 are conducting MOSFETs, MOSFET 1 is disabled, and the complementary MOSFET 4 is activated when the current limit is triggered.

## Feature Description (continued)

Figure 10. Cycle-by-Cycle Current Limit in Trapezoidal Mode

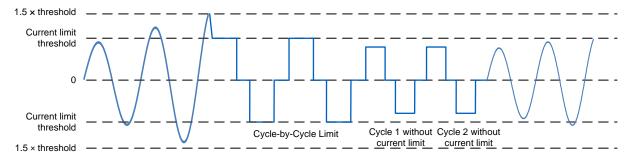

If the current limit is triggered in sinusoidal operation mode, DRV10970 device switches to trapezoidal mode of operation to exercise cycle-by-cycle current limiting. If the current limit condition does not show up for 2 electrical cycles, the device will switch back to sinusoidal mode (shown in Figure 11). The current limit threshold in sinusoidal mode is 1.5 times the current limit value in the trapezoidal mode. The current limit function can be disabled by connecting CS pin to GND.

Figure 11. Current Limit in Sinusoidal Mode

OCP has a fixed threshold  $I_{OCP}$ , it can protect the device in catastrophic short-circuit conditions such as phase short to GND, phase short to VM and phase short to another phase. The  $I_{OCP}$  limit is similar to the current limit, except that when phase current crosses  $I_{OCP}$  threshold (positively or negatively), the device shuts down all the MOSFETs immediately. The device will wait for 2 ms before it starts driving the motor again. If the high current still exists, the device will shut down the MOSFETs and again wait for 2 ms. This process of checking overcurrent will continue until the OC event goes away. The device is capable of handling an OC event continuously for its lifetime. The OC protection feature cannot be disabled.

#### Feature Description (continued)

#### 8.3.2 Thermal Shutdown

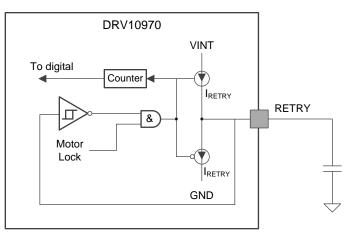

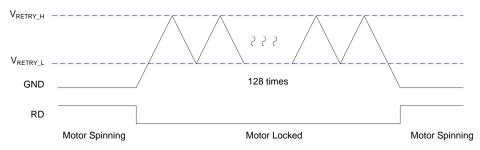

#### 8.3.3 Rotor Lock Detection and Retry

A locked rotor condition is detected if the Hall signal stops toggling for  $t_{LOCK\_EN}$ . The device enters a motor parking state: coasting (if BRKMOD = 0) or braking state (if BRKMOD = 1). In the coasting state, the device places its outputs (U, V, W) in a high-impedance state. In the braking state, it keeps the low-side MOSFETs ON and high-side MOSFETs OFF. The RD pin is asserted to indicate the rotor lock condition. Operation resumes after  $t_{LOCK\_EX}$  time at the same time RD is deasserted. This process repeats until the locked rotor condition is cleared. RD will be deasserted in sleep mode.

The  $t_{LOCK\_EX}$  time is determined by the capacitor value connected to the RETRY pin. The accuracy of the capacitor and ground potential difference between the device ground and  $C_{RETRY}$  capacitor ground affects the accuracy of the time setting. After the DRV10970 device enters rotor locked state,  $I_{RETRY}$ , sourcing current starts to charge the capacitor,  $C_{RETRY}$ , until the voltage of the capacitor reaches  $V_{RETRY\_H}$ , then  $I_{RETRY}$  sinking current starts to discharge the capacitor,  $C_{RETRY}$ , until the voltage of the capacitor falls below  $V_{RETRY\_L}$ . This process repeats 128 times which determines the  $t_{LOCK\_EX}$ , then DRV10970 retry starting the motor.

$t_{LOCK\_EX} = 15.36 \times 10^6 \times C_{RETRY}$  (in seconds)

Figure 12. Lock Release Timing Circuit

Figure 13. Lock Release Timing Waveform

### 8.3.4 Supply Undervoltage Condition (UVLO)

When the supply voltage (VM) level falls below the undervoltage lockout threshold voltage ( $V_{UVLO-Th-f}$ ), the DRV10970 will keep phases (U, V, W) in high-impedance mode. Operation resumes when VM rises above the  $V_{UVLO-Th-r}$  threshold.

Copyright © 2016, Texas Instruments Incorporated

Submit Documentation Feedback 15

### Feature Description (continued)

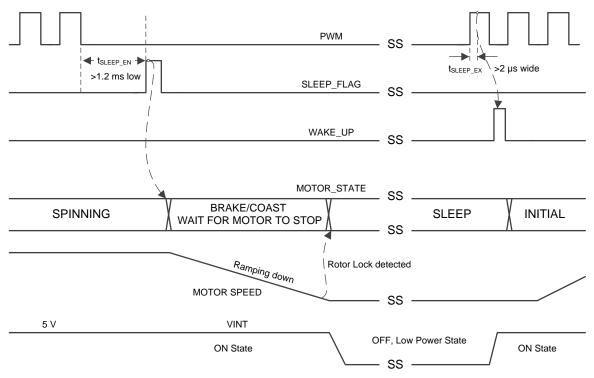

#### 8.3.5 Sleep Mode

The DRV10970 provides a sleep mode function to save power when the motor is not spinning. The device can be commanded to enter sleep mode by driving logic low on PWM pin for at least  $t_{SLEEP_EN}$  seconds. Before entering low-power state, the speed will be ramped down (by brake condition or by coasting) where rotor lock condition is detected. This sequence to bring the motor to a halt condition may take several seconds based on the motor. The device then enters sleep state where reset is asserted and supply is driven to low. Only a small portion of the logic is kept alive to detect the PWM pin high. The device will wake up after PWM goes high (PWM high signal needs to be longer than  $t_{SLEEP_EX}$ ) and starts to drive the motor again.

Figure 14. Sleep Mode Sequence and Timing

The current consumption during sleep mode is less than  $I_{VM\_SLEEP}$ .

In sleep mode, internal regulator VINT is shut down; if the Hall sensors are powered by VINT, the Hall sensors are also put into power off condition to further save power. The U, V, and W phase outputs are tri-stated, FG and RD pins are de-asserted while in the sleep mode. The device will not be able to perform OCP while in sleep mode.

### 8.4 Device Functional Modes

### 8.4.1 Operation in Trapezoidal Mode and Sinusoidal Mode

The DRV10970 device can operate in either trapezoidal mode or sinusoidal mode depending on the setting of CMTMOD pin. Sinusoidal operation mode provides better acoustic performance, which is more suitable for applications like refrigerator fans, HVAC fans, pumps, and other home appliances. Trapezoidal mode provides higher driving torque, which is more suitable for systems with heavy and unpredictable load conditions, such as power tools and actuators.

#### **Device Functional Modes (continued)**

#### 8.4.1.1 Trapezoidal Control Mode

Trapezoidal control is also called 120° control or 6-step control. In the trapezoidal control mode, the DRV10970 device drives standard six step commutation sequence based on the Hall input states and FR (direction) pin value. Trapezoidal (30° Hall placement) commutation is in accordance with Table 1. The startup scheme of sinusoidal control mode is also based on trapezoidal commutation. Trapezoidal mode does not support single Hall sensor operation; it may cause unpredictable motor operation.

| STATE             | ЦА | HALL SIGNAL <sup>(1)</sup> |   |      |        | PHASE O | UTPUT <sup>(2)</sup> |      |      |

|-------------------|----|----------------------------|---|------|--------|---------|----------------------|------|------|

| STATE             | па |                            |   |      | FR = 1 |         | FR = 0               |      |      |

|                   | U  | V                          | W | U    | V      | W       | U                    | V    | W    |

| 1                 | 1  | 1                          | 0 | High | Hi-Z   | Low     | Low                  | Hi-Z | High |

| 2                 | 1  | 0                          | 0 | High | Low    | Hi-Z    | Low                  | High | Hi-Z |

| 3                 | 1  | 0                          | 1 | Hi-Z | Low    | High    | Hi-Z                 | High | Low  |

| 4                 | 0  | 0                          | 1 | Low  | Hi-Z   | High    | High                 | Hi-Z | Low  |

| 5                 | 0  | 1                          | 1 | Low  | High   | Hi-Z    | High                 | Low  | Hi-Z |

| 6                 | 0  | 1                          | 0 | Hi-Z | High   | Low     | Hi-Z                 | Low  | High |

| 1x <sup>(3)</sup> | 0  | 0                          | 0 | Hi-Z | Hi-Z   | Hi-Z    | Hi-Z                 | Hi-Z | Hi-Z |

| 2x <sup>(3)</sup> | 1  | 1                          | 1 | Hi-Z | Hi-Z   | Hi-Z    | Hi-Z                 | Hi-Z | Hi-Z |

(1) Hall signal XHALL = 1 if the positive input terminal voltage (x\_HP) is higher than the negative input terminal voltage (x\_HN)

(2) Phase output = Hi-Z which means both the high-side and low-side MOSFETs are turned off.

(3) State 1x and 2x are invalid states, DRV10970 will output high impedance for all three phases in this condition. Hall sensor placement or connection needs to be changed.

#### Table 2. Trapezoidal Commutation With 0° Hall Placement

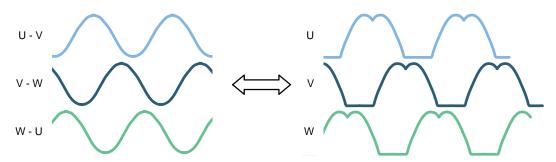

#### 8.4.1.2 Sinusoidal Pulse Wide Modulation (SPWM) Control Mode

If the sinusoidal operation mode is selected, the device will start the motor with trapezoidal operation (based on the commutation table shown in Table 1) and switch to sinusoidal after 6 electrical cycles. If current limit is triggered during trapezoidal startup, the transition will be delayed until current limit is cleared. If current limit is triggered in sinusoidal operation, the device will switch back to trapezoidal mode and will remain until the current limit event goes away (refer to *Current Limit and OCP*).

In sinusoidal control mode, the commutation will only rely on phase U Hall sensor input and ignore the phase V and W Hall sensor input.

The DRV10970 provides sinusoidal voltage shaping in the SPWM mode. The device generates 25-kHz PWM outputs on each phase, which have an average value of sinusoidal waveform on phase to phase. If the phase voltage is measured with respect to ground, the waveform is sinusoidal coupled with third-order harmonics. At any time among the three phases, one phase output equals to zero, as shown in Figure 16.

Figure 15. PWM Output and the Average Value

LEFT: Sinusoidal voltage from phase to phase. RIGHT: Sinusoidal voltage with third-order harmonics from phase to GND

#### Figure 16. Sinusoidal Voltage With Third-Order Harmonics Output

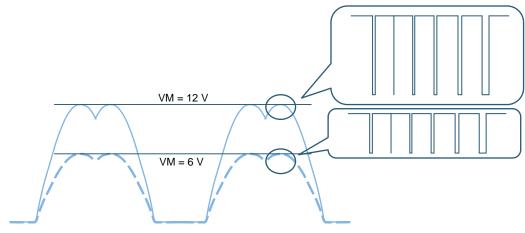

The output amplitude is determined by the VM and the maximum PWM duty cycle among one electrical cycle. If VM is used to control the motor speed, the output maximum PWM duty cycle is 100%. The output amplitude is proportional to the VM amplitude.

Figure 17. Adjust VM to Control the Motor Speed

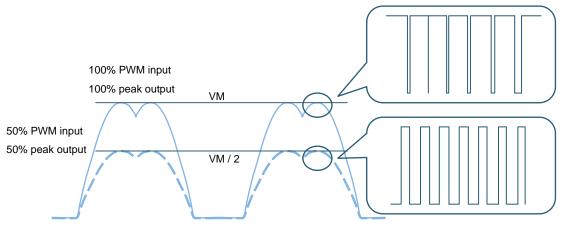

The PWM is used for controlling the motor speed. System calculates the duty cycle of the PWM input as DutyIN, which is converted into sinusoidal PWM output.

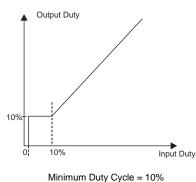

The maximum amplitude is when PWM input is 100% and maximum PWM output duty cycle is 100%, the output amplitude will be VM. A lower value such as VM / 2 could be achieved by driving the PWM duty to 50%. When the input duty cycle is less than 10% and greater than 0% DRV10970 keeps the input command at a 10% duty cycle (see Figure 18).

Figure 18. Duty Cycle Profile

Figure 19. Adjust PWM Input Duty Cycle to Control the Motor Speed

Note that the speed control PWM input frequency does not reflect to PWM output frequency on the phase outputs. The device supports input PWM frequency in the range of 15 to 100 kHz, the PWM output frequency on the phase is always 25 kHz.

## 8.4.2 Single Hall Sensor Operation

The DRV10970 device supports single Hall sensor operation to reduce system cost.

If only U phase Hall sensor is connected to the device and V and W phase Hall sensors are not installed in the system, the device automatically drives the motor in single Hall sensor mode. Single Hall sensor operation does not support trapezoidal operation, which may cause unpredictable motor behavior.

In single hall sensor mode, rotor is aligned to a known position for about 700 ms first and then motor is driven with 2-step DC current into the coil, which means instead of 6-step control, the device only outputs 2 steps based on the U phase Hall sensor signal. The direction of driving current is based on the FR input and the commutation mode setting. Table 3 shows the startup logic. For example, if 0° Hall placement is selected (CMTMOD pin equals to High), FR equals to high, and U phase Hall sensor signal is high, DRV10970 will drive U phase PWM and both V and W phase low.

|                   | PHASE OUTPUT |      |        |      |      |     |      |  |

|-------------------|--------------|------|--------|------|------|-----|------|--|

| HALL<br>PLACEMENT | HALL SIGNAL  |      | FR = 1 |      |      |     |      |  |

| LACEMENT          |              | U    | v      | w    | U    | V   | w    |  |

| 0°                | 1            | PWM  | LOW    | LOW  | LOW  | PWM | PWM  |  |

| 0°                | 0            | LOW  | PWM    | PWM  | PWM  | LOW | LOW  |  |

| 30°               | 1            | PWM  | LOW    | Hi-Z | LOW  | PWM | Hi-Z |  |

| 30°               | 0            | LOW  | PWM    | Hi-Z | PWM  | LOW | Hi-Z |  |

| Single H          | lall Align   | Hi-Z | LOW    | PWM  | Hi-Z | LOW | PWM  |  |

| Table 3. Single Hall Startup | <b>Commutation Table</b> |

|------------------------------|--------------------------|

|------------------------------|--------------------------|

Cycle-by-cycle current limit is effective during single Hall sensor startup. After 6 electrical cycles of startup, the device will switch to sinusoidal mode of operation. If current limit is triggered, sinusoidal control will transit back to 2-step drive mode, same as startup sequence. Refer to *Current Limit and OCP*.

Note that single Hall sensor operation mode may exhibit slight reverse spin of the rotor during startup. The reverse movement will be less than 180 electrical degrees.

The rotor locked condition is detected when no U-phase hall switching for about 700ms. For certain low inertia motors or no load condition, the rotor may continue to vibrate when the rotor is locked which may result in a hall signal switching. This condition is not detected by the device as the hall period may look like a normal motor spinning condition. In this scenario, the device may continue to drive the motor. Lowering the OC limit may help resolve this condition.

Copyright © 2016, Texas Instruments Incorporated

#### 8.4.3 Adaptive Drive Angle Adjustment (ADAA) Mode

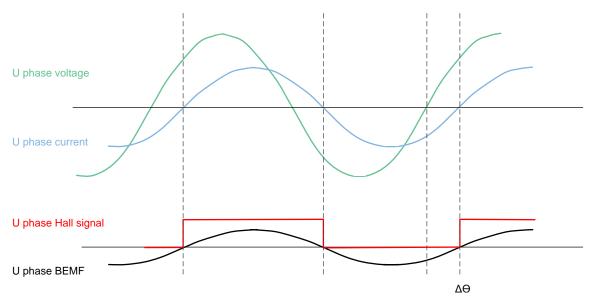

In sinusoidal mode, the phase voltage vector is driven such that phase current and BEMF voltages are aligned (in-phase) in order to achieve the maximum motor efficiency possible. When Hall sensor is placed at 0°, the BEMF voltage will be in-phase with respective Hall signals. The ADAA logic takes advantage of this fact and aligns the U-phase current to the U-Hall sensor input.

If DAA pin is floating, the DRV10970 device will operate in the ADAA mode, in which case, the device continuously monitors the phase difference between the U-phase current and U-phase Hall signal while adjusting the phase voltage driving angle  $\Delta\theta$  (with respect to the U-Hall sensor signal, same as U-BEMF zero crossing) to align the current and Hall signal (shown in Figure 20). ADAA mode is the recommended mode of operation where the motor efficiency is maximized irrespective of motor parameters, load conditions, and motor speeds. ADAA mode is only available in sinusoidal mode and 0° Hall sensor placement. The motors with 30° Hall placement may use the fixed drive angle feature to achieve maximum system efficiency for a given application.

Figure 20. Adaptive Drive Angle Adjustment

For sinusoidal mode and 0° Hall sensor placement, if DAA pin is connected to GND, voltage driving angle will be fixed at 10°. If DAA pin is connected to VINT, voltage driving angle will be fixed at 5°.

For sinusoidal mode and 30° Hall sensor placement, if DAA is floating, voltage drive angle will be fixed at 0°. DAA pin is connected to GND, voltage driving angle will be fixed at 10°. If the DAA pin is connected to VINT, voltage driving angle will be fixed at 5°.

In trapezoidal operation mode, DAA input is ignored and always control the output based on Table 2.

Table 4 shows the DRV10970 operation modes with DAA and CMT\_MOD configurations.

| MODE               | MOTOR<br>TYPE      | HALL<br>PLACEMENT | DAA = FLOATING                           | DAA = GND       | DAA = VINT                               | COMMENTS                                                                                                               |                                                                                                                           |

|--------------------|--------------------|-------------------|------------------------------------------|-----------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| CMT_MOD = floating | Trapezoidal        | 30°               | Trapezoidal mode, DAA signal is ignored. |                 | Trapezoidal mode, DAA signal is ignored. |                                                                                                                        | The Trapezoidal motor with 0° Hall placement<br>may use 30 degree Hall delay (OTP setting) to<br>achieve optimum driving. |

| CMT_MOD =<br>GND   |                    | 0°                | ADAA                                     | 10° drive angle | 5° drive angle                           | BEMF zero crossing and Hall crossing will be in-sync.                                                                  |                                                                                                                           |

| CMT_MOD =<br>VINT  | 9 = Sinusoidal 30° |                   | 0° drive angle                           | 10° drive angle | 5° drive angle                           | The drive angle is specified with respect to BEMF zero crossing. When measured with respect to Hall-U signal, add 30°. |                                                                                                                           |

## 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 9.1 Application Information

#### 9.1.1 Hall Sensor Configuration and Connections

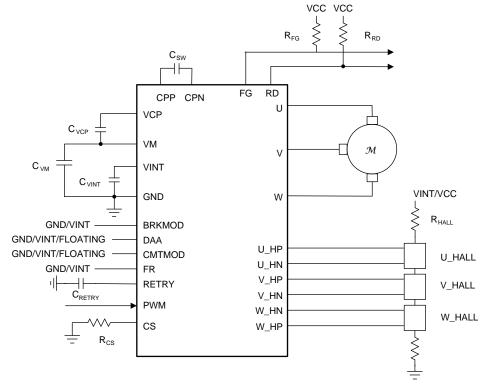

Hall sensors must be connected to the DRV10970 to provide the feedback of the motor position. The DRV10970 Hall sensor input circuit is capable of interfacing with a variety of Hall sensors, and with two different ways of Hall sensor placement, which are 0° placement and 30° placement.

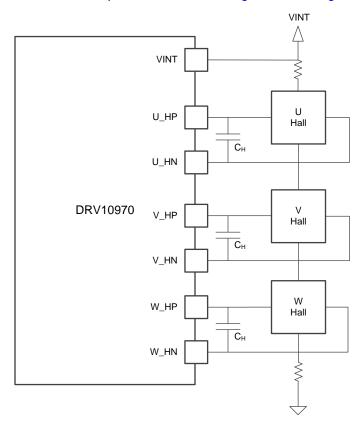

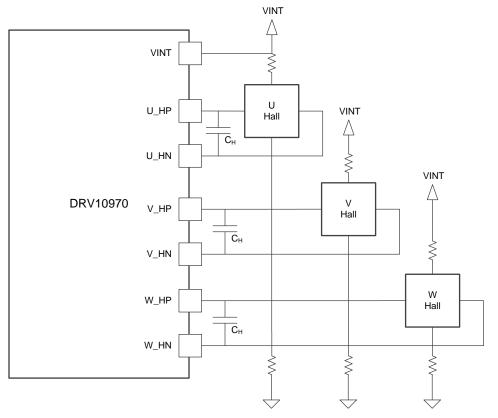

Typically, a Hall element is used, which outputs a differential signal on the order of 100 mV or higher. The VINT regulator can be used for powering the Hall sensors, which eliminates the need for an external regulator. The Hall elements can be connected in serial or parallel as shown in Figure 21 and Figure 22.

Figure 21. Serial Hall Element Connection

## **Application Information (continued)**

Figure 22. Parallel Hall Element Connection

Noise on the Hall signal degrades the commutation performance of the device. Therefore, take utmost care to minimize the noise while routing the Hall signals to the device inputs. The device internally has fixed time hall filtering of about 320  $\mu$ s. To further minimize the high-frequency noise, a noise filtering capacitor may be connected across x\_HP and x\_HN pins as shown in Figure 21 and Figure 22. The value of the capacitor can be selected such that the RC time constant is in the range of 0.1 to 2  $\mu$ s. For example, Hall sensor with internal impedance (between Hall output to ground) of 1 k $\Omega$ , C<sub>H</sub> value is 1  $\mu$ F for 1- $\mu$ s time constant.

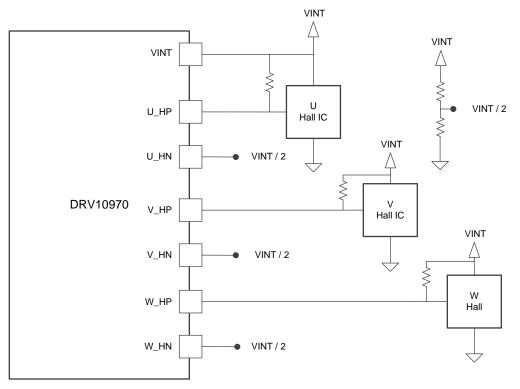

Some motors integrate Hall sensors that provide logic outputs with open-drain type. These sensors can also be used with the DRV10970, with circuits shown in Figure 23. The negative ( $x_HN$ ) inputs are biased to 2.5 V by a pair of resistors between VINT and ground. For open-drain type Hall sensors, an additional pullup resistor to supply is needed on the positive ( $x_HP$ ) input, where VINT is used again. The VINT output may be used to supply power to the Hall sensors as well.

## **Application Information (continued)**

Figure 23. Hall IC Connection

The correspondence between the phase U, V, W and the Hall signal U, V, W needs to follow the DRV10970 definition, which is:

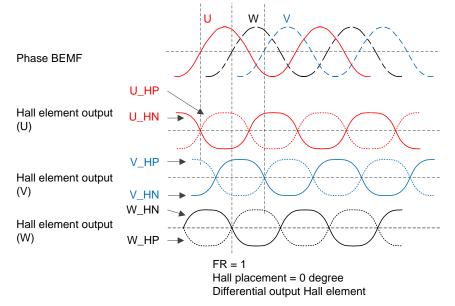

- 1. Phase U is leading phase W by 120°, phase W is leading phase V by 120°. The Hall signal positive output is aligned with respective phase BEMF. Choose FR = 1 and 0° placement option (see Figure 24).

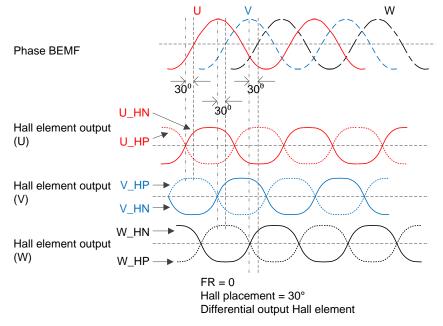

- Phase U is leading phase V by 120°, phase V is leading phase W by 120°. The Hall signal positive output is aligned with respective phase BEMF in the opposite direction. Choose FR = 0 and 0° placement option (see Figure 25).

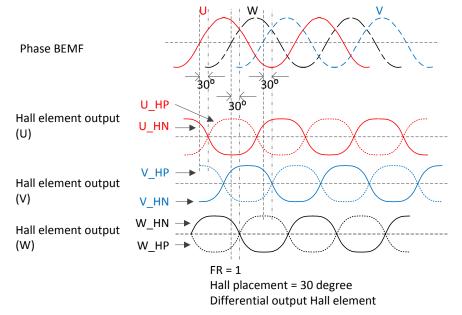

- 3. Phase U is leading phase W by 120°, phase W is leading phase V by 120°. The Hall signal positive output is 30° lagging of respective phase BEMF. Choose FR = 1 and 30° placement option (see Figure 26).

- Phase U is leading phase V by 120°, phase V is leading phase W by 120°. The Hall signal positive output is 30° leading of respective phase BEMF. Choose FR = 0 and 30° placement option (see Table 2 and Figure 29).

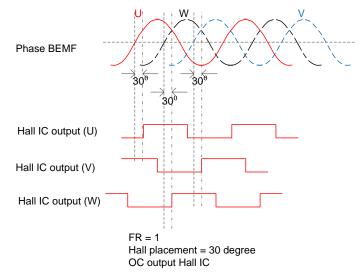

The correspondence and sequency is also applied to applications using open-drain output Hall ICs. Figure 28 is an example of FR = 0, and 30° placement condition.

## **Application Information (continued)**

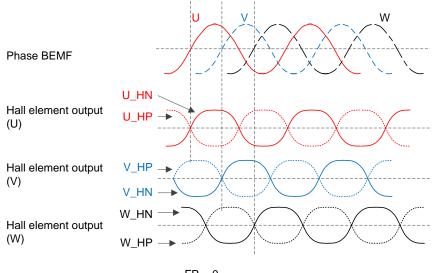

Figure 24. Correspondence Between Motor BEMF and Hall Signal (FR = 1, 0° Placement)

FR = 0 Hall placement = 0 degree Differential output Hall element

Figure 25. Correspondence Between Motor BEMF and Hall Signal (FR = 0, 0° Placement)

## **Application Information (continued)**

Figure 26. Correspondence Between Motor BEMF and Hall Signal (FR = 1, 30° Placement)

Figure 27. Correspondence Between Motor BEMF and Hall Signal (FR = 0, 30° Placement)

## **Application Information (continued)**

Figure 28. Correspondence Between Motor BEMF and Hall Signal (FR = 1, 30° Placement, Hall IC)

If the motor terminal definition is different from the previous description, rename the motor phase U, V, W, or the Hall U, V, W, or swap the positive and negative of the Hall sensor output to make it match.

Use these tips to find the correct U, V, and W phases and the respective Hall sensors:

- 1. Assume motor phases and Hall outputs do not have labels. If named, remove them.

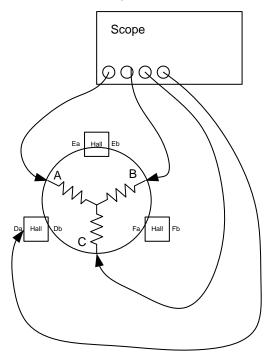

- 2. Label A, B, C to the motor terminals (phases). Label Da and Db, Ea and Eb, Fa and Fb to the Hall output pairs. If Hall ICs are used, just label the digital outputs as D, E, F.

- 3. Use three 10-k $\Omega$  resistors, connect them to motor terminals A, B, C with star connection. The center is called COM.

- 4. Provide power to the Hall sensors.

#### **Application Information (continued)**

- 5. Use 4 channel Scope to observe signals. Connect probe -1, 2, 3 to A, B, C terminals of the motor (phases), probe-4 connects to Hall Da (or D). Name the probe 1 (terminal-A) as U-phase. (see Figure 30)

- 6. Turn the rotor manually in clock-wise direction. If the waveform on probe-1 (U-phase) is leading probe-2 (terminal-B) by 120°, name the terminal-B as phase W and terminal-C as phase V. Else if waveform on the probe-2 is leading probe 1 (U) by 120°, terminal-B as V, terminal-C as W. At this stage all three phases of the motor are identified.

- 7. Motor manufacturers have two popular Hall placement options. The first is 0° Hall placement (BEMF and Hall signals are in-phase) and the second is 30° Hall placement (BEMF leads Hall signal by 30°). If the probe-4 is in-phase (or lagging 30°) with phase-U, name Da as Hall U positive (U\_HP), Db as Hall U negative (U\_HN). If probe-4 is in-phase with phase U (or lagging 30°), but inverted polarity, name Da as U\_HN, Db as U\_HP. If the probe-4 is not in-phase (or lagging 30°) with respect to U but aligns with phase-V or W, name accordingly as V\_HP/V\_HN or W\_HP/W\_HN. Repeat this step to map Ea/Eb and Fa/Fb in the same way. By end of this step, all three sets of Hall signals are mapped to respective phase signals phase U & Hall U\_HP/HN, phase V & Hall V\_HP/V\_HN and phase W and W\_HP/W\_HN. Care should be taken while judging 30° Hall placement, sometimes 30° and 60° look alike. If U phase is leading Hall Da by 60°, there will be another phase (V or W) with in-phase or lagging by 30° relationship. Hence it's important to check all three phases before concluding.

- 8. When Hall ICs are used, if the Hall D is in-phase or lagging 30° with respect to phase U but inverted polarity, name the Hall D output as U\_HN, and 2.5-V reference voltage to U\_HP. If Hall D is leading 30°, then turn the rotor in counter clock-wise direction and map remaining E & F Hall outputs.

- 9. After phase UVW and Hall UVW positive negative are identified, manually rotate the motor again, check if the result matches Figure 24 and Figure 25 (0° placement) or Figure 26 and Figure 25 (30° placement).

- 10. Connect U,V,W and Hall U,V,W to the DRV10970, with the FR = 1, it should rotate with direction you manually spun it. Connect FR = 0, the motor will spin in the other direction.

Figure 30. Motor Measurement

DRV10970 SLVSCU7A-FEBRUARY 2016-REVISED MARCH 2016

www.ti.com

## 9.2 Typical Application

Figure 31. Typical Application Schematic

### 9.2.1 Design Requirements

Table 5 gives design input parameters for system design.

| DESIGN PARAMETER                     | EXAMPLE VALUE |

|--------------------------------------|---------------|

| Supply voltage                       | 5 to 18 V     |

| Continuous operation current         | 0 to 1 A      |

| Peak current                         | 1.5 A         |

| Hall sensor differential output peak | >40 mV        |

| PWM input frequency                  | 15 to 100 kHz |

| PWM duty cycle                       | 0% to 100%    |

#### **Table 5. Design Parameters**

#### 9.2.2 Detailed Design Procedure

- Refer to *Design Requirements* and make sure the system meets the recommended application range.

- Refer to *Hall Sensor Configuration and Connections* and make sure correct phases and corresponding hall signals are identified.

- Refer to Hall Sensor Configuration and Connections and make sure hall signals are connected accurately.

- Build your hardware based on Layout Guidelines.

- Connect the device into system and validate your system.

### 9.2.3 Application Curves

## **10** Power Supply Recommendations

The DRV10970 is designed to operate from an input voltage supply (VM) range between 5 and 18 V. Place a 10- $\mu$ F ceramic capacitor rated for VM as close as possible to the DRV10970.

## 11 Layout

### 11.1 Layout Guidelines

The VM terminal should be bypassed to GND using a low-ESR ceramic bypass capacitor with a recommended value of  $10-\mu$ F rated for VM. Place this capacitor as close as possible to the VM pin with a thick trace or ground plane connection to the device GND pin.

The  $C_{RETRY}$  capacitor should be placed as close to the RETRY pin as possible with a thick trace or ground plane connection to the device GND pin.

A low-ESR ceramic capacitor must be placed in between the CPN and CPP pins. TI recommends a value of 0.1- $\mu$ F rated for VM. Place this component as close as possible to the pins.

A low-ESR ceramic capacitor must be placed in between the VM and VCP pins. TI recommends a value of  $1-\mu$ F rated for 16 V. Place this component as close as possible to the pins.

Bypass VINT to ground with 2.2-µF ceramic capacitors rated for 10 V. Place these bypassing capacitors as close to the pins as possible.

Because the GND pin carries motor current, take utmost care while planning grounding scheme, keep the ground potential difference between any two points less than 100 mV.

### 11.2 Layout Example

## **12 Device and Documentation Support**

### 12.1 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E<sup>™</sup> Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support TI's Design Support** Quickly find helpful E2E forums along with design support tools and contact information for technical support.

### 12.2 Trademarks

PowerPAD, E2E are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

### 12.3 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## 12.4 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

3-Aug-2017

## PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|----------------------------|------------------|---------------------|--------------|-------------------------|---------|

| DRV10970PWP      | ACTIVE | HTSSOP       | PWP                | 24   | 60             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | DRV10970                | Samples |

| DRV10970PWPR     | ACTIVE | HTSSOP       | PWP                | 24   | 2000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | DRV10970                | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**ROHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## PACKAGE OPTION ADDENDUM

3-Aug-2017

## PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

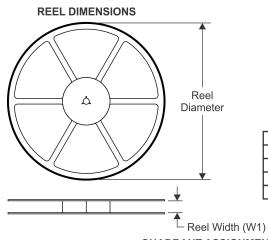

## TAPE AND REEL INFORMATION

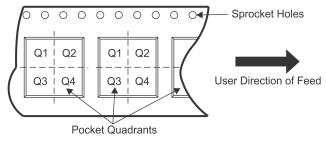

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |  |

|-----------------------------|--|

|-----------------------------|--|

| Device       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| DRV10970PWPR | HTSSOP          | PWP                | 24 | 2000 | 330.0                    | 16.4                     | 6.95       | 8.3        | 1.6        | 8.0        | 16.0      | Q1               |

TEXAS INSTRUMENTS

www.ti.com

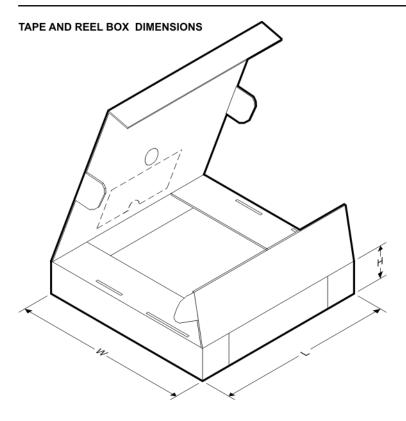

## PACKAGE MATERIALS INFORMATION

26-Feb-2019

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DRV10970PWPR | HTSSOP       | PWP             | 24   | 2000 | 350.0       | 350.0      | 43.0        |

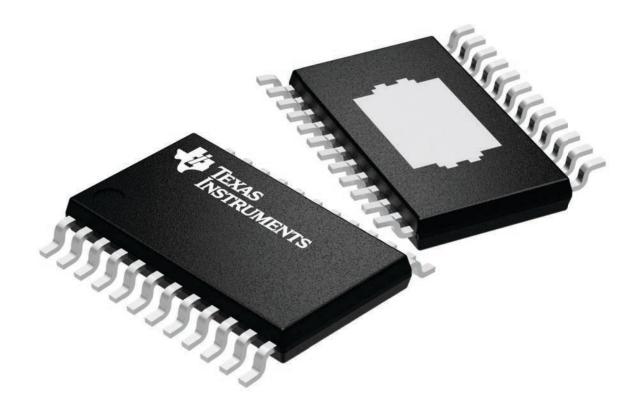

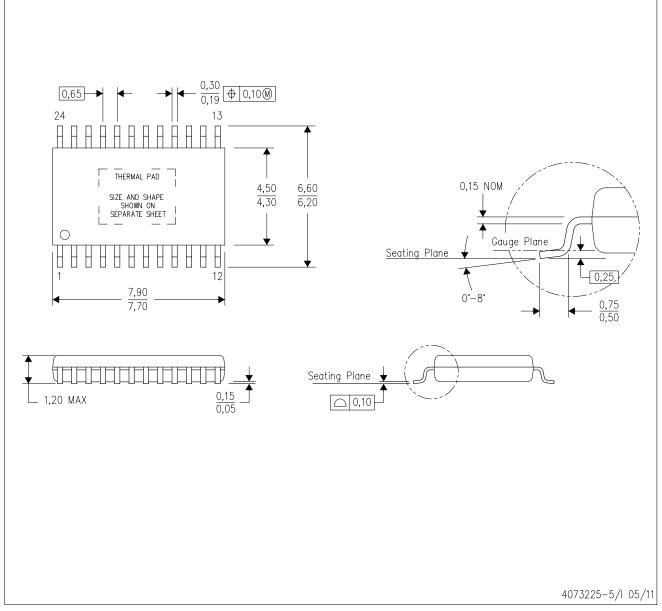

## **PWP 24**

## **GENERIC PACKAGE VIEW**

# PowerPAD<sup>™</sup> TSSOP - 1.2 mm max height

PLASTIC SMALL OUTLINE

4.4 x 7.6, 0.65 mm pitch

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

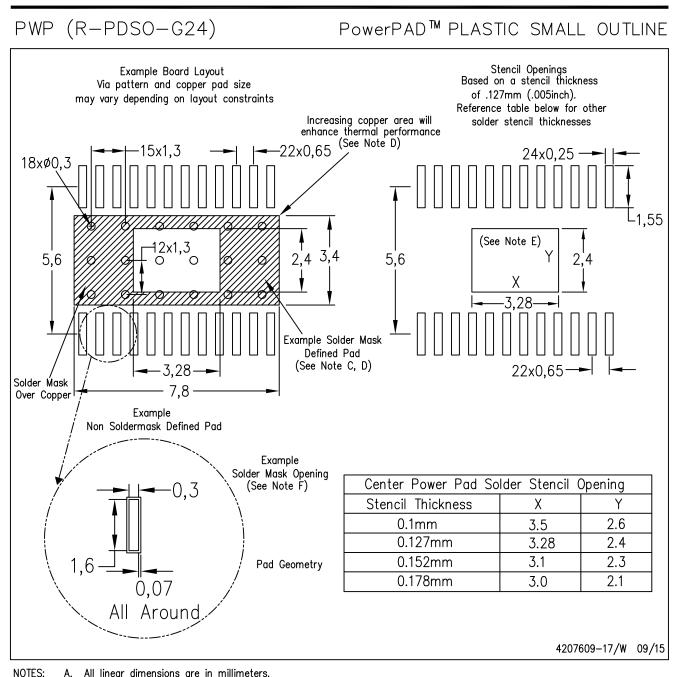

PWP (R-PDSO-G24)

PowerPAD<sup>™</sup> PLASTIC SMALL OUTLINE

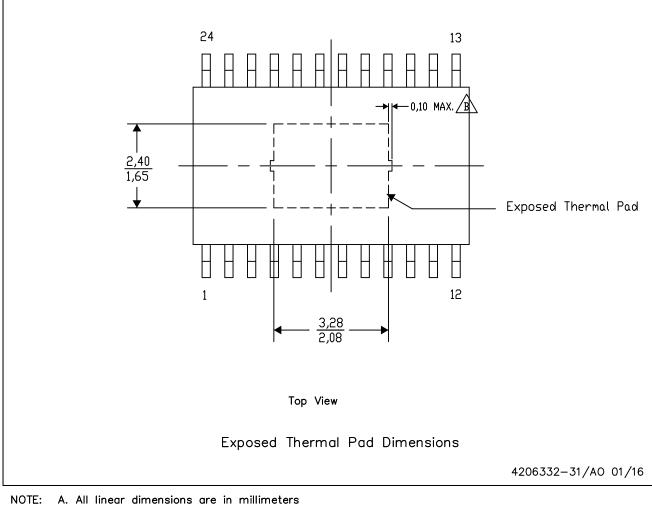

All linear dimensions are in millimeters. NOTES: Α.

- Β. This drawing is subject to change without notice.

- Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side. C.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad D. Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>. E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

#### THERMAL INFORMATION