DRV10983-Q1

SLVSD14 - JUNE 2017

# DRV10983-Q1 Automotive, Three-Phase, Sensorless BLDC Motor Driver

# **Features**

- **Qualified for Automotive Applications**

- AEC-Q100 Qualified With the Following Results:

- Device Temperature Grade 1: -40°C to 125°C Ambient Operating Temperature Range

- Device HBM ESD Classification Level 1C

- Device CDM ESD Classification Level C4A

- Operation Voltage Range:

- Motor Operation, 6.2 V to 28 V

- Register Setting Preserved, 4.5 V to 45 V

- Supports Load Dump Voltage up to 45 V

- Total Driver H + L r<sub>DS(on)</sub>

- 250 mΩ at T<sub>A</sub> = 25°C

- 325 mΩ at T<sub>A</sub> = 125°C

- Drive Current: 2-A Continuous Winding Current (3-A Peak)

- Configurable Output PWM Slew Rate and Frequency for EMI Management

- Sensorless Proprietary Back Electromotive Force (BEMF) Control Scheme (No Need of Hall Sensors)

- Continuous Sinusoidal 180° Commutation

- Initial Position-Detect Algorithm to Avoid Back Spin During Start-Up

- No External Sense Resistor Required

- Flexible User Interface Options:

- I<sup>2</sup>C Interface: Access Registers for Command and Feedback

- Dedicated SPEED Pin: Accepts Either Analog or PWM Input

- Dedicated FG Pin: Provides TACH Feedback

- Spin-Up Profile Can Be Customized With **EEPROM**

- Forward-Reverse Control With DIR Pin

- Integrated Buck Converter to Efficiently Provide 5-V and 3.3-V LDOs for Internal and External

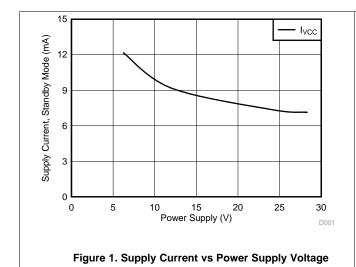

- Supply Current 8.5 mA With Standby Version (DRV10983SQ)

- Supply Current of 48 µA With Sleep Version (DRV10983Q)

- **Protection Features**

- Overcurrent Protection (Protection for Phaseto-Phase, Phase-to-GND and Phase-to-V<sub>CC</sub> Shorts

- Lock Detection

- Anti-Voltage Surge (AVS) Protection

- **UVLO Protection**

- Thermal Shutdown Protection

- Thermally Enhanced Package

# 2 Applications

- Small Automotive Pumps and Fans

- Seat Ventilation Fans

- Motorcycle Fuel Pumps

- **HEV Battery Cooling Fans**

# 3 Description

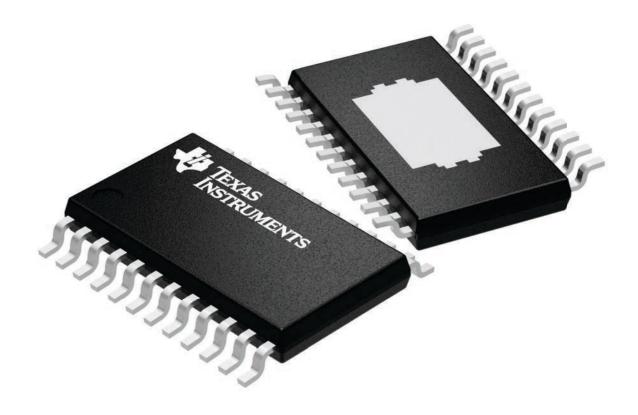

The DRV10983-Q1 device is a 3-phase sensorless motor driver with integrated power MOSFETs, which can provide continuous drive current up to 2 A. The device is specifically designed for cost-sensitive, lownoise, low-external-component-count fan and pump applications.™

The DRV10983-Q1 device preserves register setting down to 4.5 V and delivers current to the motor with supply voltage as low as 6.2 V. If the power supply voltage is higher than 28 V, the device stops driving the motor and protects the DRV10983-Q1 circuitry. This function is able to handle a load dump condition up to 45 V.

#### **Device Options:**

DRV10983Q: Sleep Version

DRV10983SQ: Standby Version

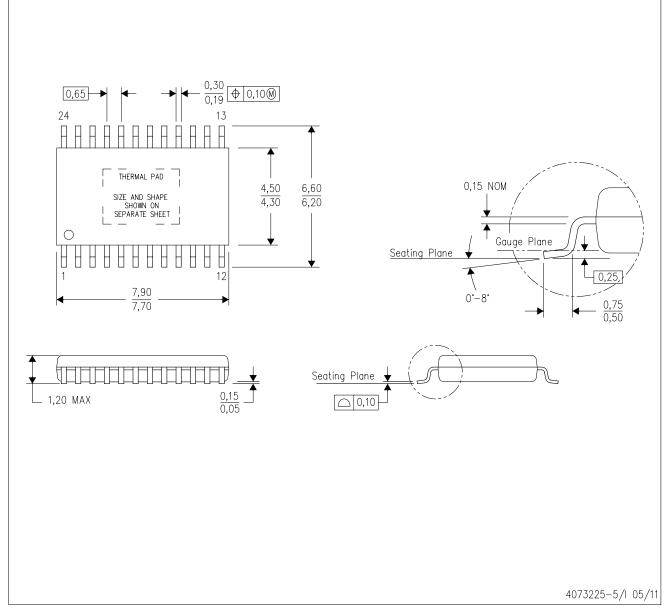

# **Device Information** (1)

| PART NUMBER | PACKAGE     | BODY SIZE (NOM)   |

|-------------|-------------|-------------------|

| DRV10983-Q1 | HTSSOP (24) | 7.80 mm × 6.40 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

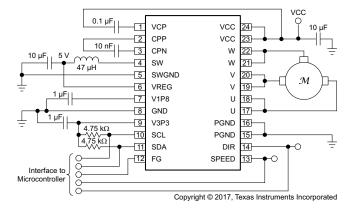

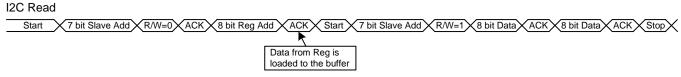

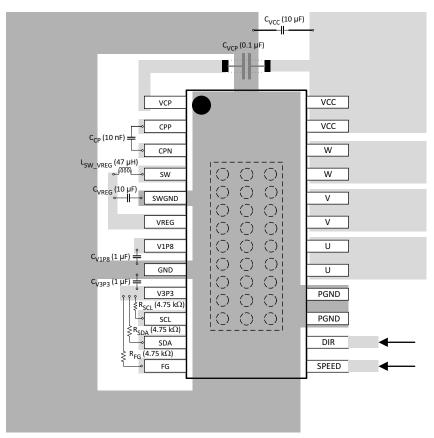

# Application Schematic

# **Table of Contents**

| 1<br>2<br>3<br>4<br>5<br>6<br>7 | Features         1           Applications         1           Description         1           Revision History         2           Description (Continued)         3           Pin Configuration and Functions         3           Specifications         5           7.1 Absolute Maximum Ratings         5                                                               | 9<br>10<br>11 | 8.4 Device Functional Modes | 60<br>60<br>60<br>63<br>63 |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------|----------------------------|

| 8                               | 7.2 ESD Ratings       5         7.3 Recommended Operating Conditions       6         7.4 Thermal Information       6         7.5 Electrical Characteristics       7         7.6 Typical Characteristics       9         Detailed Description       10         8.1 Overview       10         8.2 Functional Block Diagram       11         8.3 Feature Description       11 | 12            | 11.2 Layout Example         | 64 64 ates 64 64           |

# 4 Revision History

| DATE      | REVISION | NOTES           |  |

|-----------|----------|-----------------|--|

| June 2017 | *        | Initial release |  |

Submit Documentation Feedback

# 5 Description (Continued)

The DRV10983-Q1 device uses a proprietary sensorless control scheme to provide continuous sinusoidal drive, which significantly reduces the pure tone acoustics that typically occur as a result of commutation. The interface to the device is designed to be simple and flexible. The motor can be controlled directly through PWM, analog, or I<sup>2</sup>C inputs. Motor speed feedback is available through both the FG pin and the I<sup>2</sup>C interface simultaneously.

The DRV10983-Q1 device features an integrated buck regulator to step down the supply voltage efficiently to 5 V for powering both internal and external circuits. The 3.3-V LDO also may be used to provide power for external circuits. The device is available in either a sleep mode or a standby mode version to conserve power when the motor is not running. The standby mode (8.5 mA) version (DRV10983SQ) leaves the regulator running and the sleep mode (48 μA) version (DRV10983Q) shuts the regulator off. Use the standby mode version in applications where the regulator is used to power an external microcontroller. Throughout this data sheet, the DRV10983-Q1 part number is used for both devices i.e. DRV10983Q (sleep version) and DRV10983SQ (standby version), except for specific discussions of sleep vs standby functionality.

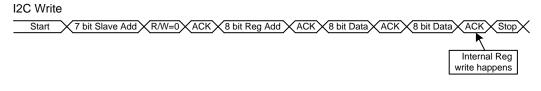

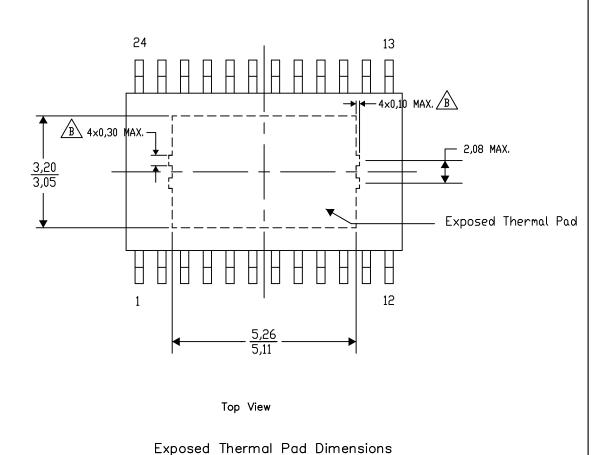

An I<sup>2</sup>C interface allows the user to reprogram specific motor parameters in registers and to program the EEPROM to help optimize the performance for a given application. The DRV10983-Q1 device is available in a thermally-efficient HTSSOP, 24-pin package with an exposed thermal pad. The operating ambient temperature is specified from -40°C to 125°C.

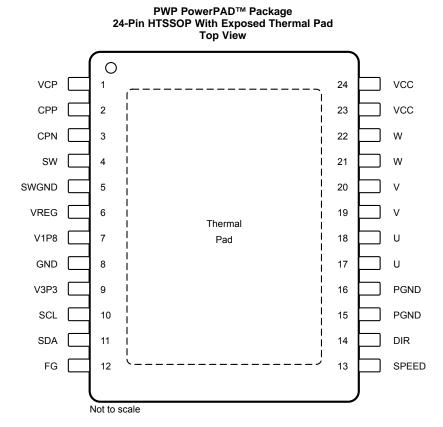

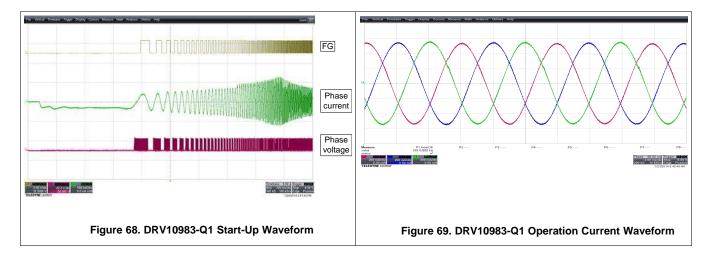

# 6 Pin Configuration and Functions

Copyright © 2017, Texas Instruments Incorporated

# **Pin Functions**

| PIN               |        | TYPE | DESCRIPTION                                                                                                                                                                                                     |  |

|-------------------|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| N/AME             | HTSSOP | (1)  | DESCRIPTION  Charge numb bin 1, use a ceramic capacitor between CPN and CPP                                                                                                                                     |  |

| CPN               | 3      | Р    | Charge pump pin 1, use a ceramic capacitor between CPN and CPP                                                                                                                                                  |  |

| CPP               | 2      | Р    | Charge pump pin 2, use a ceramic capacitor between CPN and CPP                                                                                                                                                  |  |

| DIR               | 14     | I    | Direction; When low, phase driving sequence is $U \to V \to W$ When high, phase driving sequence is $U \to W \to V$                                                                                             |  |

| FG                | 12     | 0    | FG signal output indicates speed of motor                                                                                                                                                                       |  |

| GND               | 8      | Р    | Digital and analog ground                                                                                                                                                                                       |  |

| PGND              | 15, 16 | Р    | Power ground                                                                                                                                                                                                    |  |

| SCL               | 10     | I    | I <sup>2</sup> C clock signal                                                                                                                                                                                   |  |

| SDA               | 11     | I/O  | I <sup>2</sup> C data signal                                                                                                                                                                                    |  |

| SPEED             | 13     | I    | Speed control signal for PWM or analog input speed command                                                                                                                                                      |  |

| SW                | 4      | 0    | Step-down regulator switching node output                                                                                                                                                                       |  |

| SWGND             | 5      | Р    | Step-down regulator ground                                                                                                                                                                                      |  |

| U                 | 17, 18 | 0    | Motor U phase                                                                                                                                                                                                   |  |

| V                 | 19, 20 | 0    | Motor V phase                                                                                                                                                                                                   |  |

| V1P8              | 7      | Р    | Internal 1.8-V digital core voltage. V1P8 capacitor must connect to GND. This is an output, but is not specified to drive external loads.                                                                       |  |

| V3P3              | 9      | Р    | Internal 3.3-V supply voltage. V3P3 capacitor must connect to GND. This is an output and may drive external loads not to exceed I <sub>V3P3_MAX</sub> .                                                         |  |

| V <sub>CC</sub>   | 23, 24 | Р    | Device power supply                                                                                                                                                                                             |  |

| VCP               | 1      | Р    | Charge pump output, use a ceramic capacitor between VCP and V <sub>CC</sub>                                                                                                                                     |  |

| VREG              | 6      | Р    | Step-down regulator output and feedback point                                                                                                                                                                   |  |

| W                 | 21, 22 | 0    | Motor W phase                                                                                                                                                                                                   |  |

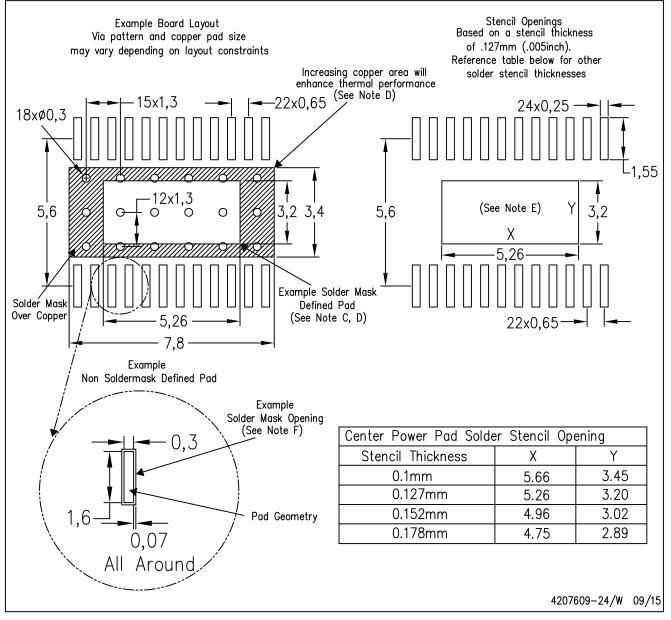

| Thermal pad (GND) | _      | Р    | The exposed thermal pad must be electrically connected to the ground plane by soldering to the PCB for proper operation, and connected to the bottom side of the PCB through vias for better thermal spreading. |  |

<sup>(1)</sup> I = Input, O = Output, I/O = Input/output, NC = No connect, P = Power

Submit Documentation Feedback

Copyright © 2017, Texas Instruments Incorporated

# 7 Specifications

www.ti.com

# 7.1 Absolute Maximum Ratings

over operating ambient temperature range (1)

|                    |                                                                       | MIN  | MAX                 | UNIT |  |

|--------------------|-----------------------------------------------------------------------|------|---------------------|------|--|

|                    | V <sub>CC</sub>                                                       | -0.3 | 28                  |      |  |

| Input voltage (2)  | V <sub>CC</sub> during load dump (V <sub>CC</sub> slew rate < 1 V/μs) | -0.3 | 45                  |      |  |

|                    | SPEED                                                                 | -0.3 | 4                   | \/   |  |

|                    | PGND, SWGND                                                           | -0.3 | 0.3                 | V    |  |

|                    | SCL, SDA                                                              | -0.3 | 4                   |      |  |

|                    | DIR                                                                   | -0.3 | 4                   |      |  |

|                    | U, V, W                                                               | -1   | 30                  |      |  |

|                    | SW                                                                    | -1   | 30                  |      |  |

|                    | VREG                                                                  | -0.3 | 7                   |      |  |

|                    | FG                                                                    | -0.3 | 4                   |      |  |

| Output voltage (2) | VCP                                                                   | -0.3 | V <sub>CC</sub> + 6 | V    |  |

|                    | CPN                                                                   | -0.3 | 30                  |      |  |

|                    | CPP                                                                   | -0.3 | V <sub>CC</sub> + 6 |      |  |

|                    | V3P3                                                                  | -0.3 | 4                   |      |  |

|                    | V1P8                                                                  | -0.3 | 2.5                 |      |  |

| $T_{J\_MAX}$       | Maximum junction temperature                                          | -40  | 150                 | °C   |  |

| T <sub>stg</sub>   | Storage temperature                                                   | -55  | 150                 | °C   |  |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                    |               |                                                        | VALUE | UNIT |

|--------------------|---------------|--------------------------------------------------------|-------|------|

| V                  | Electrostatic | Human body model (HBM), per AEC Q100-002, all pins (1) | ±2000 | \/   |

| V <sub>(ESD)</sub> | discharge     | Charged device model (CDM), per AEC Q100-011, all pins | ±750  | V    |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

Copyright © 2017, Texas Instruments Incorporated

<sup>(2)</sup> All voltage values are with respect to the ground terminal (GND) unless otherwise noted.

# 7.3 Recommended Operating Conditions

|                |                                                                     | MIN  | NOM | MAX                 | UNIT |

|----------------|---------------------------------------------------------------------|------|-----|---------------------|------|

| Supply voltage | V <sub>CC</sub> , register contents preserved                       | 4.5  | 12  | 45                  | V    |

| Supply voltage | V <sub>CC</sub> , motor operational                                 | 6.2  | 12  | 28                  | V    |

|                | U, V, W                                                             | -0.7 |     | 29                  |      |

|                | SCL, SDA, FG, SPEED, DIR                                            | -0.1 | 3.3 | 3.6                 |      |

| Valtaga ranga  | PGND, GND, SWGND                                                    | -0.1 |     | 0.1                 | V    |

| Voltage range  | VCP, CPP                                                            | -0.1 |     | V <sub>CC</sub> + 5 | V    |

|                | CPN                                                                 | -0.1 |     | $V_{CC}$            |      |

|                | SW                                                                  | -0.7 |     | V <sub>CC</sub>     |      |

|                | Step-down regulator output current (buck mode)                      |      |     | 100                 |      |

| Current range  | Step-down regulator output current (resistive mode)                 |      |     | 5                   | mA   |

| ourient range  | V3P3 LDO output current (no load on VREG and V3P3 in resitive mode) |      |     | 5                   | ША   |

| T <sub>A</sub> | Operating ambient temperature                                       | -40  | ·   | 125                 | °C   |

# 7.4 Thermal Information

|                      |                                              | DRV10983-Q1  |      |

|----------------------|----------------------------------------------|--------------|------|

|                      | THERMAL METRIC (1)                           | PWP (HTSSOP) | UNIT |

|                      |                                              | 24 PINS      |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 36.1         | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 17.4         | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 14.8         | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.4          | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 14.5         | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 1.1          | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see Semiconductor and IC Package Thermal Metrics.

www.ti.com

# 7.5 Electrical Characteristics

over operating voltage and ambient temperature range (unless otherwise noted)

|                          | PARAMETER                                            | TEST CONDITIONS                                                         | MIN | TYP     | MAX  | UNIT |

|--------------------------|------------------------------------------------------|-------------------------------------------------------------------------|-----|---------|------|------|

| SUPPLY CURF              | RENT (DRV10983Q)                                     |                                                                         |     |         |      |      |

| 1                        | Cloop ourrent                                        | V <sub>SPEED</sub> = 0 V; VCC = 12 V; T <sub>A</sub> = 25°C             |     | 48      | 54   |      |

| I <sub>VccSLEEP1</sub>   | Sleep current                                        | V <sub>SPEED</sub> = 0 V; VCC = 12 V; across temperature                |     |         | 81   | μΑ   |

|                          |                                                      | V <sub>SPEED</sub> > 0 V; buck regulator with inductor; no motor load   |     | 10      | 15   |      |

| I <sub>Vcc</sub>         | Active current                                       | V <sub>SPEED</sub> > 0 V; buck regulator with resistor; no motor load   |     | 13      | 16   | mA   |

| SUPPLY CURF              | RENT (DRV10983SQ)                                    |                                                                         |     |         |      |      |

|                          | Olas aller annual                                    | V <sub>SPEED</sub> = 0 V; buck regulator with inductor                  |     | 8.5     | 14   | Α.   |

| I <sub>VccSTBY</sub>     | Standby current                                      | V <sub>SPEED</sub> = 0 V; buck regulator with resistor                  |     | 11      | 15   | mA   |

|                          |                                                      | V <sub>SPEED</sub> > 0 V; buck regulator with inductor; no motor load   |     | 10      | 15   |      |

| I <sub>Vcc</sub>         | Active current                                       | V <sub>SPEED</sub> > 0 V; buck regulator with resistor; no motor load   |     | 13      | 16   | mA   |

| UVLO                     |                                                      | 1                                                                       |     |         |      |      |

| V <sub>UVLO_R</sub>      | UVLO rising threshold voltage                        |                                                                         | 5.8 | 6       | 6.2  | V    |

| V <sub>UVLO_F</sub>      | UVLO falling threshold voltage                       |                                                                         | 5.6 | 5.8     | 6    | V    |

| V <sub>UVLO_HYS</sub>    | UVLO threshold voltage hysteresis                    |                                                                         | 170 | 195     | 220  | mV   |

| V <sub>V1P8_UVLO_R</sub> | V1P8 UVLO rising threshold                           |                                                                         | 1.5 | 1.6     | 1.7  | V    |

| V <sub>V1P8_UVLO_F</sub> | V1P8 UVLO falling threshold                          |                                                                         | 1.4 | 1.55    | 1.65 | V    |

| V <sub>V3P3_UVLO_R</sub> | V3P3 UVLO rising threshold                           |                                                                         | 2.7 | 2.85    | 2.95 | V    |

| V <sub>V3P3_UVLO_F</sub> | V3P3 UVLO falling threshold                          |                                                                         | 2.5 | 2.7     | 2.8  | V    |

| V <sub>VREG_UVLO_R</sub> | VREG UVLO rising threshold                           |                                                                         | 4   | 4.2     | 4.3  | V    |

| V <sub>VREG_UVLO_F</sub> | VREG UVLO falling threshold                          |                                                                         | 3.9 |         | 4.2  | V    |

| LDO OUTPUT               |                                                      |                                                                         |     |         |      |      |

| V3P3                     | Output voltage                                       | Buck regulator with inductor, 20-mA load                                | 3.1 | 3.1 3.3 | 3.5  | V    |

|                          |                                                      | Buck regulator with resistor, no load                                   | -   |         |      |      |

| I <sub>V3P3_MAX</sub>    | Maximum load from V3P3                               | Only with inductor mode of buck operation, with resistor mode no load   |     |         | 20   | mA   |

| V1P8                     | Output voltage                                       | No load                                                                 | 1.7 | 1.8     | 1.9  | V    |

| STEP-DOWN F              |                                                      |                                                                         |     |         | -    |      |

|                          |                                                      | $L_{SW}$ = 47 $\mu$ H, $C_{SW}$ = 10 $\mu$ F<br>$I_{load}$ = 100 mA     |     |         |      |      |

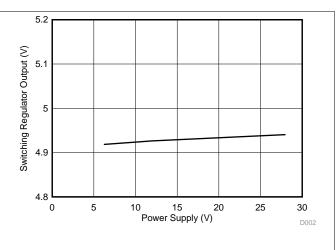

| $V_{REG}$                | Regulator output voltage                             | $R_{SW} = 39 \Omega$ , $C_{SW} = 10 \mu F$<br>$I_{load} = 5 \text{ mA}$ | 4.5 | 5       | 5.5  | V    |

| I <sub>REG_MAX_L</sub>   | Maximum load from V <sub>REG</sub> in switching mode | L <sub>SW</sub> = 47 μH, C <sub>SW</sub> = 10 μF                        |     |         | 100  | mA   |

| I <sub>REG_MAX_R</sub>   | Maximum load from V <sub>REG</sub> in linear mode    | $R_{SW} = 39 \ \Omega, \ C_{SW} = 10 \ \mu F$                           |     |         | 5    | mA   |

| INTEGRATED               | MOSFET                                               | ,                                                                       |     |         |      |      |

|                          | <b>2</b> 1                                           | $T_A = 25^{\circ}C; V_{(VCC)} > 6.5 V; Io = 1 A$                        |     | 250     | 400  | _    |

| r <sub>DS(ON)</sub>      | Series resistance (H + L)                            | $T_A = 125^{\circ}C; V_{(VCC)} > 6.5V; Io = 1 A$                        |     | 325     | 550  | mΩ   |

# **Electrical Characteristics (continued)**

over operating voltage and ambient temperature range (unless otherwise noted)

|                                               | PARAMETER                                       | TEST CONDITIONS                                                        | MIN                       | TYP  | MAX                 | UNIT |

|-----------------------------------------------|-------------------------------------------------|------------------------------------------------------------------------|---------------------------|------|---------------------|------|

| SPEED - AN                                    | ALOG MODE                                       |                                                                        |                           |      |                     |      |

| V <sub>AN/A FS</sub>                          | Analog full-speed voltage                       |                                                                        | V <sub>(V3P3)</sub> × 0.9 |      | V <sub>(V3P3)</sub> | V    |

| V <sub>AN/A_ZS</sub>                          | Analog zero-speed voltage                       |                                                                        | 0                         |      | 100                 | mV   |

| t <sub>SAM</sub>                              | Sampling period for analog voltage on SPEED pin |                                                                        |                           | 320  |                     | μs   |

| V <sub>AN/A_RES</sub>                         | Analog voltage resolution                       |                                                                        |                           | 6.5  |                     | mV   |

|                                               | M DIGITAL MODE                                  |                                                                        | <u>'</u>                  |      |                     |      |

| V <sub>DIG_IH</sub>                           | PWM input high voltage                          |                                                                        | 2.2                       |      |                     | V    |

| V <sub>DIG_IL</sub>                           | PWM input low voltage                           |                                                                        |                           |      | 0.6                 | V    |

| $f_{PWM}$                                     | PWM input frequency                             |                                                                        | 0.1                       |      | 100                 | kHz  |

|                                               | IDBY CONDITION                                  |                                                                        |                           |      |                     |      |

| V <sub>EN_SL_SB</sub>                         | Analog voltage to enter sleep/standby           | SpdCtrlMd = 0 (analog mode)                                            |                           |      | 100                 | mV   |

| V <sub>EX_SL</sub>                            | Analog voltage to exit sleep                    | SpdCtrlMd = 0 (analog mode)                                            | 2.2                       |      |                     | V    |

| V <sub>EX_SB</sub>                            | Analog voltage to exit standby                  | SpdCtrlMd = 0 (analog mode)                                            | 0.17                      |      | 3.3                 | V    |

| t <sub>EX_SL</sub>                            | Time to exit from sleep mode                    | $SpdCtrlMd = 0 \text{ (analog mode)}$ $V_{SPEED} > V_{EX\_SL}$         |                           | 2    |                     | μs   |

| t <sub>EX_SB</sub>                            | Time to exit from standby mode                  | SpdCtrlMd = 0 (analog mode)<br>V <sub>SPEED</sub> > V <sub>EX_SB</sub> |                           | 700  | 800                 | ms   |

| t <sub>EX_SL_SB</sub>                         | Time to exit from sleep or standby condition    | SpdCtrlMd = 1 (PWM mode)<br>V <sub>SPEED</sub> > V <sub>DIG_IH</sub>   |                           | 2    |                     | μs   |

| t <sub>EN_SL_SB</sub>                         | Time to enter sleep or standby condition        | SpdCtrlMd = 1 (PMW mode)<br>V <sub>SPEED</sub> < V <sub>DIG_IL</sub>   |                           | 60   |                     | ms   |

| DIGITAL I/O (                                 | (DIR INPUT, FG OUTPUT )                         | _                                                                      | ,                         |      |                     |      |

| V <sub>DIR_H</sub>                            | Input high                                      |                                                                        | 2.2                       |      |                     | V    |

| $V_{DIR\_L}$                                  | Input low                                       |                                                                        |                           |      | 0.6                 | V    |

| V <sub>FG_OH</sub>                            | Output high voltage I <sub>o</sub> = 5 mA       |                                                                        |                           | 3.3  |                     | V    |

| V <sub>FG_OL</sub> I <sup>2</sup> C SERIAL II | Output low voltage I <sub>o</sub> = 5 mA        |                                                                        |                           |      | 0.6                 | V    |

| V <sub>I2C_H</sub>                            | Input high                                      |                                                                        | 2.2                       |      |                     | V    |

| V <sub>12C_L</sub>                            | Input low                                       |                                                                        | 2.2                       |      | 0.6                 | V    |

| fl2C_L                                        | I <sup>2</sup> C clock frequency                |                                                                        | 0                         |      | 400                 | kHz  |

|                                               | CTION RELEASE TIME                              |                                                                        |                           |      |                     |      |

| t <sub>LOCK_OFF</sub>                         | Lock release time                               |                                                                        |                           | 5    |                     | s    |

| t <sub>LCK_ETR</sub>                          | Lock enter time                                 |                                                                        |                           | 0.3  |                     | s    |

|                                               | ENT PROTECTION                                  | L                                                                      | 1                         |      |                     |      |

| I <sub>OC_limit_HS</sub>                      | HS overcurrent protection                       | V <sub>CC</sub> < 28.5 V                                               | 3.5                       | 4.25 | 5.5                 | Α    |

| I <sub>OC_limit_LS</sub>                      | LS overcurrent protection                       | V <sub>CC</sub> < 28.5 V                                               | 3.5                       | 4.25 | 5.5                 | A    |

| THERMAL SH                                    | <u>'</u>                                        |                                                                        | 1                         |      |                     | -    |

| T <sub>SDN</sub>                              | Junction temperature shutdown threshold         |                                                                        | 150                       | 165  | 180                 | °C   |

| T <sub>SDN_HYS</sub>                          | Junction temperature shutdown hysteresis        |                                                                        | 15                        | 20   | 25                  | °C   |

| T <sub>WARN</sub>                             | Junction temperature warning threshold          |                                                                        | 115                       | 125  | 140                 | °C   |

Submit Documentation Feedback

Copyright © 2017, Texas Instruments Incorporated

www.ti.com

# **Electrical Characteristics (continued)**

over operating voltage and ambient temperature range (unless otherwise noted)

|                      | PARAMETER                                                           | TEST CONDITIONS                                           | MIN  | TYP  | MAX  | UNIT |

|----------------------|---------------------------------------------------------------------|-----------------------------------------------------------|------|------|------|------|

| PHASE DRIV           | VER                                                                 |                                                           |      |      |      |      |

| SL <sub>PH_LH0</sub> | Phase slew rate switching low to high                               | PHslew = 0; measure 20% to 80%;<br>V <sub>CC</sub> = 12 V | 85   | 120  | 145  | V/µs |

| SL <sub>PH_LH1</sub> | Phase slew rate switching low to high                               | PHslew = 1; measure 20% to 80%; V <sub>CC</sub> = 12 V    | 60   | 80   | 100  | V/µs |

| SL <sub>PH_LH2</sub> | Phase slew rate switching low to high                               | PHslew = 2; measure 20% to 80%; V <sub>CC</sub> = 12 V    | 38   | 50   | 62   | V/µs |

| SL <sub>PH_LH3</sub> | Phase slew rate switching low to high                               | PHslew = 3; measure 20% to 80%;<br>V <sub>CC</sub> = 12 V | 27   | 35   | 44   | V/µs |

| SL <sub>PH_HL0</sub> | Phase slew rate switching high to low                               | PHslew = 0; measure 80% to 20%;<br>V <sub>CC</sub> = 12 V | 85   | 120  | 145  | V/µs |

| SL <sub>PH_HL1</sub> | Phase slew rate switching high to low                               | PHslew = 1; measure 80% to 20%; V <sub>CC</sub> = 12 V    | 59   | 80   | 100  | V/µs |

| SL <sub>PH_HL2</sub> | Phase slew rate switching high to low                               | PHslew = 2; measure 80% to 20%;<br>V <sub>CC</sub> = 12 V | 36   | 50   | 60   | V/µs |

| SL <sub>PH_HL3</sub> | Phase slew rate switching high to low                               | PHslew = 3; measure 80% to 20%;<br>V <sub>CC</sub> = 12 V | 25   | 35   | 45   | V/µs |

| LOAD DUM             | PROTECTION                                                          |                                                           |      |      |      |      |

| V <sub>OV_R</sub>    | Load dump protection mode entry on rising V <sub>CC</sub> threshold |                                                           | 28.5 | 29.2 | 30   | V    |

| V <sub>OV_F</sub>    | Load dump protection mode exit on falling V <sub>CC</sub> threshold |                                                           | 27.7 | 28.2 | 28.8 | V    |

| V <sub>OV_HYS</sub>  | Load dump protection mode hysteresis                                |                                                           | 0.73 | 1    | 1.1  | V    |

# 7.6 Typical Characteristics

Figure 2. Switching Regulator Output vs Power Supply Voltage

# TEXAS INSTRUMENTS

# 8 Detailed Description

#### 8.1 Overview

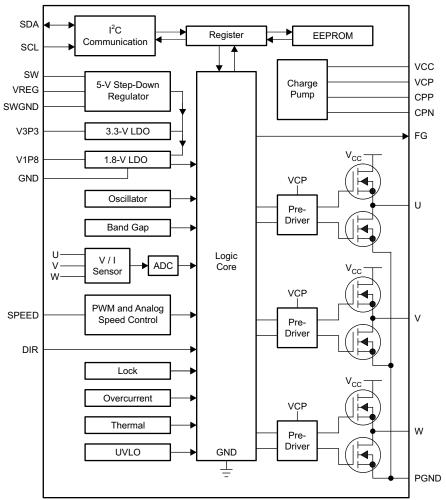

The DRV10983-Q1 device is a three-phase sensorless motor driver with integrated power MOSFETs that provides drive-current capability up to 2 A continuously. The device is specifically designed for low-noise, low-external-component-count motor-drive applications. The device is configurable through a simple I<sup>2</sup>C interface to accommodate different motor parameters and spin-up profiles for different customer applications.

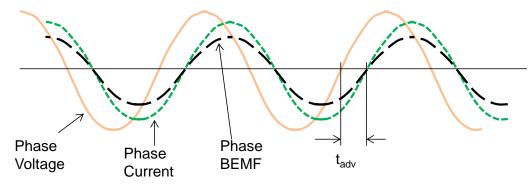

A 180° sensorless control scheme provides continuous sinusoidal output voltages to the motor phases to enable ultra-quiet motor operation by keeping the electrically induced torque ripple small.

The DRV10983-Q1 device features extensive protection and fault-detection mechanisms to ensure reliable operation. Voltage surge protection prevents the input  $V_{CC}$  capacitor from overcharging, which is typical during motor deceleration. The device provides overcurrent protection without the need for an external current-sense resistor. Rotor-lock detection is available through several methods. These methods can be configured with register settings to ensure reliable operation. The device provides additional protection for undervoltage lockout (UVLO) and for thermal shutdown.

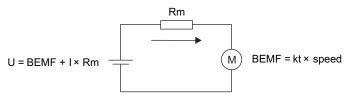

The commutation control algorithm continuously measures the motor phase current and periodically measures the  $V_{CC}$  supply voltage. The device uses this information for BEMF estimation, and the information is also provided through the  $I^2C$  register interface for debug and diagnostic use in the system, if desired.

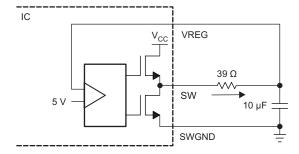

A buck switching regulator efficiently steps down the supply voltage. The output of this regulator provides power for the internal circuits and can also be used to provide power for an external circuit such as a microcontroller. If providing power for an external circuit is not necessary (and to reduce system cost), configure the buck switching regulator as a linear regulator by replacing the inductor with a resistor.

The DRV10983-Q1 device has a flexible interface, capable of supporting both analog and digital inputs. In addition to the  $I^2$ C interface, the device has FG, DIR, and SPEED pins. SPEED is the speed command input pin. DIR is the direction control input pin. FG is the speed indicator output, which shows the frequency of the motor commutation.

EEPROM is integrated in the DRV10983-Q1 device as memory for the motor parameter and operation settings. EEPROM data transfers to the registers after power-on and exit from sleep mode.

The DRV10983-Q1 device can also operate in register mode. If the system includes a microcontroller communicating through the I<sup>2</sup>C interface, the device can dynamically update the motor parameters and operation settings by writing to the registers. In this configuration, the EEPROM data is bypassed by the register settings.

10

# 8.2 Functional Block Diagram

Copyright © 2017, Texas Instruments Incorporated

#### 8.3 Feature Description

#### 8.3.1 Regulators

#### 8.3.1.1 Step-Down Regulator

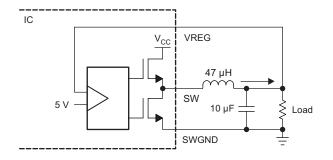

The DRV10983-Q1 device includes a step-down hysteretic voltage regulator that can operate with either an external inductor or with an external resistor. The best efficiency is achieved when an external inductor (see Figure 3) is used. The regulator output voltage is 5 V. When the regulated voltage drops by the hysteresis level, the high-side FET turns on to raise the regulated voltage back to the target of 5 V. The switching frequency of the hysteretic regulator is not constant and changes with load.

If the step-down regulator is configured with an external inductor, it can deliver current to the load as specified by  $I_{REG\_MAX\_L}$ . If the step-down regulator is configured with an external resistor it, can deliver current to the load as specified by  $I_{REG\_MAX\_R}$ .

# TEXAS INSTRUMENTS

# Feature Description (continued)

Buck Regulator with External Inductor

**Buck Regulator with External Resistor**

Figure 3. Step-Down Regulator Configurations

#### 8.3.1.2 3.3-V and 1.8-V LDO

The DRV10983-Q1 device includes a 3.3-V LDO and a 1.8-V LDO. The 1.8-V LDO is for internal circuits only. The 3.3-V LDO is mainly for internal circuits, but can also drive external loads not to exceed  $I_{V3P3\_MAX}$ . For example, it can work as a pullup voltage for the FG, DIR, SDA, and SCL interface.

Both the V1P8 and V3P3 capacitors must be connected to GND.

#### 8.3.2 Protection Circuits

#### 8.3.2.1 Thermal Shutdown

The DRV10983-Q1 device has a built-in thermal shutdown function, which shuts down the device when the junction temperature is more than  $T_{SDN}$  and recovers operating conditions when the junction temperature falls to  $T_{SDN} - T_{SDN}$  HYS  $^{\circ}$ C.

The OverTemp status bit (address 0x00, bit 15) is set during thermal shutdown. In addition to the thermal shutdown function there is a warning bit that is set whenever the device exceeds  $T_{WARN}$  and is indicated by the TempWarning bit of the FaultReg register (address 0x00, bit 14).

## 8.3.2.2 UVLO

The DRV10983-Q1 device has a built-in UVLO function block. The device is locked out when  $V_{CC}$  is below  $V_{UVLO\_F}$  and is unlocked when  $V_{CC}$  is above  $V_{UVLO\_R}$ . The hysteresis of the UVLO threshold is  $V_{UVLO\_HYS}$ . In addition to the main supply, the step-down regulator, charge pump, and 3.3-V LDO all have undervoltage lockout monitors.

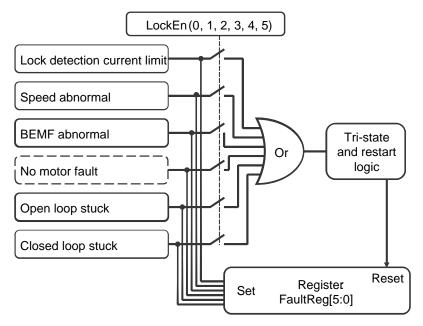

#### 8.3.2.3 Current Protection

The overcurrent shutdown function acts to protect the device if the current, as measured from the FETs, exceeds the  $I_{OC-limit}$  threshold. It protects the device in the event of a short-circuit condition on the motor phases. This includes phase shorts to GND, phase shorts to phase, or phase shorts to  $V_{CC}$ . The DRV10983-Q1 device places the output drivers into a high-impedance state until the lock time  $t_{LOCK\_OFF}$  has expired. The OverCurr status bit of the FaultReg register (address 0x00, bit 11) is set.

The DRV10983-Q1 device also provides acceleration current-limit and lock-detection current-limit functions to protect the device and motor (see *Current Limit* and *Lock Detect and Fault Handling*).

www.ti.com SLVSD14 – JUNE 2017

# **Feature Description (continued)**

#### 8.3.2.4 Lock

When the motor is blocked or stopped by an external force, lock protection is triggered, and the device stops driving the motor immediately. After the lock release time t<sub>LOCK\_OFF</sub>, the DRV10983-Q1 device resumes driving the motor again. If the lock condition is still present, it enters the next lock protection cycle, and repeats until the lock condition is removed. With this lock protection, the motor and device do not overheat or become damaged due to the motor being locked (see *Lock Detect and Fault Handling*).

During a lock condition the Status register indicates which of the locks has occurred.

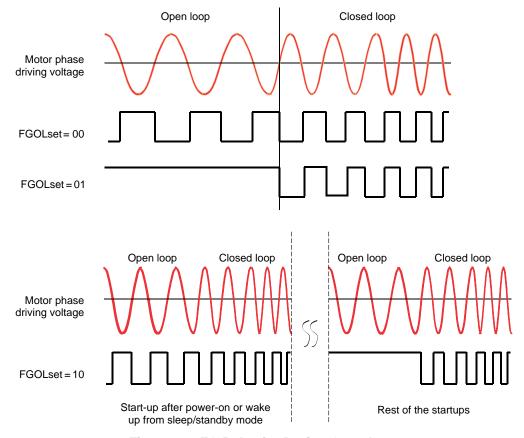

## 8.3.3 Motor Speed Control

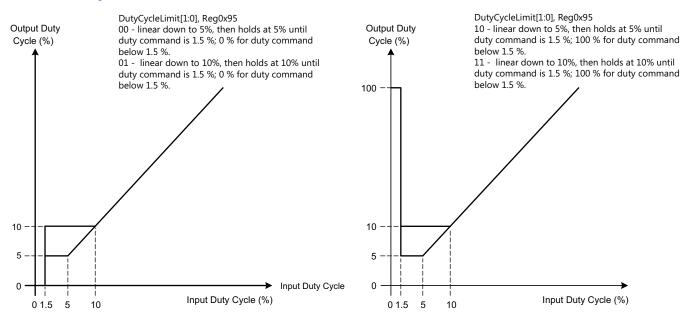

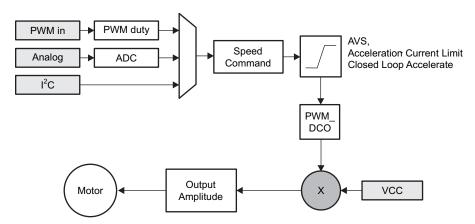

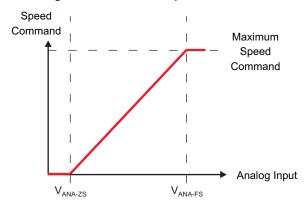

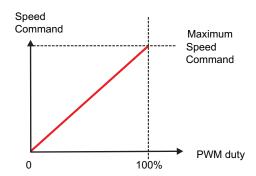

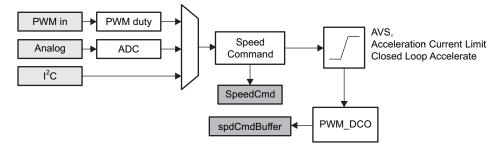

The DRV10983-Q1 device offers four methods for indirectly controlling the speed of the motor by adjusting the output voltage amplitude. This can be accomplished by varying the supply voltage (V<sub>CC</sub>) or by controlling the speed command. The speed command can be controlled in one of three ways. The user can set the speed command by adjusting either the PWM input (PWM in) or the analog input (Analog) or by writing the speed command directly through the I<sup>2</sup>C serial port (I<sup>2</sup>C). The speed command is used to determine the PWM duty cycle output (PWM\_DCO) (see Figure 5).

The input PWM input (PWM in) can have a minimum duty cycle limit applied. DutyCycleLimit[1:0], accessible through the I<sup>2</sup>C interface, allows the user to configure the minimum duty cycle behavior. This behavior is illustrated in Figure 4.

Figure 4. Duty Cycle Profile

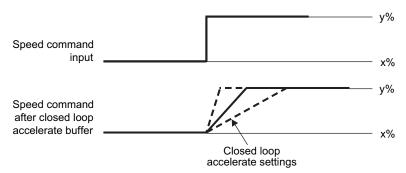

The speed command may not always be equal to the PWM\_DCO because the DRV10983-Q1 device has the AVS function (see *Anti Voltage Supression Function*), the acceleration current-limit function (see *Acceleration Current Limit*), and the closed-loop accelerate function (see *Closed-Loop Accelerate*) to optimize the control performance. These functions can limit the PWM\_DCO, which affects the output amplitude (see Figure 5).

# TEXAS INSTRUMENTS

# **Feature Description (continued)**

Figure 5. Multiplexing the Speed Command to the Output Amplitude Applied to the Motor

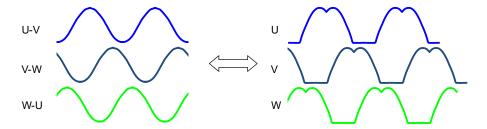

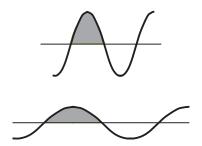

The output voltage amplitude applied to the motor is developed through sine wave modulation so that the phase-to-phase voltage is sinusoidal.

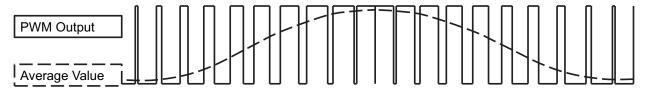

When any phase is measured with respect to ground, the waveform is sinusoidally coupled with third-order harmonics. This encoding technique permits one phase to be held at ground while the other two phases are pulse-width modulated. Figure 6 and Figure 7 show the sinusoidal encoding technique used in the DRV10983-Q1 device.

Figure 6. PWM Output and the Average Value

Sinusoidal voltage from phase to phase

Sinusoidal voltage with third-order harmonics from phase to GND

Figure 7. Representing Sinusoidal Voltages With Third-Order Harmonic Output

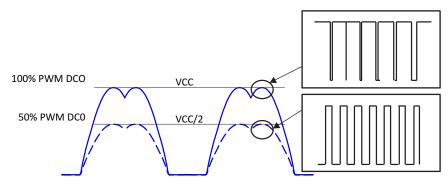

The output amplitude is determined by the magnitude of  $V_{CC}$  and the PWM duty cycle output (PWM\_DCO). The PWM\_DCO represents the peak duty cycle that is applied in one electrical cycle. The maximum amplitude is reached when PWM\_DCO is at 100%. The peak output amplitude is  $V_{CC}$ . When the PWM\_DCO is at 50%, the peak amplitude is  $V_{CC}$  / 2 (see Figure 8).

SLVSD14 - JUNE 2017

# Feature Description (continued)

Figure 8. Output Voltage Amplitude Adjustment

Motor speed is controlled indirectly by controlling the output amplitude, which is achieved by either controlling V<sub>CC</sub>, or controlling the PWM\_DCO. The DRV10983-Q1 device provides different options for the user to control the PWM DCO:

- Analog input (SPEED pin)

- PWM encoded digital input (SPEED pin)

- I<sup>2</sup>C serial interface.

See the *Closed Loop* section for more information.

### 8.3.4 Load Dump Handling

The recommended operation voltage of the DRV10983-Q1 device is from 6.2 V to 28 V. The device is able to drive the motor within this V<sub>CC</sub> range.

In the load dump condition,  $V_{CC}$  can rise up to 45 V. Once the DRV10983-Q1 device detects that  $V_{CC}$  is higher than  $V_{OV_R}$ 3, it stops driving the motor and protects its own circuitry. When  $V_{CC}$  drops below  $V_{OV_F}$ , the DRV10983-Q1 device continues to operate the motor based on the user's command.

#### 8.3.5 Sleep or Standby Condition

The DRV10983-Q1 device is available in either a sleep mode (DRV10983Q) or standby mode version (DRV10983SQ). The DRV10983-Q1 device enters either sleep or standby to conserve energy. When the device enters either sleep or standby, the device stops driving the motor. The switching regulator is disabled in the sleep mode version to conserve more energy. The I<sup>2</sup>C interface is disabled and any register data not stored in EEPROM is reset for the sleep mode version. The switching regulator remains active in the standby mode version. The register data is maintained, and the I<sup>2</sup>C interface remains active for standby mode version.

For different speed command modes, Table 1 shows the timing and command to enter the sleep or standby condition.

|                          |                                                                     | •                                                                | •                                                            |

|--------------------------|---------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------|

| SPEED<br>COMMAND<br>MODE | ENTER SLEEP OR STANDBY<br>CONDITION                                 | EXIT FROM STANDBY CONDITION                                      | EXIT FROM SLEEP CONDITION                                    |

| Analog                   | SPEED pin voltage < V <sub>EN_SL_SB</sub> for t <sub>EN_SL_SB</sub> | SPEED pin voltage > V <sub>EX_SB</sub> for t <sub>EX_SB</sub>    | SPEED pin high (V > $V_{DIG\_IH}$ ) for $t_{EX\_SL\_SB}$     |

| PWM                      | SPEED pin low (V < $V_{DIG\_IL}$ ) for $t_{EN\_SL\_SB}$             | SPEED pin high (V > $V_{DIG\_IH}$ ) for $t_{EX\_SL\_SB}$         | SPEED pin high (V > $V_{DIG\_IH}$ ) for $t_{EX\_SL\_SB}$ (1) |

| I <sup>2</sup> C         | SpdCtrl[8:0] is programmed as 0 for                                 | SpdCtrl[8:0] is programmed as non-zero for t <sub>EX_SL_SB</sub> | SPEED pin high (V > V <sub>DIG_IH</sub> ) for                |

Table 1. Conditions to Enter or Exit Sleep or Standby Condition

(1) See Table 2 for details on PWM duty cycle requirements to exit sleep mode.

Note that when using the analog speed command, a higher voltage is required to exit from the sleep condition than from the standby condition. The I<sup>2</sup>C speed command cannot take the device out of the sleep condition because I<sup>2</sup>C communication is disabled during the sleep condition.

Table 2. Minimum PWM Duty Cycle Requirement for Different PWM Frequency to Exit Sleep Condition

| INPUT PWM FREQUENCY (kHz) | PWM DUTY CYCLE (%) |

|---------------------------|--------------------|

| 0.1 to 0.5                | 14                 |

| 0.5 to 1                  | 11                 |

| 1 to 50                   | 9                  |

| 50 to 100                 | 4                  |

| 100                       | 3.5                |

#### 8.3.6 EEPROM Access

The DRV10983-Q1 device has 112 bits (7 registers with 16-bit width) of EEPROM data, which are used to program the motor parameters as described in the PC Serial Interface.

The procedure for programming the EEPROM is as follows. TI recommends to perform the EEPROM programming without the motor spinning, cycle the power after the EEPROM write, and read back the EEPROM to verify the programming is successful.

- 1. Power up with any voltage within operating voltage range (6.2 V to 28 V)

- 2. (DRV10983Q only) Exit from sleep condition

- 3. Wait 10 ms

- 4. Write register 0x60 to set MTR DIS = 1; this disables the motor driver.

- 5. Write register 0x31 with 0x0000 to clear the EEPROM access code

- 6. Write register 0x31 with 0xC0DE to enable access to EEPROM

- 7. Read register 0x32 for eeReadyStatus = 1

- 8. Case-A: Mass Write

- (a) Write all individual shadow registers

- (a) Write register 0x90 (CONFIG1) with CONFIG1 data

- (b) ...

- (c) Write register 0x96 (CONFIG7) with CONFIG7 data

- (b) Write the following to register 0x35

- (a) ShadowRegEn = 0

- (b) eeRefresh = 0

- (c) eeWRnEn = 1

- (d) EEPROM Access Mode = 10

- (c) Wait for register 0x32 eeReadyStatus = 1 EEPROM is now updated with the contents of the shadow registers.

- 9. Case-B: Mass Read

- (a) Write the following to register 0x35

- (a) ShadowRegEn = 0

- (b) eeRefresh = 0

- (c) eeWRnEn = 0

- (d) eeAccMode = 10

- (b) Internally, the device starts reading the EEPROM and storing it in the shadow registers.

- (c) Wait for register 0x32 eeReadyStatus = 1 shadow registers now contain the EEPROM values

- 10. Write register 0x60 to set MTR\_DIS = 0; this re-enables the motor driver

Product Folder Links: DRV10983-Q1

**NSTRUMENTS**

www.ti.com SLVSD14 – JUNE 2017

#### 8.4 Device Functional Modes

This section includes the logic required to be able to reliably start and drive the motor. It describes the processes used in the logic core and provides the information needed to configure the parameters effectively to work over a wide range of applications.

#### 8.4.1 Motor Parameters

See the DRV10983-Q1 Tuning Guide for the motor parameter measurement.

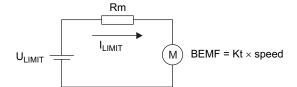

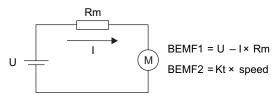

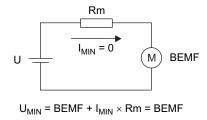

The motor resistance and motor velocity constants are two important parameters used to characterize a BLDC motor. The DRV10983-Q1 device requires these parameters to be configured in the register. The motor resistance is programmed by writing the values for Rm[6:0] (combination of RMShift[2:0] and RMValue[3:0]) in the Config1 register. The motor velocity constant is programmed by writing the values for Kt[6:0] (combination of KTShift[2:0] and KTValue[3:0]) in the Config2 register.

#### 8.4.1.1 Motor Resistance

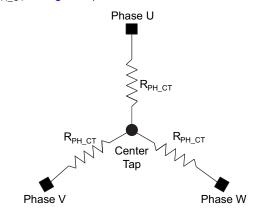

For a wye-connected motor, the motor phase resistance refers to the resistance from the phase output to the center tap,  $R_{PH\ CT}$  (denoted as  $R_{PH\ CT}$  in Figure 9).

Figure 9. Wye-Connected Motor Resistance

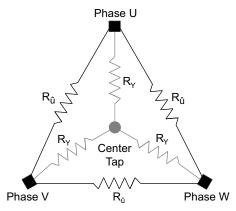

For a delta-connected motor, the motor phase resistance refers to the equivalent phase to center tap in the wye configuration. In Figure 10, it is denoted as  $R_Y$ .  $R_{PH\ CT} = R_Y$ .

For both the delta-connected motor and the wye-connected motor, the easy way to get the equivalent  $R_{PH\_CT}$  is to measure the resistance between two phase terminals ( $R_{PH\_PH}$ ), and then divide this value by two,  $R_{PH\_CT} = \frac{1}{2}$   $R_{PH\_PH}$ .

Figure 10. Delta-Connected Motor and the Equivalent Wye Connections

Copyright © 2017, Texas Instruments Incorporated

# TEXAS INSTRUMENTS

# **Device Functional Modes (continued)**

The motor resistance ( $R_{PH\_CT}$ ) must be converted to a 7-bit digital register value Rm[6:0] to program the motor resistance value. The digital register value can be determined as follows:

- 1. Convert the motor resistance ( $R_{PH\_CT}$ ) to a digital value where the LSB is weighted to represent 9.67 m $\Omega$ : Rmdig =  $R_{PH\_CT}$  / 0.00967.

- 2. Encode the digital value such that Rmdig = RMValue[3:0] << RMShift[2:0].

The maximum resistor value,  $R_{PH\_CT}$ , that can be programmed for the DRV10983-Q1 device is 18.5  $\Omega$ , which represents Rmdig = 1920 and an encoded Rm[6:0] value of 0x7Fh. The minimum resistor the DRV10983-Q1 device supports is 0.029  $\Omega$ ,  $R_{PH\_CT}$ , which represents Rmdig = 3.

For convenience, the encoded value for Rm[6:0] can also be obtained from Table 3.

**Table 3. Motor Resistance Look-Up Table**

|          | MShift[2:0],<br>ue[3:0]} | DMV-1[2-0])   |          | R <sub>PH CT</sub> (Ω) | RM[6:0] {RMShift[2:0],<br>RMValue[3:0]} |          |      |                      |

|----------|--------------------------|---------------|----------|------------------------|-----------------------------------------|----------|------|----------------------|

| BINARY   | HEX                      | _ · ·PH_CI (/ | BINARY   | HEX                    |                                         | BINARY   | HEX  | $R_{PH\_CT}(\Omega)$ |

| 000 0000 | 0x00                     | 0             | 0101000  | 0x28                   | 0.3104                                  | 1011000  | 0x58 | 2.4832               |

| 000 0001 | 0x01                     | 0.0097        | 010 1001 | 0x29                   | 0.3492                                  | 101 1001 | 0x59 | 2.7936               |

| 000 0010 | 0x02                     | 0.0194        | 010 1010 | 0x2A                   | 0.388                                   | 101 1010 | 0x5A | 3.104                |

| 000 0011 | 0x03                     | 0.0291        | 010 1011 | 0x2B                   | 0.4268                                  | 101 1011 | 0x5B | 3.4144               |

| 000 0100 | 0x04                     | 0.0388        | 010 1100 | 0x2C                   | 0.4656                                  | 101 1100 | 0x5C | 3.7248               |

| 000 0101 | 0x05                     | 0.0485        | 010 1101 | 0x2D                   | 0.5044                                  | 101 1101 | 0x5D | 4.0352               |

| 000 0110 | 0x06                     | 0.0582        | 010 1110 | 0x2E                   | 0.5432                                  | 101 1110 | 0x5E | 4.3456               |

| 000 0111 | 0x07                     | 0.0679        | 010 1111 | 0x2F                   | 0.582                                   | 101 1111 | 0x5F | 4.656                |

| 000 1000 | 0x08                     | 0.0776        | 011 1000 | 0x38                   | 0.6208                                  | 110 1000 | 0x68 | 4.9664               |

| 000 1001 | 0x09                     | 0.0873        | 011 1001 | 0x39                   | 0.6984                                  | 110 1001 | 0x69 | 5.5872               |

| 000 1010 | 0x0A                     | 0.097         | 011 1010 | 0x3A                   | 0.776                                   | 110 1010 | 0x6A | 6.208                |

| 000 1011 | 0x0B                     | 0.1067        | 011 1011 | 0x3B                   | 0.8536                                  | 110 1011 | 0x6B | 6.8288               |

| 000 1100 | 0x0C                     | 0.1164        | 011 1100 | 0x3C                   | 0.9312                                  | 110 1100 | 0x6C | 7.4496               |

| 000 1101 | 0x0D                     | 0.1261        | 011 1101 | 0x3D                   | 1.0088                                  | 110 1101 | 0x6D | 8.0704               |

| 000 1110 | 0x0E                     | 0.1358        | 011 1110 | 0x3E                   | 1.0864                                  | 110 1110 | 0x6E | 8.6912               |

| 000 1111 | 0x0F                     | 0.1455        | 011 1111 | 0x3F                   | 1.164                                   | 110 1111 | 0x6F | 9.312                |

| 001 1000 | 0x18                     | 0.1552        | 100 1000 | 0x48                   | 1.2416                                  | 111 1000 | 0x78 | 9.9328               |

| 001 1001 | 0x19                     | 0.1746        | 100 1001 | 0x49                   | 1.3968                                  | 111 1001 | 0x79 | 11.1744              |

| 001 1010 | 0x1A                     | 0.194         | 100 1010 | 0x4A                   | 1.552                                   | 111 1010 | 0x7A | 12.416               |

| 001 1011 | 0x1B                     | 0.2134        | 100 1011 | 0x4B                   | 1.7072                                  | 111 1011 | 0x7B | 13.6576              |

| 001 1100 | 0x1C                     | 0.2328        | 100 1100 | 0x4C                   | 1.8624                                  | 111 1100 | 0x7C | 14.8992              |

| 001 1101 | 0x1D                     | 0.2522        | 100 1101 | 0x4D                   | 2.0176                                  | 111 1101 | 0x7D | 16.1408              |

| 001 1110 | 0x1E                     | 0.2716        | 100 1110 | 0x4E                   | 2.1728                                  | 111 1110 | 0x7E | 17.3824              |

| 001 1111 | 0x1F                     | 0.291         | 100 1111 | 0x4F                   | 2.328                                   | 111 1111 | 0x7F | 18.624               |

# 8.4.1.2 Motor Velocity Constant

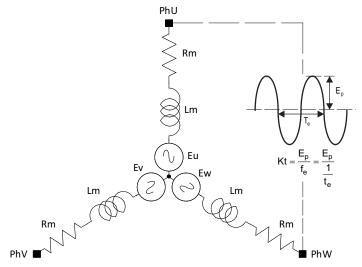

The motor velocity constant, Kt[6:0] describes the phase-to-phase BEMF voltage of the motor as a function of the motor velocity.

Figure 11 shows the measurement technique for this constant as used in the DRV10983-Q1 device.

Figure 11. Kt<sub>PH</sub> Definition

With the motor coasting, use an oscilloscope to capture the differential voltage waveform between any two phases. Derive the motor velocity constant used by the DRV10983-Q1 device as shown in Equation 1.

$$Kt_{PH} = E_p \times t_e$$

where

- E<sub>p</sub> is ½ the peak-to-peak amplitude of the measured voltage

- t<sub>e</sub> is the electrical period

The measured motor velocity constant (Kt<sub>PH</sub>) must be converted to a 7-bit digital register value Kt[6:0] (combination of KtShift[2:0] and KtValue[3:0]) to program the motor velocity constant value. The digital register value can be determined as follows:

- 1. Convert the measured  $Kt_{PH}$  to a weighted digital value:  $Kt_{ph\ dig} = 1090 \times Kt_{PH}$

- 2. Encode the digital value such that Kt<sub>ph dig</sub> = KtValue[3:0] << KtShift[2:0].

The maximum  $Kt_{PH}$  that can be programmed is 1760 mV/Hz. This represents a digital value of 1920 and an encoded Kt[6:0] value of 0x7Fh. The minimum  $Kt_{PH}$  that can be programmed is 0.92 mV/Hz, which represents a digital value of 1 and an encoded Kt[6:0] value of 0x01h.

For convenience, the encoded value of Kt[6:0] may also be obtained from Table 4.

(1)

#### **Table 4. Motor Velocity Constant Look-Up Table**

|          | tShift[2:0],<br>ie[3:0]} | Kt <sub>PH</sub> |          | (tShift[2:0],<br>ie[3:0]} | Kt <sub>PH</sub> | Kt [6:0] {KtShift[2:0],<br>KtValue[3:0]} |      | Kt <sub>PH</sub> |

|----------|--------------------------|------------------|----------|---------------------------|------------------|------------------------------------------|------|------------------|

| BINARY   | HEX                      | (mV/Hz)          | BINARY   | HEX                       | (mV/Hz)          | BINARY                                   | HEX  | (mV/Hz)          |

| 000 0000 | 0x00                     | 0                | 010 1000 | 0x28                      | 29.44            | 101 1000                                 | 0x58 | 235.52           |

| 000 0001 | 0x01                     | 0.92             | 010 1000 | 0x29                      | 33.12            | 101 1000                                 | 0x59 | 264.96           |

| 000 0010 | 0x02                     | 1.84             | 010 1000 | 0x2A                      | 36.8             | 101 1000                                 | 0x5A | 294.4            |

| 000 0011 | 0x03                     | 2.76             | 010 1000 | 0x2B                      | 40.48            | 101 1000                                 | 0x5B | 323.84           |

| 000 0100 | 0x04                     | 3.68             | 010 1000 | 0x2C                      | 44.16            | 101 1000                                 | 0x5C | 353.28           |

| 000 0101 | 0x05                     | 4.6              | 010 1000 | 0x2D                      | 47.84            | 101 1000                                 | 0x5D | 382.72           |

| 000 0110 | 0x06                     | 5.52             | 010 1000 | 0x2E                      | 51.52            | 101 1000                                 | 0x5E | 412.16           |

| 000 0111 | 0x07                     | 6.44             | 010 1000 | 0x2F                      | 55.2             | 101 1000                                 | 0x5F | 441.6            |

| 000 1000 | 0x08                     | 7.36             | 011 1000 | 0x38                      | 58.88            | 110 1000                                 | 0x68 | 471.04           |

| 000 1001 | 0x09                     | 8.28             | 011 1000 | 0x39                      | 66.24            | 110 1000                                 | 0x69 | 529.92           |

| 000 1010 | 0x0A                     | 9.2              | 011 1000 | 0x3A                      | 73.6             | 110 1000                                 | 0x6A | 588.8            |

| 000 1011 | 0x0B                     | 10.12            | 011 1000 | 0x3B                      | 80.96            | 110 1000                                 | 0x6B | 647.68           |

| 000 1100 | 0x0C                     | 11.04            | 011 1000 | 0x3C                      | 88.32            | 110 1000                                 | 0x6C | 706.56           |

| 000 1101 | 0x0D                     | 11.96            | 011 1000 | 0x3D                      | 95.68            | 110 1000                                 | 0x6D | 765.44           |

| 000 1110 | 0x0E                     | 12.88            | 011 1000 | 0x3E                      | 103.04           | 110 1000                                 | 0x6E | 824.32           |

| 000 1111 | 0x0F                     | 13.8             | 011 1000 | 0x3F                      | 110.4            | 110 1000                                 | 0x6F | 883.2            |

| 001 1000 | 0x18                     | 14.72            | 100 1000 | 0x48                      | 117.76           | 111 1000                                 | 0x78 | 942.08           |

| 001 1001 | 0x19                     | 16.56            | 100 1000 | 0x49                      | 132.48           | 111 1000                                 | 0x79 | 1059.84          |

| 001 1010 | 0x1A                     | 18.4             | 100 1000 | 0x4A                      | 147.2            | 111 1000                                 | 0x7A | 1177.6           |

| 001 1011 | 0x1B                     | 20.24            | 100 1000 | 0x4B                      | 161.92           | 111 1000                                 | 0x7B | 1295.36          |

| 001 1100 | 0x1C                     | 22.08            | 100 1000 | 0x4C                      | 176.64           | 111 1000                                 | 0x7C | 1413.12          |

| 001 1101 | 0x1D                     | 23.92            | 100 1000 | 0x4D                      | 191.36           | 111 1000                                 | 0x7D | 1530.88          |

| 001 1110 | 0x1E                     | 25.76            | 100 1000 | 0x4E                      | 206.08           | 111 1000                                 | 0x7E | 1648.64          |

| 001 1111 | 0x1F                     | 27.6             | 100 1000 | 0x4F                      | 220.8            | 111 1000                                 | 0x7F | 1766.4           |

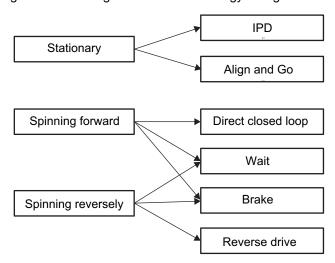

#### 8.4.2 Starting the Motor Under Different Initial Conditions

The motor can be in one of three states when the DRV10983-Q1 device attempts to begin the start-up process. The motor may be stationary, or spinning in the forward or reverse directions. The DRV10983-Q1 device includes a number of features to allow for reliable motor start under all of these conditions. Figure 12 shows the motor start-up flow for each of the three initial motor states.

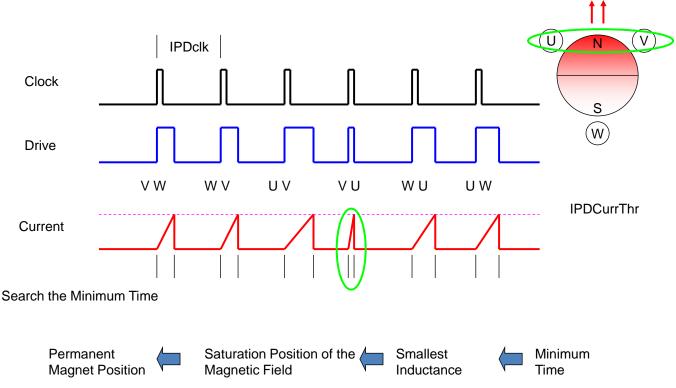

#### 8.4.2.1 Case 1 - Motor is Stationary

If the motor is stationary, the commutation logic must be initialized to be in phase with the position of the motor. The DRV10983-Q1 device provides for two options to initialize the commutation logic to the motor position. Initial position detect (IPD) determines the position of the motor based on the deterministic inductance variation, which is often present in BLDC motors. The *align-and-go* technique forces the motor into alignment by applying a voltage across a particular motor phase to force the motor to rotate in alignment with this phase.

#### 8.4.2.2 Case 2 – Motor is Spinning in the Forward Direction

If the motor is spinning forward with enough velocity, the DRV10983-Q1 device may be configured to go directly into closed loop. By resynchronizing to the spinning motor, the user achieves the fastest possible start-up time for this initial condition.

#### 8.4.2.3 Case 3 – Motor is Spinning in the Reverse Direction

If the motor is spinning in the reverse direction, the DRV10983-Q1 device provides several methods to convert it back to the forward direction.

One method, reverse drive, allows the motor to be driven so that it accelerates through zero velocity. The motor achieves the shortest possible spin-up time in systems where the motor is spinning in the reverse direction.

If this feature is not selected, then the DRV10983-Q1 device may be configured either to wait for the motor to stop spinning or to brake the motor. After the motor has stopped spinning, the motor start-up sequence proceeds as it would for a motor which is stationary.

Take care when using the reverse-drive or brake feature to ensure that the current is limited to an acceptable level and that the supply voltage does not surge as a result of energy being returned to the power supply.

Figure 12. Start the Motor Under Different Initial Conditions

# TEXAS INSTRUMENTS

#### 8.4.3 Motor Start Sequence

Figure 13 shows the motor-start sequence implemented in the DRV10983-Q1 device.

Figure 13. Motor Starting-Up Flow

- **Power-On State** This is the initial power-on state of the motor start sequencer (MSS). The MSS starts in this state on initial power-up or whenever the DRV10983-Q1 device comes out of either standby or sleep mode.

- **ISDen Judgment** After power-on, the DRV10983-Q1 MSS enters the ISDen judgment where it checks to see if the initial speed detect (ISD) function is enabled (ISDen = 1). If ISD is disabled, the MSS proceeds directly to the BrkEn Judgment. If ISD is enabled, the motor start sequence advances to the ISD state.

- **ISD State** The MSS determines the initial condition of the motor (see *Initial Speed Detect*).

- **Speed<ISDThr Judgment** If the motor speed is lower than the threshold defined by ISDThr[1:0], then the motor is considered to be stationary and the MSS proceeds to the BrkEn judgment. If the speed is greater than the threshold defined by ISDThr[1:0], the start sequence proceeds to the Forward judgment.

- **Forward Judgment** The MSS determines whether the motor is spinning in the forward or the reverse direction. If the motor is spinning in the forward direction, the DRV10983-Q1 device executes the resynchronization (see *Motor Resynchronization*) process by transitioning directly into the ClosedLoop state. If the motor is spinning in the reverse direction, the MSS proceeds to the

22

www.ti.com

Speed>RvsDrThr.

- Speed>RvsDrThr Judgment The motor start sequencer checks to see if the reverse speed is greater than the threshold defined by RvsDrThr[1:0]. If it is, then the MSS returns to the ISD state to allow the motor to decelerate. This prevents the DRV10983-Q1 device from attempting to reverse drive or brake a motor that is spinning too quickly. If the reverse speed of the motor is less than the threshold defined by RvsDrThr[1:0], then the MSS advances to the RvsDrEn judgment.

- **RvsDrEn Judgment** The MSS checks to see if the reverse drive function is enabled (RvsDrEn = 1). If it is, the MSS transitions into the RvsDr state. If the reverse drive function is not enabled, the MSS advances to the BrkEn judgment.

- **RvsDr State** The DRV10983-Q1 device drives the motor in the forward direction to force it to rapidly decelerate (see *Reverse Drive*). When it reaches zero velocity, the MSS transitions to the Accelerate state.

- **BrkEn Judgment** The MSS checks to determine whether the brake function is enabled (BrkDoneThr[2:0] ≠ 000). If the brake function is enabled, the MSS advances to the brake state.

- **Brake State** The device performs the brake function (see *Motor Brake*).

- **Time>BrkDoneThr Judgment** The MSS applies brake for a time configured by BRKDoneThr[2:0]. After brake state, the MSS advances to the IPDEn judgment.

- **IPDEn Judgment** The MSS checks to see if IPD has been enabled (IPDCurrThr[3:0] ≠ 0000). If the IPD is enabled, the MSS transitions to the IPD state. Otherwise, it transitions to the align state.

- **Align State** The DRV10983-Q1 device performs the align function (see *Align*). After the align completes, the MSS transitions to the Accelerate state.

- **IPD State** The DRV10983-Q1 device performs the IPD function. The IPD function is described in *IPD*. After the IPD completes, the MSS transitions to the accelerate state.

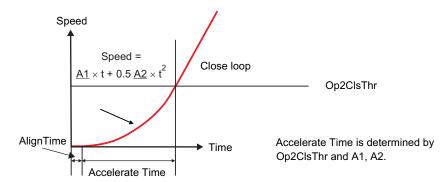

- **Accelerate State** The DRV10983-Q1 device accelerates the motor according to the settings of StAccel and StAccel2. After applying the accelerate settings, the MSS advances to the Speed>Op2ClsThr judgment.

- **Speed>Op2CIsThr Judgment** The motor accelerates until the drive rate exceeds the threshold configured by the Op2CIsThr[4:0] settings. When this threshold is reached, the DRV10983-Q1 device enters into the ClosedLoop state.

- **ClosedLoop State** In this state, the DRV10983-Q1 device drives the motor based on feedback from the commutation control algorithm.

- **DIR Pin Change Judgment** If the DIR pin is changed during any of above states, DRV10983-Q1 device stops driving the motor and restarts from the beginning.

#### 8.4.3.1 Initial Speed Detect

The ISD function is used to identify the initial condition of the motor. If the function is disabled, the DRV10983-Q1 device does not perform the initial speed detect function and treats the motor as if it is stationary.

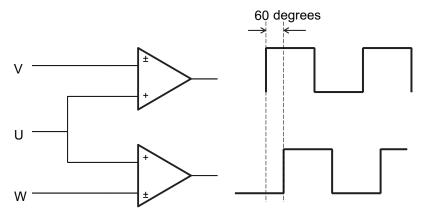

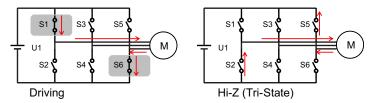

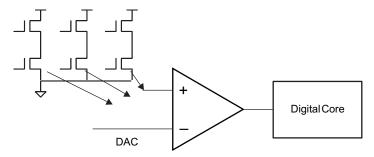

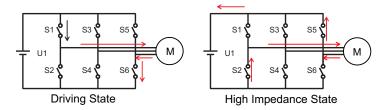

Phase-to-phase comparators are used to detect the zero crossings of the motor's BEMF voltage while it is coasting (motor phase outputs are in the high-impedance state). Figure 14 shows the configuration of the comparators.

Figure 14. Initial Speed Detect Function

If the UW comparator output is lagging the UV comparator by 60°, the motor is spinning forward. If the UW comparator output is leading the UV comparator by 60°, the motor is spinning in reverse.

The motor speed is determined by measuring the time between two rising edges of either of the comparators.

If neither of the comparator outputs toggles for a given amount of time, the condition is defined as stationary. The amount of time can be programmed by setting the register bits ISDThr[1:0].

#### 8.4.3.2 Motor Resynchronization

The resynchronize function works when the ISD function is enabled and determines that the initial state of the motor is spinning in the forward direction. The speed and position information measured during ISD are used to initialize the drive state of the DRV10983-Q1 device, which can transition directly into the closed-loop running state without needing to stop the motor.

#### 8.4.3.3 Reverse Drive

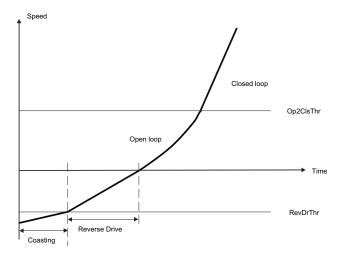

The ISD function measures the initial speed and the initial position; the DRV10983-Q1 reverse drive function acts to reverse accelerate the motor through zero speed and to continue accelerating until the closed loop threshold is reached (see Figure 15). If the reverse speed is greater than the threshold configured in RysDrThr[1:0], then the DRV10983-Q1 device waits until the motor coasts to a speed that is less than the threshold before driving the motor to reverse accelerate.

Figure 15. Reverse Drive Function

SLVSD14 - JUNE 2017

Reverse drive is suitable for applications where the load condition is light at low speed and relatively constant and where the reverse speed is low (that is, a fan motor with little friction). For other load conditions, the motor brake function provides a method for helping force a motor which is spinning in the reverse direction to stop spinning before a normal start-up sequence.

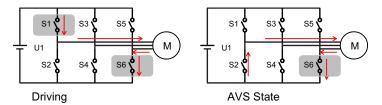

#### 8.4.3.4 Motor Brake

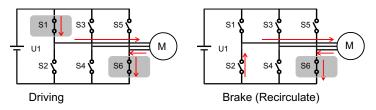

The motor brake function can be used to stop the spinning motor before attempting to start the motor. The brake is applied by turning on all three of the low-side driver FETs.

Brake is enabled by configuring a non-zero BrkDoneThr[2:0]. Brake is applied for a time configured by BrkDoneThr[2:0] (forward or reverse). After the motor is stopped, the motor position is unknown. To proceed with restarting in the correct direction, the IPD or align-and-go algorithm must be implemented. The motor start sequence is the same as it would be for a motor starting in the stationary condition.

The motor brake function can be disabled. The motor skips the brake state and attempts to spin the motor as if it were stationary. If this happens while the motor is spinning in either direction, the start-up sequence may not be successful.

#### 8.4.3.5 Motor Initialization

#### 8.4.3.5.1 Align

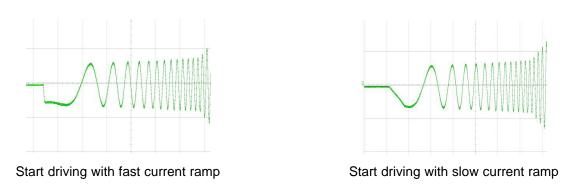

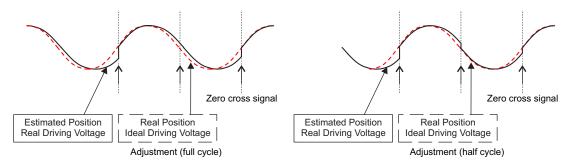

The DRV10983-Q1 device aligns a motor by injecting dc current through a particular phase pattern which is current flowing into phase V, flowing out from phase W for a certain time (configured by AlignTime[2:0]). The current magnitude is determined by OpenLCurr[1:0]. The motor should be aligned at the known position.