### **DS25BR400**

# **Quad Transceiver with Input Equalization and Output De-Emphasis**

### **General Description**

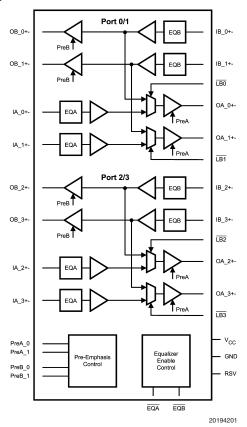

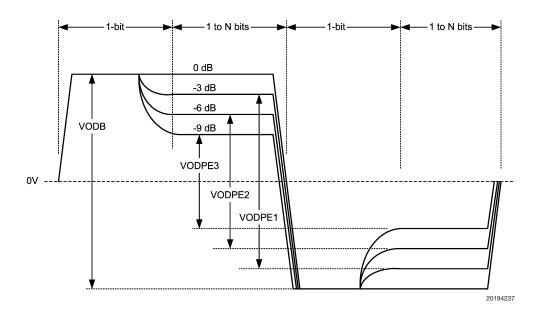

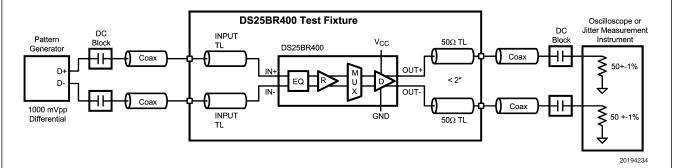

The DS25BR400 is a quad 250 Mbps - 2.5 Gbps CML transceiver, or 8-channel buffer, for use in XAUI Fibre Channel backplane and cable applications. With operation down to 250 Mbps, the DS25BR400 can be used in applications requiring both low and high frequency data rates. Each input stage has a fixed equalizer to reduce ISI distortion from board traces. The equalizers are grouped in fours and are enabled through two control pins. These control pins provide customers flexibility in XAUI applications where ISI distortion may vary from one direction to another. All output drivers have four selectable steps of de-emphasis to compensate against transmission loss across long FR4 backplanes. The de-emphasis blocks are also grouped in fours. In addition, the DS25BR400 also has loopback control capability on four channels. All CML drivers and receivers are internally terminated with  $50\Omega$  pull-up resistors.

#### **Features**

- Quad 2.5 Gbps Transceiver or 8-Channel CML Serial Buffer

- 250 Mbps 2.5 Gbps Fully Differential Data Paths

- Optional Fixed Input Equalization

- Selectable Output De-emphasis

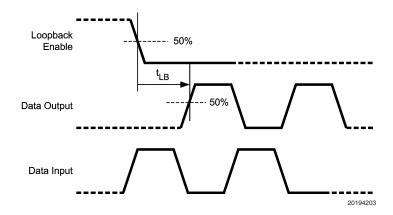

- Individual Loopback Controls

- On-chip Termination

- +3.3V supply

- Low Power, 1.3 Watts MAX

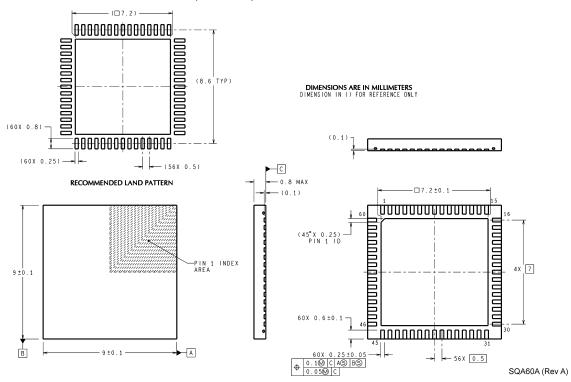

- Lead-less eLLP-60 pin package (9mmx9mmx0.8mm, 0.4mm pitch)

- -40°C to +85°C Industrial Temperature Range

- 6 kV ESD Rating, HBM

### **Functional Block Diagram**

#### **Connection Diagram** PreA\_1 45 PreB\_1 LB1 GND OB\_1+ 43 IB\_1+ GND = DAP OB\_1-42 IB\_1-41 $v_{cc}$ $V_{CC}$ IA\_1+ 40 OA\_1+ 39 IA\_1-OA\_1-60 Pin eLLP 38 GND GND **Top View Shown** 37 IA\_2-OA\_2-IA\_2+ 10 36 OA\_2+ $v_{\rm cc}$ 35 $V_{CC}$ OB\_2-IB\_2-33 OB\_2+ IB\_2+ 32 GND LB2 31 PreA\_0 PreB\_0 15 GND IB\_3-IB\_3+ ر دد GND EQB GND $^{\circ}_{\rm CC}$ OB\_3-LB3

Leadless eLLP-60 Pin Package (9mmx9mmx0.8mm, 0.4mm pitch) Order number DS25BR400TSQ See NS Package Number SQA060 20194202

# **Pin Descriptions**

| Pin Name       | Pin<br>Number | I/O      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------|---------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIFFERENTI     | AL I/O        | •        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| IB_0+          | 51            | I        | Inverting and non-inverting differential inputs of port_0. IB_0+ and IB_0- are internally                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| IB_0-          | 52            |          | connected to a reference voltage through a $50\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| OA_0+          | 48            | 0        | Inverting and non-inverting differential outputs of port_0. OA_0+ and OA_0- are connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| -0_AC          | 49            |          | to $V_{CC}$ through a $50\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| B_1+           | 43            | I        | Inverting and non-inverting differential inputs of port_1. IB_1+ and IB_1- are internally                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| B_1-           | 42            |          | connected to a reference through a $50\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| OA_1+          | 40            | 0        | Inverting and non-inverting differential outputs of port_1. OA_1+ and OA_1- are connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OA_1-          | 39            |          | to $V_{CC}$ through a $50\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| B_2+           | 33            | ı        | Inverting and non-inverting differential inputs of port_2. IB_2+ and IB_2- are internally                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| B_2-           | 34            |          | connected to a reference voltage through a $50\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| OA_2+          | 36            | 0        | Inverting and non-inverting differential outputs of port_2. OA_2+ and OA_2- are connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DA_2-          | 37            |          | to $V_{CC}$ through a $50\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| B_3+           | 25            | 1        | Inverting and non-inverting differential inputs of port_3. IB_3+ and IB_3- are internally                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| B_3-           | 24            |          | connected to a reference voltage through a $50\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <br>DA_3+      | 28            | 0        | Inverting and non-inverting differential outputs of port_3. OA_3+ and OA_3- are connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DA_3-          | 27            |          | to $V_{CC}$ through a 50 $\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| A_0+           | 58            | 1        | Inverting and non-inverting differential inputs of port_0. IA_0+ and IA_0- are internally                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| A_0-           | 57            | ١.       | connected to a reference voltage through a $50\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| OB_0+          | 55            | 0        | Inverting and non-inverting differential outputs of port_0. OB_0+ and OB_0- are connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OB_0+<br>OB_0- | 54            |          | to $V_{CC}$ through a 50 $\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                |               |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| A_1+           | 6<br>7        | '        | Inverting and non-inverting differential inputs of port_1. IA_1+ and IA_1- are internally                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| A_1-           |               |          | connected to a reference through a $50\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| OB_1+          | 3             | 0        | Inverting and non-inverting differential outputs of port_1. OB_1+ and OB_1- are connected to M_ at the content of the content  |

| OB_1-          | 4             | <u> </u> | to V <sub>CC</sub> through a 50Ω resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A_2+           | 10            | '        | Inverting and non-inverting differential inputs of port_2. IA_2+ and IA_2- are internally                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| A_2-           | 9             |          | connected to a reference voltage through a $50\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| OB_2+          | 13            | 0        | Inverting and non-inverting differential outputs of port_2. OB_2+ and OB_2- are connected to the connected t |

| OB_2-          | 12            |          | to V <sub>CC</sub> through a 50Ω resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A_3+           | 18            | I        | Inverting and non-inverting differential inputs of port_3. IA_3+ and IA_3- are internally                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| IA_3-          | 19            |          | connected to a reference voltage through a $50\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| OB_3+          | 21            | 0        | Inverting and non-inverting differential outputs of port_3. OB_3+ and OB_3- are connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OB_3-          | 28            |          | to V <sub>CC</sub> through a 50Ω resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                | 3.3V LVCMOS   | )        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| EQA            | 60            | I        | This pin is active LOW. A logic LOW at EQA enables equalization for input channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |