# **DS25MB100** 2.5 Gbps 2:1/1:2 CML Mux/Buffer with Transmit De-**Emphasis and Receive Equalization**

## **General Description**

www

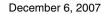

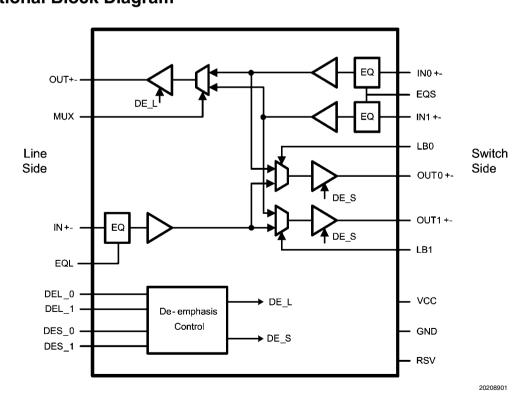

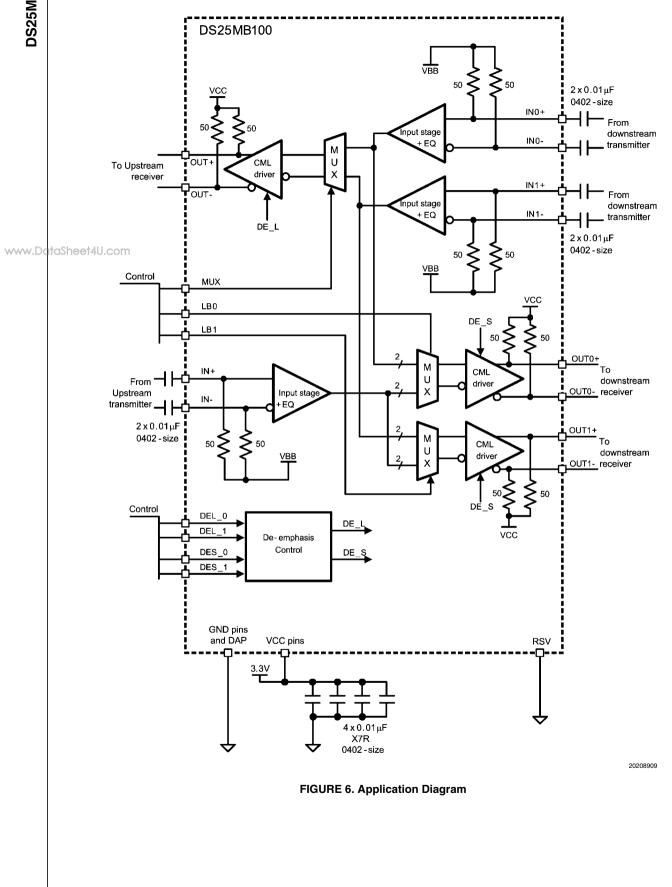

The DS25MB100 is a signal conditioning 2:1 multiplexer and 1:2 fan-out buffer designed for use in backplane redundancy or cable driving applications. Signal conditioning features include input equalization and programmable output de-emphasis that enable data communication in FR4 backplane up to 2.5 Gbps. Each input stage has a fixed equalizer to reduce ISI distortion from board traces. All output drivers have four selectable levels of de-emphasis to compensate for transmission losses from long FR4 backplane or cable attenuation reducing deterministic jitter. The de-emphasis levels can be independently controlled for the line-side and switch-side drivers. The internal loopback paths from switch-side input to switch-side output enable at-speed system testing. All receiver inputs and driver outputs are internally terminated with  $100\Omega$  differential terminating resistors.

### Features

- 2:1 multiplexer and 1:2 buffer

- 0.25-2.5 Gbps fully differential data paths

- Fixed input equalization

- Programmable output de-emphasis

- Independent de-emphasis controls -

- Programmable loopback modes

- -**On-chip terminations**

- HBM ESD rating 5.5 kV on all pins

- +3.3V supply

- Low power, 0.45 W typical

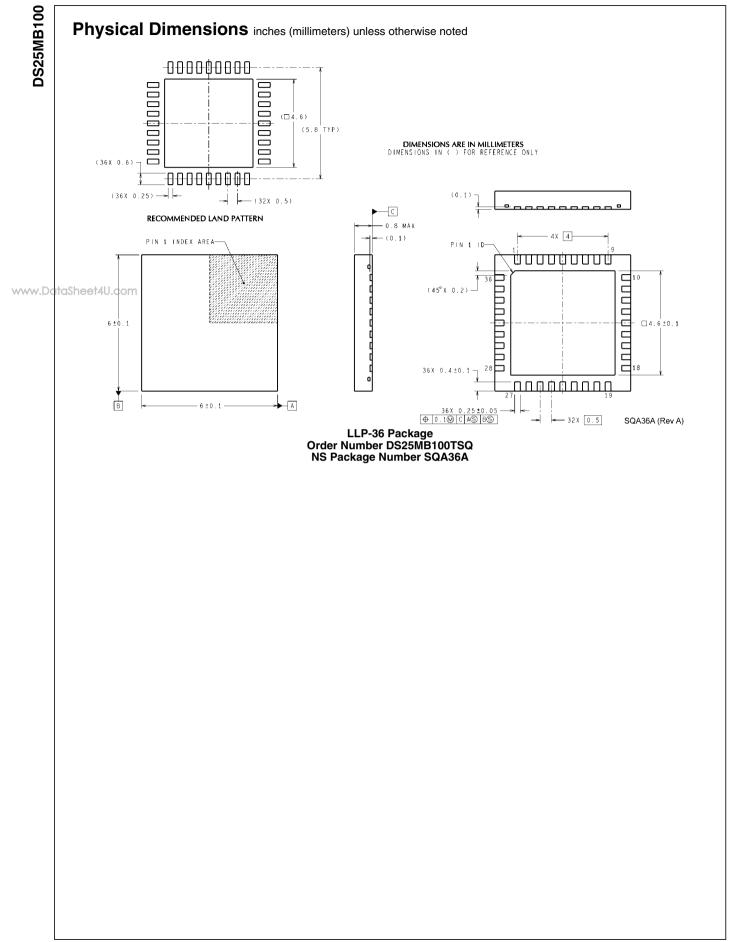

- Lead-less LLP-36 package

- -40°C to +85°C operating temperature range

## Applications

- Backplane or cable driver

- Redundancy and signal conditioning applications

- CPRI/OBSAI

# Functional Block Diagram

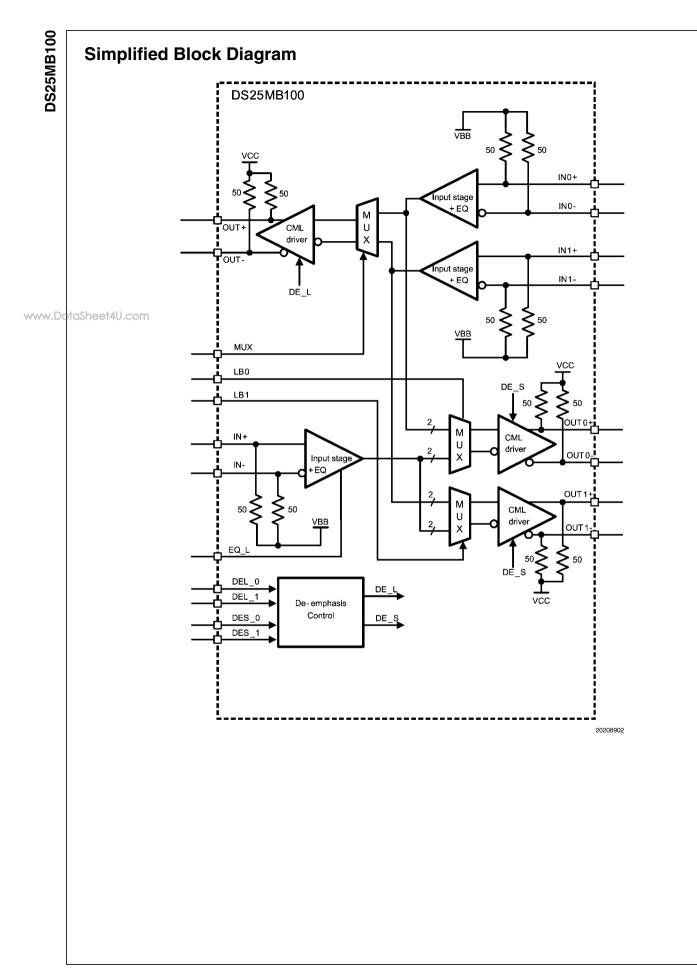

# **Pin Descriptions**

| Pin Name F        | Pin Number          | I/O   | Description                                                                                                                                     |

|-------------------|---------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| LINE SIDE HIG     | H SPEED DI          | FFERE | ENTIAL IO'S                                                                                                                                     |

| IN+               | 33                  | Ι     | Inverting and non-inverting differential inputs at the line side. IN+ and IN– have an internal $50\Omega$                                       |

| IN–               | 34                  |       | connected to an internal reference voltage.                                                                                                     |

| OUT+              | 30                  | 0     | Inverting and non-inverting differential outputs at the line side. OUT+ and OUT- have an international outputs at the line side.                |

| OUT-              | 31                  |       | 50Ω connected to $V_{CC}$ .                                                                                                                     |

| SWITCH SIDE       | HIGH SPEED          | DIFF  | ERENTIAL IO's                                                                                                                                   |

| OUT0+             | 3                   | 0     | Inverting and non-inverting differential outputs of mux0 at the switch side. OUT0+ and OUT0- hav                                                |

| OUT0-             | 4                   |       | an internal 50 $\Omega$ connected to V <sub>CC</sub> .                                                                                          |

| OUT1+             | 22                  | 0     | Inverting and non-inverting differential outputs of mux1 at the switch side. OUT1+ and OUT1- hav                                                |

| OUT1-             | 21                  |       | an internal 50 $\Omega$ connected to V <sub>CC</sub> .                                                                                          |

| IN0+              | 6                   | Ι     | Inverting and non-inverting differential inputs to the mux at the switch side. IN0+ and IN0- have                                               |

| INO-              | 7                   |       | an internal 50 $\Omega$ connected to an internal reference voltage.                                                                             |

| tashteet4U.com    | 25                  | I     | Inverting and non-inverting differential inputs to the mux at the switch side. IN1+ and IN1- have                                               |

| IN1–              | 24                  |       | an internal 50 $\Omega$ connected to an internal reference voltage.                                                                             |

| CONTROL (3.3      | V LVCMOS)           |       |                                                                                                                                                 |

| MUX               | 19                  | I     | A logic low at MUX_S0 selects mux_0 to switch B. MUX_S0 is internally pulled high. Default state for mux_0 is switch A.                         |

| EQL               | 11                  | 1     | A logic low enables the EQ. EQL is internally pulled high. Default is with EQ disabled.                                                         |

| EQS               | 36                  |       | A logic low chables the EQ. EQS is internally pulled high. Default is with EQ disabled.                                                         |

| DEL_0             | 18                  |       | DEL_0 and DEL_1 select the output de-emphasis of the line side drivers (OUT±).                                                                  |

| DEL_0             | 27                  | '     | DEL_0 and DEL_1 are internally pulled high.                                                                                                     |

| DES_0             | 10                  | 1     | DES_0 and DES_1 select the output de-emphasis of the switch side drivers (OUT0±, OUT1±).                                                        |

| DES_1             | 1                   | •     | DES_0 and DES_1 are internally pulled high.                                                                                                     |

| LB0               | 28                  |       | A logic low at LB0 enables the internal loopback path from $IN0\pm$ to $OUT0\pm$ . LB0 is internally pulle high.                                |

| LB1               | 26                  | I     | A logic low at LB1 enables the internal loopback path from $IN1\pm to OUT1\pm$ . LB1 is internally pulle high.                                  |

| RSV               | 17                  | I     | Reserve pin to support factory testing. This pin can be left open, or tied to GND, or tied to GND through an external pull-down resistor.       |

| POWER             |                     |       |                                                                                                                                                 |

| V <sub>CC</sub> 5 | , 13, 15, 23,<br>32 | Ρ     | $V_{CC}$ = 3.3V ± 5%. The maximum current consumption under worst voltage, temperature, and process variation conditions does not exceed 170mA. |

|                   | 02                  |       | Each $V_{CC}$ pin should be connected to the $V_{CC}$ plane through a low inductance path, typically wi                                         |

|                   |                     |       | a via located as close as possible to the landing pad of the $V_{CC}$ pin.                                                                      |

|                   |                     |       | It is recommended to have a 0.01 $\mu$ F or 0.1 $\mu$ F, X7R, size-0402 bypass capacitor from each V <sub>c</sub>                               |

|                   |                     |       | pin to ground plane.                                                                                                                            |

| GND               | 2, 8, 9, 12,        | Р     | Ground reference. Each ground pin should be connected to the ground plane through a low                                                         |

|                   | 14, 16, 20,         |       | inductance path, typically with a via located as close as possible to the landing pad of the GND                                                |

|                   | 29, 35              |       | pin.                                                                                                                                            |

| GND               | DAP                 | Р     | DAP is the metal contact at the bottom side, located at the center of the LLP package. It should                                                |

|                   |                     |       | be connected to the GND plane with at least 16 via to lower the ground impedance and improv                                                     |

|                   |                     |       | the thermal performance of the package.                                                                                                         |

Note: I=Input, O=Output, P=Power

## **Functional Description**

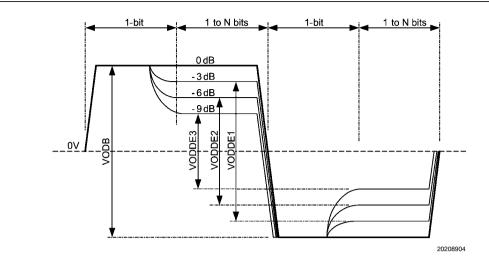

The DS25MB100 is a signal conditioning 2:1 multiplexer and a 1:2 buffer designed to support port redundancy up to 2.5 Gbps. Each input stage has a fixed equalizer that provides equalization to compensate about 5 dB of transmission loss from a short backplane trace (about 10 inches backplane). The output driver has de-emphasis (driver-side equalization) to compensate the transmission loss of the backplane that it is driving. The driver conditions the output signal such that the lower frequency and higher frequency pulses reach approximately the same amplitude at the end of the backplane, and minimize the deterministic jitter caused by the amplitude disparity. The DS25MB100 provides four steps of user-selectable de-emphasis ranging from 0, -3, -6 and -9 dB to handle different lengths of backplane. Figure 1 shows a driver de-emphasis waveform. The de-emphasis duration is 188ps nominal, corresponds to 0.47 bit-width at 2.5 Gbps. The deemphasis levels of switch-side and line-side can be individually programmed.

The high speed inputs are self-biased to about 1.3V and are designed for AC coupling. The inputs are compatible to most

AC coupling differential signals such as LVDS, LVPECL and CML.

#### TABLE 1. Logic Table For Multiplex Controls

| MUX_S0    | Mux Function                   |

|-----------|--------------------------------|

| 0         | MUX select switch input, IN1±. |

| 1         | MUX select switch input, IN0±. |

| (default) |                                |

#### **TABLE 2. Logic Table For Loopback Controls**

| LB0       | Loopback Function                   |

|-----------|-------------------------------------|

| 0         | Enable loopback from IN0± to OUT0±. |

| 1         | Normal mode. Loopback disabled.     |

| (default) |                                     |

| LB1       | Loopback Function                   |

| 0         | Enable loopback from IN1± to OUT1±. |

| 1         | Normal mode. Loopback disabled.     |

| (default) |                                     |

#### **TABLE 3. Line-Side De-Emphasis Controls**

| DEL_[1:0]     | De-Emphasis<br>Level in mV <sub>PP</sub><br>(VODB) | De-Emphasis<br>Level in mV <sub>PP</sub><br>(VODPE) | De-Emphasis in dB<br>(VODPE/VODB) | Typical FR4 Board Trace |

|---------------|----------------------------------------------------|-----------------------------------------------------|-----------------------------------|-------------------------|

| 00            | 1300                                               | 1300                                                | 0                                 | 10 inches               |

| 01            | 1300                                               | 920                                                 | -3                                | 20 inches               |

| 10            | 1300                                               | 650                                                 | -6                                | 30 inches               |

| 1 1 (default) | 1300                                               | 461                                                 | -9                                | 40 inches               |

#### TABLE 4. Switch-Side De-Emphasis Controls

| DES_[1:0]     | De-Emphasis<br>Level in mV <sub>PP</sub><br>(VODB) | De-Emphasis<br>Level in mV <sub>PP</sub><br>(VODPE) | De-Emphasis in dB<br>(VODPE/VODB) | Typical FR4 Board Trace |

|---------------|----------------------------------------------------|-----------------------------------------------------|-----------------------------------|-------------------------|

| 00            | 1300                                               | 1300                                                | 0                                 | 10 inches               |

| 01            | 1300                                               | 920                                                 | -3                                | 20 inches               |

| 10            | 1300                                               | 650                                                 | -6                                | 30 inches               |

| 1 1 (default) | 1300                                               | 461                                                 | -9                                | 40 inches               |

#### TABLE 5. EQ Controls For Line And Switch Sides

| EQL/EQS     | Loopback Function                   |

|-------------|-------------------------------------|

| 0           | Enable equalization.                |

| 1 (default) | Normal mode. Equalization disabled. |

FIGURE 1. Driver De-Emphasis Differential Waveform (Showing All 4 De-Emphasis Steps)

www.DataSheet4U.com

## Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage (V <sub>CC</sub> )          | –0.3V to 4V                      |

|--------------------------------------------|----------------------------------|

| CMOS/TTL Input Voltage                     | –0.3V to (V <sub>CC</sub> +0.3V) |

| CML Input/Output Voltage                   | –0.3V to (V <sub>CC</sub> +0.3V) |

| Junction Temperature                       | +150°C                           |

| Storage Temperature                        | –65°C to +150°C                  |

| Lead Temperature                           |                                  |

| Soldering, 4 seconds                       | +260°C                           |

| Thermal Resistance, $\theta_{JA}$ (Note 8) | 26.2°C/W                         |

| Thermal Resistance, $\theta_{JC-top}$      | 3.3°C/W                          |

| Thermal Resistance, $\Phi_{JB}$ | 11.1°C/W |

|---------------------------------|----------|

| ESD Rating (Note 10)            |          |

| HBM, 1.5 kΩ, 100 pF             | 6 kV     |

| CDM                             | 1.25 kV  |

| MM                              | 350V     |

|                                          | Min       | Тур | Мах   | Units     |

|------------------------------------------|-----------|-----|-------|-----------|

| Supply Voltage (V <sub>CC</sub> -GND)    | 3.13<br>5 | 3.3 | 3.465 | V         |

| Supply Noise Amplitude<br>10 Hz to 2 GHz |           |     | 100   | $mV_{PP}$ |

| Ambient Temperature                      | -40       |     | 85    | °C        |

| Case Temperature                         |           |     | 100   | °C        |

## **Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol            | Parameter                                                               | Conditions                                                                                                                                                                                                                                                                                               | Min        | Typ<br>(Note 2)     | Max                     | Units                                  |

|-------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------|-------------------------|----------------------------------------|

| LVCMOS            | DC SPECIFICATIONS                                                       |                                                                                                                                                                                                                                                                                                          |            |                     |                         |                                        |

| V <sub>IH</sub>   | High Level Input Voltage                                                |                                                                                                                                                                                                                                                                                                          | 2.0        |                     | V <sub>CC</sub><br>+0.3 | V                                      |

| V <sub>IL</sub>   | Low Level Input Voltage                                                 |                                                                                                                                                                                                                                                                                                          | -0.3       |                     | 0.8                     | V                                      |

| I <sub>IH</sub>   | High Level Input Current                                                | $V_{IN} = V_{CC}$                                                                                                                                                                                                                                                                                        | -10        |                     | 10                      | μA                                     |

| I <sub>IL</sub>   | Low Level Input Current                                                 | V <sub>IN</sub> = GND                                                                                                                                                                                                                                                                                    | 75         | 94                  | 124                     | μA                                     |

| R <sub>PU</sub>   | Pull-High Resistance                                                    |                                                                                                                                                                                                                                                                                                          |            | 35                  |                         | kΩ                                     |

| RECEIVE           | R SPECIFICATIONS                                                        | •                                                                                                                                                                                                                                                                                                        |            |                     |                         |                                        |

| V <sub>ID</sub>   | Differential Input Voltage<br>Range (Note 9)                            | AC Coupled Differential Signal<br>Below 1.25 Gbps<br>Above 1.25 Gbps<br>This parameter is not tested at production                                                                                                                                                                                       | 100<br>100 |                     | 1750<br>1560            | mV <sub>P-P</sub><br>mV <sub>P-P</sub> |

| V <sub>ICM</sub>  | Common Mode Voltage at Receiver Inputs                                  | Measured at receiver inputs reference to ground                                                                                                                                                                                                                                                          |            | 1.3                 |                         | v                                      |

| R <sub>ITD</sub>  | Input Differential<br>Termination (Note 3)                              | On-chip differential termination between IN+ or IN-                                                                                                                                                                                                                                                      | 84         | 100                 | 116                     | Ω                                      |

| R <sub>ITSE</sub> | Input Termination (single-<br>end)                                      | On-chip termination IN+ or IN– to GND for frequency<br>> 100 MHz                                                                                                                                                                                                                                         |            | 50                  |                         | Ω                                      |

| DRIVER \$         | SPECIFICATIONS                                                          |                                                                                                                                                                                                                                                                                                          |            | •                   |                         |                                        |

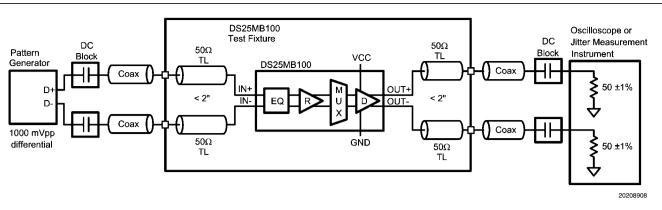

| VODB              | Output Differential<br>Voltage Swing<br>withoutdDe-Emphasis<br>(Note 4) | $R_L = 100\Omega \pm 1\%$<br>DES_1=DES_0=0<br>DEL_1=DEL_0=0<br>Driver De-emphasis disabled<br>Running K28.7 pattern at 2.5 Gbps<br>See <i>Figure 5</i> for test circuit.                                                                                                                                 | 1100       | 1300                | 1500                    | mV <sub>P-P</sub>                      |

| V <sub>DE</sub>   | Output De-Emphasis<br>Voltage Ratio<br>20*log(VDODPE/VODB)              | $R_L = 100\Omega \pm 1\%$<br>Running K28.7 pattern at 2.5 Gbps<br>$DEx_[1:0]=00$<br>$DEx_[1:0]=01$<br>$PREx_[1:0]=10$<br>$DEx_[1:0]=11$<br>x=S for switch side de-emphasis control<br>x=L for line side de-emphasis control<br>See <i>Figure 1</i> on waveform.<br>See <i>Figure 5</i> for test circuit. |            | 0<br>-3<br>-6<br>-9 |                         | dB<br>dB<br>dB<br>dB                   |

| Symbol                      | Parameter                                     | Conditions                                                                                                                                                                          | Min  | Typ<br>(Note 2) | Max         | Unit         |

|-----------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------|-------------|--------------|

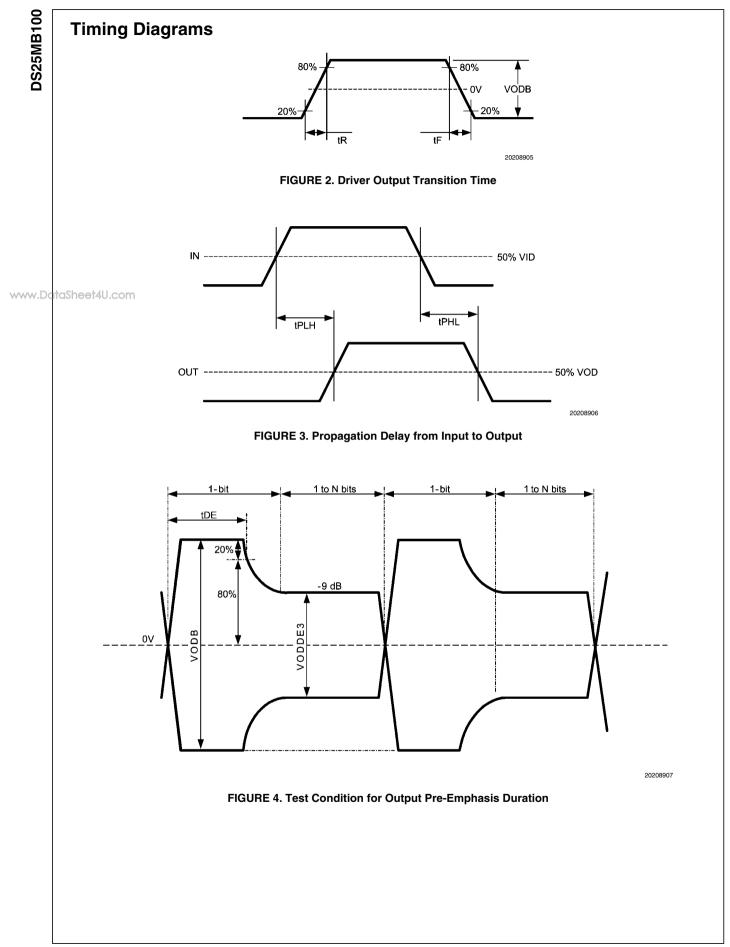

| T <sub>DE</sub>             | De-Emphasis Width                             | Tested at –9 dB de-emphasis level, DEx[1:0]=11<br>x=S for switch side de-emphasis control<br>x=L for line side de-emphasis control<br>See <i>Figure 4</i> on measurement condition. | 125  | 188             | 250         | ps           |

| R <sub>OTSE</sub>           | Output Termination (Note 3)                   | On-chip termination from OUT+ or OUT– to $\rm V_{\rm CC}$                                                                                                                           | 42   | 50              | 58          | Ω            |

| R <sub>OTD</sub>            | Output Differential<br>Termination            | On-chip differential termination between OUT+ and OUT-                                                                                                                              |      | 100             |             | Ω            |

| $\Delta R_{OTSE}$           | Mis-Match in Output<br>Termination Resistors  | Mis-match in output terminations at OUT+ and OUT-                                                                                                                                   |      |                 | 5           | %            |

| V <sub>OCM</sub>            | Output Common Mode<br>Voltage                 |                                                                                                                                                                                     |      | 2.7             |             | V            |

| POWER                       | DISSIPATION                                   |                                                                                                                                                                                     |      |                 |             |              |

| P <sub>D</sub><br>taSheet4U | Power Dissipation<br>com                      | $V_{DD} = 3.3V @ 25^{\circ}C$<br>All outputs terminated by 100 $\Omega \pm 1\%$ .<br>DEL_[1:0]=0, DES_[1:0]=0<br>Running PRBS 2 <sup>7</sup> -1 pattern at 2.5 Gbps                 |      | 0.45            |             | W            |

| AC CHAF                     | ACTERISTICS                                   |                                                                                                                                                                                     |      |                 |             |              |

| t <sub>R</sub>              | Differential Low to High<br>Transition Time   | Measured with a clock-like pattern at 2.5 Gbps,<br>between 20% and 80% of the differential output                                                                                   |      | 100             |             | ps           |

| t <sub>F</sub>              | Differential High to Low<br>Transition Time   | voltage. de-emphasis disabled<br>Transition time is measured with fixture as shown in<br><i>Figure 5</i> , adjusted to reflect the transition time at the<br>output pins            |      | 100             |             | ps           |

| t <sub>PLH</sub>            | Differential Low to High<br>Propagation Delay | Measured at 50% differential voltage from input to output                                                                                                                           |      |                 | 1           | ns           |

| t <sub>PHL</sub>            | Differential High to Low<br>Propagation Delay |                                                                                                                                                                                     |      |                 | 1           | ns           |

| t <sub>SKP</sub>            | Pulse Skew                                    | It <sub>PHL</sub> t <sub>PLH</sub> I                                                                                                                                                |      |                 | 20          | ps           |

| t <sub>sko</sub>            | Output Skew<br>(Note 7)                       | Difference in propagation delay between two outputs in the same device                                                                                                              |      |                 | 100         | ps           |

| t <sub>SKPP</sub>           | Part-to-Part Skew                             | Difference in propagation delay between the same<br>output from devices operating under identical<br>conditions                                                                     |      |                 | 100         | ps           |

| t <sub>SM</sub>             | Mux Switch Time                               | Measured from $V_{\rm IH}$ or $V_{\rm IL}$ of the mux-control or loopback control to 50% of the valid differential output                                                           |      | 1.8             | 6           | ns           |

| RJ                          | Device Random Jitter<br>(Note 5)              | See <i>Figure 5</i> for test circuit.<br>Alternating-1-0 pattern<br>EQ and de-emphasis disabled.<br>At 0.25 Gbps<br>At 1.25 Gbps<br>At 2.5 Gbps                                     |      |                 | 2<br>2<br>2 | psrm<br>psrm |

| DJ                          | Device Deterministic Jitter<br>(Note 6)       | See <i>Figure 5</i> for test circuit.<br>EQ and de-emphasis disabled<br>Between 0.25 and 2.5 Gbps with PRBS7 pattern for<br>DS25MB100 @ -40°C to 85°C                               |      |                 | 35          | Psp          |

| DR                          | Data Rate (Note 9)                            | Tested with alternating-1-0 pattern                                                                                                                                                 | 0.25 |                 | 2.5         | Gbp          |

Note 1: "Absolute Maximum Ratings" are the ratings beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits.

Note 2: Typical parameters measured at  $V_{CC} = 3.3V$ ,  $T_A = 25^{\circ}C$ , and represent most likely parametric norms at the time of product characterization. The typical specifications are not guaranteed.

**Note 3:** IN+ and IN- are generic names refer to one of the many pairs of complimentary inputs of the DS25MB100. OUT+ and OUT- are generic names refer to one of the many pairs of the complimentary outputs of the DS25MB100. Differential input voltage  $V_{ID}$  is defined as IIN+-IN-I. Differential output voltage  $V_{OD}$  is defined as IOUT+-OUT-I.

Note 4: K28.7 pattern is a 10-bit repeating pattern of K28.7 code group {001111 1000}

K28.5 pattern is a 20-bit repeating pattern of +K28.5 and -K28.5 code groups {110000 0101 001111 1010}

**Note 5:** Device output random jitter is a measurement of the random jitter contribution from the device. It is derived by the equation  $sqrt(RJ_{OUT}^2 - RJ_{IN}^2)$ , where  $RJ_{OUT}$  is the total random jitter measured at the output of the device in psrms,  $RJ_{IN}$  is the random jitter of the pattern generator driving the device.

Note 6: Device output deterministic jitter is a measurement of the deterministic jitter contribution from the device. It is derived by the equation (DJ<sub>OUT</sub>-DJ<sub>IN</sub>), where DJ<sub>OUT</sub> is the total peak-to-peak deterministic jitter measured at the output of the device in pspp, DJ<sub>IN</sub> is the peak-to-peak deterministic jitter of the pattern generator driving the device.

**Note 7:**  $t_{SKO}$  is the magnitude difference in the propagation delays among data paths between switch A and switch B of the same port and similar data paths between port 0 and port 1. An example is the output skew among data paths from SIA\_0± to LO\_0±, SIB\_0± to LO\_0±, SIA\_1± to LO\_1± and SIB\_1± to LO\_1±. Another example is the output skew among data paths from L\_0± to SOA\_0±, LI\_0± to SOB\_0±, LI\_1± to SOA\_1± and LI\_1± to SOB\_1±.  $t_{SKO}$  also refers to the delay skew of the loopback paths of the same port and between similar data paths between port 0 and port 1. An example is the output skew among data paths from L\_0± to SOA\_0±, LI\_0± to SOB\_0±, LI\_1± to SOA\_1± and LI\_1± to SOB\_1±.  $t_{SKO}$  also refers to the delay skew of the loopback paths of the same port and between similar data paths between port 0 and port 1. An example is the output skew among data paths SIA\_0± to SOA\_0±, SIB\_0± to SOB\_0±, SIA\_1± to SOA\_1± and SIB\_1± to SOB\_1±.

Note 8: Thermal resistances are based on having 16 thermal relief vias on the DAP pad under the 0 airflow condition.

Note 9: This parameter is guaranteed by design and/or characterization. It is not tested in production.

Note 10: ESD tests conform to the following standards:

Human Body Model applicable standard: MIL-STD-883, Method 3015.7

Machine Model applicable standard: JESD22-A115-A (ESD MM standard of JEDEC)

Field-induced Charge Device Model: Applicable standard JESD22-C101-C (ESD FICDM standard of JEDEC)

www.DataSheet4U.com

www.DataSheet4U.com

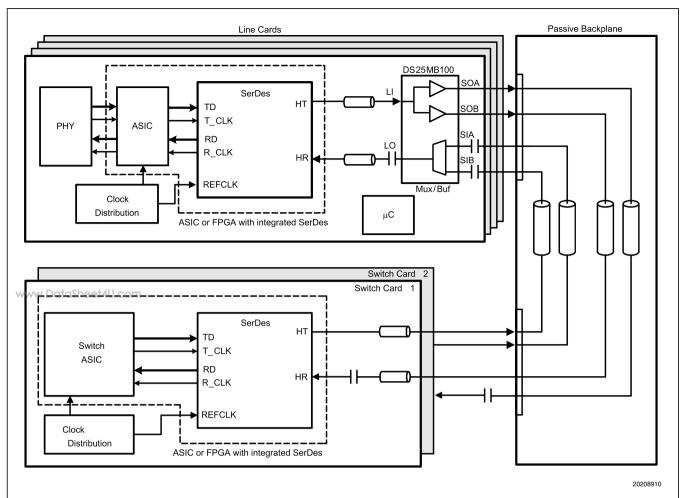

# **Application Information**

FIGURE 7. Chassis Based Network Switch System With Redundancy

# Notes

www.DataSheet4U.com

DS25MB100

# Notes

| Products                       |                              | Design Support          |                                |

|--------------------------------|------------------------------|-------------------------|--------------------------------|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH                 | www.national.com/webench       |

| Audio                          | www.national.com/audio       | Analog University       | www.national.com/AU            |

| Clock Conditioners             | www.national.com/timing      | App Notes               | www.national.com/appnotes      |

| Data Converters                | www.national.com/adc         | Distributors            | www.national.com/contacts      |

| Displays                       | www.national.com/displays    | Green Compliance        | www.national.com/quality/green |

| Ethernet                       | www.national.com/ethernet    | Packaging               | www.national.com/packaging     |

| Interface                      | www.national.com/interface   | Quality and Reliability | www.national.com/quality       |

| LVDS                           | www.national.com/lvds        | Reference Designs       | www.national.com/refdesigns    |

| Power Management               | www.national.com/power       | Feedback                | www.national.com/feedback      |

| Switching Regulators           | www.national.com/switchers   |                         |                                |

| LDOs                           | www.national.com/ldo         |                         |                                |

| LED Lighting                   | www.national.com/led         |                         |                                |

| PowerWise                      | www.national.com/powerwise   |                         |                                |

| Serial Digital Interface (SDI) | www.national.com/sdi         |                         |                                |

| Temperature Sensors            | www.national.com/tempsensors |                         |                                |

| Wireless (PLL/VCO)             | www.national.com/wireless    |                         |                                |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2007 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530-85-86 Email: europe.support@nsc.com Deutsch Tei: +49 (0) 69 9508 6208 English Tei: +49 (0) 870 24 0 2171 Français Tei: +33 (0) 1 41 91 8790 National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560