# DS90LV011A 3V LVDS Single High Speed Differential Driver

#### **General Description**

www.Dat

The DS90LV011A is a single LVDS driver device optimized for high data rate and low power applications. The DS90LV011A is a current mode driver allowing power dissipation to remain low even at high frequency. In addition, the short circuit fault current is also minimized. The device is designed to support data rates in excess of 400Mbps (200MHz) utilizing Low Voltage Differential Signaling (LVDS) technology.

The device is in both a 5-lead small outline transistor package and a new LLP-8 package with a 3mm x 3mm body size. The LVDS outputs have been arranged for easy PCB layout. The differential driver outputs provide low EMI with its typical low output swing of 350 mV. The DS90LV011A can be paired with its companion single line receiver, the DS90LV012A, or with any of National's LVDS receivers, to provide a high-speed LVDS interface.

#### **Features**

- Conforms to TIA/EIA-644-A Standard

- >400Mbps (200MHz) switching rates

- 700 ps (100 ps typical) maximum differential skew

- 1.5 ns maximum propagation delay

- Single 3.3V power supply

- ±350 mV differential signaling

- Power Off Protection (outputs in TRI-STATE)

- Pinout simplifies PCB layout

- Low power dissipation (23 mW @ 3.3V typical)

- SOT-23 5-lead package

- Leadless LLP-8 package (3x3 mm body size)

- SOT-23 version pin compatible with SN65LVDS1

- Fabricated with advanced CMOS process technology

- Industrial temperature operating range (-40°C to +85°C)

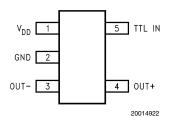

#### **Connection Diagrams**

(Top View) Order Number DS90LV011ATMF See NS Package Number MF05A

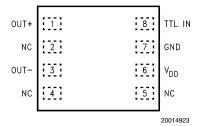

(Top View)

Order Number DS90LV011ATLD

See NS Package Number LDA08A

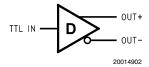

# **Functional Diagram**

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

-0.3V to +4VSupply Voltage (V<sub>DD</sub>) LVCMOS input voltage (TTL IN) -0.3V to +3.6VLVDS output voltage (OUT±) -0.3V to +3.9VLVDS output short circuit current 24mA

Maximum Package Power Dissipation @ +25°C

LDA Package 2.26 W Derate LDA Package 18.1 mW/°C above +25°C Thermal resistance  $(\theta_{IA})$ 55.3°C/Watt MF Package 902 mW 7.22 mW/°C above +25°C Derate MF Package

Thermal resistance ( $\theta_{JA}$ ) 138.5°C/Watt Storage Temperature -65°C to +150°C

Lead Temperature Range Soldering

+260°C (4 sec.)

Maximum Junction

Temperature +150°C

**ESD** Ratings

HBM (1.5 k $\Omega$ , 100 pF) ≥ 9kV EIAJ (0 Ω, 200 pF) ≥ 900V CDM (0 Ω, 0 pF) ≥ 2000V IEC direct (330  $\Omega$ , 150 pF)  $\geq 4kV$

### **Recommended Operating Conditions**

|                                   | Min | Тур | Max | Units |

|-----------------------------------|-----|-----|-----|-------|

| Supply Voltage (V <sub>DD</sub> ) | 3.0 | 3.3 | 3.6 | V     |

| Temperature (T <sub>A</sub> )     | -40 | +25 | +85 | °C    |

#### **Electrical Characteristics**

Over Supply Voltage and Operating Temperature ranges, unless otherwise specified. (Notes 2, 3, 8)

| Symbol             | Parameter                                             | Conditions                             |                          | Pin             | Min   | Тур        | Max      | Units |

|--------------------|-------------------------------------------------------|----------------------------------------|--------------------------|-----------------|-------|------------|----------|-------|

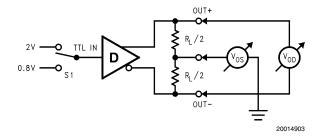

| IV <sub>OD</sub> I | Output Differential Voltage                           | $R_L = 100\Omega$                      |                          | OUT+,           | 250   | 350        | 450      | mV    |

| $\Delta V_{OD}$    | V <sub>OD</sub> Magnitude Change                      | (Figure 1 and Figure 2)                |                          | OUT-            |       | 3          | 35       | mV    |

| V <sub>os</sub>    | Offset Voltage                                        | $R_L = 100\Omega$                      |                          |                 | 1.125 | 1.22       | 1.375    | V     |

| $\Delta V_{OS}$    | Offset Magnitude Change                               | (Figure 1)                             |                          |                 | 0     | 1          | 25       | mV    |

| I <sub>OFF</sub>   | Power-off Leakage                                     | $V_{OUT} = 3.6V$ or GND, $V_{DD} = 0V$ |                          | ]               |       | ±1         | ±10      | μA    |

| l <sub>os</sub>    | Output Short Circuit Current (Note 4)                 | $V_{OUT+}$ and $V_{OUT-} = 0V$         |                          |                 |       | -6         | -24      | mA    |

| l <sub>osp</sub>   | Differential Output Short Circuit<br>Current (Note 4) | $V_{OD} = 0V$                          |                          |                 |       | <b>-</b> 5 | -12      | mA    |

| C <sub>OUT</sub>   | Output Capacitance                                    |                                        |                          | 1               |       | 3          |          | pF    |

| V <sub>IH</sub>    | Input High Voltage                                    |                                        |                          | TTL IN          | 2.0   |            | $V_{DD}$ | V     |

| V <sub>IL</sub>    | Input Low Voltage                                     |                                        |                          |                 | GND   |            | 0.8      | V     |

| I <sub>IH</sub>    | Input High Current                                    | V <sub>IN</sub> = 3.3V or 2.4V         |                          |                 |       | ±2         | ±10      | μA    |

| I <sub>IL</sub>    | Input Low Current                                     | V <sub>IN</sub> = GND or 0.5V          |                          |                 |       | ±1         | ±10      | μΑ    |

| V <sub>CL</sub>    | Input Clamp Voltage                                   | I <sub>CL</sub> = -18 mA               |                          |                 | -1.5  | -0.6       |          | V     |

| C <sub>IN</sub>    | Input Capacitance                                     |                                        |                          |                 |       | 3          |          | pF    |

| I <sub>DD</sub>    | Power Supply Current                                  | No Load                                | $V_{IN} = V_{DD}$ or GND | V <sub>DD</sub> |       | 5          | 8        | mA    |

|                    |                                                       | $R_L = 100\Omega$                      |                          |                 |       | 7          | 10       | mA    |

## **Switching Characteristics**

Over Supply Voltage and Operating Temperature Ranges, unless otherwise specified. (Notes 3, 5, 6, 7)

| Symbol            | Parameter                                                                 | Conditions                     | Min | Тур | Max | Units |

|-------------------|---------------------------------------------------------------------------|--------------------------------|-----|-----|-----|-------|

| t <sub>PHLD</sub> | Differential Propagation Delay High to Low                                | $R_L = 100\Omega, C_L = 15 pF$ | 0.3 | 1.0 | 1.5 | ns    |

| t <sub>PLHD</sub> | Differential Propagation Delay Low to High                                | (Figure 3 and Figure 4)        | 0.3 | 1.1 | 1.5 | ns    |

| t <sub>SKD1</sub> | Differential Pulse Skew It <sub>PHLD</sub> - t <sub>PLHD</sub> I (Note 9) |                                | 0   | 0.1 | 0.7 | ns    |

| t <sub>SKD3</sub> | Differential Part to Part Skew (Note 10)                                  |                                | 0   | 0.2 | 1.0 | ns    |

| t <sub>SKD4</sub> | Differential Part to Part Skew (Note 11)                                  |                                | 0   | 0.4 | 1.2 | ns    |

| t <sub>TLH</sub>  | Transition Low to High Time                                               |                                | 0.2 | 0.5 | 1.0 | ns    |

| t <sub>THL</sub>  | Transition High to Low Time                                               |                                | 0.2 | 0.5 | 1.0 | ns    |

| f <sub>MAX</sub>  | Maximum Operating Frequency (Note 12)                                     |                                | 200 | 250 |     | MHz   |

### Switching Characteristics (Continued)

- **Note 1:** "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" specifies conditions of device operation.

- Note 2: Current into device pins is defined as positive. Current out of device pins is defined as negative. All voltages are referenced to ground except VOD.

- **Note 3:** All typicals are given for:  $V_{DD} = +3.3V$  and  $T_A = +25^{\circ}C$ .

- Note 4: Output short circuit current (I<sub>OS</sub>) is specified as magnitude only, minus sign indicates direction only.

- Note 5: These parameters are guaranteed by design. The limits are based on statistical analysis of the device performance over PVT (process, voltage, temperature) ranges.

- Note 6:  $C_L$  includes probe and fixture capacitance.

- Note 7: Generator waveform for all tests unless otherwise specified: f = 1 MHz,  $Z_O = 50\Omega$ ,  $t_f \le 1$  ns,  $t_f \le 1$  ns (10%-90%).

- Note 8: The DS90LV011A is a current mode device and only function with datasheet specification when a resistive load is applied to the drivers outputs.

- Note 9: t<sub>SKD1</sub>, lt<sub>PHLD</sub> t<sub>PLHD</sub>I, is the magnitude difference in differential propagation delay time between the positive going edge and the negative going edge of the same channel.

- Note 10: t<sub>SKD3</sub>, Differential Part to Part Skew, is defined as the difference between the minimum and maximum specified differential propagation delays. This specification applies to devices at the same V<sub>DD</sub> and within 5°C of each other within the operating temperature range.

- Note 11:  $t_{SKD4}$ , part to part skew, is the differential channel to channel skew of any event between devices. This specification applies to devices over recommended operating temperature and voltage ranges, and across process distribution.  $t_{SKD4}$  is defined as IMax MinI differential propagation delay.

- Note 12:  $t_{MAX}$  generator input conditions:  $t_f = t_f < 1$  ns (0% to 100%), 50% duty cycle, 0V to 3V. Output criteria: duty cycle = 45%/55%,  $V_{OD} > 250mV$ . The parameter is guaranteed by design. The limit is based on the statistical analysis of the device over the PVT range by the transitions times ( $t_{TLH}$  and  $t_{THL}$ ).

#### Parameter Measurement Information

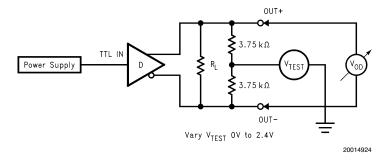

FIGURE 1. Differential Driver DC Test Circuit

FIGURE 2. Differential Driver Full Load DC Test Circuit

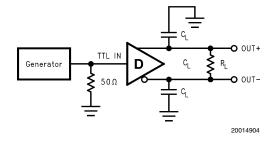

FIGURE 3. Differential Driver Propagation Delay and Transition Time Test Circuit

#### Parameter Measurement Information (Continued)

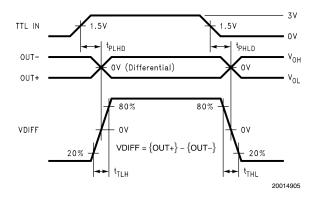

FIGURE 4. Differential Driver Propagation Delay and Transition Time Waveforms

# www.DataSilpeetApplication Information

**TABLE 1. Device Pin Descriptions**

| Package P | Package Pin Number |                 | Description                     |  |

|-----------|--------------------|-----------------|---------------------------------|--|

| SOT23     | LLP                | Pin Name        | Description                     |  |

| 5         | 8                  | TTL IN          | LVTTL/LVCMOS driver input pins  |  |

| 4         | 1                  | OUT+            | Non-inverting driver output pin |  |

| 3         | 3                  | OUT-            | Inverting driver output pin     |  |

| 2         | 7                  | GND             | Ground pin                      |  |

| 1         | 6                  | V <sub>DD</sub> | Power supply pin, +3.3V ± 0.3V  |  |

|           | 2, 4, 5            | NC              | No connect                      |  |

#### **PC Board Considerations:**

For PC board considerations for the LLP package, please refer to application note AN-1187 "Leadless Leadframe Package." It is important to note that to optimize signal integrity (minimize jitter and noise coupling), the LLP thermal

land pad, which is a metal (normally copper) rectangular region located under the package, should be attached to ground and match the dimensions of the exposed pad on the PCB (1:1 ratio).

# **Physical Dimensions** inches (millimeters) unless otherwise noted (.075) [1.91] A .115±.003 [2.92±0.07] PKG\_SYMM ₿ (.102) [2.59] .063±.003 [1.6±0.07] .112±.006 [2.84±0.15] (.039 TYP) [0.99] LAND PATTERN RECOMMENDATION www.DataSheet4U.com R.004 MIN TYP R.004 MIN TYP $\begin{bmatrix} 0.060 & 0.0015 \\ 0.0010 & 0.0015 \\ 0.152 & 0.025 \end{bmatrix}$ .038-.048

△ .004 [0.1]C

.0170±.0025 TYP [0.432±0.063]

♦ .008 [0.2]M C AS BS

MF05A (Rev A)

-.014-.022 [0.36-0.55] TYP

-SEATING PLANE

5-Lead SOT23, JEDEC MO-178, 1.6mm Order Number DS90LV011ATMF NS Package Number MF05A

.002-.006 [0.05-0.15] TYP

CONTROLLING DIMENSION IS INCH VALUES IN [ ] ARE MILLIMETERS

#### Physical Dimensions inches (millimeters) unless otherwise noted (Continued) (1.8) 2) (1 (8X 0.5) DIMENSIONS ARE IN MILLIMETERS (8X 0.25) RECOMMENDED LAND PATTERN 1:1 RATION WITH PKG SOLDER PADS -C 0.8 MAX PIN 1 INDEX AREA-(0.2) (0.1) ALL ROUND eet4U.com PIN 1 ID 1.2±0.1 3±0.1 0 8X 0 5+0 1 固 - A 3 ± 0 . 1 8X 0.25±0.05 6X 0.5 **♦** 0.1**%** C AS BS - 2X 1.5 LDA08A (Rev B)

LLP-8, 3mm x 3mm Body Order Number DS90LV011ATLD **NS Package Number LDA08A**

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Email: support@nsc.com

www.national.com

**National Semiconductor** Europe

Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor** Asia Pacific Customer Response Group Tel: 65-2544466 Fax: 65-2504466

**National Semiconductor** Tel: 81-3-5639-7560 Fax: 81-3-5639-7507

Email: ap.support@nsc.com