## microelectronics group

## **DSP32C Digital Signal Processor**

#### **Products Affected**

This advisory is effective for issue 5 of the DSP32C. Issue 5 devices are identified by a device code of the form DSP32C-X35 (where X is replaced by R or F).

The design consideration involves external writes to and reads from the parallel data register (PDR) with a system clock greater than 66 MHz.

#### **Problem Description**

Contents of the PDR register may fail to be transferred to memory during a DMA write operation when the falling edge of PEN or PWN aligns near the trailing edge of the output clock (CKO). If an external device overwrites the PDR, the DMA transaction is not completed. The status of the parallel data full (PDF) flag and associated pin may be corrupted during this transaction.

A DMA read transaction may fail if the falling edge of PEN or PGN aligns near the falling edge of CKO. The PDF flag and associated pin may not correctly assume a deasserted state.

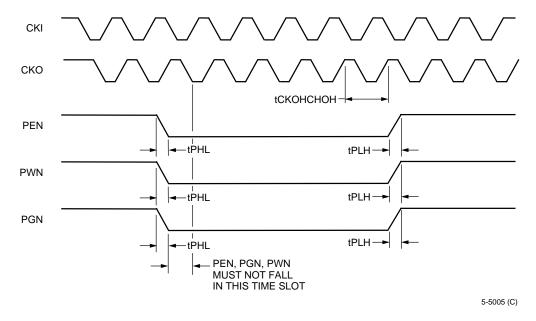

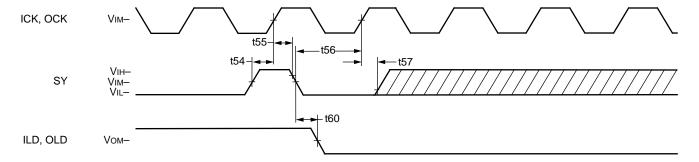

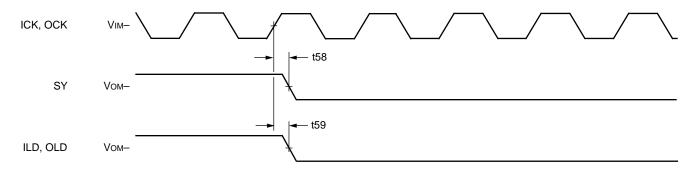

The failure occurs only when the DSP operates at a clock frequency greater than 66 MHz, and CKO is asynchronous with respect to the PEN, PWN, and PGN signals. To eliminate this potential problem, a synchronous clocking scheme is needed. This clocking scheme prevents PEN, PWN and PGN from falling a minimum of 3 ns before the falling edge of CKO. See Figure 2.

#### **Problem Resolution**

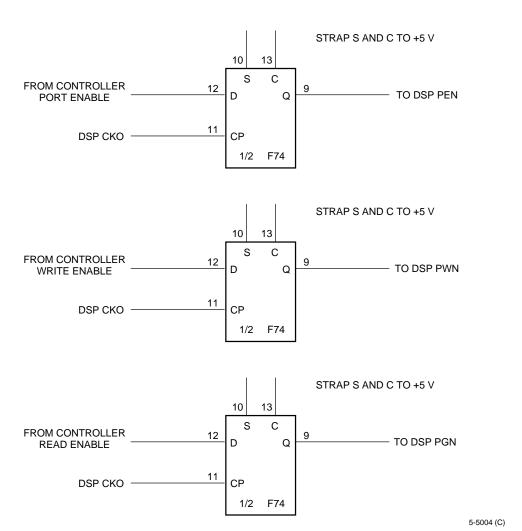

PEN, PWN, and PGN may be synchronized with the DSP clock to eliminate this potential alignment problem. Figure 1 illustrates a circuit that may be used to synchronize these inputs. Figure 2 shows the associated timing. The synchronization circuit delays the rise and fall points of PEN, PWN, and PGN. This added delay is equal to the maximum time of tCKOHCKOH + the cp to Q propagation delay of the F74 (tPLH or tPHL). For an 80 MHz CKI, the maximum delay would be 12.5 ns + the cp to Q delay of the F74. Subsequently, the user must ensure that other timing specifications listed in Table 1 and Table 2 are not violated.

## **Timing Characteristics**

Figure 1. Hardware Workaround

## Timing Characteristics (continued)

Figure 2. Hardware Workaround Timing

## Timing Characteristics (continued)

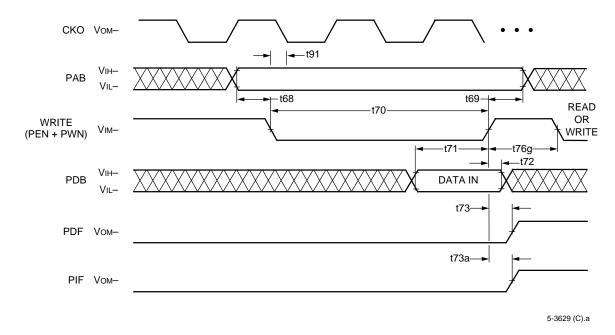

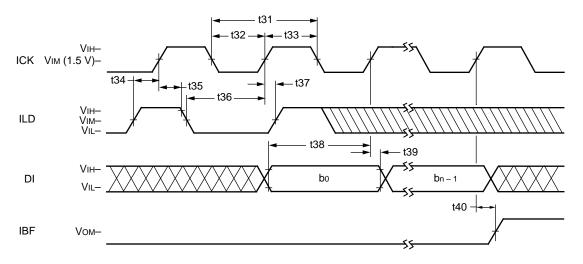

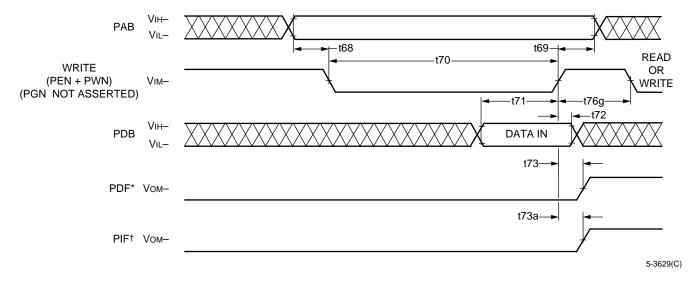

Figure 3. PIO Timing—Write Cycle (PGN High)

Table 1. Timing Characteristics for PIO Write Cycle (See Figure 3.)

| Abbreviated Reference | <i>IEEE</i> * Symbol | Parameter             | 50  | 50 ns            |  |

|-----------------------|----------------------|-----------------------|-----|------------------|--|

| Appreviated Reference | IEEE Symbol          | Parameter             | Min | Max <sup>†</sup> |  |

| t68                   | tPAVPWL              | Address Setup         | 5   | _                |  |

| t69                   | tPWHPAX              | Address Hold          | 0   | _                |  |

| t70                   | tPWLPWH              | Write Pulse           | 2T  | _                |  |

| t71                   | tPDVPWH              | Data Setup            | 10  | _                |  |

| t72                   | tPWHPDX              | Data Hold             | 0   | _                |  |

| t73                   | tPWHPDFH             | PDF Write Delay       | _   | T + 15           |  |

| t73a                  | tPWHPIFH             | PIF Write Delay       | _   | T + 15           |  |

| t76g                  | tPRWHPRWL            | PIO Idle <sup>‡</sup> | 2T  | _                |  |

| t91                   | tPWNLCKOL            | Write Setup           | 3   | _                |  |

<sup>\*</sup> IEEE is a registered trademark of The Institute of Electrical and Electronics Engineers, Inc.

<sup>†</sup> T = tCKILCKIL (system clock period).

<sup>‡</sup> A minimum 2 x T interval is required for the start of the read or write cycle following the end of the previous read or write cycle.

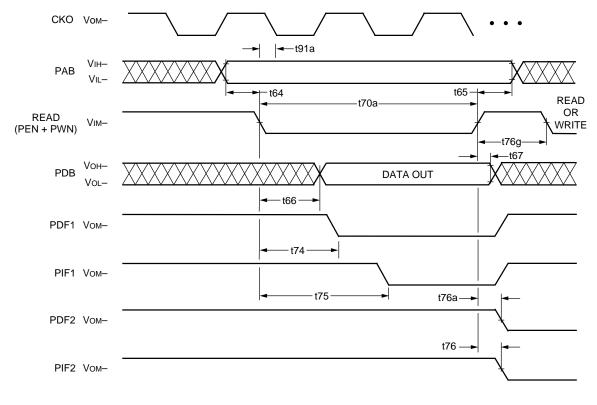

## **Timing Characteristics** (continued)

5-3629 (C).b

Notes:

PDF1 and PIF1 reflect the timing when PCR [10] = 0. PDF2 and PIF2 reflect the timing when PCR [10] = 1.

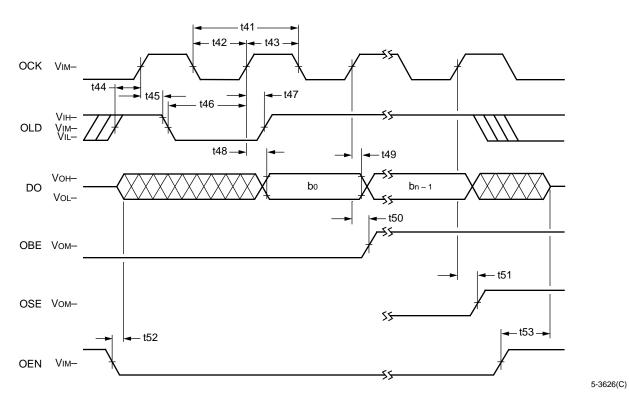

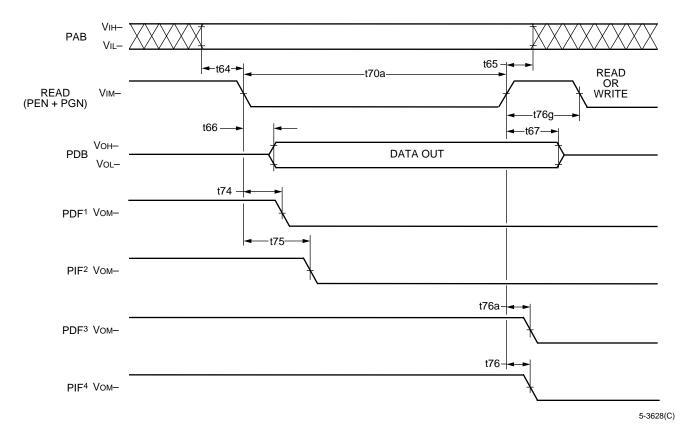

Figure 4. PIO Timing—Read Cycle (PWN High)

**Table 2. Timing Characteristics for PIO Read Cycle** (See Figure 4.)

| Abbreviated Reference | IEEE Symbol        | Parameter             | 50 ns |        |  |

|-----------------------|--------------------|-----------------------|-------|--------|--|

| Appreviated Reference | <i>IEEE</i> Symbol | Parameter             | Min   | Max*   |  |

| t64                   | tPAVPRL            | Address Setup         | 5     | _      |  |

| t65                   | tPRHPAX            | Address Hold          | 0     | _      |  |

| t66                   | tPRLPDV            | Access from Read      | _     | 17     |  |

| t67                   | tPRHPDZ            | Data Hold from Read   | 2     | 7      |  |

| t70a                  | tPRLPRH            | Read Pulse            | 2T    | _      |  |

| t74                   | tPRLPDFL           | PDF Read Delay        | _     | 15     |  |

| t75                   | tPRLPIFL           | PIF Read Delay        | _     | 15     |  |

| t76                   | tPRHPIFL           | PIF Read Delay        | _     | T + 15 |  |

| t76a                  | tPRHPDFL           | PDF Read Delay        | _     | T + 15 |  |

| t76g                  | tPRWHPRWL          | PIO Idle <sup>†</sup> | 2T    | _      |  |

| t90a                  | tPGNLCKOL          | Read Setup            | 3     | _      |  |

<sup>\*</sup> T = tCKILCKIL (system clock period).

<sup>†</sup> A minimum 2 x T interval is required for the start of the read or write cycle following the end of the previous read or write cycle.

**Notes**

**Notes**

For additional information, contact your Microelectronics Group Account Manager or the following:

INTERNET: http://www.lucent.com/micro

U.S.A.: Microelectronics Group, Lucent Technologies Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18103,

1-800-372-2447, FAX 610-712-4106 (In ČANADA: 1-800-553-2448, FAX 610-712-4106), e-mail docmaster@micro.lucent.com

ASIA PACIFIC: Microelectronics Group, Lucent Technologies Singapore Pte. Ltd., 77 Science Park Drive, #03-18 Cintech III, Singapore 118256

Tel. (65) 778 8833, FAX (65) 777 7495

JAPAN: Microelectronics Group, Lucent Technologies Japan Ltd., 7-18, Higashi-Gotanda 2-chome, Shinagawa-ku, Tokyo 141, Japan

**Tel. (81) 3 5421 1600**, FAX (81) 3 5421 1700

For data requests in Éurope:

MICROELECTRONICS GROUP DATALINE: Tel. (44) 1734 324 299, FAX (44) 1734 328 148

For technical inquiries in Europe:

CENTRAL EUROPE: (49) 89 95086 0 (Munich), NORTHERN EUROPE: (44) 1344 865 900 (Bracknell UK),

FRANCE: (33) 1 47 67 47 67 (Paris), SOUTHERN EUROPE: (39) 2 6601 1800 (Milan) or (34) 1 807 1700 (Madrid)

Lucent Technologies Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of any such product(s) or information.

Copyright © 1996 Lucent Technologies Inc. All Rights Reserved Printed in U.S.A.

Printed On

Lucent Technologies

# **DSP32C Digital Signal Processor** with External Memory Interface

#### Introduction

AT&T is an industry leader in floating-point digital signal processing. AT&T's DSP32 architecture was introduced in 1985 and is now the accepted standard in the speech, signal processing, and telecommunications application areas.

The DSP32C device offers more than three times the throughput of the DSP32 while offering pin, source code, and object code upward compatibility. In addition to powerful DSP devices, AT&T offers application support to its customers. Application support is supplied by field engineers, application notes, application software, and a 24-hour bulletin board.

Software and hardware development tools are available from both AT&T and third parties to speed development schedules. These tools include a device software simulator, hardware development board, and in-circuit emulator. The DSP32C product family offers high processing power, ease of use, and excellent development support.

## **Description**

The AT&T DSP32C Digital Signal Processor is a 32-bit, floating-point, programmable integrated circuit. As the second generation to the DSP32, it has access to a large base of both software and hardware support.

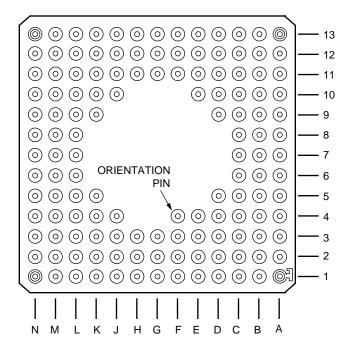

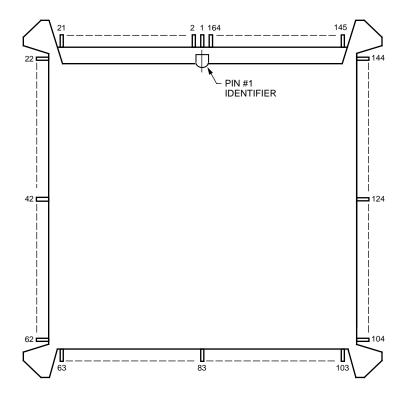

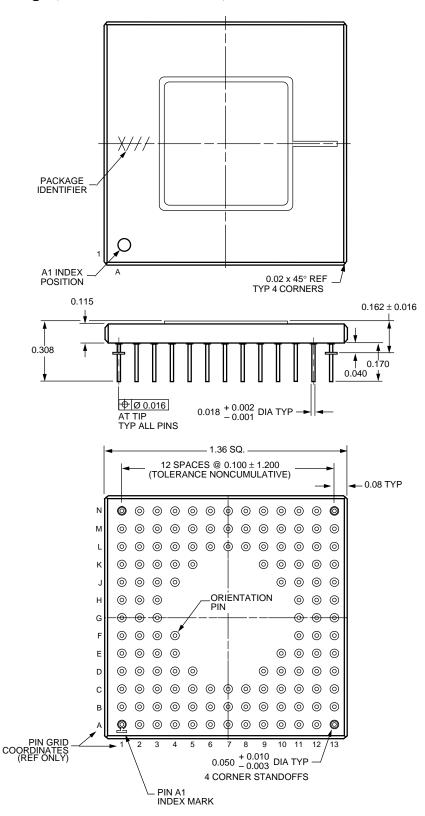

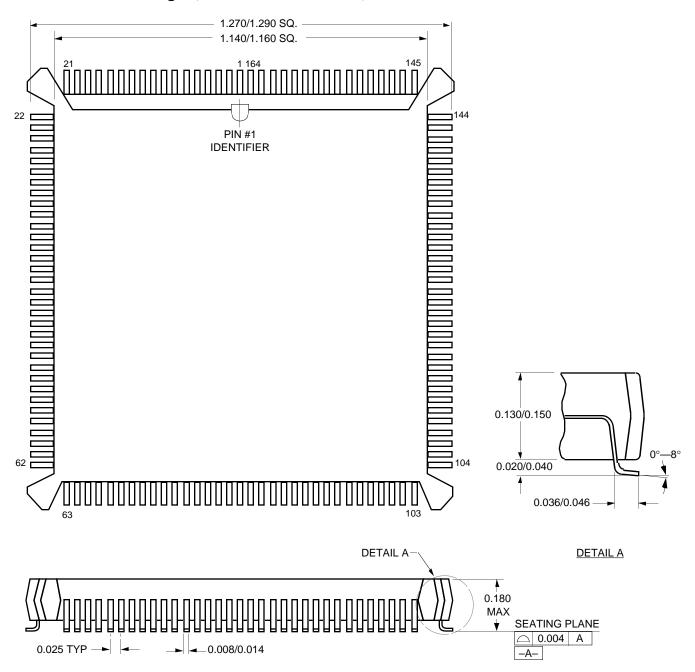

The DSP32C is fabricated in AT&T's high-speed, low-power CMOS technology. Packaging options for the DSP32C with External Memory Interface include a standard 133-pin, square ceramic pin-grid-array (CPGA) package and a 164-pin, JEDEC standard bumpered quad flat pack (BQFP) package.

Two execution units, the control arithmetic unit (CAU) and the data arithmetic unit (DAU), operate in parallel to achieve high throughput. The CAU performs 16- or 24-bit fixed-point arithmetic for logic and control functions. This unit, which includes 22 general-purpose registers, can execute 20 million instructions per second (MIPS). The DAU performs 32-bit floating-point arithmetic for signal processing functions. Four 40-bit accumulators are used as inputs/outputs to a floating-point multiplier and a floating-point adder that work in parallel to perform 40 million floating-point operations per second (MFLOPS).

Table 1. DSP32C Products

| Device Code | RAM           | Instruction Cycle Time | External Memory Interface | Package  |

|-------------|---------------|------------------------|---------------------------|----------|

| DSP32C-R35  | 3 - 0.5K x 32 | 80 ns, 60 ns, or 50 ns | Yes                       | 133 CPGA |

| DSP32C-F35  | 3 - 0.5K x 32 | 80 ns, 60 ns, or 50 ns | Yes                       | 164 BQFP |

| DSP32C-M4*  | 4 - 0.5K x 32 | 80 ns, 70 ns           | No                        | 68 PLCC  |

<sup>\*</sup> This version of the DSP32C is described in the AT&T DSP32C Without External Memory Interface Data Sheet.

## **Table of Contents**

| Contents                                     | Page |

|----------------------------------------------|------|

| Introduction                                 | 1    |

| Description                                  |      |

| Architecture                                 |      |

| Control Arithmetic Unit (CAU)                | 5    |

| Data Arithmetic Unit (DAU)                   | 5    |

| Internal and External Memory                 | 5    |

| Serial I/O Unit (SIO)                        | 6    |

| Parallel I/O Unit (PIO)                      | 6    |

| Memory Configuration                         | 6    |

| Memory Addressing                            | 8    |

| Interrupt Operation                          | 9    |

| Instruction Set                              | 10   |

| Flags                                        | 11   |

| Data Arithmetic (DA) Instructions            | 12   |

| Control Arithmetic (CA) Instructions         |      |

| Instruction Encoding                         |      |

| DA Instruction Formats                       | 18   |

| Encoding for DA Instruction Formats          |      |

| CA Instruction Formats (Eight Format Groups) |      |

| CAU Encoding for CA Instruction Formats      |      |

| Register Operation                           |      |

| Input/Output Control (ioc) Register          |      |

| DAU Control (dauc) Register                  |      |

| Parallel I/O Register Selection              |      |

| Parallel I/O Control Register (pcr)          |      |

| Error Source Register (esr)                  |      |

| Error Mask Register (emr)                    |      |

| Processor Control Word (pcw) Register        |      |

| Pin Information                              |      |

| Pins by Functional Group Order               |      |

| Pins by Numerical Order                      |      |

| Device Requirements and Characteristics      |      |

| Absolute Maximum Ratings                     |      |

| Handling Precautions                         |      |

| Temperature Class Definitions                |      |

| Recommended Operating Conditions             |      |

| Package Thermal Considerations               |      |

| Electrical Characteristics                   |      |

| Timing Requirements and Characteristics      |      |

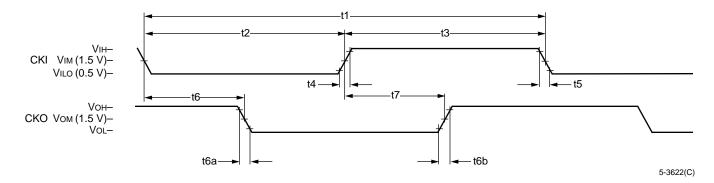

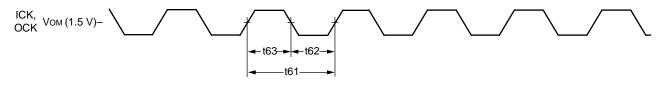

| CKI and CKO Timing                           |      |

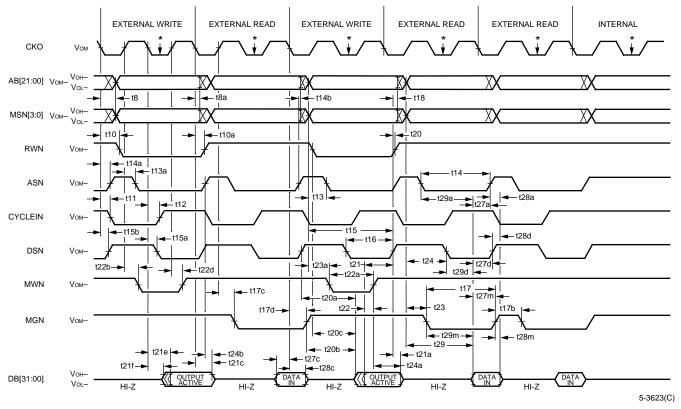

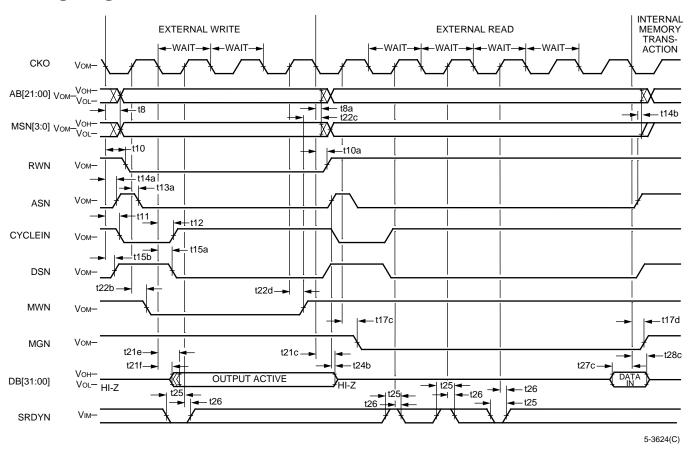

| External Memory Interface (EMI) Timing       |      |

| Serial I/O (SIO) Timing                      |      |

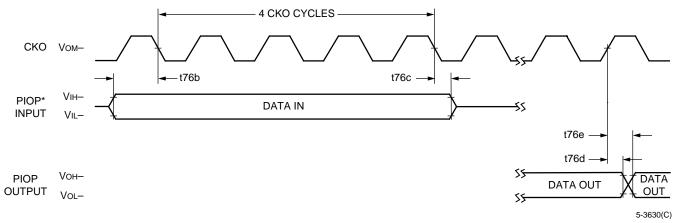

| Parallel I/O (PIO) Timing                    |      |

| Reset and Interrupt Timing                   |      |

| Bus Request Timing                           |      |

| Timing Diagrams                              |      |

| 8-Bit PIO                                    |      |

| Outline Diagrams                             |      |

| 133-Pin CPGA Package                         |      |

| 164-Pin BQFP Package                         | /5   |

## **Description** (continued)

Table 2. Features and Benefits of the DSP32C

| Features                                                     | Benefits                                                      |

|--------------------------------------------------------------|---------------------------------------------------------------|

| Full 32-bit floating-point architecture                      | Simplifies program development to provide faster              |

| Increased precision & dynamic range                          | time to market                                                |

|                                                              | Much easier algorithm development opens up                    |

|                                                              | new application possibilities                                 |

| Instruction started every instruction cycle                  | Allows more complex functions or a greater num-               |

|                                                              | ber of simultaneous functions to be implemented               |

| Four memory accesses per instruction cycle                   | Eliminates memory accessing bottlenecks                       |

| Exceptional memory bandwidth                                 |                                                               |

| C-like assembly language                                     | Easy to learn/excellent readability                           |

| Serial and parallel ports with DMA                           | Clean interface to external devices                           |

| High bandwidth, nonintrusive I/O                             | Lower system cost                                             |

|                                                              | Easy interface to PC buses                                    |

|                                                              | External control via parallel I/O (PIO)                       |

| Hardware data format conversions                             | Eliminates lengthy software routines                          |

| <ul><li>— IEEE* P754 floating-point</li></ul>                | Permits shared data with host processor or other              |

|                                                              | platforms                                                     |

| — Integer conversions:                                       | Increased throughput in:                                      |

| 8-bit unsigned                                               | <ul> <li>Graphics and image processing</li> </ul>             |

| 16-bit linear                                                | <ul> <li>Applications with 16-bit data</li> </ul>             |

| 24-bit linear                                                | <ul> <li>HQ digital audio and control applications</li> </ul> |

| <ul><li>μ-law/A-law conversions</li></ul>                    | <ul> <li>Telecom and speech applications</li> </ul>           |

| Fully vectored interrupt structure with hardware             | Allows very fast interrupt processing (up to                  |

| context save                                                 | 2 million interrupts/s)                                       |

| Byte-addressable address space                               | Efficient storage of 8- and 16-bit data                       |

|                                                              | Lower system cost                                             |

| Flexible wait-state facility                                 | Greater memory speed selection flexibility than               |

| <ul> <li>Each wait-state is 1/4 instruction cycle</li> </ul> | conventional full-cycle wait-states                           |

| <ul> <li>Two independent external memory speed</li> </ul>    | Allows mixing of slow and fast memory                         |

| partitions                                                   | Optimizes system speed/cost requirements                      |

<sup>\*</sup> IEEE is a registered trademark of The Institute of Electrical and Electronics Engineers, Inc.

Table 3. DSP32C with External Memory Interface Device Speed Options

| Minimum Instruction<br>Cycle Time (ns) | Maximum Clock Frequency (MHz) |

|----------------------------------------|-------------------------------|

| 50                                     | 80.000                        |

| 60                                     | 66.666                        |

| 80                                     | 50.000                        |

## **Description** (continued)

| LEGEND | ):                            | -       |                                | •      |                            |

|--------|-------------------------------|---------|--------------------------------|--------|----------------------------|

| a0—a3  | Accumulators 0—3              | IR1—IR4 | Instruction register pipeline  | pdr    | PIO data register          |

| ALU    | Arithmetic logic unit         | ISR     | Input shift register           | pdr2   | PIO data register 2        |

| CAU    | Control arithmetic unit       | ivtp    | Interrupt vector table pointer | pin    | Serial DMA input pointer   |

| DAU    | Data arithmetic unit          | obuf    | Output buffer                  | PIO    | Parallel I/O unit          |

| dauc   | DAU control register          | OSR     | Output shift register          | piop   | Parallel I/O port register |

| emr    | Error mask register           | par     | PIO address register           | pir    | PIO interrupt register     |

| esr    | Error source register         | pare    | PIO address register extended  | pout   | Serial DMA output pointer  |

| ibuf   | Input buffer                  | рс      | Program counter                | r1—r19 | Registers 1—19             |

| ioc    | Input/output control register | pcr     | PIO control register           | RAM    | Read/write memory          |

| IR     | Instruction register          | pcw     | Processor control word         | SIO    | Serial I/O unit            |

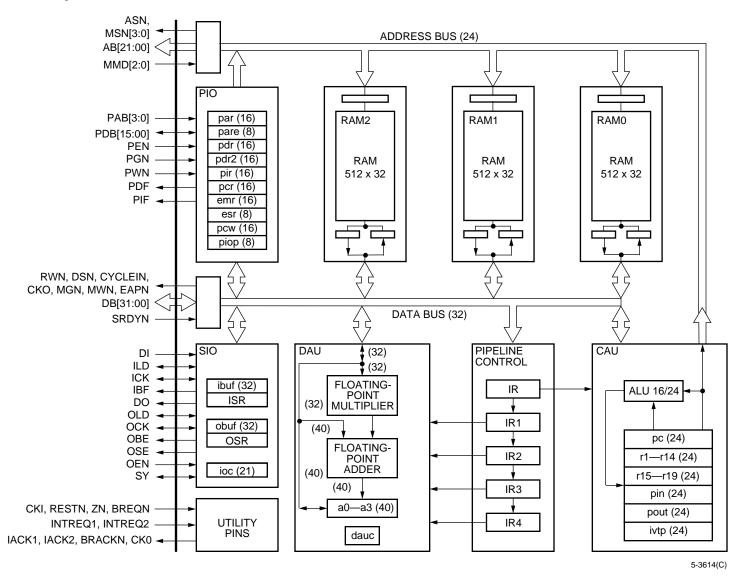

Figure 1. Block Diagram of the DSP32C with External Memory Interface

#### **Architecture**

The DSP32C architecture is being used today to solve a wide variety of complex problems. A large set of general-purpose registers simplifies assembly-language programming and allows very efficient compiler implementations. Both internal and external memory are treated as a general resource allowing the programmer to freely mix both programs and/or data within the 16 Mbyte address space.

In addition to its powerful number-crunching capabilities and flexible memory organization, the DSP32C offers many features that allow it to be easily and quickly integrated into real world systems.

A block diagram of the DSP32C with External Memory Interface appears in Figure 1. The following subsections describe the components shown in this diagram.

### **Control Arithmetic Unit (CAU)**

The CAU generates memory addresses and performs 16- or 24-bit integer arithmetic at the rate of 20 million instructions per second. The CAU consists of a 24-bit arithmetic logic unit (ALU) which performs the integer arithmetic and logical operations, a 24-bit program counter (pc) register, and 22 general-purpose 24-bit registers. All 22 registers can be used for operands in the execution of 16- or 24-bit integer operations; however, some of these registers also serve special purposes. When addressing 32-bit floating-point operands, registers r1—r14 are used as memory pointers (rP), and r15—r19 are used as increment registers (rl). Register r20, also called pin, is used as the serial DMA input pointer. Register r21, also called pout, is used as the serial DMA output pointer. Register r22, also called interrupt vector table pointer (ivtp), is used as the base address for the interrupt vector table.

#### Data Arithmetic Unit (DAU)

The DAU is configured for multiply/accumulate operations and is the primary execution unit for signal-processing algorithms. The DAU contains a floating-point multiplier and a floating-point adder, and four 40-bit accumulators ( $\mathbf{a0}$ — $\mathbf{a3}$ ). The multiplier and adder work in parallel to perform 20 million instructions per second of the form a = b + c \* d. The DAU multiplier operands (c and d) are 32-bit floating-point numbers (an 8-bit

exponent and a 24-bit mantissa) from memory or an accumulator. The multiplier always provides one 40-bit input to the adder. The other input can originate from memory, the I/O ports, or an accumulator. The operands for this second adder input can be 8-, 16-, 24-, 32-, or 40-bit numbers. The 40-bit operands (8-bit exponent, 24-bit mantissa, and eight mantissa guard bits) come from an accumulator (a0-a3). The 8-, 16-, and 24-bit operands are used in special function instructions whose purpose is data-type conversion. For either conversions or addition operations, 32-bit operands may come from memory or I/O registers. Available conversions are between the DSP32C floating-point format and the following: 8-, 16-, and 24-bit two's complement integer, µ-law, A-law, and single-precision IEEE floating-point format.

#### **Internal and External Memory**

The DSP32C provides on-chip RAM and an external memory interface for off-chip ROM and/or RAM expansion. All memory can be addressed as 8-, 16-, 24-, or 32-bit words, with 32-bit data accessed at the same speed as 8-bit data. Instructions, tables, and data can be arbitrarily located in on-chip RAM or external memory. The addresses of the various blocks of memory can be configured in eight different memory modes. Four of the memory modes provide a DSP32-compatible 16-bit address space. The other four memory modes provide a full 24-bit address space. See the Memory Configuration section for more information on configuring the address space. Regardless of the configuration, the first instruction executed after reset is at address 0x000000.

Internally, the DSP32C device has 1,536 words of RAM which are available in all memory configurations. The on-chip RAM is static and does not need to be refreshed.

The external memory interface can directly address up to 16 Mbytes of additional memory. The interface supports wait-states and bus arbitration. The external memory is divided into two sections: a low partition (A) and a high partition (B). The number of wait-states for each partition is independently configurable (see Register Operation, Table 25, **pcw** Register). Therefore, a mix of slow and fast memories can be used to provide the necessary throughput at a reasonable cost.

#### Architecture (continued)

### Serial I/O Unit (SIO)

The serial I/O unit is used for serial-to-parallel conversion of input data and parallel-to-serial conversion of output data. SIO inputs are loaded into the input shift register (ISR) and then into the input buffer (**ibuf**). SIO outputs are loaded into the output buffer (**obuf**) and then into the output shift register (OSR). This double-buffering makes back-to-back transfers possible, allowing the DSP32C program to begin a second transfer before the first has been completed. Data widths can be 8, 16, 24, or 32 bits. The input/output control (**ioc**) register in the SIO is used to select various I/O configurations, bit lengths, internal or external clocks, and internal or external synchronization (see Register Operation, Table 19, **ioc** Register).

#### Parallel I/O Unit (PIO)

The parallel I/O unit is an on-chip register file and bidirectional data bus that can be used for communication between the DSP32C device and an external device. The external PIO data bus can be 8 or 16 bits wide. PIO data transfers are made under program or DMA control. Using PIO DMA, an external device can download a program or data without interrupting execution of the DSP32C program. The PIO has three 16-bit data registers (pdr, pdr2, and pir), a 24-bit address register (par/pare), a 16-bit processor control word (pcw), an 8-bit I/O port register (piop), a 16-bit control register (pcr), a 16-bit error mask register (emr), and an 8-bit error source register (esr). These registers are used to control PIO transfers and configure error control and interrupt features (see Register Operation).

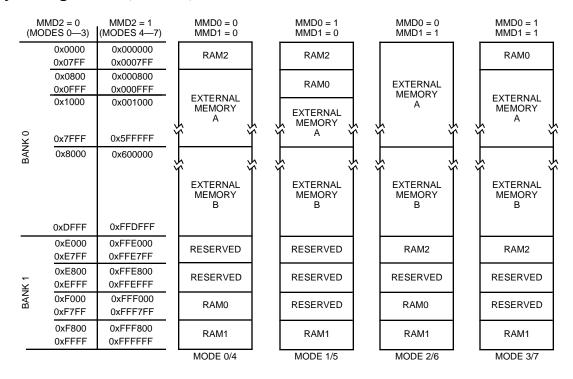

### **Memory Configuration**

The addresses of the various blocks of memory can be configured in eight different memory modes. Four of the memory modes (0—3) provide a DSP32-compatible, 16-bit address space. The other four memory modes (4—7) provide a full 24-bit address space. Pin MMD2 selects either the DSP32 compatible 16-bit address space or the expanded 24-bit address space. Pins MMD0 and MMD1 select memory modes that determine the location of on-chip memory resources in the memory address space. Figure 2 shows the location of memory resources.

Memory accesses can be made without regard to the type or location of the physical memory; however, to achieve maximum throughput, instruction/data memory accesses of floating-point operations must alternate between physical memories. There are four physical memories: (1) RAM0, (2) RAM1, (3) external memory A and B, and (4) RAM2.

The number of wait-states for the external memory partitions A and B are independently configurable via the MEMA and MEMB fields of the **pcw** register. The number of wait-states may be statically configured or externally controlled. Statically configured waits of 1, 2, or 3 states allow the DSP32C to access memory without delays for handshaking (a state is one period of CKI, or 12.5 ns at maximum clock frequency). When configured for two or more externally controlled wait-states, the DSP32C generates wait-states until the memory acknowledges the transaction via the synchronous ready (SRDYN) handshaking signal.

5-3619(C)

## Architecture (continued)

#### **Memory Configuration** (continued)

Figure 2. DSP32C Memory Configurations

#### **Architecture** (continued)

## **Memory Addressing**

Each 32-bit word is organized as 4 bytes, e.g., 3, 2, 1, 0, where byte 3 is the most significant byte (MSbyte) and byte 0 is the least significant byte (LSbyte) (see Table 4, Memory Addressing). A 16-bit integer is 2 bytes, either 1, 0 (with byte 1 the MSbyte and byte 0 the LSbyte) or 3, 2 (with byte 3 the MSbyte and byte 2 the LSbyte).

Integer operands of 24 bits are organized as 4 bytes. Byte 2 is the MSbyte, byte 0 is the LSbyte, and byte 3 is a sign extension of byte 2. Integer operands of 24 bits are addressed the same as 32-bit words. Memory address 0 can refer to an 8-bit byte (byte 0), a 16-bit integer (bytes 1, 0), a 24-bit integer (bytes 2, 1, 0), or a 32-bit word (bytes 3, 2, 1, 0).

**Table 4. Memory Addressing**

|        | 24-Bit Integer |        |                   |   |  |  |  |

|--------|----------------|--------|-------------------|---|--|--|--|

| 16-Bit | Integer        | 16-Bit | Memory<br>Address |   |  |  |  |

| Byte   | Byte           | Byte   | Byte              |   |  |  |  |

| 3      | 2              | 1      | 0                 | 0 |  |  |  |

| 7      | 6              | 5      | 4                 | 4 |  |  |  |

| 11     | 10             | 9      | 8                 | 8 |  |  |  |

|        | ı              | etc.   | 1.                |   |  |  |  |

The external memory is accessed by a 22-bit external address bus (AB00—AB21) and four byte select lines (MSN0—MSN3) (see Table 5, Data Type Memory Select and Write Data). The bus obtains its data from the 22 most significant bits of the address bus and selects a 32-bit word in memory. The four byte select signals (active-low) select bytes within the 32-bit word (see Pin Information). The value of the byte select lines is determined by the two least significant bits of the address and the data type implied in the instruction. The address is specified either directly or via a register pointer (pc, r1—r22). With the maximum external memory attached, one can address a total of 16M bytes, 8M 16-bit integers, 4M 24-bit integers, or 4M 32-bit words.

Table 5. Data Type Memory Select and Write Data

|               | Data Type Memory Select |      |      |      |       | DSP32C V | Vrite Data* |     |

|---------------|-------------------------|------|------|------|-------|----------|-------------|-----|

| Data Type     | MSN3                    | MSN2 | MSN1 | MSN0 | 24—31 | 16—23    | 8—15        | 0—7 |

| Byte 0        | 1                       | 1    | 1    | 0    | Α     | Α        | Α           | Α   |

| Byte 1        | 1                       | 1    | 0    | 1    | В     | В        | В           | В   |

| Byte 2        | 1                       | 0    | 1    | 1    | С     | С        | С           | С   |

| Byte 3        | 0                       | 1    | 1    | 1    | D     | D        | D           | D   |

| Low 16-bit    | 1                       | 1    | 0    | 0    | В     | Α        | В           | Α   |

| High 16-bit   | 0                       | 0    | 1    | 1    | D     | С        | D           | С   |

| 32-bit/24-bit | 0                       | 0    | 0    | 0    | D     | С        | В           | А   |

<sup>\*</sup> A = write data DB00—DB07; B = write data DB08—DB15; C = write data DB16—DB23; D = write data DB24—DB31.

## Architecture (continued)

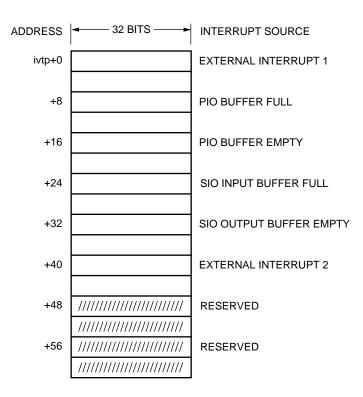

## **Interrupt Operation**

The DSP32C provides a single-level interrupt facility with six sources (four internal and two external). The interrupts are prioritized and are individually maskable via the INTER field of the **pcw** register. The sources are described below in descending priority:

- External Interrupt One (INTREQ1) level sensitive.

- Parallel Buffer Full (PDF) generated when the pdr register is loaded.

- 3. Parallel Buffer Empty (PDE) generated when the **pdr** register is read.

- 4. SIO Input Buffer Full (IBF) generated when the IBF flag is set.

- 5. SIO Output Buffer Empty (OBE) generated when the OBE flag is set.

- External Interrupt Two (INTREQ2) level sensitive.

Before servicing an interrupt, the DSP32C saves the state of the machine that is invisible to the programmer, as well as DAU accumulators a0-a3 and the dauc register. Internal states that are visible to the programmer and need to be saved, except a0-a3 and the dauc, must be saved and restored by the interrupt service routine. In response to a given interrupt, the DSP32C branches to the corresponding address in the interrupt vector table. The interrupt vector table contains six pairs of 32-bit words starting at the location specified in the interrupt vector table pointer register ivtp (r22). Each pair of words in the table should contain an unconditional branch to the appropriate interrupt routine. Note that even when masked, the interrupt conditions may be tested in conditional branch instructions (see Instruction Set). Figure 3 is a memory map of the interrupt vector table. To return to the interrupted program, the user should restore the user-visible state of the DSP32C (which was saved), and then execute the ireturn instruction. The latter operation restores a0—a3 and the state of the machine that is not visible to the user.

Figure 3. Interrupt Vector Table

AT&T Microelectronics 9

5-3621(C)

#### Instruction Set

Table 6. Features and Benefits of the DSP32C Instruction Set

| Features                                                                  | Benefits                                                                        |

|---------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| Instruction started every instruction cycle                               | Allows more complex or a greater number of applications to be implemented       |

| Full set of microprocessor-like instructions                              | Expands the number of applications that can be efficiently handled              |

| Conditional branches                                                      | Simplifies programming task*                                                    |

| Conditional ALU operations                                                | Permits very fast, efficient coding* Eliminates unnecessary branch instructions |

| Single-cycle <b>pc-</b> relative addressing for position-independent code | Simplifies multitask applications*                                              |

| Data stationary coding                                                    | Enables parallel operation of arithmetic and logical operations                 |

|                                                                           | Allows efficient compiler implementations*                                      |

|                                                                           | Provides automatic pipeline control*                                            |

|                                                                           | Simplifies program development process*                                         |

<sup>\*</sup> Provides faster time to market.

The DSP32C assembly language frees programmers from tedious memorization of assembly-language mnemonics. Instructions in the DSP32C are patterned after the C programming language and are entered in a natural equation syntax. In addition to being easier to learn, the resulting code is far more readable than mnemonic-based assembly languages, making code maintenance much easier.

C-like assembly language  $\rightarrow$  Easy to learn/excellent readability

Assembly-language example (32-bit multiply/ accumulate with store to memory):

$$*r1++ = a0 = a1 + *r2++ * *r3++$$

The execution of this instruction simply follows the conventions of the high-level C programming language:

"Multiply the 32-bit floating-point values stored in the memory locations pointed to by registers **r2** and **r3**. Add the result to the contents of accumulator **a1**, store the result in accumulator **a0**, and write the result to the 32-bit memory location pointed to by register **r1**. Post-increment pointer registers **r1**, **r2**, and **r3**."

The DSP32C has two general types of instructions that correspond to the two execution units: data arithmetic (DA) instructions and control arithmetic (CA) instructions.

Primarily, DA instructions perform 32-bit floating-point multiply/accumulate operations for signal processing algorithms. Other DA instructions convert the DSP32C's internal floating-point data to and from each of the following types: 8-bit, 16-bit, or 24-bit 2's complement integer;  $\mu$ -law; A-law; or single-precision  $\emph{IEEE}$  floating-point.

The CA instructions perform microprocessor operations such as 16-bit and 24-bit integer arithmetic and logic functions, conditional branching, and moving data.

### **Flags**

The DSP32C has internal flags that are affected by the results of certain DA, CA, or I/O instructions and certain I/O events. These flags, although not directly visible to the user, may be tested by conditional instructions. Table 7 lists the flags and their meanings.

Table 7. DSP32C Flags

|      | DAU Flags                        |                                                                                                              |  |  |  |  |

|------|----------------------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Flag | Meaning (Flag = 1)               | Description                                                                                                  |  |  |  |  |

| N    | Result is negative               | Sign bit = 1.                                                                                                |  |  |  |  |

| Z    | Result is zero                   | All 40 bits of accumulator = 0.                                                                              |  |  |  |  |

| V    | Result overflowed*               | DAU result   > 3.40282 E 38.                                                                                 |  |  |  |  |

| U    | Result underflowed*              | DAU result   < 5.87747 E -39.                                                                                |  |  |  |  |

|      |                                  | CAU Flags                                                                                                    |  |  |  |  |

| n    | Result is negative               | (16-bit) n = b23 (bit 23 of ALU result).<br>(24-bit) n = b23.                                                |  |  |  |  |

| Z    | Result is zero                   | (16-bit) $z = \overline{b23+b22+ \dots b1+b0}$ (+ = OR).<br>(24-bit) $z = \overline{b23+b22+ \dots b1+b0}$ . |  |  |  |  |

| С    | Carry or borrow out of MSB       | (16-bit) $c = b15c$ (carry out of ALU bit 15). (24-bit) $c = b23c$ .                                         |  |  |  |  |

| V    | Result overflowed                | (16-bit) $v = b14c \land b15c (\land = exclusive OR)$ .<br>(24-bit) $v = b22c \land b23c$ .                  |  |  |  |  |

|      |                                  | I/O Flags                                                                                                    |  |  |  |  |

| i    | Serial input buffer full         | Pin IBF = 1.                                                                                                 |  |  |  |  |

| О    | Serial output buffer full        | Pin OBE = 0.                                                                                                 |  |  |  |  |

| р    | Parallel data register full      | Pin PDF = 1.                                                                                                 |  |  |  |  |

| Р    | Parallel interrupt register full | Pin PIF = 1.                                                                                                 |  |  |  |  |

| s    | SY (I/O sync) set (1)            | Pin SY = 1.                                                                                                  |  |  |  |  |

| b    | Serial I/O frame boundary        | fbs = 1.                                                                                                     |  |  |  |  |

| r    | Interrupt pin 1 high (1)         | Pin INTREQ1 = 1.                                                                                             |  |  |  |  |

| R    | Interrupt pin 2 high (1)         | Pin INTREQ2 = 1.                                                                                             |  |  |  |  |

<sup>\*</sup> The DSP3207 Digital Signal Processor Information Manual dated July 1994, Section 3.3.3, contains a detailed description of the floating-point formats and exceptions. The DSP3207 floating-point format and arithmetic is identical to that of the DSP32C.

DSP32C instructions and the flags affected by each instruction are specified in the following tables. A zero (0) shown in place of a flag means that the flag is always made zero; a dash (—) in place of a flag means that the flag is unaffected by the instruction.

The complete DSP32C instruction set, grouped as DA and CA instructions, follows. Where braces, { }, are shown in an instruction, one of the enclosed items must be chosen. Items enclosed in brackets, [ ], are optional.

**Note:** { } and [ ] are not part of the instruction syntax. Parentheses, ( ), are part of the syntax and must appear where shown in an instruction. Lower-case letters are part of the syntax and upper-case letters are replaced by immediate data or by a register name (see tables following each instruction group).

### **Data Arithmetic (DA) Instructions**

The DA instructions are divided into two functional groups: multiply/accumulate and special functions.

Table 8. Data Multiply/Accumulate Instructions

| Instruction                   | DAU Flags<br>Affected | Description                                                                                                                                                                                                                                    |

|-------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [Z=] aN = [-]aM {+,-} Y*X     | NZVU                  | The product of the <b>X</b> and <b>Y</b> fields is added to or subtracted from the accumulator <b>aM</b> (or its negative), and the result is stored in accumulator <b>aN</b> . The result can also be output according to the <b>Z</b> field. |

| $aN = [-]aM \{+,-\} (Z=Y)*X$  | NZVU                  | The Y field operand is output according to the Z field. The product of the X and Y fields is added to or subtracted from the accumulator aM (or its negative), and the sum is stored in accumulator aN.                                        |

| $[Z=] aN = [-]Y \{+,-\} aM*X$ | NZVU                  | The product of the <b>X</b> field and the accumulator <b>aM</b> is added to or subtracted from the <b>Y</b> field (or its negative). The result is placed in accumulator <b>aN</b> and can also be output according to the <b>Z</b> field.     |

| [Z=] aN = [-]Y*X              | NZVU                  | The product of the <b>X</b> and <b>Y</b> fields is added to or subtracted from zero. The result is stored in accumulator <b>aN</b> and can also be output according to the <b>Z</b> field.                                                     |

| aN = [-](Z=Y)*X               | NZVU                  | The value of the <b>Y</b> field is output according to the <b>Z</b> field. The product of the <b>Y</b> and <b>X</b> fields (or the negative of the product) is stored in accumulator <b>aN</b> .                                               |

| $[Z=] aN = [-]Y \{+,-\}X$     | NZVU                  | The sum or difference of the Y and X fields is stored in accumulator aN, and the result can also be output according to the Z field. Note that X is a multiplier input.                                                                        |

| [Z=] aN = [-]Y                | NZVU                  | The value of the <b>Y</b> field (or its negative) is placed in accumulator <b>aN</b> and can also be output according to the <b>Z</b> field.                                                                                                   |

| $aN = [-](Z=Y) \{+,-\} X$     | NZVU                  | The sum or difference of the <b>Y</b> and <b>X</b> fields is stored in accumulator <b>aN</b> , and <b>Y</b> can also be output according to the <b>Z</b> field.                                                                                |

Table 9. Replacement Table for DA Multiply/Accumulate Instructions

| Replace | Value <sup>†</sup>                                   | Description                                                                                                                    |

|---------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| aN, aM  | a0—a3                                                | One of the four DAU accumulators.                                                                                              |

| X, Y    | *rP, *rP++, *rP, *rP++rl<br>a0—a3<br>ibuf            | 32-bit memory location. One of the four DAU accumulators. SIO input buffer.                                                    |

| Z       | *rP, *rP++, *rP,<br>*rP++rl, *rP++rlr<br>obuf<br>pdr | 32-bit memory location.  rIr indicates carry reverse add.  SIO output buffer.  PIO data register (pdr concatenated with pdr2). |

<sup>†</sup> rP refers to r1—r14 and is used as a memory pointer. rI refers to r15—r19 and is used as an increment pointer.

### Data Arithmetic (DA) Instructions (continued)

**Table 10. DA Special Function Instructions**

| Instruction          | DAU Flags<br>Affected | Description                                                            |

|----------------------|-----------------------|------------------------------------------------------------------------|

| [Z=] aN = ic(Y)      | NZ00                  | Input conversion, μ-law, A-law, 8-bit linear to float.                 |

| [Z=] aN = oc(Y)      | <del>_</del>          | Output conversion, float to μ-law, A-law, 8-bit linear (see Table 20). |

| [Z=] aN = float(Y)   | NZ00                  | 16-bit integer to float.                                               |

| [Z=] aN = float24(Y) | NZ00                  | 24-bit integer to float.                                               |

| [Z=] aN = int(Y)     | <u> </u>              | Float to 16-bit integer (round or truncate, dauc[4]).                  |

| [Z=] aN = int24(Y)   | <u> </u>              | Float to 24-bit integer (round or truncate, dauc[4]).                  |

| [Z=] aN = round(Y)   | NZVU*                 | Round float (40-bit) to float (32-bit).                                |

| [Z=] aN = ifalt(Y)   | <del>_</del>          | If $(aN < 0)$ then $[Z =] aN = Y$ else $[Z =] aN$ .                    |

| [Z=] aN = ifaeq(Y)   | <del>_</del>          | If $(aN = 0)$ then $[Z =] aN = Y$ else $[Z =] aN$ .                    |

| [Z=] aN = ifagt(Y)   | _                     | If $(aN > 0)$ then $[Z =] aN = Y$ else $[Z =] aN$ .                    |

| [Z=] aN = dsp(Y)     | NZVU*                 | IEEE-to-DSP32 format conversion.                                       |

| [Z=] aN = ieee(Y)    | _                     | DSP32-to-IEEE format conversion.                                       |

| [Z=] aN = seed(Y)    | NZ0U*                 | 32-bit to 32-bit reciprocal program seed.                              |

The DSP3207 Digital Signal Processor Information Manual dated July 1994 contains detailed descriptions of underflow and overflow for the **round**, **dsp**, and **seed** instructions. These descriptions can be found in the detailed descriptions of each instruction in Section 4.7 of the manual. The DSP3207 floating-point format, arithmetic, and the **round**, **dsp**, and **seed** instructions are identical to the DSP32C.

Table 11. Replacement Table for DA Special Function Instructions

| Replace | Value <sup>†</sup>       | Description                                     |  |  |  |  |

|---------|--------------------------|-------------------------------------------------|--|--|--|--|

| aN      | a0—a3                    | One of the four DAU accumulators.               |  |  |  |  |

| Υ‡      | *rP, *rP++, *rP, *rP++rI | 32-bit memory location.                         |  |  |  |  |

|         | a0—a3                    | One of the four DAU accumulators.               |  |  |  |  |

|         | ibuf                     | SIO input buffer.                               |  |  |  |  |

|         | pdr                      | PIO data register ( <b>pdr</b> ).               |  |  |  |  |

| Z       | *rP, *rP++, *rP, *rP++rI | 32-bit memory location.                         |  |  |  |  |

|         | obuf                     | SIO output buffer.                              |  |  |  |  |

|         | pdr                      | PIO data register (pdr concatenated with pdr2). |  |  |  |  |

<sup>†</sup> rP refers to r1—r14 and is used as a memory pointer. rI refers to r15—r19 and is used as an increment pointer. † Y may not be a0—a3 for the float or dsp special functions.

### **Control Arithmetic (CA) Instructions**

**Table 12. CA Control Instructions**

| Instruction                           | Flags<br>Affected | Instruction<br>Format | Description                                                                                          |

|---------------------------------------|-------------------|-----------------------|------------------------------------------------------------------------------------------------------|

| if (CA COND) goto {rH, N, rH+N,}      | None              | 0                     | Conditional branch.                                                                                  |

| if $(rM>= 0)$ goto $\{rH, N, rH+N,\}$ |                   | 3a                    | Conditional branch.                                                                                  |

| if (DA COND) goto {rH, N, rH+N,}      |                   | 0                     | Conditional branch.                                                                                  |

| if (IO COND) goto {rH, N, rH+N,}      |                   | 0                     | Conditional branch.                                                                                  |

| call {rH, N, M, rH+N,} (rM)           |                   | 4                     | Call subroutine.                                                                                     |

| return (rM)                           |                   | 0                     | Return from subroutine.                                                                              |

| ireturn                               |                   | 0                     | Return from interrupt.                                                                               |

| do J,{K,rH}                           |                   | 3b, 3c                | Do next J + 1 instructions.<br>K + 1 (or rH + 1) times.<br>J = 0, 1, 2 31.<br>K = rH = 0, 1, 2 2047. |

| goto {rH, N, M, rH+N}                 |                   | 0                     | Unconditional branch.                                                                                |

| nop                                   |                   | 0                     | No operation.                                                                                        |

Notes:

The **do** instruction and the instructions it encompasses are not interruptible, except for the last instruction during the last iteration. Further, the **do** instruction cannot be used in an interrupt routine.

A do loop should not contain any goto or call instructions. The assembler does not issue any warnings or errors if this is attempted

Table 13. Replacement Table for CA Control Group Instructions, CA Conditions (CA COND)

| Value | CAU Flags*      | Description                     |  |  |  |  |

|-------|-----------------|---------------------------------|--|--|--|--|

| pl    | n = 0           | Result is nonnegative (plus).   |  |  |  |  |

| mi    | n = 1           | Result is negative (minus).     |  |  |  |  |

| ne    | z = 0           | Result not equal to zero.       |  |  |  |  |

| eq    | z = 1           | Result equal to zero.           |  |  |  |  |

| VC    | v = 0           | Overflow clear, no overflow.    |  |  |  |  |

| VS    | v = 1           | Overflow set, overflowed.       |  |  |  |  |

| СС    | c = 0           | Carry clear, no carry.          |  |  |  |  |

| cs    | c = 1           | Carry set, carry.               |  |  |  |  |

| ge    | n ^ v = 0       | Greater than or equal to.       |  |  |  |  |

| lt    | n ^ v = 1       | Less than.                      |  |  |  |  |

| gt    | z   (n ^ v) = 0 | Greater than.                   |  |  |  |  |

| le    | z   (n ^ v) = 1 | Less than or equal to.          |  |  |  |  |

| hi    | c   z = 0       | Greater than (unsigned number). |  |  |  |  |

| Is    | c   z = 1       | Less than (unsigned number).    |  |  |  |  |

<sup>\*</sup> Symbol interpretation:  $^{\land}$  = XOR; | = OR.

## Control Arithmetic (CA) Instructions (continued)

Table 14. Replacement Table for CA Control Group Instructions, DA Conditions (DA COND)

| Value | DAU Flags | Description                    |  |  |  |

|-------|-----------|--------------------------------|--|--|--|

| ane   | Z = 0     | Not equal to zero.             |  |  |  |

| aeq   | Z = 1     | Equal to zero.                 |  |  |  |

| age   | N = 0     | Greater than or equal to zero. |  |  |  |

| alt   | N = 1     | Less than zero.                |  |  |  |

| avc   | V = 0     | Overflow clear, no overflow.   |  |  |  |

| avs   | V = 1     | Overflow set, overflowed.      |  |  |  |

| auc   | U = 0     | Underflow clear, no underflow. |  |  |  |

| aus   | U = 1     | Underflow set, underflowed.    |  |  |  |

| agt   | N   Z = 0 | Greater than zero.             |  |  |  |

| ale   | N   Z = 1 | Less than or equal to zero.    |  |  |  |

Table 15. Replacement Table for CA Control Group Instructions, I/O Conditions (IO COND)

| Mnemonic | Condition | Description                        |  |  |  |

|----------|-----------|------------------------------------|--|--|--|

| ibe      | ibf = 0   | Input buffer empty.                |  |  |  |

| ibf      | ibf = 1   | Input buffer full.                 |  |  |  |

| obe      | obe = 1   | Output buffer empty.               |  |  |  |

| obf      | obe = 0   | Output buffer full.                |  |  |  |

| pde      | pdf = 0   | Parallel data register empty.      |  |  |  |

| pdf      | pdf = 1   | Parallel data register full.       |  |  |  |

| pie      | pif = 0   | Parallel interrupt register empty. |  |  |  |

| pif      | pif = 1   | Parallel interrupt register full.  |  |  |  |

| syc      | sy = 0    | Sync signal low.                   |  |  |  |

| sys      | sy = 1    | Sync signal high.                  |  |  |  |

| fbc      | fb = 0    | Serial frame boundary clear.       |  |  |  |

| fbs      | fb = 1    | Serial frame boundary set.         |  |  |  |

| ireq1_hi | ireq1 = 1 | INTREQ1 pin is deasserted (1).     |  |  |  |

| ireq1_lo | ireq1 = 0 | INTREQ1 pin is asserted (0).       |  |  |  |

| ireq2_hi | ireq2 = 1 | INTREQ2 pin is deasserted (1).     |  |  |  |

| ireq2_lo | ireq2 = 0 | INTREQ2 pin is asserted (0).       |  |  |  |

### Control Arithmetic (CA) Instructions (continued)

Table 16. CA Arithmetic/Logic Instructions

| Instruction                    | CAU Flags<br>Affected | Instruction<br>Format | Description                                            |

|--------------------------------|-----------------------|-----------------------|--------------------------------------------------------|

| rD[e] = rH + N                 | nzvc                  | 5a, 5b                | Three operand add with 16-bit sign extended immediate. |

| rD[e] = rS1 + rS2              | nzvc                  | 6a, 6b                | Triadic add.                                           |

| rD[e] = rD + rS                | nzvc                  | 6a, 6b                | Dyadic add.                                            |

| rD[e] = rS1 - rS2              | nzvc                  | 6a, 6b                | Triadic left subtract.                                 |

| rD[e] = rS2 - rS1              | nzvc                  | 6a, 6b                | Triadic right subtract.                                |

| $rD[e] = rD - \{N, rS\}$       | nzvc                  | 6a, 6b, 6c, 6d        | Right subtract.                                        |

| rD[e] - {N, rS}                | nzvc                  | 6a, 6b, 6c, 6d        | Compare.                                               |

| $rD[e] = \{N, rS\} - rD$       | nzvc                  | 6a, 6b, 6c, 6d        | Left subtract.                                         |

| $rD[e] = rD \& \{N, rS\}$      | nz00                  | 6a, 6b, 6c, 6d        | AND.                                                   |

| rD[e] = rS1 & rS2              | nz00                  | 6a, 6b                | Triadic AND.                                           |

| rD[e] & {N, rS}                | nz00                  | 6a, 6b, 6c, 6d        | Bit test.                                              |

| $rD[e] = rD   \{N, rS\}$       | nz00                  | 6a, 6b, 6c, 6d        | OR.                                                    |

| rD[e] = rS1   rS2              | nz00                  | 6a, 6b                | Triadic OR.                                            |

| $rD[e] = rD ^{N, rS}$          | nz00                  | 6a, 6b, 6c, 6d        | XOR.                                                   |

| rD[e] = rS1 ^ rS2              | nz00                  | 6a, 6b                | Triadic XOR.                                           |

| rD[e] = rS / 2                 | nz0c                  | 6a, 6b                | Arithmetic right shift.                                |

| rD[e] = rS >> 1                | 0z0c                  | 6a, 6b                | Logical right shift.                                   |

| rD[e] = rS >>> 1               | nz0c                  | 6a, 6b                | Rotate right through carry.                            |

| rD[e] = rS <<< 1               | nzvc                  | 6a, 6b                | Rotate left through carry.                             |

| rD[e] = -rS                    | nzvc                  | 6a, 6b                | Negate.                                                |

| rD[e] = rS * 2                 | nzvc                  | 6a, 6b                | Arithmetic left shift.                                 |

| $rD[e] = rD \# \{N, rS\}$      | nz0c                  | 6a, 6b, 6c, 6d        | Dyadic carry reverse add.                              |

| rD[e] = rS1 # rS2              | nz0c                  | 6a, 6b                | Triadic carry reverse add.                             |

| $rD[e] = rD \& \sim \{N, rS\}$ | nzvc                  | 6a, 6b, 6c, 6d        | Dyadic AND with complement.                            |

| rD[e] = rS1 &~ rS2             | nzvc                  | 6a, 6b                | Triadic AND with complement.                           |

| rD[e] = rS                     | nzvc                  | 6a, 6b                | Assignment.                                            |

| rD[e] = rS {+,-} 1             | nzvc                  | 6a, 6b                | Increment/decrement.                                   |

Except for instructions with immediate operands ( $\mathbf{N}$ ), all CA arithmetic/logic instructions above may also be conditionally executed on the basis of CA conditions. The syntax is as follows:

if (CA COND) instruction

The optional e suffix is for 24-bit (extended) operands. Flags are set according to the rules for 24-bit operands. **N** is always 16 bits, and bit 15 is extended to 24 bits, for 24-bit operations.

## Control Arithmetic (CA) Instructions (continued)

**Table 17. CA Data Move Instructions**

| Instruction                                            | CAU Flags<br>Affected | Format | Description                         |

|--------------------------------------------------------|-----------------------|--------|-------------------------------------|

| rD = N                                                 | nz00                  | 6c     | 16-bit immediate load.              |

| rDe = M                                                | _                     | 8b     | 24-bit immediate load.              |

| {ioc <sup>†</sup> , dauc} = VALUE                      |                       | 5a     | 5- or 21-bit immediate load.        |

| $\{MEM, *N, obuf, piop\} = \{rSh, rSl\}$               |                       | 7      | MEM, *N, piop, and obuf are 8 bits. |

| {MEM, *N, obuf, pdr, pdr2, pir, pcw} = rS, pcsh        |                       | 7      | MEM, *N, and obuf are 16 bits.      |

| {MEM, *N, obuf} = rSe, pcshe                           |                       | 7      | MEM, *N, and obuf are 24 bits.      |

| $\{rDh, rDl\} = \{MEM, *N, ibuf, piop\}$               | nz00                  | 7      | MEM, *N, piop, and ibuf are 8 bits. |

| rD = {MEM, *N, ibuf, pdr, pdr2, pir, pcw} <sup>‡</sup> | nz00                  | 7      | MEM, *N, and ibuf are 16 bits.      |

| rDe = {MEM, *N, ibuf}                                  | nz00                  | 7      | MEM, *N, and ibuf are 24 bits.      |

| MEM = {ibufl, piop}                                    |                       | 7      | 8-bit transfer.                     |

| MEM = {ibuf, pdr, pdr2, pir, pcw}§                     |                       | 7      | 16-bit transfer.                    |

| MEM = {ibufe, pdre}§                                   |                       | 7      | 32-bit transfer.                    |

| {obufl, piop} = MEM                                    |                       | 7      | 8-bit transfer.                     |

| {obuf, pdr, pdr2, pir, pcw} = MEM                      | _                     | 7      | 16-bit transfer.                    |

| {obufe, pdre} = MEM                                    | _                     | 7      | 32-bit transfer.                    |

Table 18. Replacement Table for All CA Instructions

| Replace    | Value                                      | Description                                                                                                           |

|------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| rH         | pc, r1—r22                                 | One of 22 general-purpose registers, or the program counter.                                                          |

| rM, rS, rD | r1—r22                                     | One of 22 CAU registers.                                                                                              |

| rDh, rSh   | r1—r22                                     | High-order bits 8—15 are moved. The low-order bits 0—7 are cleared for <b>rD</b> and remain unchanged for <b>rS</b> . |

| rDI, rSI   | r1—r22                                     | Low-order bits 0—7 are moved. The high-order bits are cleared for <b>rD</b> and remain unchanged for <b>rS</b> .      |

| MEM        | *rP, *rP++, *rP,<br>*rP++rl, (P, I = 1—22) | 32-bit, 16-bit, or 8-bit memory location.                                                                             |

| N          | 16-bit number                              | Two's complement integer.                                                                                             |

| М          | 24-bit number                              | Two's complement integer.                                                                                             |

| VALUE      | 21-bit number or<br>5-bit number           | VALUE is a 21-bit value for the <b>ioc</b> word and a 5-bit value for the <b>dauc</b> word.                           |

<sup>†</sup> ioc = VALUE may not be used in an interrupt routine.

† rD = {pdr, pdr2, pir, pcw} cannot be used in the presence of 32-bit PIO DMA.

§ MEM = {pdr, pdr2, pir, pcw, pdre} cannot be used in the presence of PIO DMA.

## **Instruction Encoding**

The following sections specify the device level encoding of the DSP32C instruction set.

#### **DA Instruction Formats**

Format 1. [Z=] aN =  $\{+,-\}$  Y  $\{+,-\}$  aM \* X

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20—14 | 13—7 | 6—0 |

|-------|----|----|----|----|----|----|----|----|----|----|----|-------|------|-----|

| Field | 0  | 0  | 1  |    | М  |    | r  | F  | S  | 1  | ٧  | X     | Υ    | Z   |

Format 2.  $aN = \{+,-\} aM \{+,-\} (Z=Y) * X$

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20—14 | 13—7 | 6—0 |

|-------|----|----|----|----|----|----|----|----|----|----|----|-------|------|-----|

| Field | 0  | 1  | 0  |    | М  |    | r  | F  | S  | 1  | ٧  | Х     | Υ    | Z   |

Format 3. [Z=] aN =  $\{+,-\}$  aM  $\{+,-\}$  Y \* X

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20—14 | 13—7 | 6—0 |

|-------|----|----|----|----|----|----|----|----|----|----|----|-------|------|-----|

| Field | 0  | 1  | 1  |    | М  |    | r  | F  | S  | 1  | N  | X     | Υ    | Z   |

Format 4.  $aN = \{+,-\} (Z = Y) \{+,-\} X$

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20—14 | 13—7 | 6—0 |

|-------|----|----|----|----|----|----|----|----|----|----|----|-------|------|-----|

| Field | 0  | 0  | 1  | 1  | 1  | 0  | r  | F  | S  | 1  | ١  | Х     | Y    | Z   |

#### Format 5. Special Function Instructions

| Bit   | 31 | 30 | 29 | 28 | 27 | 26—23 | 22 | 21 | 20—14   | 13—7 | 6—0 |

|-------|----|----|----|----|----|-------|----|----|---------|------|-----|

| Field | 0  | 1  | 1  | 1  | 1  | G     | 1  | ٧  | 0000000 | Y    | Z   |

### **Encoding for DA Instruction Formats**

**G Field.** Specifies a data-type conversion operation.

| G    | Operation                  |

|------|----------------------------|

| 0000 | ic (input conversion)      |

| 0001 | oc (output conversion)     |

| 0010 | float                      |

| 0011 | int                        |

| 0100 | round                      |

| 0101 | ifalt                      |

| 0110 | ifaeq                      |

| 0111 | ifagt                      |

| 1000 | Reserved                   |

| 1001 | Reserved                   |

| 1010 | float24                    |

| 1011 | int24                      |

| 1100 | ieee (convert DSP to IEEE) |

| 1101 | dsp (convert IEEE to DSP)  |

| 1110 | seed                       |

| 1111 | Reserved                   |

**M Field.** Specifies the accumulator used or a constant value.

| M   | Operation                       |

|-----|---------------------------------|

| 000 | a0                              |

| 001 | a1                              |

| 010 | a2                              |

| 011 | a3                              |

| 100 | 0.0                             |

| 101 | 1.0                             |

| 110 | Specifies Format 4 DAU instruc- |

|     | tion                            |

| 111 | Reserved                        |

**F Field.** Specifies sign of operation (adder input).

| F | Operation |

|---|-----------|

| 0 | +         |

| 1 | _         |

**S Field.** Specifies sign of operation (product).

| S | Operation |

|---|-----------|

| 0 | +         |

| 1 | _         |

**r Field.** Specifies bit-reversed addressing mode (carry-reverse add with register).

| r | Operation       |

|---|-----------------|

| 0 | Nonbit-reversed |

| 1 | Bit-reversed    |

X, Y, Z Fields. These fields indicate register direct or register indirect modes. The 7-bit fields are divided into two subfields, p and i (ppppiii). Bits 0—2 of the 7-bit field are labeled i. The i subfield specifies an rI register in the CAU. Bits 3—6 are labeled p. The p field specifies an rP register in the CAU.

**p Field.** Specifies register indirect: \*rP, \*rP++, \*rP--, \*rP++rI, \*rP++rIr.

| р    | Operation                            |

|------|--------------------------------------|

| 0000 | Selects register direct <sup>†</sup> |

| 0001 | r1                                   |

| 0010 | r2                                   |

| 0011 | r3                                   |

| 0100 | r4                                   |

| 0101 | r5                                   |

| 0110 | r6                                   |

| 0111 | r7                                   |

| 1000 | r8                                   |

| 1001 | r9                                   |

| 1010 | r10                                  |

| 1011 | r11                                  |

| 1100 | r12                                  |

| 1101 | r13                                  |

| 1110 | r14                                  |

| 1111 | Not allowed                          |

<sup>†</sup> See i field (p = 0000).

## **Encoding for DA Instruction Formats** (continued)

N Field. Specifies the accumulator used.

| N  | Operation |

|----|-----------|

| 00 | a0        |

| 01 | a1        |

| 10 | a2        |

| 11 | аЗ        |

i Field (p  $\neq$  0000). Specifies register-indirect: rI, rP++rI.

| i   | Operation (p ≠ 0000) |

|-----|----------------------|

| 000 | 0                    |

| 001 | r15                  |

| 010 | r16                  |

| 011 | r17                  |

| 100 | r18                  |

| 101 | r19                  |

| 110 | -4(f), -2(i), -1(b)  |

| 111 | +4(f), +2(i), +1(b)  |

**i Field (p = 0000).** Specifies a register-direct operation: REG. This is a special case of the i field (when p field equals zero).

| i   | Operation (p = 0000)    |

|-----|-------------------------|

| 000 | a0 - X, Y fields only   |

| 001 | a1 – X, Y fields only   |

| 010 | a2 – X, Y fields only   |

| 011 | a3 – X, Y fields only   |

| 100 | ibuf – X, Y fields only |

| 101 | obuf – Z field only     |

| 110 | pdr – Y, Z fields       |

| 111 | No write, Z field only  |

## **CA Instruction Formats (Eight Format Groups)**

Refer to CAU Encoding for CA Instruction Formats for an explanation of each field, except where actual bit values (0, 1) are given.

Formats 0 and 1. Conditional Branch: 24-Bit Register-Indirect with 16-Bit Sign-Extended Offset.

| Bit   | 31 | 30 | 29 | 28 | 27 | 26—22 | 21 | 20—16 | 15—0 |

|-------|----|----|----|----|----|-------|----|-------|------|

| Field | 0  | 0  | 0  | 0  | 0  | С     | G  | Н     | N    |

For **ireturn** instruction, C = 00000, G = 1, H = pcsh = 11110, N = 0. For **nop** instruction, C = 00000, G = 0, H = 00000, N = 0.

#### Format 2. Reserved

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25—20 | 19—15 | 14—10 | 9—5 | 4—0 |

|-------|----|----|----|----|----|----|-------|-------|-------|-----|-----|

| Field | 0  | 0  | 0  | 0  | 1  | 0  | _     | _     |       | _   |     |

#### Format 3a. Loop Counter

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25—21 | 20—16 | 15—0 |

|-------|----|----|----|----|----|----|-------|-------|------|

| Field | 0  | 0  | 0  | 0  | 1  | 1  | М     | Н     | N    |

### CA Instruction Formats (Eight Format Groups) (continued)

#### Format 3b. Do Instruction (Immediate)

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25—21 | 20—16 | 15—11 | 10—0 |

|-------|----|----|----|----|----|----|-------|-------|-------|------|

| Field | 1  | 0  | 0  | 0  | 1  | 1  | 00000 | J     | 00000 | K    |

#### Format 3c. Do Instruction (Register)

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25—21 | 20—16 | 15—5       | 4—0 |

|-------|----|----|----|----|----|----|-------|-------|------------|-----|

| Field | 1  | 0  | 0  | 0  | 1  | 1  | 00001 | J     | 0000000000 | Н   |

#### Format 4. Call: 24-Bit Register-Indirect with 16-Bit Immediate Offset

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25—21 | 20—16 | 15—0 |

|-------|----|----|----|----|----|----|-------|-------|------|

| Field | 0  | 0  | 0  | 1  | 0  | 0  | М     | Н     | N    |

#### Format 5a. 16-Bit Three Operand Add

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25—21 | 20—16 | 15—0 |

|-------|----|----|----|----|----|----|-------|-------|------|

| Field | 0  | 0  | 0  | 1  | 0  | 1  | D     | Н     | N    |

#### Format 5b. 24-Bit Three Operand Add with 16-Bit Sign-Extended Immediate

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25—21 | 20—16 | 15—0 |

|-------|----|----|----|----|----|----|-------|-------|------|

| Field | 1  | 0  | 0  | 1  | 0  | 1  | D     | Н     | N    |

#### Format 6a. 16-Bit Arithmetic/Logic Group — Register Source

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24—21 | 20—16 | 15—13 | 12 | 11 | 10 | 9—5 | 4—0 |

|-------|----|----|----|----|----|----|----|-------|-------|-------|----|----|----|-----|-----|

| Field | 0  | 0  | 0  | 1  | 1  | 0  | 0  | F     | D     | C*    | G  | Е  | K  | S1  | S2  |

<sup>\*</sup> Three least significant bits of the C field (CA conditions only).

#### Format 6b. 24-Bit Arithmetic/Logic Group — Register Source

| Bi  | t   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24—21 | 20—16 | 15—13 | 12 | 11 | 10 | 9—5 | 4—0 |

|-----|-----|----|----|----|----|----|----|----|-------|-------|-------|----|----|----|-----|-----|

| Fie | eld | 1  | 0  | 0  | 1  | 1  | 0  | 0  | F     | D     | C*    | G  | Е  | K  | S1  | S2  |

<sup>\*</sup> Three least significant bits of the C field (CA conditions only).

#### Format 6c. 16-Bit Arithmetic/Logic Group — Immediate Operand

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24—21 | 20—16 | 15—0 |

|-------|----|----|----|----|----|----|----|-------|-------|------|

| Field | 0  | 0  | 0  | 1  | 1  | 0  | 1  | F     | D     | N    |

#### Format 6d. 24-Bit Arithmetic/Logic Group — Immediate Operand

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24—21 | 20—16 | 15—0 |

|-------|----|----|----|----|----|----|----|-------|-------|------|

| Field | 1  | 0  | 0  | 1  | 1  | 0  | 1  | F     | D     | N    |

### CA Instruction Formats (Eight Format Groups) (continued)

Format 7a. Data Move Group — Direct Memory Address

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20—16 | 15—0 |

|-------|----|----|----|----|----|----|----|----|----|----|----|-------|------|

| Field | 0  | 0  | 0  | 1  | 1  | 1  | 0  | Т  | ١  | N  | 0  | Н     | N    |

Format 7b. Data Move Group — Pointer Increment, Memory Address

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20—16 | 15—11 | 10 | 9—5 | 4—0 |

|-------|----|----|----|----|----|----|----|----|----|----|----|-------|-------|----|-----|-----|

| Field | 0  | 0  | 0  | 1  | 1  | 1  | 1  | Т  | ٧  | ٧  | 1  | Н     |       | r  | Р   | 1   |

Format 7c. Data Move Group — I/O

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20—16 | 15—10 | 9—5   | 4—0 |

|-------|----|----|----|----|----|----|----|----|----|----|----|-------|-------|-------|-----|

| Field | 0  | 0  | 0  | 1  | 1  | 1  | 1  | Т  | ٧  | V  | 0  | Н     | _     | 00000 | R   |

Format 7d. Data Move Group — Memory to I/O

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20—16 | 15—11 | 10 | 9—5 | 4—0 |

|-------|----|----|----|----|----|----|----|----|----|----|----|-------|-------|----|-----|-----|

| Field | 0  | 0  | 0  | 1  | 1  | 1  | 0  | Т  | ٧  | V  | 1  | R     |       | r  | Р   | I   |

Format 8a. Unconditional Branch: 24-Bit Register-Indirect with 24-Bit Offset

| Bit   | 31 | 30 | 29 | 28—21 | 20—16 | 15—0 |

|-------|----|----|----|-------|-------|------|

| Field | 1  | 0  | 1  | NE    | Н     | N    |

Format 8b. 24-Bit Immediate Load

| Bit   | 31 | 30 | 29 | 28—21 | 20—16 | 15—0 |

|-------|----|----|----|-------|-------|------|

| Field | 1  | 1  | 0  | NE    | Н     | N    |

Format 8c. Call Subroutine: 24-Bit Direct Immediate Address

| Bit   | 31 | 30 | 29 | 28—21 | 20—16 | 15—0 |

|-------|----|----|----|-------|-------|------|

| Field | 1  | 1  | 1  | NE    | М     | N    |

### **CAU Encoding for CA Instruction Formats**

**C Field.** Specifies a CA, DA, or I/O condition. For Format 6a and 6b instructions, only CA conditions are allowed, and are specified by the three least significant bits of the C field.

| С     | Operation     |

|-------|---------------|

| 00xxx | CA Condition  |

| 00000 | No condition  |

| 00001 | n             |

| 00010 | z             |

| 00011 | V             |

| 00100 | С             |

| 00101 | n^v           |

| 00110 | z   (n ^ v)   |

| 00111 | c z           |

| 01xxx | DA Condition  |

| 01000 | U             |

| 01001 | N             |

| 01010 | Z             |