# **DSP56003/005**

# 24-BIT DIGITAL SIGNAL PROCESSOR USER'S MANUAL

Motorola, Inc. Semiconductor Products Sector DSP Division 6501 William Cannon Drive, West Austin, Texas 78735-8598

Order this document by DSP56003UM/AD

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not authorized for use as components in life support devices or systems intended for surgical implant into the body or intended to support or sustain life. Buyer agrees to notify Motorola of any such intended end use whereupon Motorola shall determine availability and suitability of its product or products for the use intended. Motorola and Aare registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Employment Opportunity /Affirmative Action Employer.

OnCE™ is a trade mark of Motorola, Inc.

© Motorola Inc., 1994

# **TABLE OF CONTENTS**

| Paragrap<br>Number                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Page<br>Number                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                            | SECTION 1<br>INTRODUCTION TO THE DSP56003/005                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                   |

| 1.1<br>1.1.2<br>1.1.3<br>1.1.4<br>1.1.5<br>1.2<br>1.3<br>1.3.1<br>1.3.2<br>1.3.2.1<br>1.3.2.2<br>1.3.2.3<br>1.3.2.4<br>1.3.2.5<br>1.3.2.5.1<br>1.3.2.5.1<br>1.3.2.5.1<br>1.3.2.5.3<br>1.3.2.5.4<br>1.3.2.5.4<br>1.3.2.5.4<br>1.3.2.5<br>1.3.2.9.1<br>1.3.2.9.1<br>1.3.2.9.1<br>1.3.2.9.2<br>1.3.2.9.3<br>1.3.2.9.5<br>1.3.2.9.5<br>1.3.2.9.5<br>1.3.2.9.5<br>1.3.2.9.5<br>1.3.2.9.5<br>1.3.2.9.6<br>1.3.2.9.7<br>1.3.2.9.8 | MANUAL INTRODUCTION Related Literature Training. Technical Assistance Manual Conventions. Manual Organization PRODUCT USE DSP56003/005 ARCHITECTURAL OVERVIEW DSP56003/005 Features Block Diagram Description Data Buses Address Buses Data ALU Address Generation Unit Memories Program Memory X Data Memory Y Data Memory Y Data Memory Y Data Memory Bootstrap ROM Program Control Unit Phase-locked Loop (PLL) On-chip Emulator (OnCE™) Port Input/Output External Memory Interface (Port A) General Purpose I/O (HI, SCI, SSI, Timer/Event Counter) Host Interface (HI) Serial Communication Interface (SCI) Synchronous Serial Interface (SSI) Timer/Event Counter Pulse Width Modulators (PWM) Watchdog Timer | . 1-3<br>. 1-6<br>. 1-6<br>. 1-7<br>. 1-9<br>. 1-11<br>. 1-12<br>. 1-13<br>. 1-14<br>. 1-15<br>. 1-15<br>. 1-16<br>. 1-18<br>. 1-18<br>. 1-18<br>. 1-18<br>. 1-18<br>. 1-19<br>. 1-19<br>. 1-20<br>. 1-20<br>. 1-21<br>. 1-21<br>. 1-22<br>. 1-22 |

|                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | · · · ——                                                                                                                                                                                                                                          |

|           | Table of Contents (Continued) |        |

|-----------|-------------------------------|--------|

| Paragraph |                               | Page   |

| Number    | Title                         | Number |

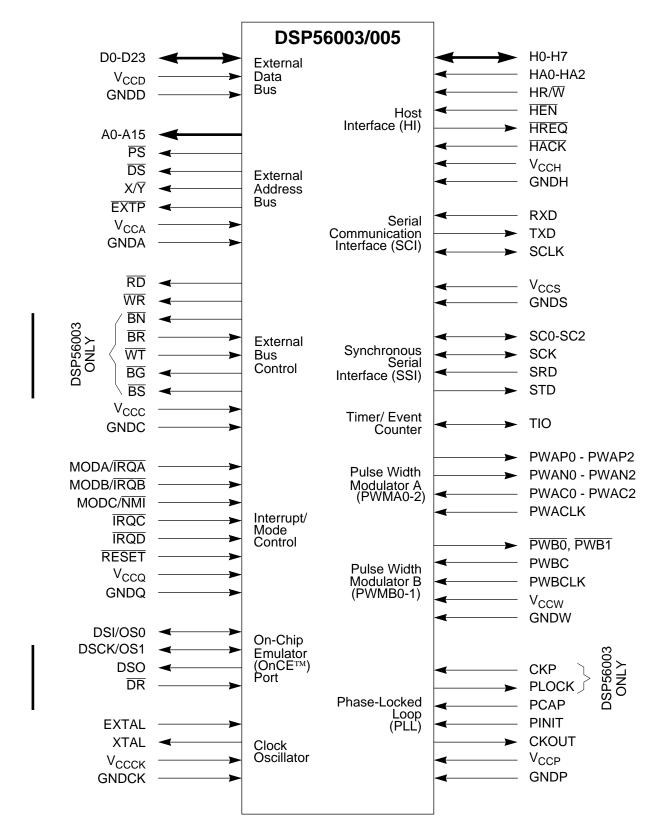

### SECTION 2 PIN DESCRIPTIONS

| 2.1     | INTRODUCTION                                                     |

|---------|------------------------------------------------------------------|

| 2.2     | PIN DESCRIPTIONS2-3                                              |

| 2.2.1   | Port A Address Bus, Data Bus, and Basic Bus Control 2-5          |

| 2.2.1.1 | Address Bus (A0–A15) — three-state, outputs2-5                   |

| 2.2.1.2 | Data Bus (D0–D23) — three-state, bidirectional input/outputs 2-5 |

| 2.2.1.3 | Program Memory Select (PS) — three-state, active low output2-5   |

| 2.2.1.4 | Data Memory Select (DS) — three-state, active low output 2-5     |

| 2.2.1.5 | $X/\overline{Y}$ Select $(X/\overline{Y})$ — three-state output  |

| 2.2.1.6 | Read Enable (RD) — three-state, active low output                |

| 2.2.1.7 | Write Enable (WR) — three-state, active low output2-6            |

| 2.2.1.8 | External Peripheral (EXTP) — active low output2-6                |

| 2.2.2   | Enhanced Bus Control                                             |

| 2.2.2.1 | Bus Needed (BN) — active low output — DSP56003 Only2-7           |

| 2.2.2.2 | Bus Request (BR) — active low input — DSP56003 Only 2-7          |

| 2.2.2.3 | Bus Grant (BG) — active low output — DSP56003 Only 2-8           |

| 2.2.2.4 | Bus Strobe (BS) — active low output — DSP56003 Only2-8           |

| 2.2.2.5 | Bus Wait (WT) — active low input — DSP56003 Only                 |

| 2.2.3   | Host Interface                                                   |

| 2.2.3.1 | Host Data Bus (H0–H7) — bidirectional                            |

| 2.2.3.2 | Host Address (HA0–HA2) — input2-9                                |

| 2.2.3.3 | Host Read/Write (HR/W) — input*2-9                               |

| 2.2.3.4 | Host Enable (HEN) — active low input*2-9                         |

| 2.2.3.5 | Host Request (HREQ) — active low output*2-9                      |

| 2.2.3.6 | Host Acknowledge (HACK) — active low input*                      |

| 2.2.4   | Serial Communication Interface (SCI)2-10                         |

| 2.2.4.1 | Receive Data (RXD) — input*2-10                                  |

| 2.2.4.2 | Transmit Data (TXD) — output*2-10                                |

| 2.2.4.3 | SCI Serial Clock (SCLK) — bidirectional2-11                      |

| 2.2.5   | Synchronous Serial Interface (SSI)2-11                           |

| 2.2.5.1 | Serial Control 0 (SC0) — bidirectional2-11                       |

| 2.2.5.2 | Serial Control 1 (SC1) — bidirectional2-11                       |

| 2.2.5.3 | Serial Control 2 (SC2) — bidirectional2-11                       |

| 2.2.5.4 | SSI Serial Clock (SCK) — bidirectional2-11                       |

| 2.2.5.5 | SSI Receive Data (SRD) — input*2-12                              |

| 2.2.5.6 | SSI Transmit Data (STD) — output*                                |

| 2.2.6   | Timer/Event Counter Pin2-12                                      |

| 2.2.6.1 | Timer/Event Counter Input/Output (TIO) — bidirectional2-12       |

|           | Table of Contents (Continued)                               |        |

|-----------|-------------------------------------------------------------|--------|

| Paragraph | · · · ·                                                     | Page   |

| Number    | Title                                                       | Number |

|           |                                                             |        |

| 2.2.7     | Dulco Width Modulator A (DWMA)                              | 2.42   |

| 2.2.7     | Pulse Width Modulator A (PWMA)                              | 2-12   |

| 2.2.7.1   | output                                                      | 2-12   |

| 2.2.7.2   | Pulse Width Modulator A Negative (PWAN0 - PWAN2) —          | 2-12   |

| 2.2.7.2   | output                                                      | 2-13   |

| 2.2.7.3   | Pulse Width Modulator A Carrier (PWAC0 - PWAC2) — input     | 2-13   |

| 2.2.7.4   | Pulse Width Modulator A Clock (PWACLK) — input              |        |

| 2.2.8     | Pulse Width Modulator B (PWMB)                              |        |

| 2.2.8.1   | Pulse Width Modulator B Carrier (PWBC) — input              |        |

| 2.2.8.2   | Pulse Width Modulator B Output (PWB0-PWB1) —                |        |

| 2.2.0.2   | active low output                                           | 2-14   |

| 2.2.8.3   | Pulse Width Modulator B Clock (PWBCLK) — input              |        |

| 2.2.9     | On-Chip Emulation (OnCE™) Port                              |        |

| 2.2.9.1   | Debug Serial Input/Chip Status 0 (DSI/OS0) — bidirectional  |        |

| 2.2.9.2   | Debug Serial Clock/Chip Status 1 (DSCK/OS1) — bidirectional |        |

| 2.2.9.3   | Debug Serial Output (DSO) — output                          |        |

| 2.2.9.4   | Debug Request (DR) — active low input                       |        |

| 2.2.10    | Power and Ground                                            |        |

| 2.2.10.1  | Power                                                       |        |

| 2.2.10.2  | Ground                                                      |        |

| 2.2.11    | Interrupt and Mode Control                                  |        |

| 2.2.11.1  | Mode Select A/External Interrupt Request A (MODA/IRQA) —    | •      |

|           | input                                                       | 2-18   |

| 2.2.11.2  | Mode Select B/External Interrupt Request B (MODB/IRQB) —    |        |

|           | input                                                       | 2-18   |

| 2.2.11.3  | Mode Select C/Non-Maskable Interrupt Request (MODC/NMI) —   |        |

|           |                                                             | 2-19   |

| 2.2.11.4  | External Interrupt Request C (IRQC) — edge triggered input  |        |

| 2.2.11.5  | External Interrupt Request D (IRQD) — edge triggered input  |        |

| 2.2.11.6  | Reset (RESET) — input                                       |        |

| 2.2.12    | Clock, Oscillator, and PLL Pins                             | 2-20   |

| 2.2.12.1  | Output Clock (CKOUT) — output                               |        |

| 2.2.12.2  | CKOUT Polarity Control (CKP) — input. — DSP56003 Only       |        |

| 2.2.12.3  | External Clock/Crystal (EXTAL) — input                      |        |

| 2.2.12.4  | Crystal (XTAL) — output                                     |        |

| 2.2.12.5  | PLL Filter Capacitor (PCAP) — input                         | 2-21   |

| 2.2.12.6  | PLL Initialization (PINIT) — input                          |        |

| 2.2.12.7  | Phase and Frequency Locked (PLOCK) — output —               |        |

|           | DSP56003 Only                                               | 2-21   |

|                                                                                                                                                                                                                  | Table of Contents (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Paragrap<br>Number                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page<br>Numbe                                        |

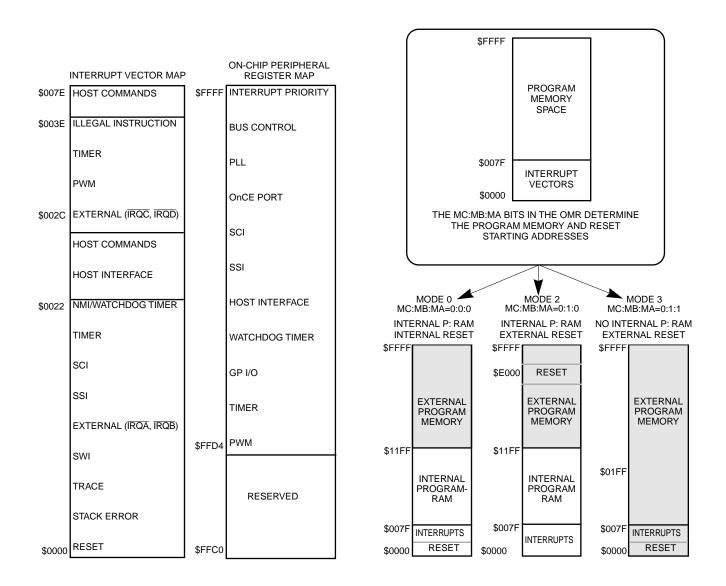

|                                                                                                                                                                                                                  | SECTION 3<br>MEMORY, OPERATING MODES,<br>AND INTERRUPTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                      |

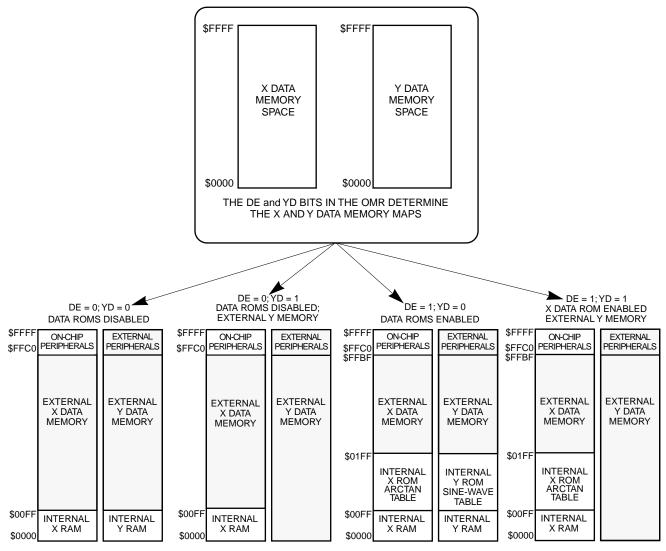

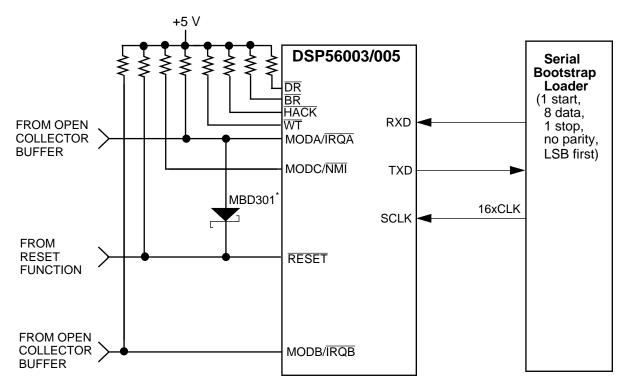

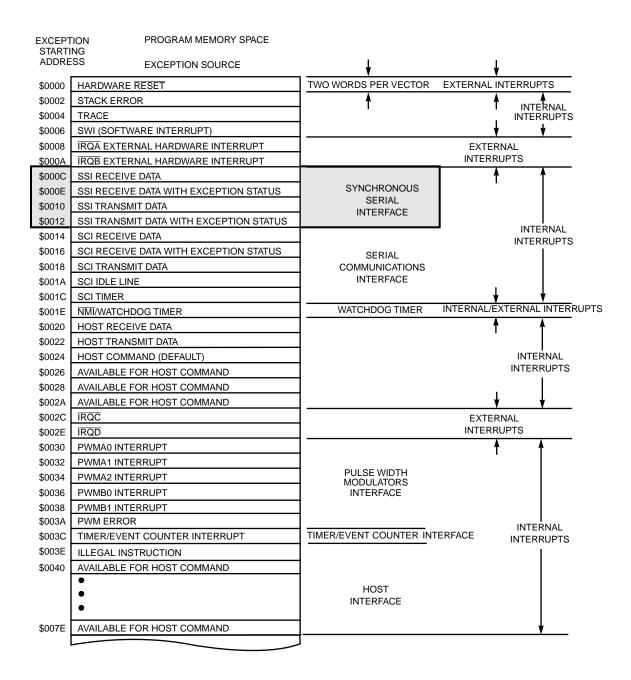

| 3.1<br>3.1.1<br>3.1.1.1<br>3.1.1.2<br>3.1.1.3<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.7<br>3.3.8<br>3.4<br>3.5 | MEMORY INTRODUCTION DSP56003/005 Data and Program Memory Program Memory X Data Memory Y Data Memory DSP56003/005 OPERATING MODE REGISTER (OMR) OMR Chip Operating Mode (MC, MB, MA) Bits 4, 1, and 0 OMR Data ROM Enable (DE) Bit 2 OMR Internal Y Memory Disable (YD) Bit 3 OMR Chip Operating Mode (MC) Bit 4 OMR Reserved Bit 5 OMR Stop Delay (SD) Bit 6 OMR Reserved Bits 7–23 DSP56003/005 OPERATING MODES Single Chip Mode (Mode 0) Bootstrap From EPROM at \$C000 (Mode 1) Normal Expanded Mode (Mode 2) Development Mode (Mode 3) Reserved (Mode 4) Bootstrap From Host (Mode 5) Bootstrap From SCI (Mode 6) Bootstrap From EPROM at \$8000 (Mode 7) DSP56003/005 PHASE-LOCKED LOOP (PLL) CONFIGURATIO | 3-33-33-43-53-63-63-73-73-73-73-13-13-113-123-123-12 |

|                                                                                                                                                                                                                  | SECTION 4 EXTERNAL MEMORY INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                      |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6                                                                                                                                                                           | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-3<br>4-9<br>4-12<br>4-12                           |

|                     | Table of Contents (Continued)                                                                                  |                          |

|---------------------|----------------------------------------------------------------------------------------------------------------|--------------------------|

| Paragraph<br>Number | Title                                                                                                          | Page<br>Number           |

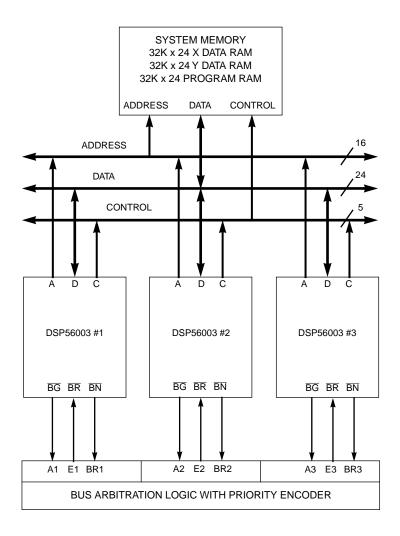

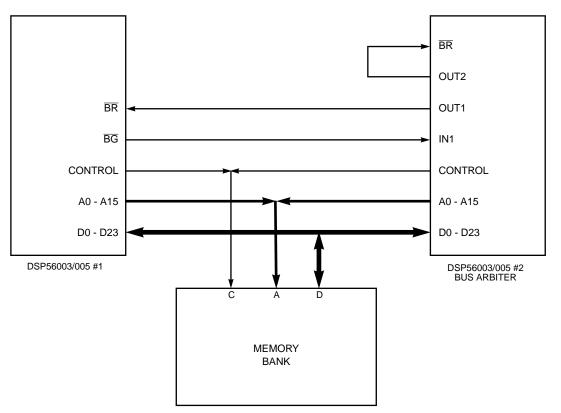

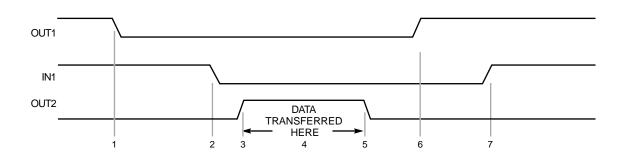

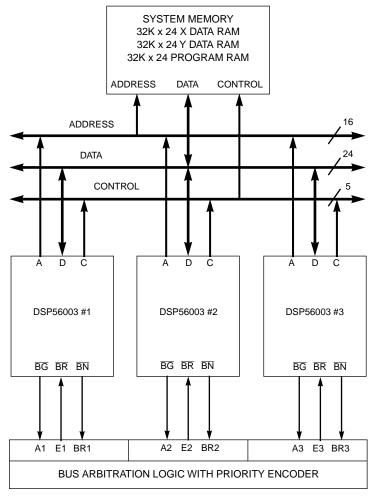

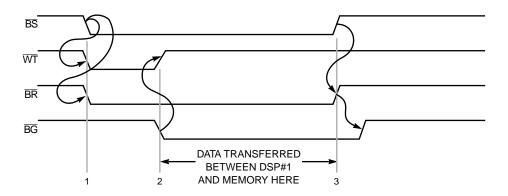

| 4.7<br>4.7.1        | BUS ARBITRATION AND SHARED MEMORY — DSP56003 Only Bus Arbitration Using Only BR and BG With Internal Control — | 4-16                     |

| 4.7.2               | DSP56003 Only                                                                                                  | 4-18                     |

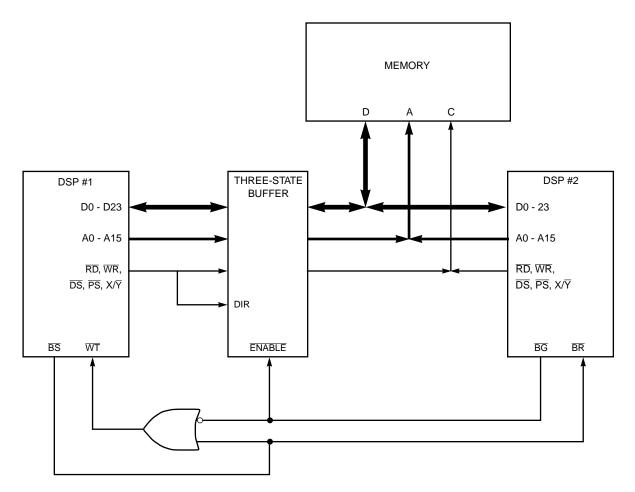

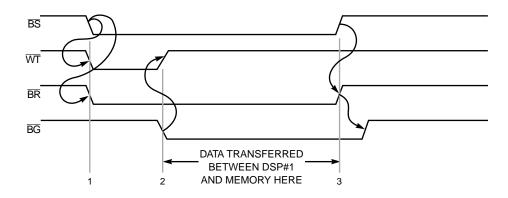

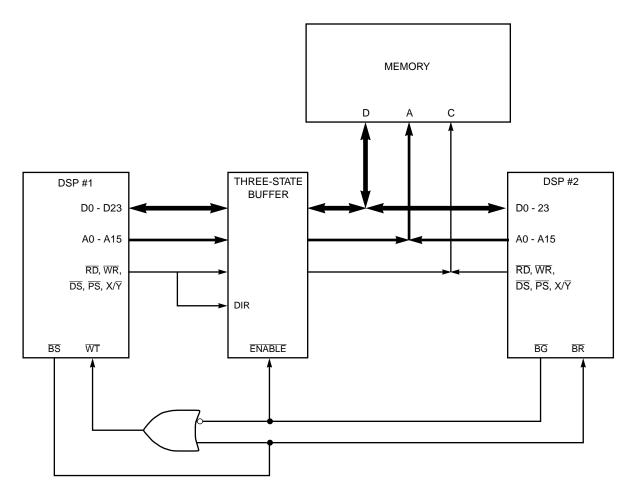

| 4.7.3               | DSP56003 Only                                                                                                  | 4-18                     |

| 4.7.4               | DSP56003 Only                                                                                                  | 4-20                     |

| 4.7.4               | Signaling Using Semaphores                                                                                     | 4-22                     |

|                     | SECTION 5<br>HOST INTERFACE                                                                                    |                          |

| 5.1                 | INTRODUCTION                                                                                                   | 5-3                      |

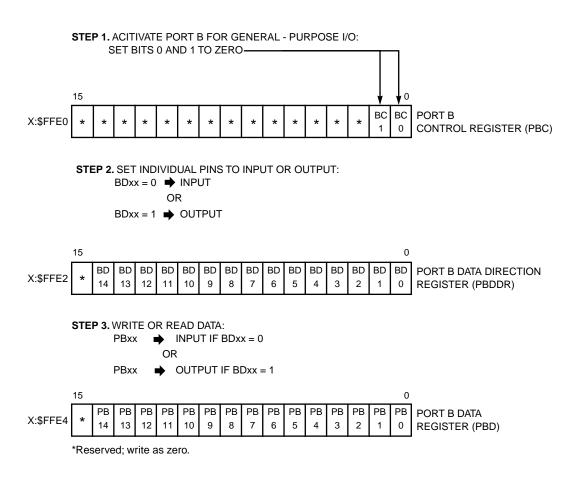

| 5.2                 | GENERAL PURPOSE I/O CONFIGURATION                                                                              |                          |

| 5.2.1               | Programming General Purpose I/O                                                                                |                          |

| 5.2.2               | Port B General Purpose I/O Timing                                                                              |                          |

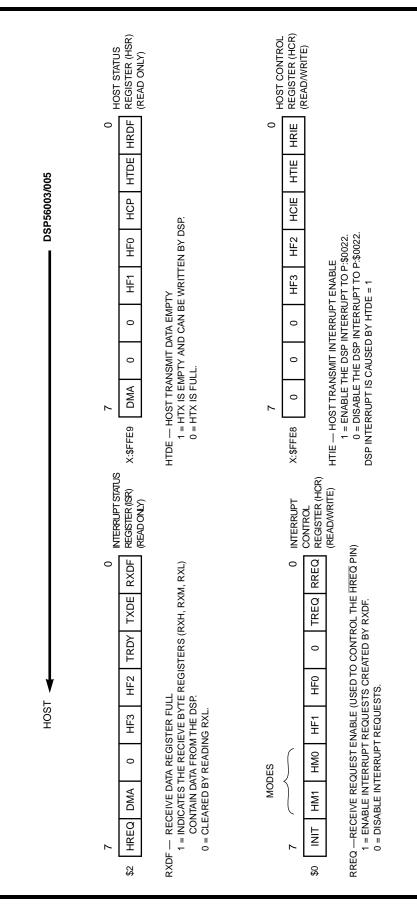

| 5.3                 | HOST INTERFACE (HI)                                                                                            | 5-10                     |

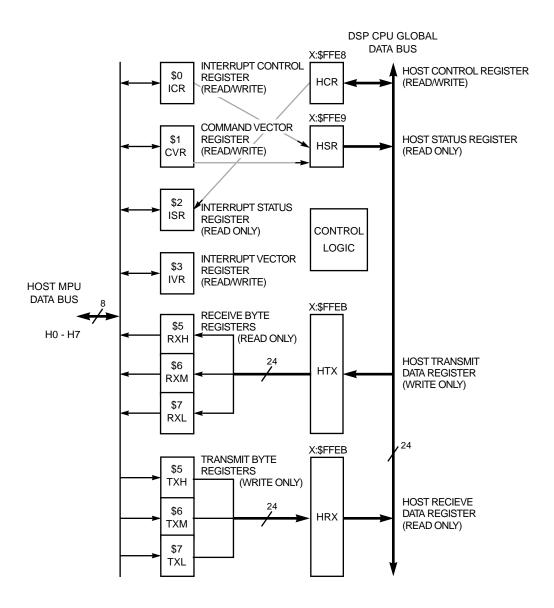

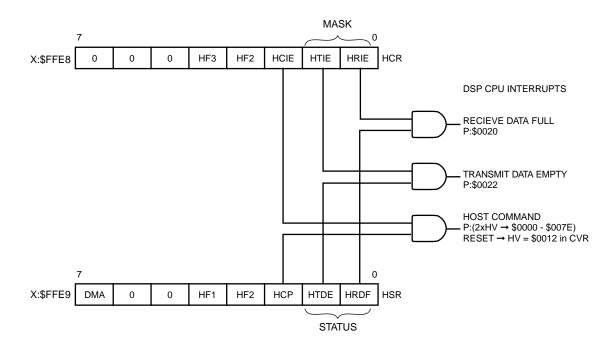

| 5.3.1               | Host Interface – DSP CPU Viewpoint                                                                             | 5-11                     |

| 5.3.2               | Programming Model – DSP CPU Viewpoint                                                                          |                          |

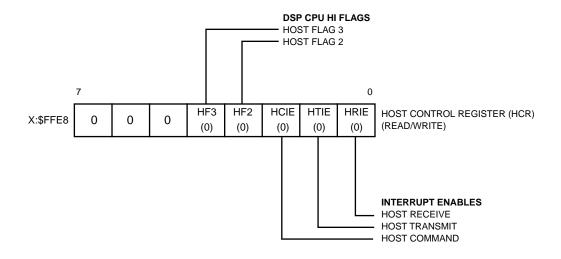

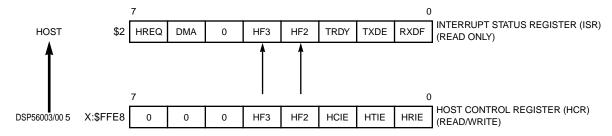

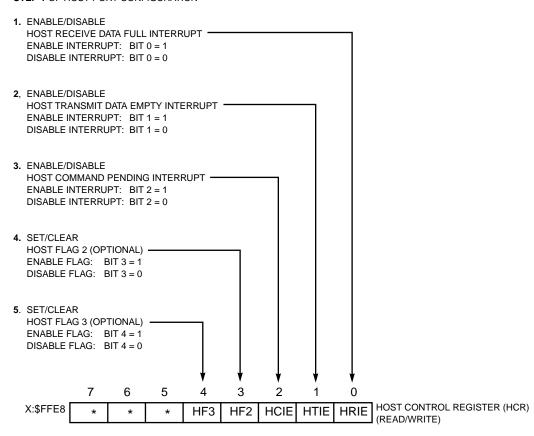

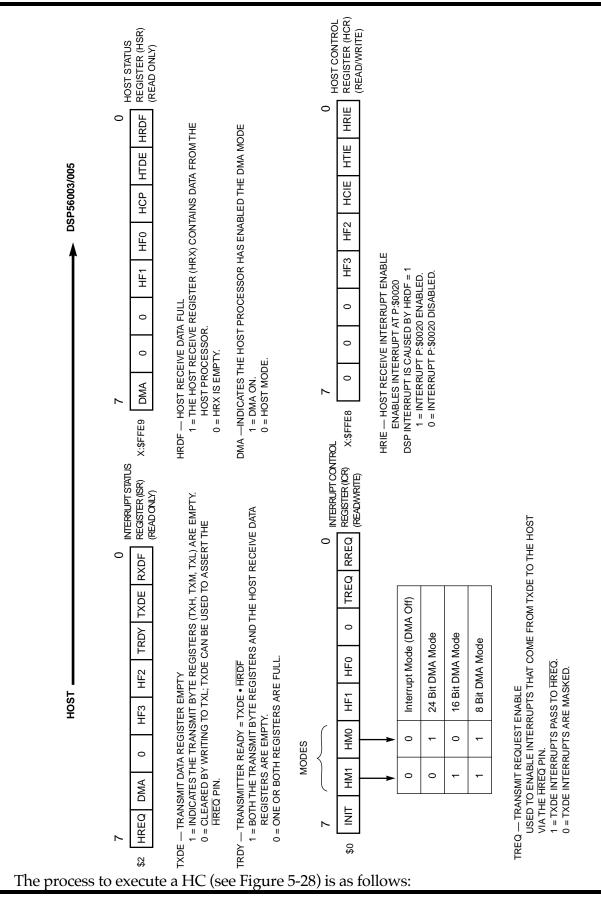

| 5.3.2.1             | Host Control Register (HCR)                                                                                    |                          |

| 5.3.2.1.1           | HCR Host Receive Interrupt Enable (HRIE) Bit 0                                                                 |                          |

| 5.3.2.1.2           | HCR Host Transmit Interrupt Enable (HTIE) Bit 1                                                                |                          |

| 5.3.2.1.3           | HCR Host Command Interrupt Enable (HCIE) Bit 2                                                                 |                          |

| 5.3.2.1.4           | HCR Host Flag 2 (HF2) Bit 3                                                                                    |                          |

| 5.3.2.1.5           | HCR Host Flag 3 (HF3) Bit 4                                                                                    |                          |

| 5.3.2.1.6           | HCR Reserved Bits 5, 6, and 7                                                                                  |                          |

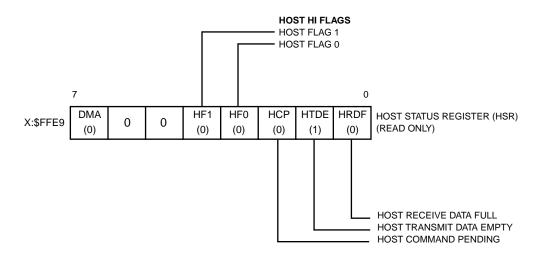

| 5.3.2.2             | Host Status Register (HSR)                                                                                     | . 5-15                   |

| 5.3.2.2.1           | HSR Host Receive Data Full (HRDF) Bit 0                                                                        |                          |

| 5.3.2.2.2           | HSR Host Transmit Data Empty (HTDE) Bit 1                                                                      |                          |

| 5.3.2.2.3           | HSR Host Command Pending (HCP) Bit 2                                                                           |                          |

| 5.3.2.2.4           | HSR Host Flag 0 (HF0) Bit 3                                                                                    |                          |

| 5.3.2.2.5           | HSR Host Flag 1 (HF1) Bit 4                                                                                    | . 5-16                   |

| 5.3.2.2.6           | HSR Reserved Bits 5 and 6                                                                                      |                          |

| 5.3.2.2.7           | HSR DMA Status (DMA) Bit 7                                                                                     |                          |

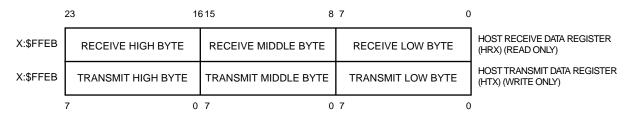

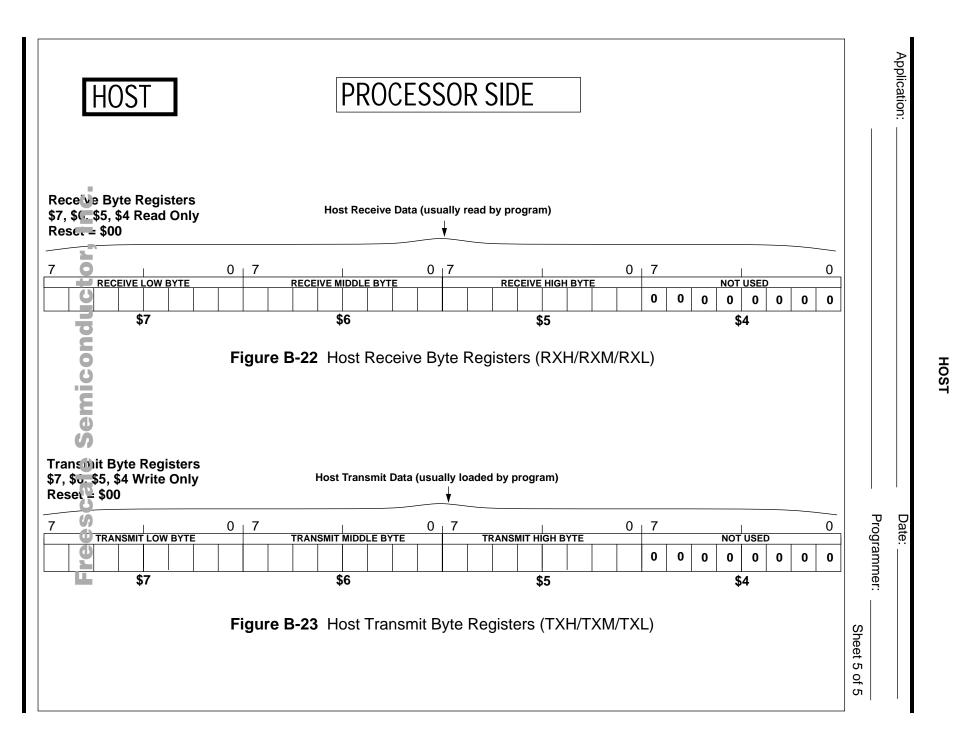

| 5.3.2.3             | Host Receive Data Register (HRX)                                                                               | . 3-1 <i>1</i><br>- 5-47 |

| 5.3.2.4             | Host Transmit Data Register (HTX)                                                                              |                          |

| 5.3.2.5             | Register Contents After Reset                                                                                  |                          |

| 5.3.2.6             | Host Interface DSP CPU Interrupts                                                                              | . J- 10                  |

|           | Table of Contents (Continued)                         |        |

|-----------|-------------------------------------------------------|--------|

| Paragraph |                                                       | Page   |

| Number    | Title                                                 | Number |

|           |                                                       |        |

| 5.3.2.7   | Host Port Use Considerations – DSP Side               |        |

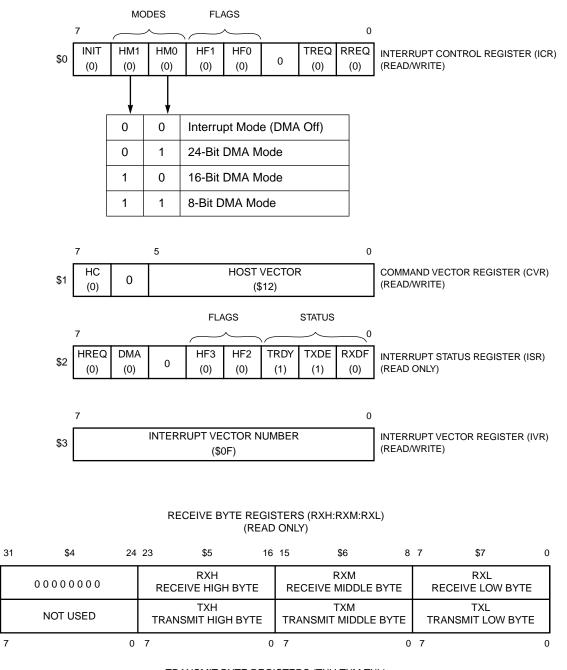

| 5.3.3     | Host Interface – Host Processor Viewpoint             |        |

| 5.3.3.1   | Programming Model – Host Processor Viewpoint          |        |

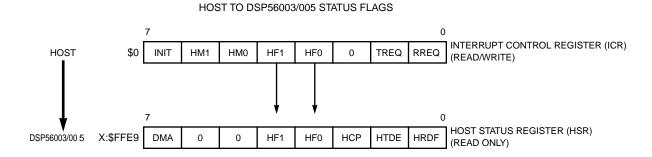

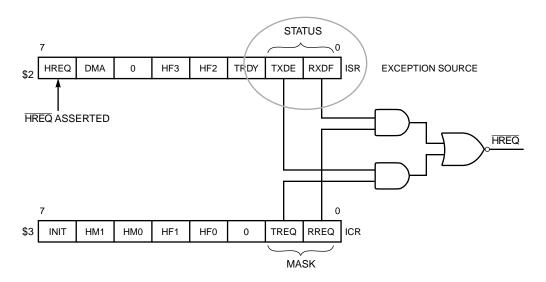

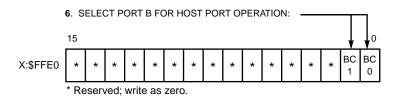

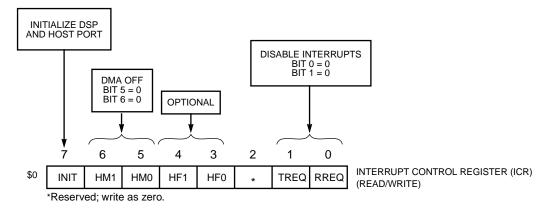

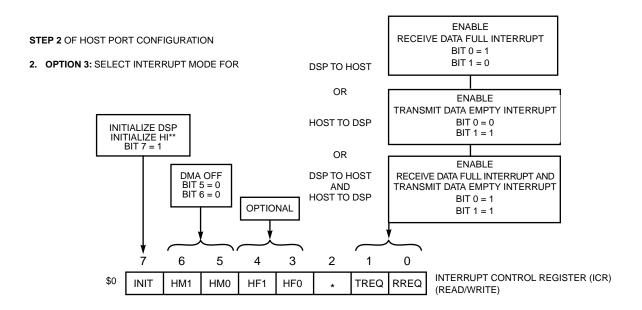

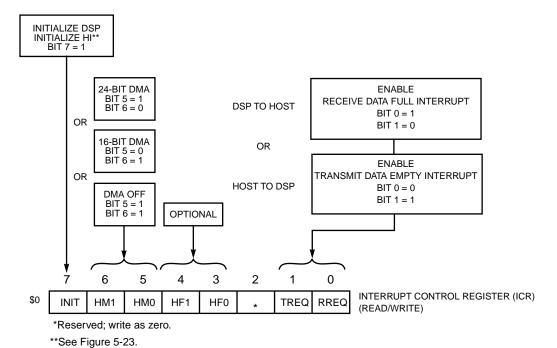

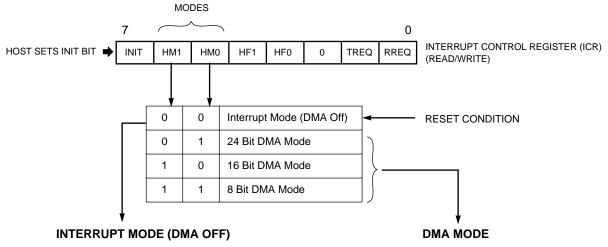

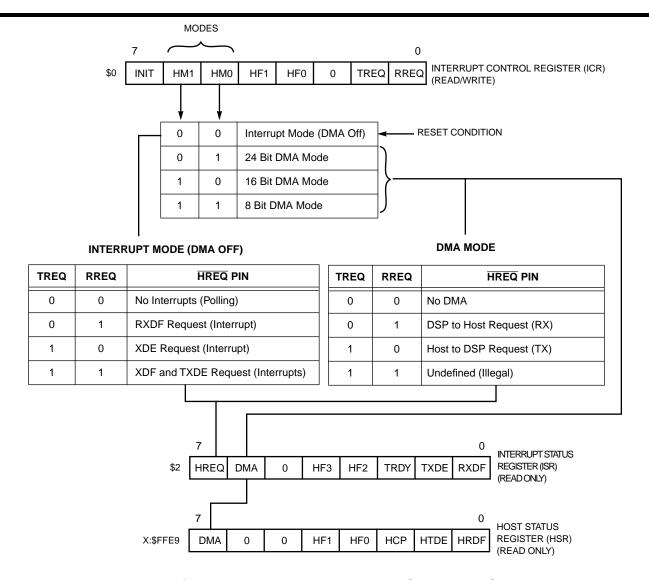

| 5.3.3.2   | Interrupt Control Register (ICR)                      | 5-20   |

| 5.3.3.2.1 | ICR Receive Request Enable (RREQ) Bit 0               |        |

| 5.3.3.2.2 | ICR Transmit Request Enable (TREQ) Bit 1              |        |

| 5.3.3.2.3 | ICR Reserved Bit 2                                    |        |

| 5.3.3.2.4 | ICR Host Flag 0 (HF0) Bit 3                           |        |

| 5.3.3.2.5 | ICR Host Flag 1 (HF1) Bit 4                           | 5-23   |

| 5.3.3.2.6 | ICR Host Mode Control (HM1 and HM0 bits) Bits 5 and 6 | 5-23   |

| 5.3.3.2.7 | ICR Initialize Bit (INIT) Bit 7                       |        |

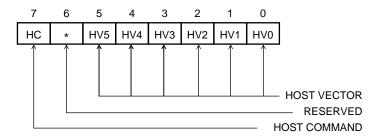

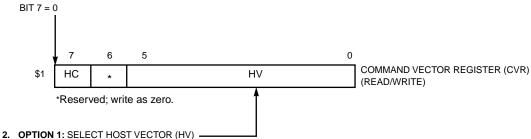

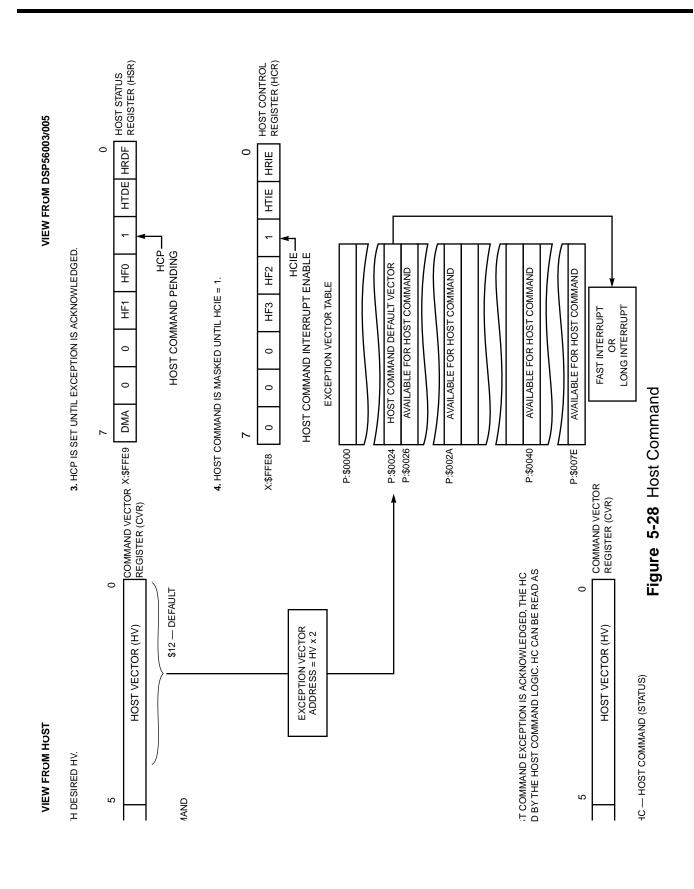

| 5.3.3.3   | Command Vector Register (CVR)                         | 5-26   |

| 5.3.3.3.1 | CVR Host Vector (HV) Bits 0–5                         |        |

| 5.3.3.3.2 | CVR Reserved Bit 6                                    | 5-27   |

| 5.3.3.3.3 | CVR Host Command Bit (HC) Bit 7                       | 5-27   |

| 5.3.3.4   | Interrupt Status Register (ISR)                       |        |

| 5.3.3.4.1 | ISR Receive Data Register Full (RXDF) Bit 0           | 5-27   |

| 5.3.3.4.2 | ISR Transmit Data Register Empty (TXDE) Bit 1         |        |

| 5.3.3.4.3 | ISR Transmitter Ready (TRDY) Bit 2                    |        |

| 5.3.3.4.4 | ISR Host Flag 2 (HF2) Bit 3                           |        |

| 5.3.3.4.5 | ISR Host Flag 3 (HF3) Bit 4                           |        |

| 5.3.3.4.6 | ISR Reserved Bit 5                                    |        |

| 5.3.3.4.7 | ISR DMA Status (DMA) Bit 6                            | 5-29   |

| 5.3.3.4.8 | ISR Host Request (HREQ) Bit 7                         |        |

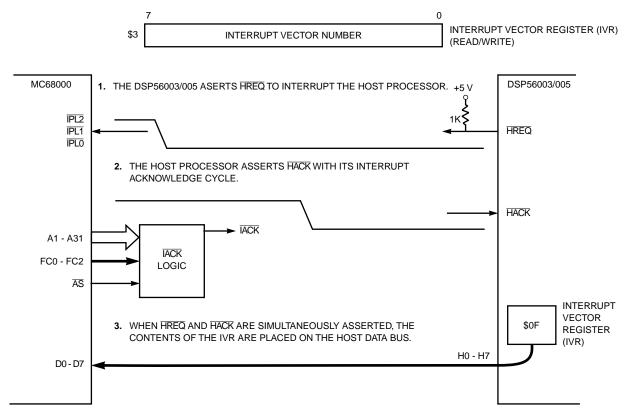

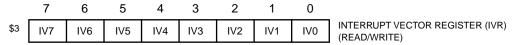

| 5.3.3.5   | Interrupt Vector Register (IVR)                       |        |

| 5.3.3.6   | Receive Byte Registers (RXH, RXM, RXL)                |        |

| 5.3.3.7   | Transmit Byte Registers (TXH, TXM, TXL)               | 5-30   |

| 5.3.3.8   | Registers After Reset                                 |        |

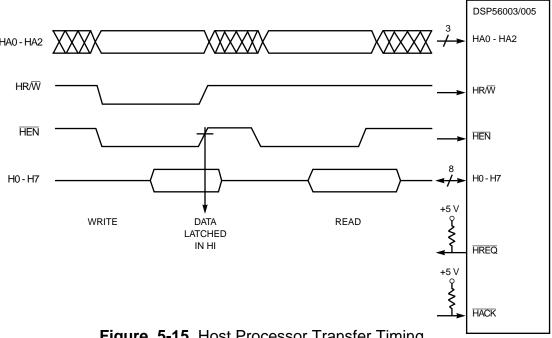

| 5.3.4     | Host Interface Pins                                   |        |

| 5.3.4.1   | Host Data Bus (H0-H7)                                 |        |

| 5.3.4.2   | Host Address (HA0-HA2)                                |        |

| 5.3.4.3   | Host Read/Write (HR/W)                                |        |

| 5.3.4.4   | Host Enable (HEN)                                     |        |

| 5.3.4.5   | Host Request (HREQ)                                   | 5-32   |

| 5.3.4.6   | Host Acknowledge (HACK)                               |        |

| 5.3.5     | Servicing the Host Interface                          |        |

| 5.3.5.1   | HI Host Processor Data Transfer                       |        |

| 5.3.5.2   | HI Interrupts Host Request (HREQ)                     |        |

| 5.3.5.3   | Polling                                               |        |

|           |                                                       |        |

|                     | Table of Contents (Continued)                       |                |

|---------------------|-----------------------------------------------------|----------------|

| Paragraph<br>Number | Title                                               | Page<br>Number |

|                     |                                                     |                |

| 5.3.5.4             | Servicing Non-DMA Interrupts                        |                |

| 5.3.5.5             | Servicing DMA Interrupts                            |                |

| 5.3.6               | HI Application Examples                             |                |

| 5.3.6.1             | HI Initialization                                   |                |

| 5.3.6.2             | Polling/Interrupt Controlled Data Transfer          |                |

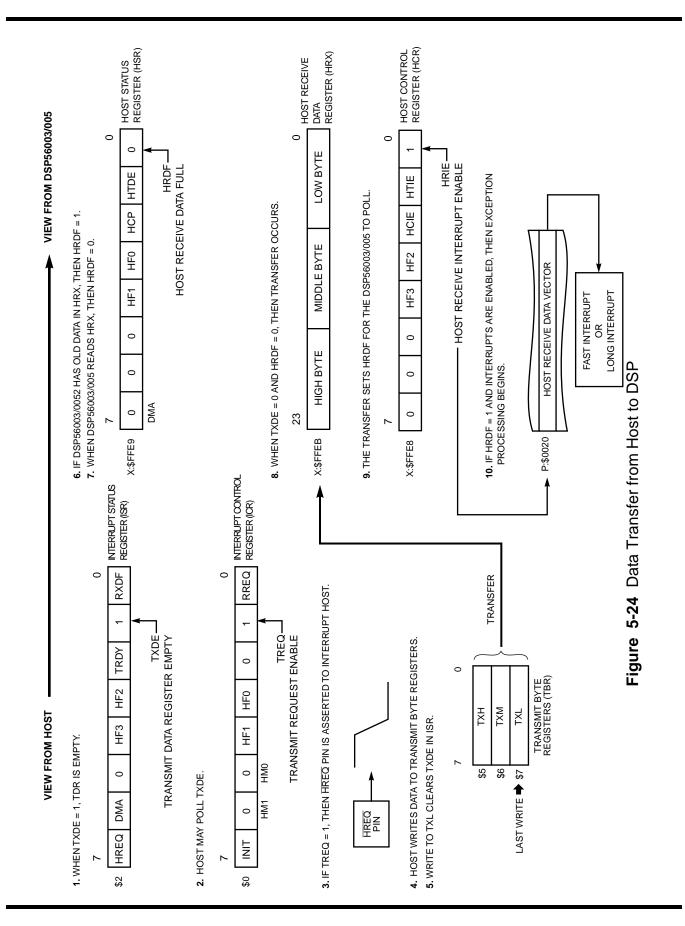

| 5.3.6.2.1           | Host to DSP — Data Transfer                         | . 5-40         |

| 5.3.6.2.2           | Host to DSP — Command Vector                        | . 5-43         |

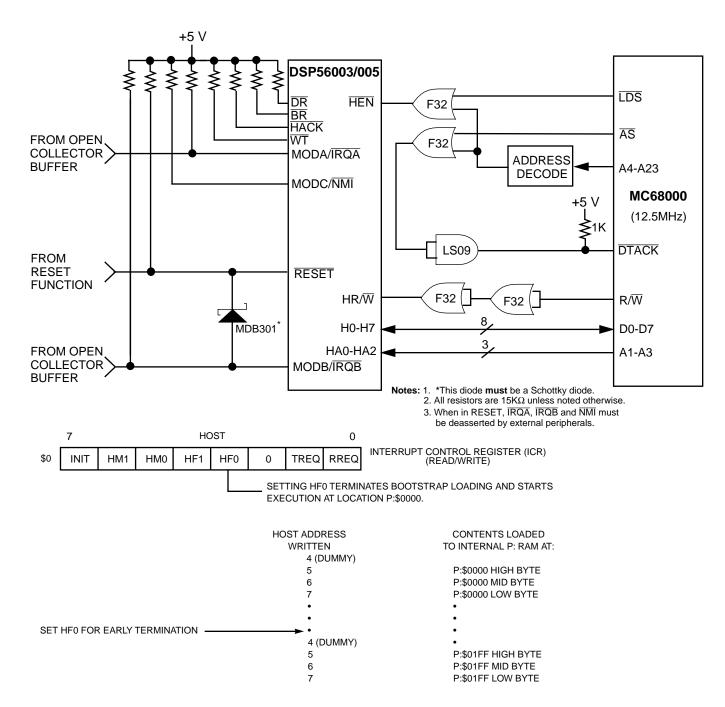

| 5.3.6.2.3           | Host to DSP — Bootstrap Loading Using the HI        | . 5-50         |

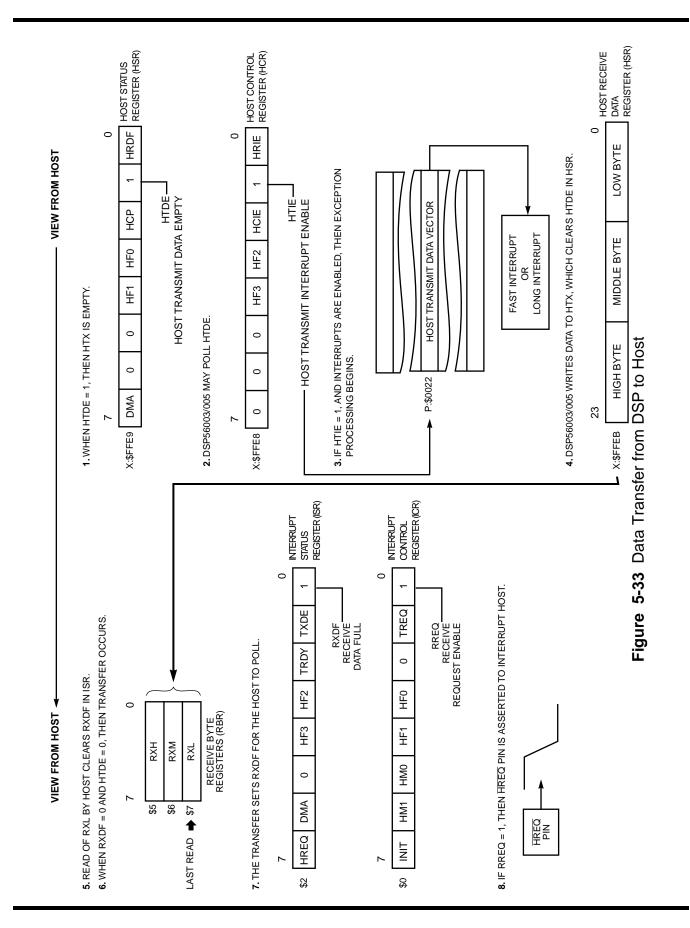

| 5.3.6.2.4           | DSP to Host Data Transfer                           | . 5-51         |

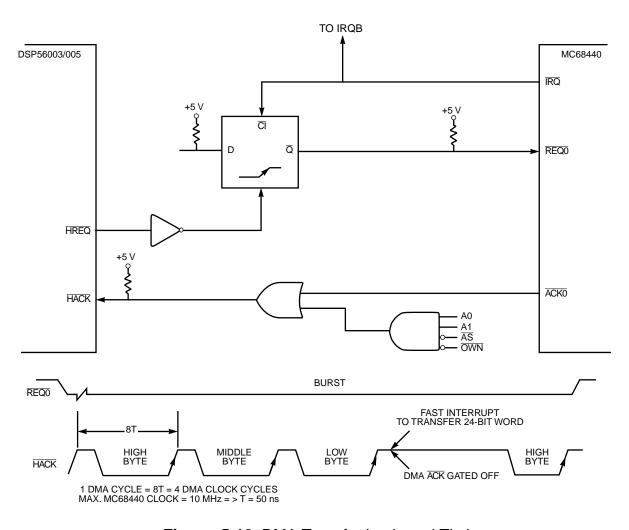

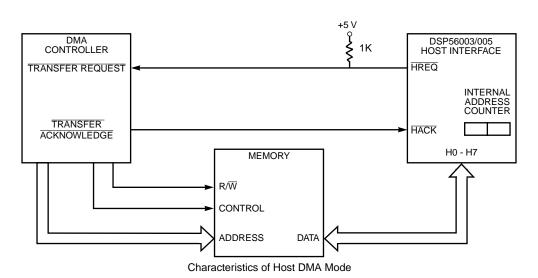

| 5.3.6.3             | DMA Data Transfer                                   | . 5-55         |

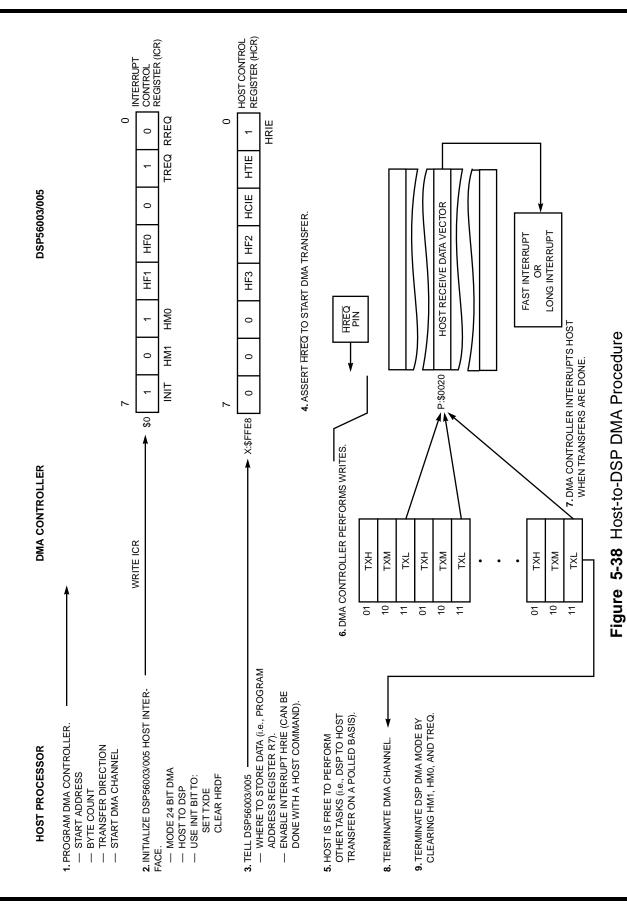

| 5.3.6.3.1           | Host To DSP Internal Processing                     | . 5-56         |

| 5.3.6.3.2           | Host to DSP DMA Procedure                           | . 5-58         |

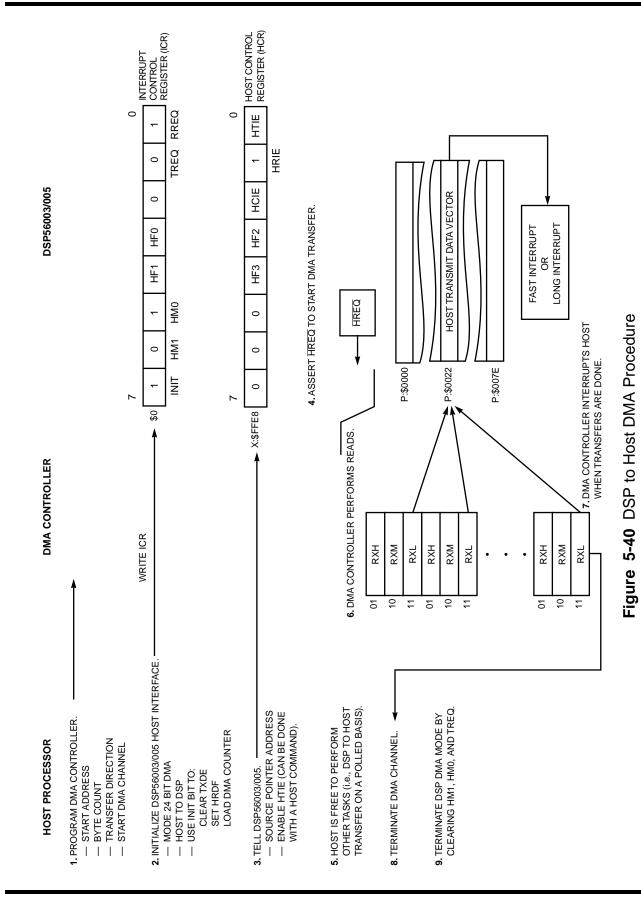

| 5.3.6.3.3           | DSP to Host Internal Processing                     | . 5-59         |

| 5.3.6.3.4           | DSP to Host DMA Procedure                           | . 5-60         |

| 5.3.6.4             | Example Circuits                                    | . 5-62         |

| 5.3.6.5             | Host Port Use Considerations — Host Side            |                |

|                     | SECTION 6 SERIAL COMMUNICATIONS INTERFACE           |                |

| 6.1                 | INTRODUCTION                                        | . 6-3          |

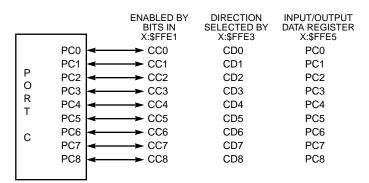

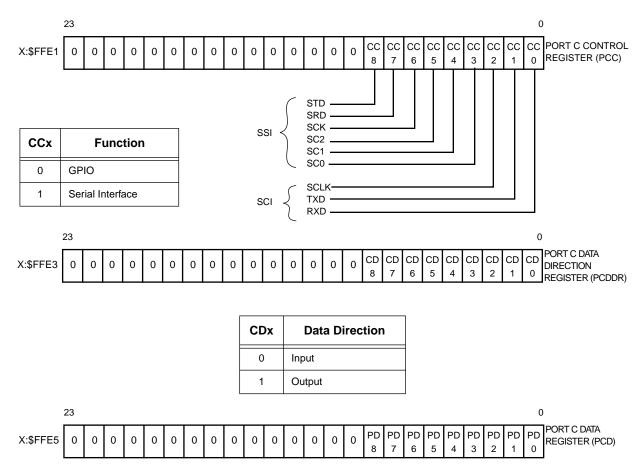

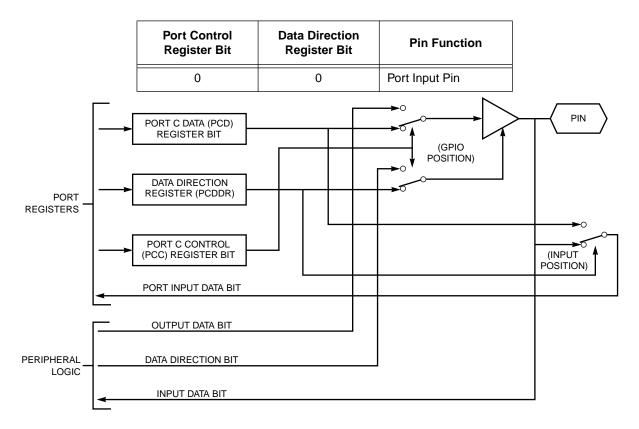

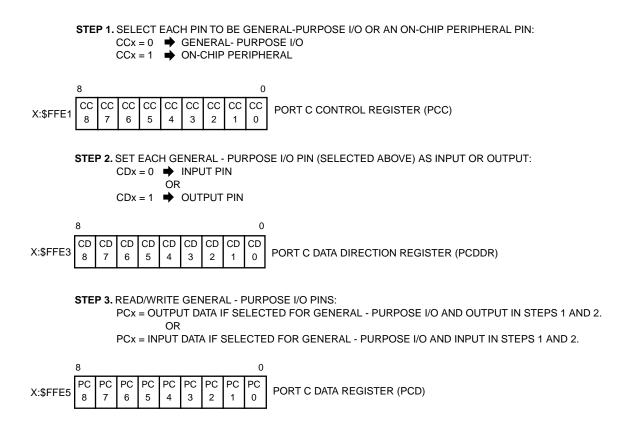

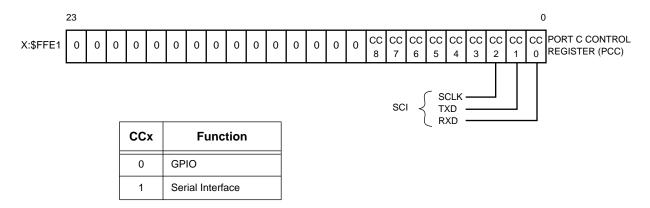

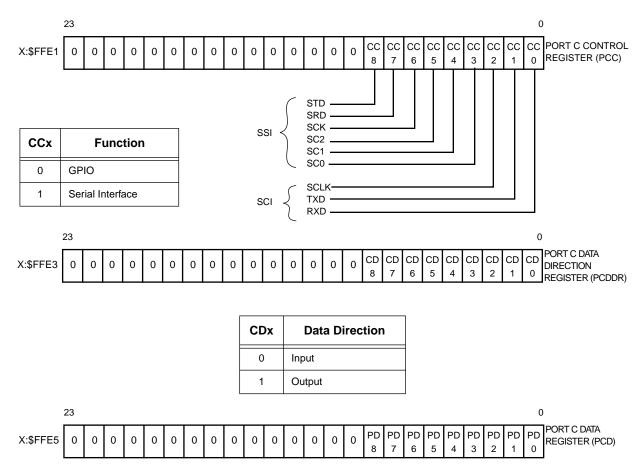

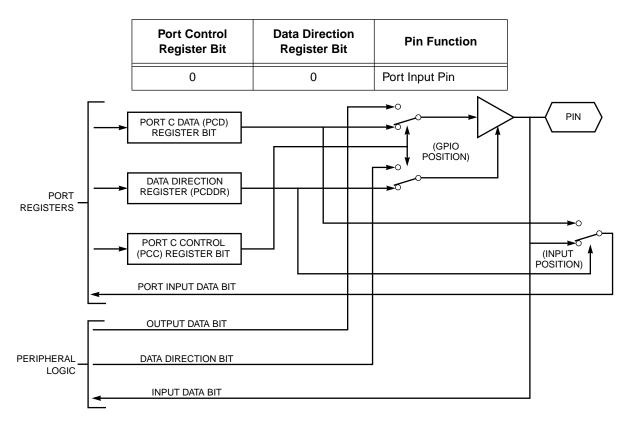

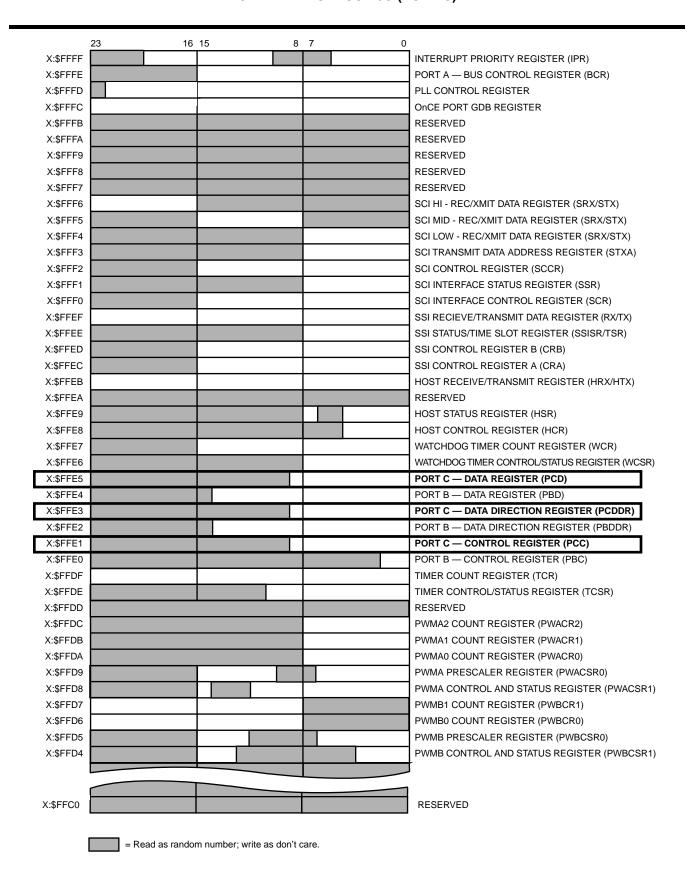

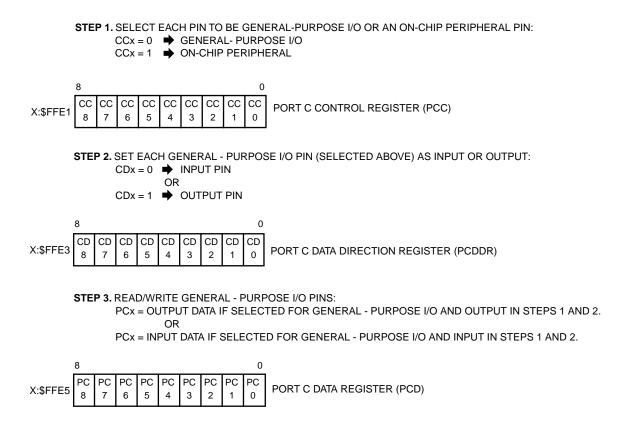

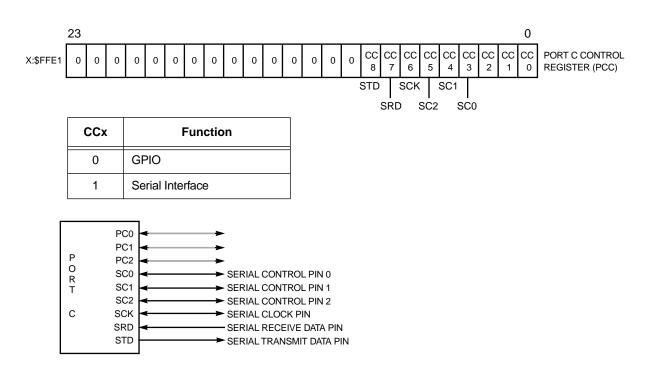

| 6.2                 | GENERAL-PURPOSE I/O (PORT C)                        |                |

| 6.2.1               | Programming General Purpose I/O                     |                |

| 6.2.2               | Port C General Purpose I/O Timing                   |                |

| 6.3                 | SERIAL COMMUNICATION INTERFACE (SCI)                | . 6-10         |

| 6.3.1               | SCI I/O Pins                                        |                |

| 6.3.1.1             | Receive Data (RXD)                                  |                |

| 6.3.1.2             | Transmit Data (TXD)                                 |                |

| 6.3.1.3             | SCI Serial Clock (SĆLK)                             |                |

| 6.3.2               | SCI Programming Model                               |                |

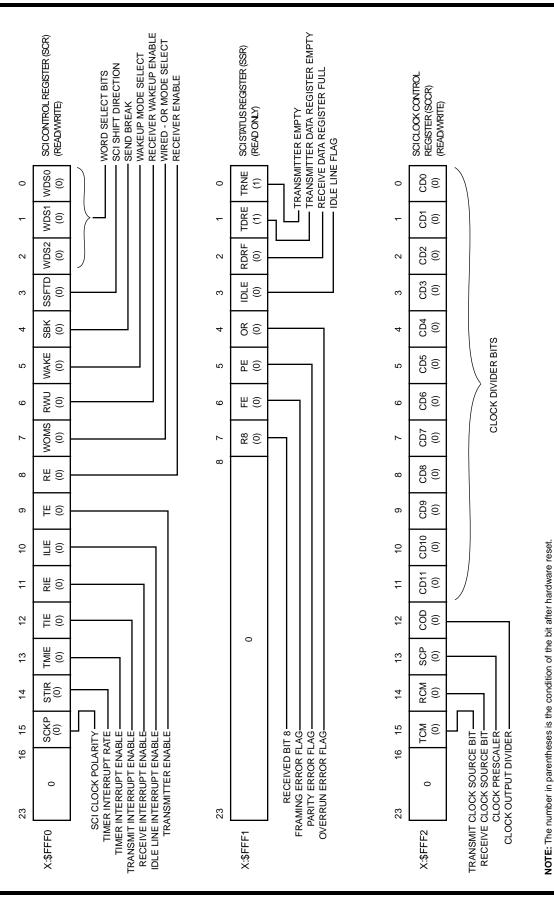

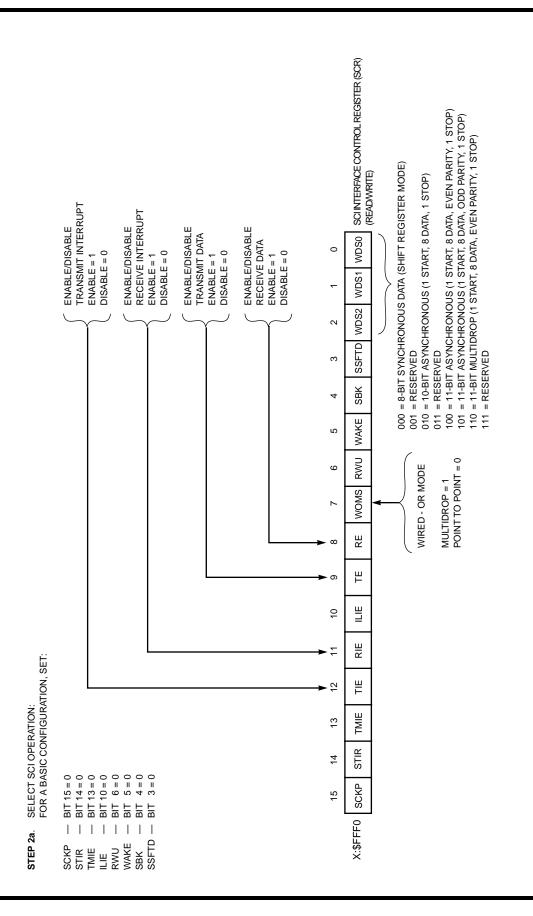

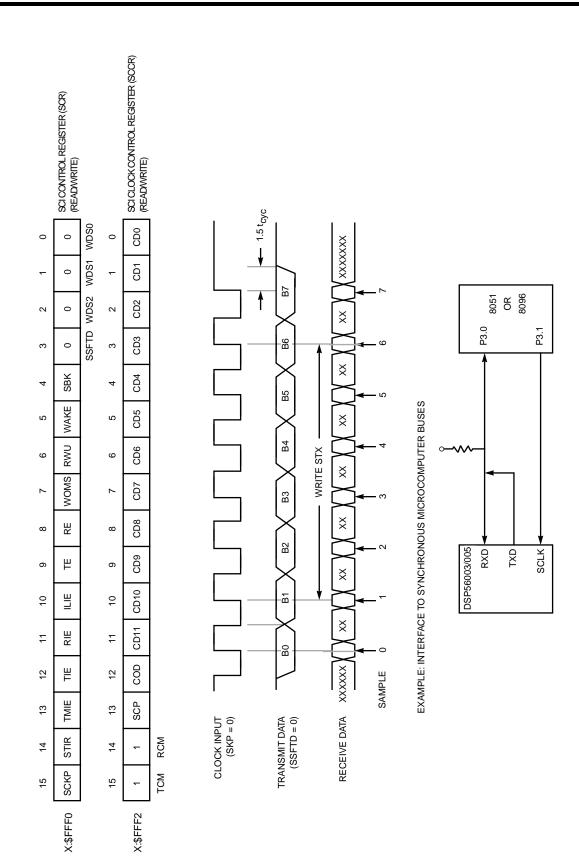

| 6.3.2.1             | SCI Control Register (SCR)                          |                |

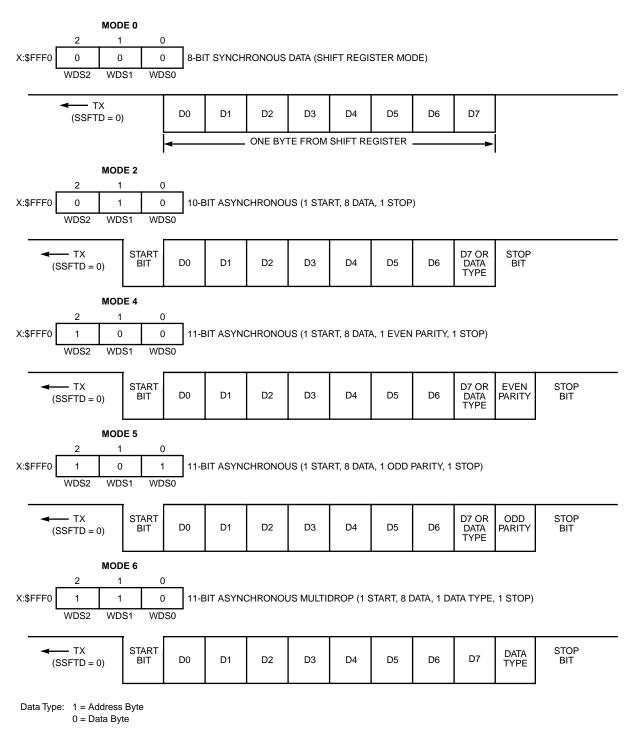

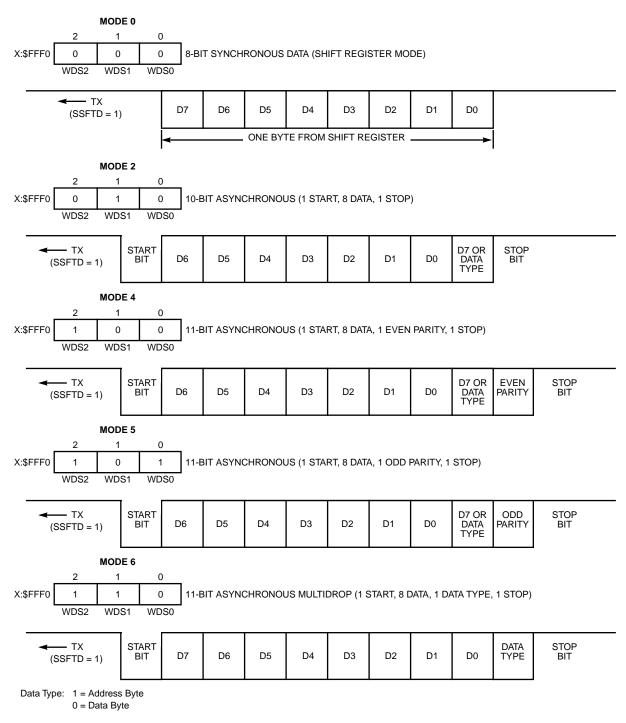

| 6.3.2.1.1           | SCR Word Select (WDS0, WDS1, WDS2) Bits 0, 1, and 2 |                |

| 6.3.2.1.2           | SCR SCI Shift Direction (SSFTD) Bit 3               |                |

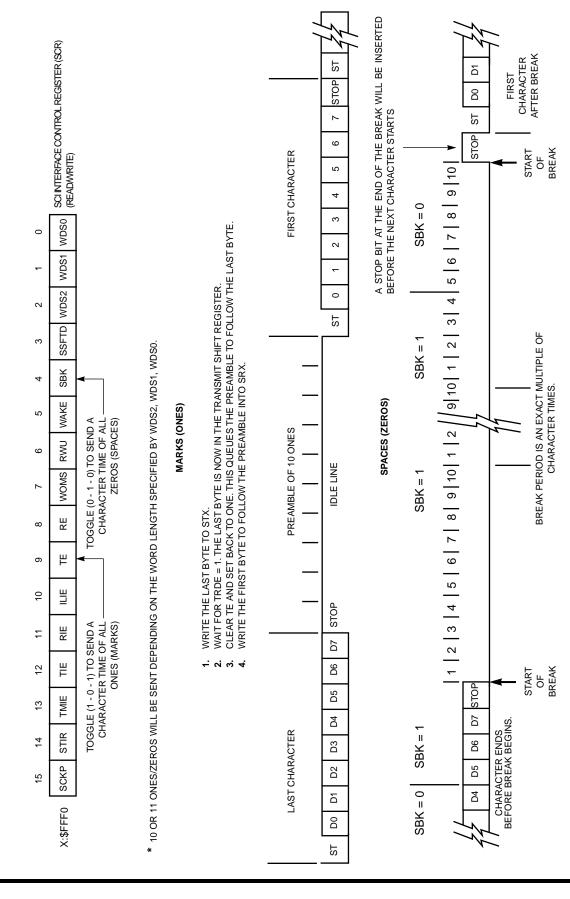

| 6.3.2.1.3           | SCR Send Break (SBK) Bit 4                          |                |

| 6.3.2.1.4           | SCR Wakeup Mode Select (WAKE) Bit 5                 |                |

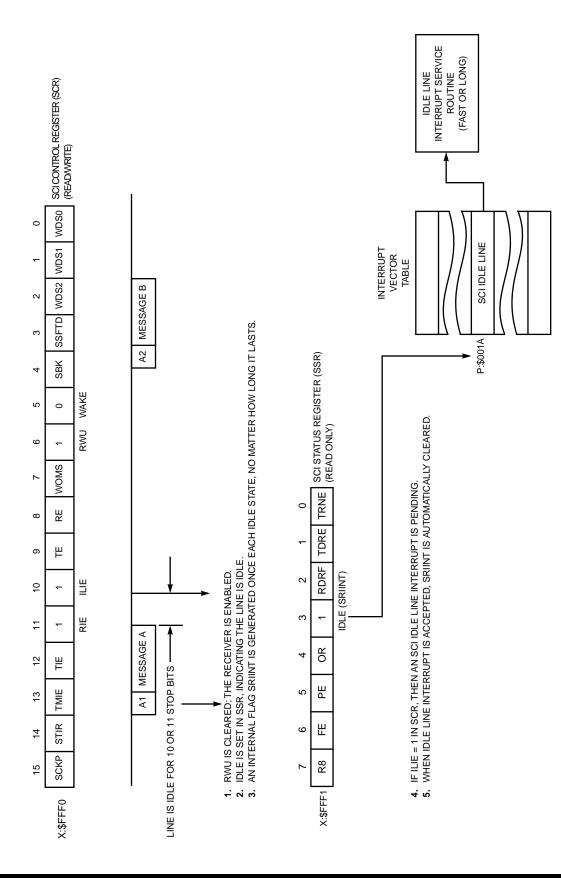

| 6.3.2.1.5           | SCR Receiver Wakeup Enable (RWU) Bit 6              |                |

| 6.3.2.1.6           | SCR Wired-OR Mode Select (WOMS) Bit 7               |                |

| 6.3.2.1.7           | SCR Receiver Enable (RE) Bit 8                      |                |

|                     | ,                                                   |                |

|                     | Table of Contents (Continued)                   |                |

|---------------------|-------------------------------------------------|----------------|

| Paragraph<br>Number | Title                                           | Page<br>Number |

|                     |                                                 |                |

| 6.3.2.1.8           | SCR Transmitter Enable (TE) Bit 9               | 6-18           |

| 6.3.2.1.9           | SCR Idle Line Interrupt Enable (ILIE) Bit 10    |                |

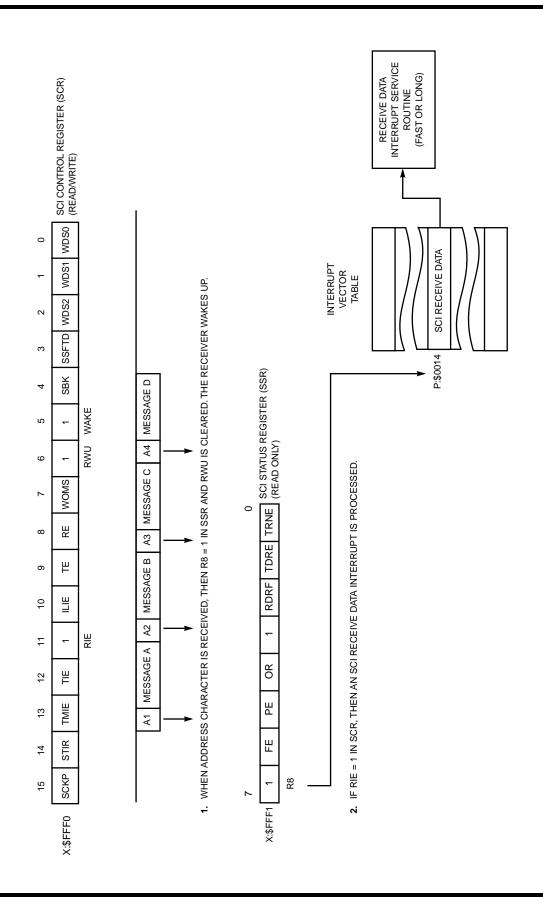

| 6.3.2.1.10          | SCR SCI Receive Interrupt Enable (RIE) Bit 11   |                |

| 6.3.2.1.11          | SCR SCI Transmit Interrupt Enable (TIE) Bit 12  | 6-20           |

| 6.3.2.1.12          | SCR Timer Interrupt Enable (TMIE) Bit 13        | 6-20           |

| 6.3.2.1.13          | SCR SCI Timer Interrupt Rate (STIR) Bit 14      |                |

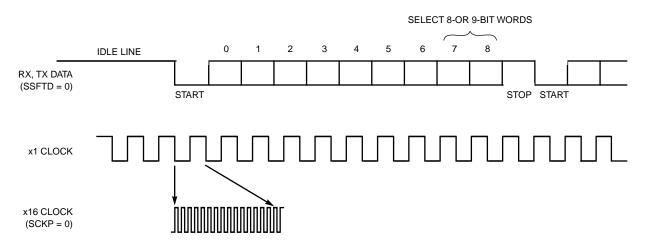

| 6.3.2.1.14          | SCR SCI Clock Polarity (SCKP) Bit 15            |                |

| 6.3.2.2             | SCI Status Register (SSR)                       | 6-20           |

| 6.3.2.2.1           | SSR Transmitter Empty (TRNE) Bit 0              |                |

| 6.3.2.2.2           | SSR Transmit Data Register Empty (TDRE) Bit 1   |                |

| 6.3.2.2.3           | SSR Receive Data Register Full (RDRF) Bit 2     |                |

| 6.3.2.2.4           | SSR Idle Line Flag (IDLE) Bit 3                 |                |

| 6.3.2.2.5           | SSR Overrun Error Flag (OR) Bit 4               |                |

| 6.3.2.2.6           | SSR Parity Error (PE) Bit 5                     | 6-22           |

| 6.3.2.2.7           | SSR Framing Error Flag (FE) Bit 6               |                |

| 6.3.2.2.8           | SSR Received Bit 8 Address (R8) Bit 7           |                |

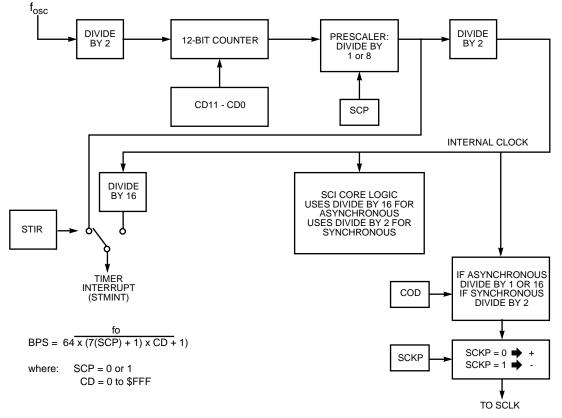

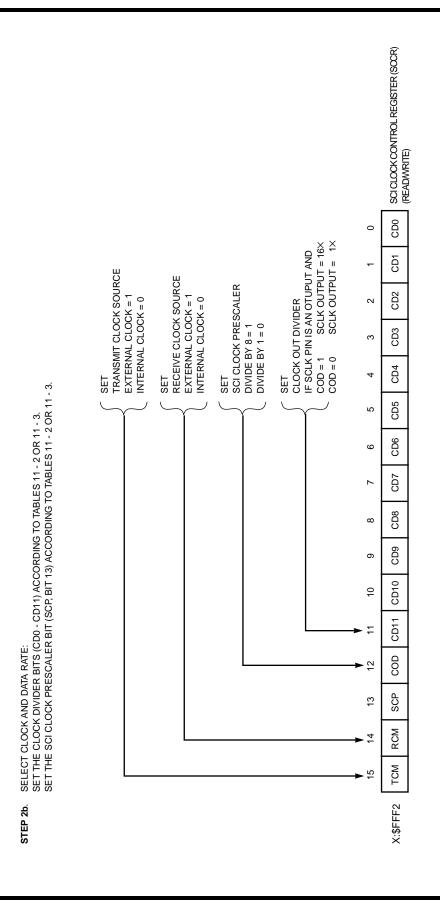

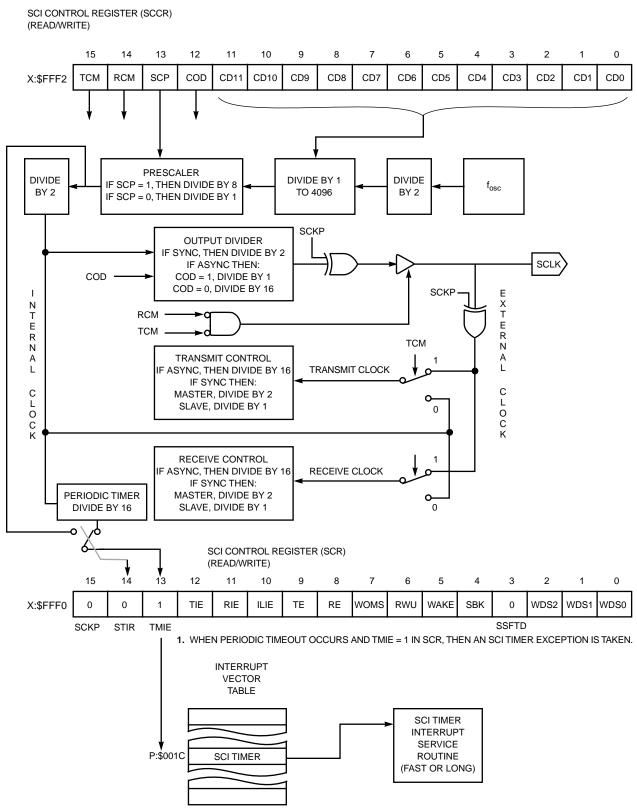

| 6.3.2.3             | SCI Clock Control Register (SCCR)               |                |

| 6.3.2.3.1           | SCCR Clock Divider (CD11–CD0) Bits 11–0         |                |

| 6.3.2.3.2           | SCCR Clock Out Divider (COD) Bit 12             | 6-24           |

| 6.3.2.3.3           | SCCR SCI Clock Prescaler (SCP) Bit 13           | 6-24           |

| 6.3.2.3.4           | SCCR Receive Clock Mode Source (RCM) Bit 14     | 6-25           |

| 6.3.2.3.5           | SCCR Transmit Clock Source (TCM) Bit 15         | 6-25           |

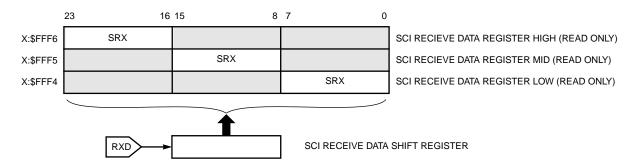

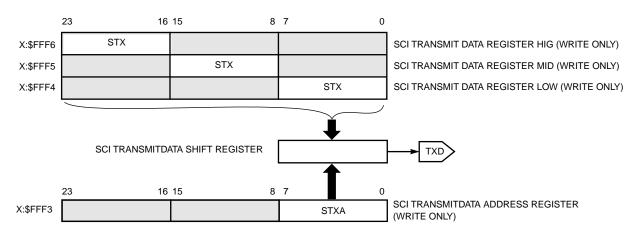

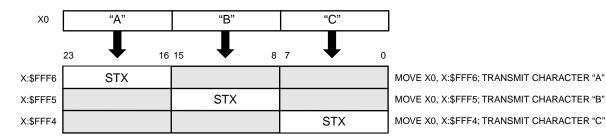

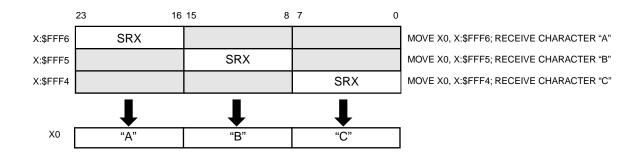

| 6.3.2.4             | SCI Data Registers                              | 6-26           |

| 6.3.2.4.1           | SCI Receive Register                            | 6-26           |

| 6.3.2.4.2           | SCI Transmit Registers                          |                |

| 6.3.2.5             | Preamble, Break, and Data Transmission Priority | 6-29           |

| 6.3.3               | Register Contents After Reset                   |                |

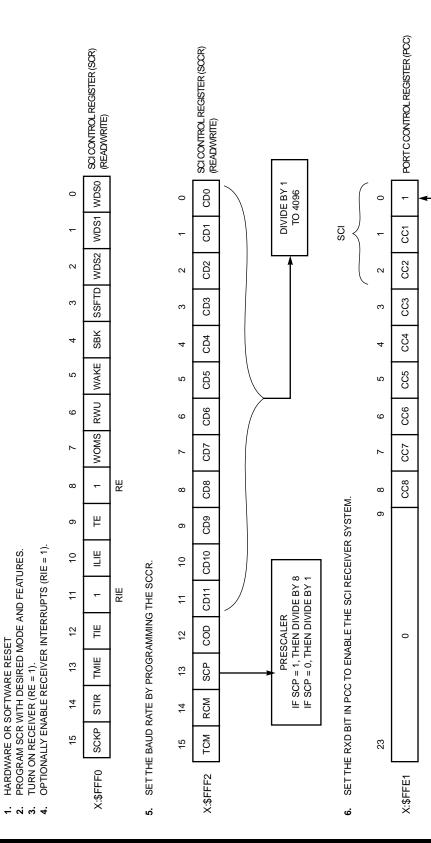

| 6.3.4               | SCI Initialization                              | 6-29           |

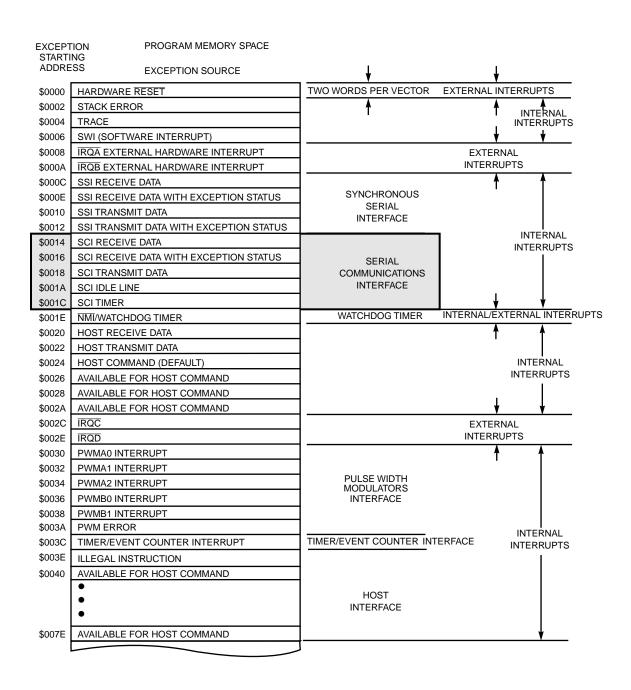

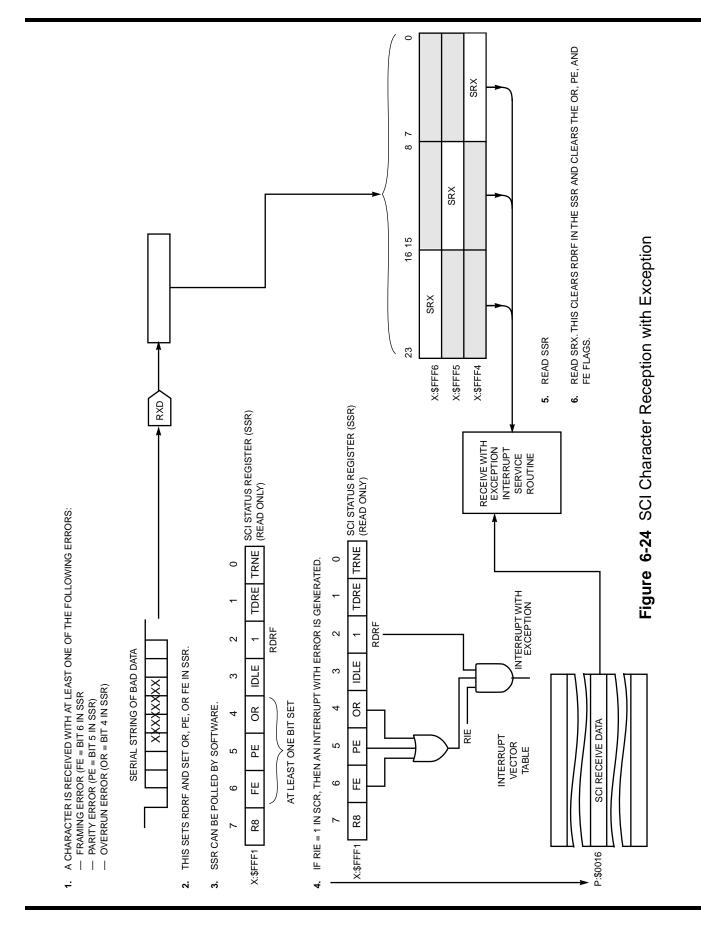

| 6.3.5               | SCI Exceptions                                  | 6-36           |

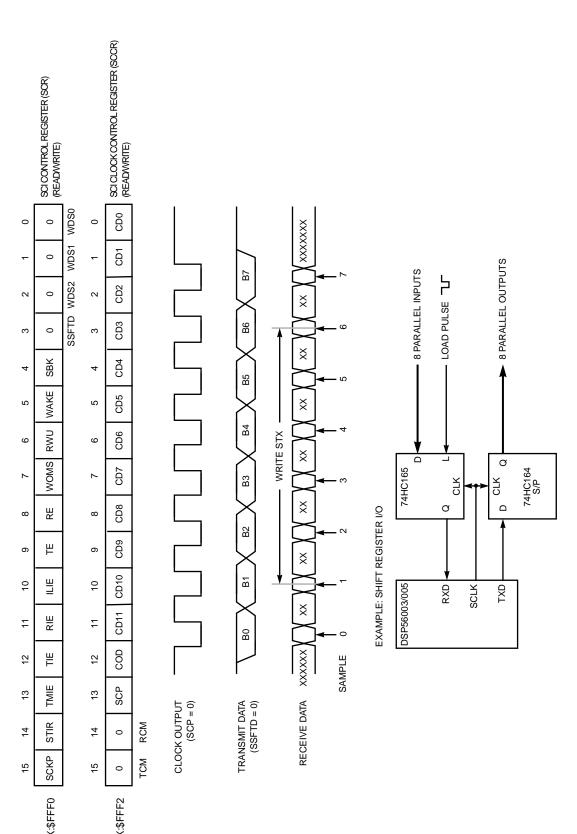

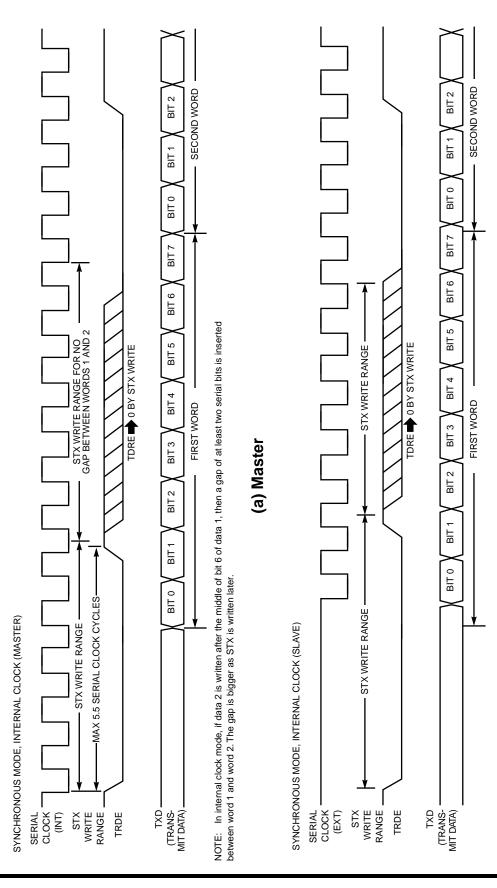

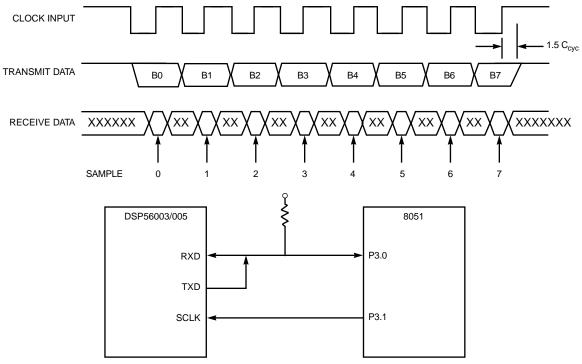

| 6.3.6               | Synchronous Data Mode                           | 6-36           |

| 6.3.7               | Asynchronous Data                               | 6-43           |

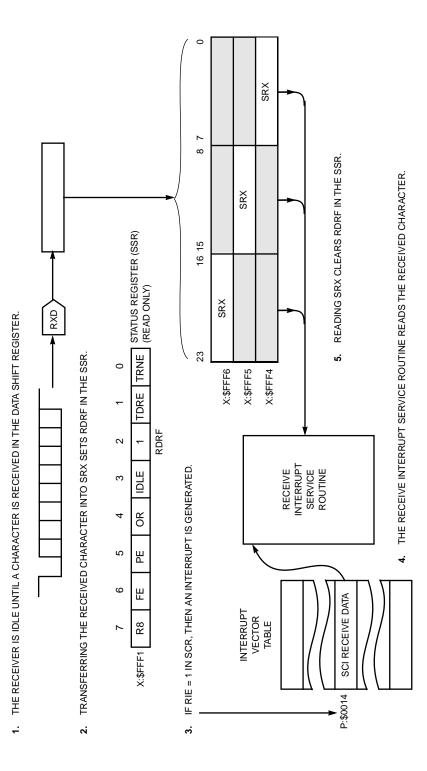

| 6.3.7.1             | Asynchronous Data Reception                     | 6-44           |

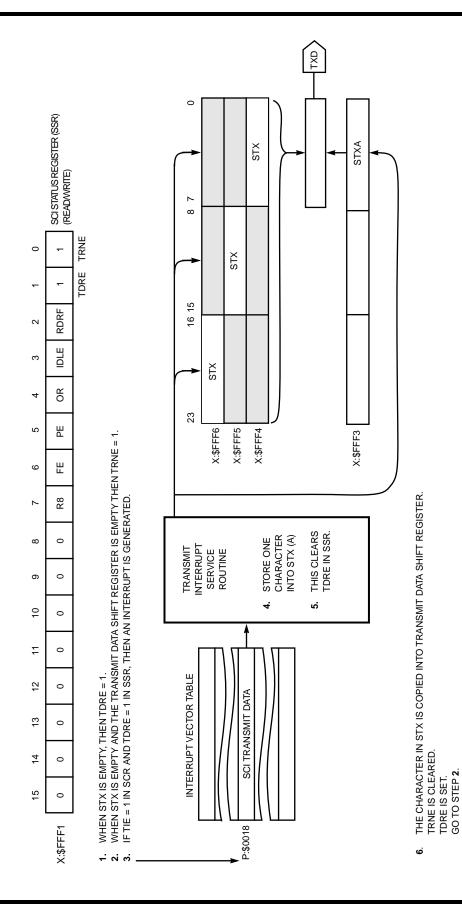

| 6.3.7.2             | Asynchronous Data Transmission                  |                |

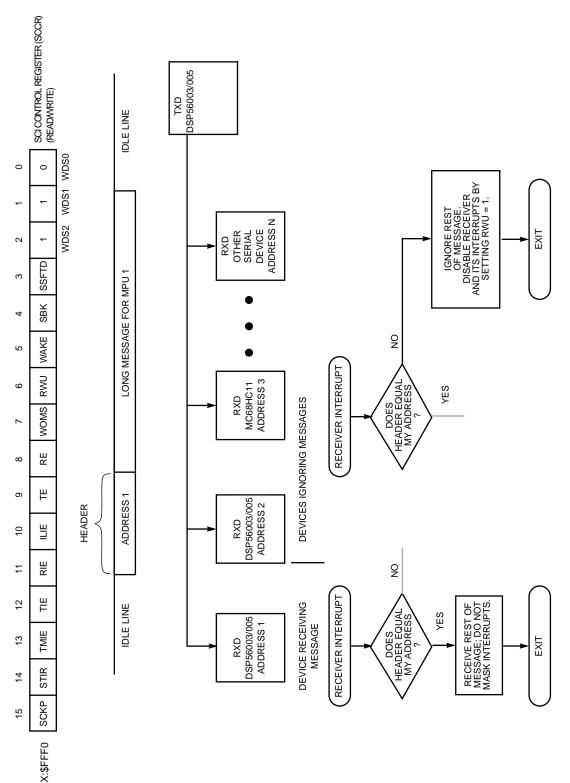

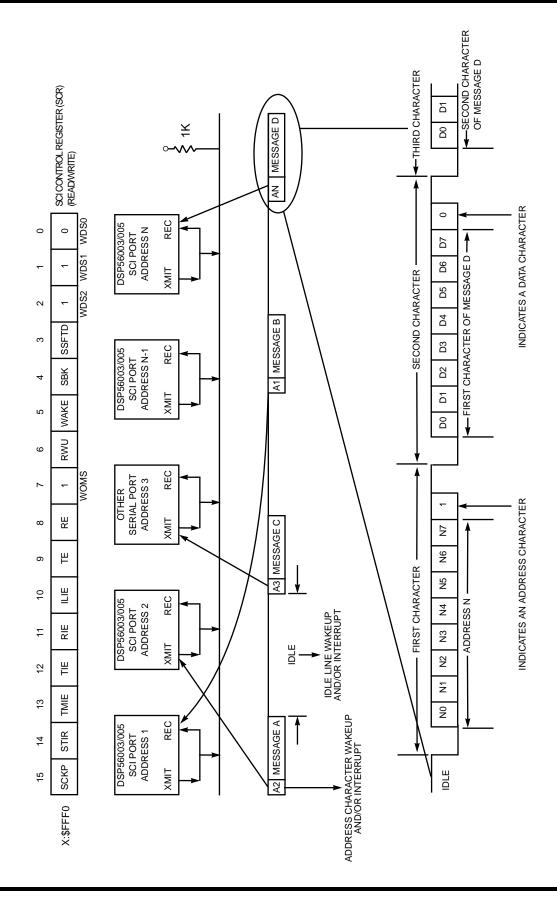

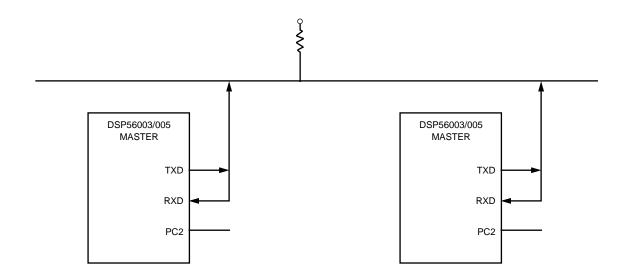

| 6.3.8               | Multidrop                                       | 6-53           |

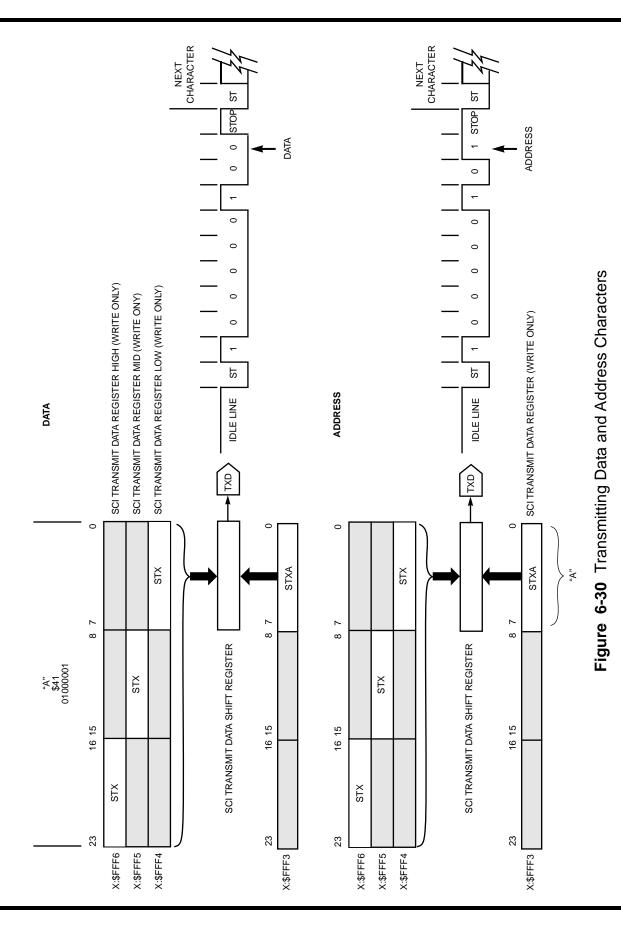

| 6.3.8.1             | Transmitting Data and Address Characters        |                |

| 6.3.8.2             | Wired-OR Mode                                   |                |

| 6.3.8.3             | Idle Line Wakeup                                |                |

| 6.3.8.4             | Address Mode Wakeup                             |                |

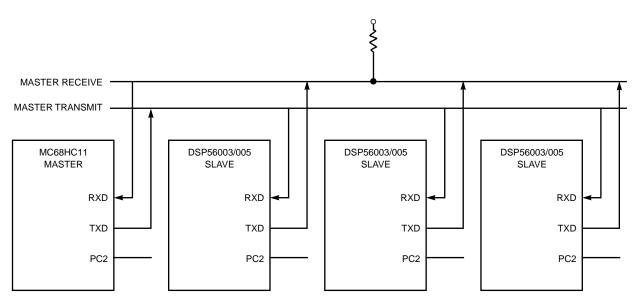

| 6.3.8.5             | Multidrop Example                               |                |

|                     |                                                 |                |

|                                                                              | Table of Contents (Continued)                                                                                                                                                                                                                   |                                              |

|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Paragraph<br>Number                                                          | n<br>Title                                                                                                                                                                                                                                      | Page<br>Number                               |

| 6.3.9<br>6.3.10<br>6.3.11                                                    | SCI Timer                                                                                                                                                                                                                                       | 6-69                                         |

|                                                                              | SECTION 7 SYNCHRONOUS SERIAL INTERFACE                                                                                                                                                                                                          |                                              |

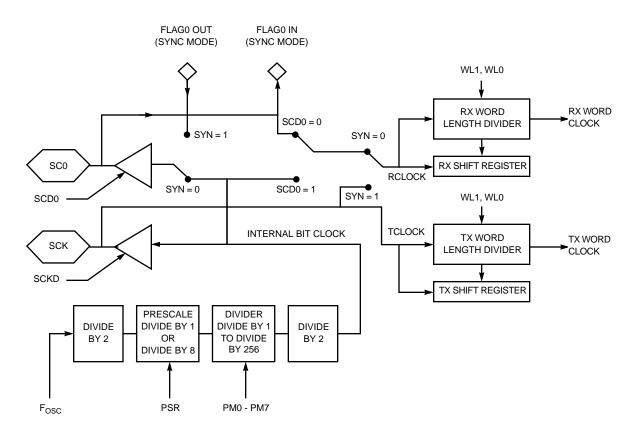

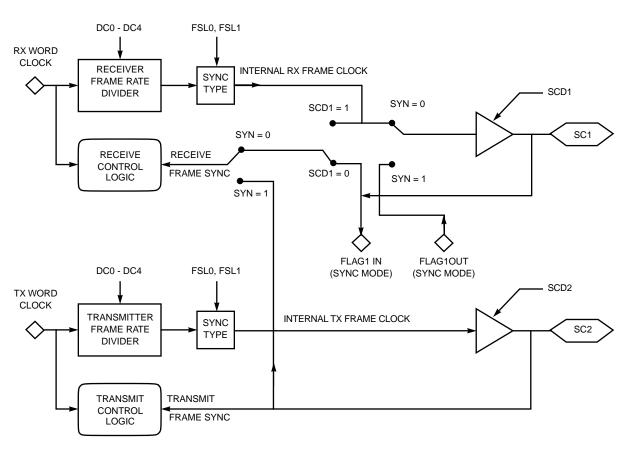

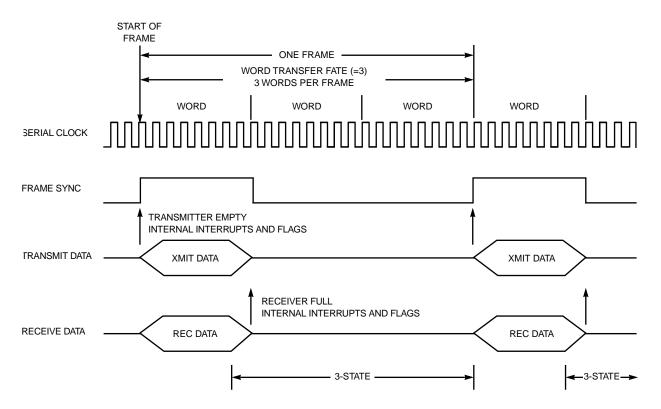

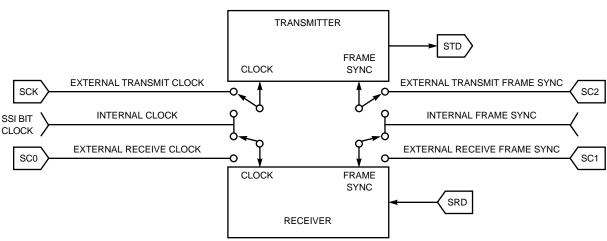

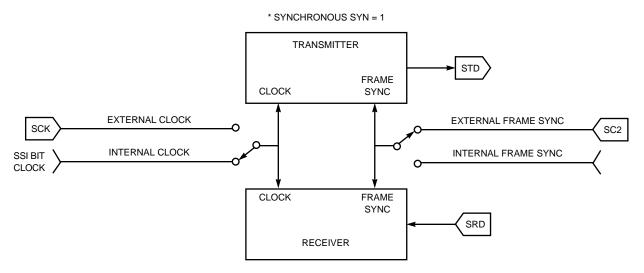

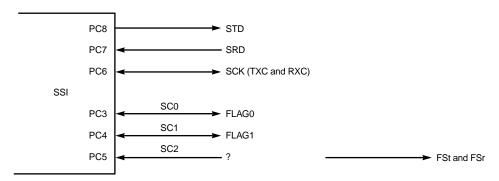

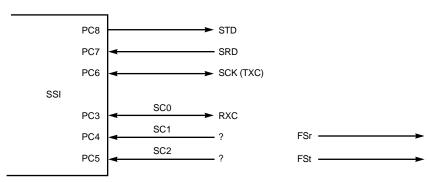

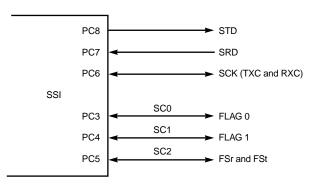

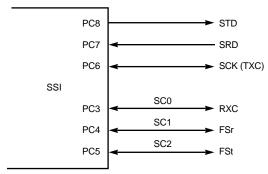

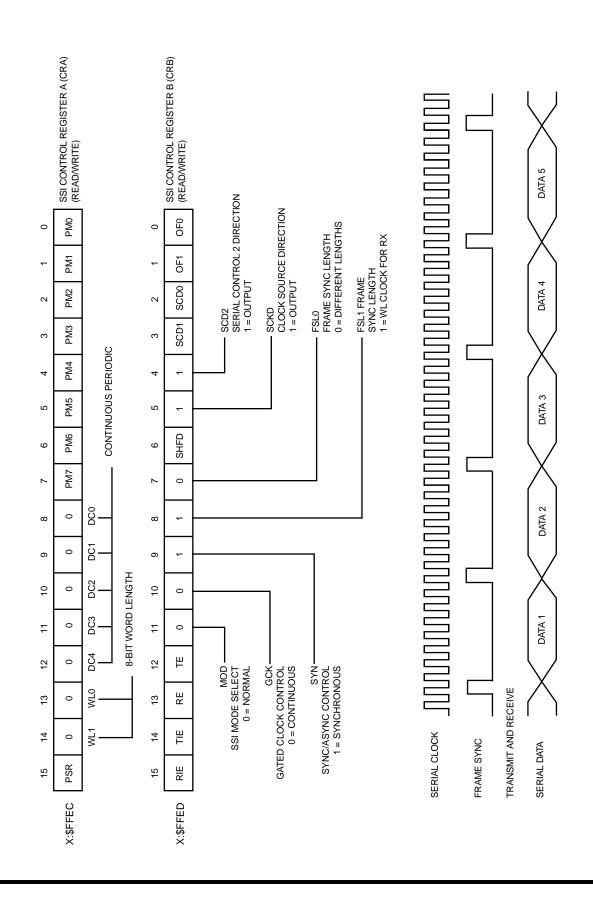

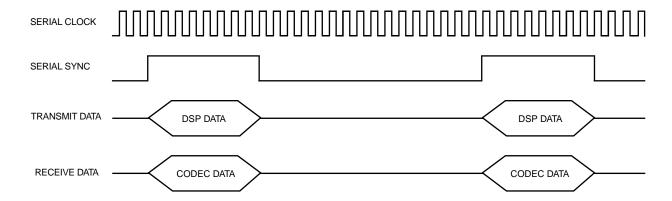

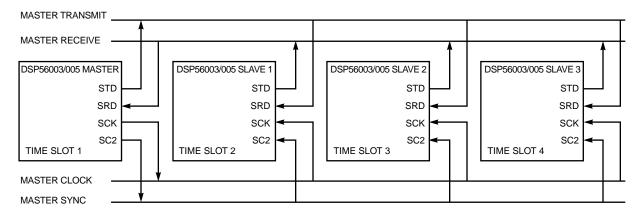

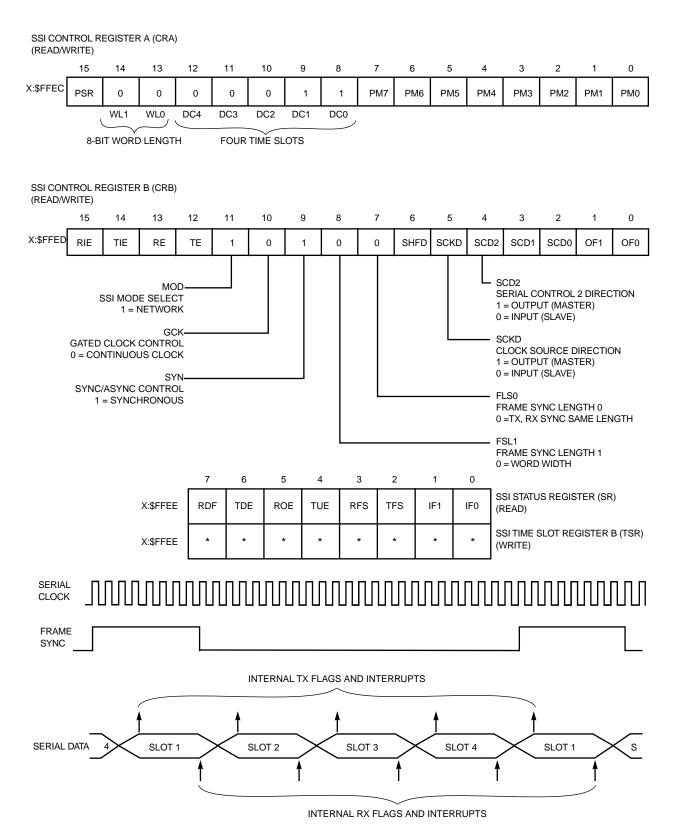

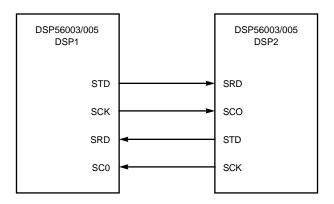

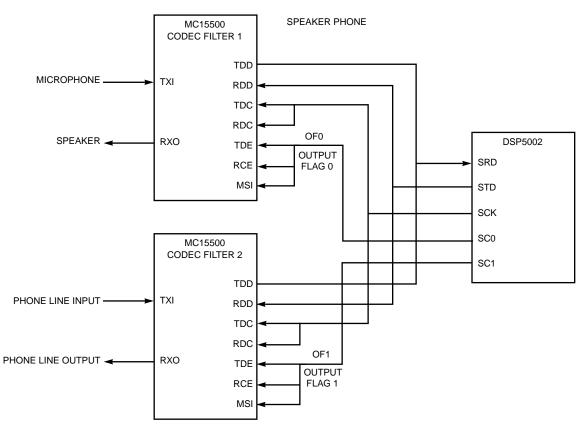

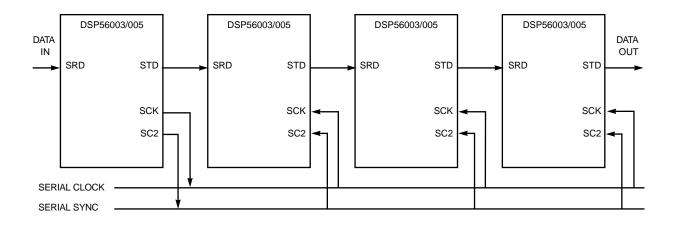

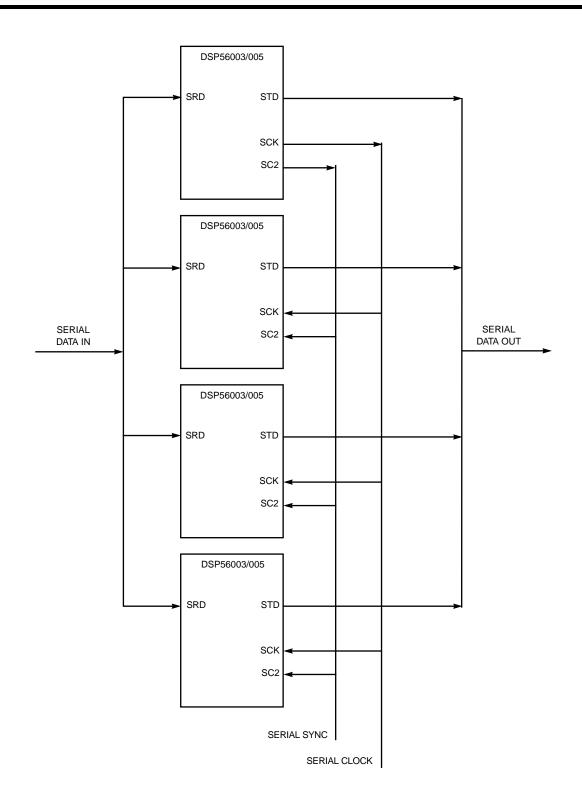

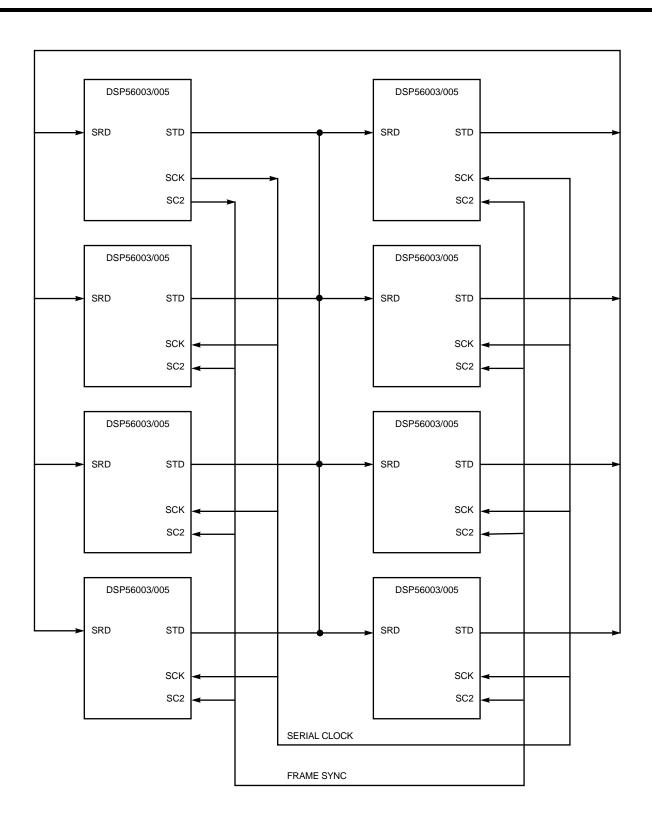

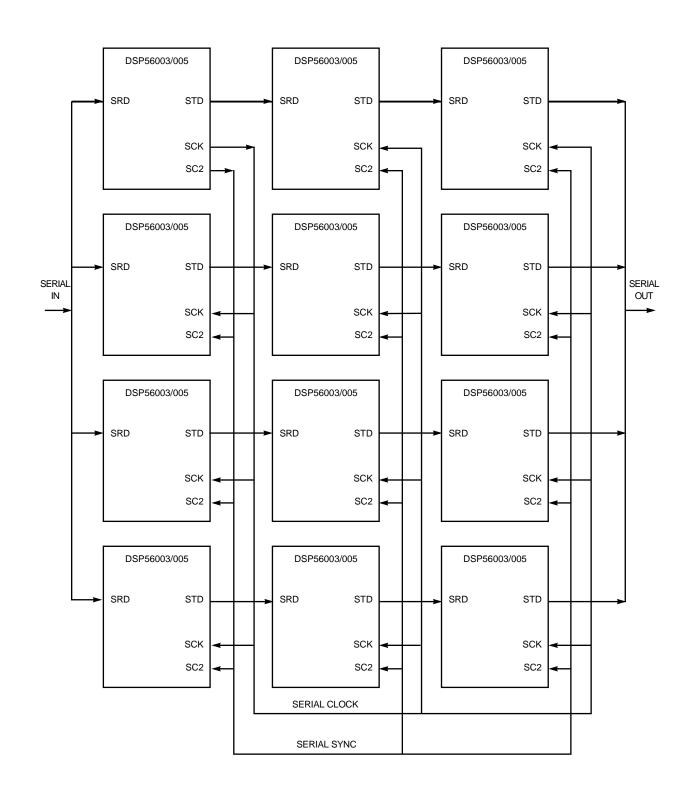

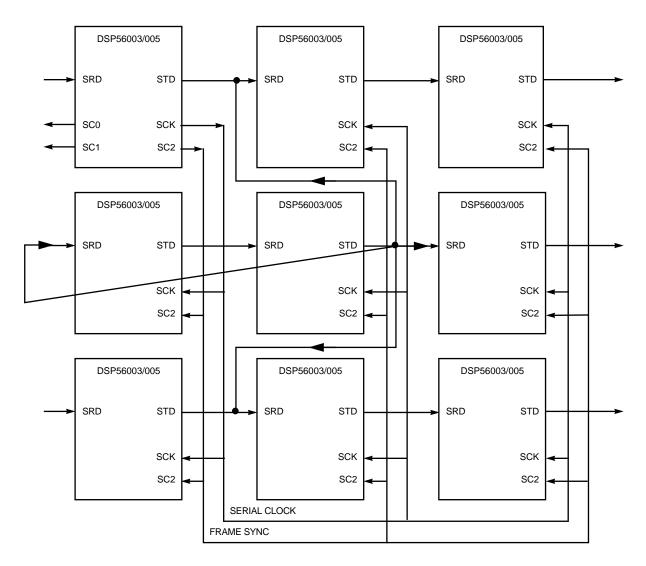

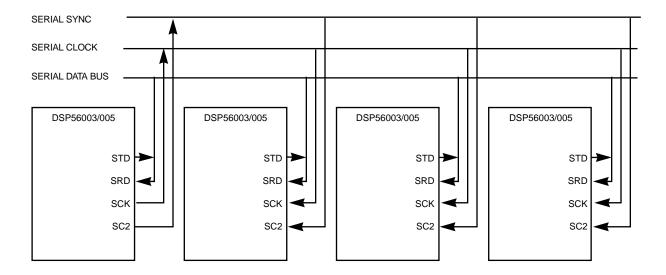

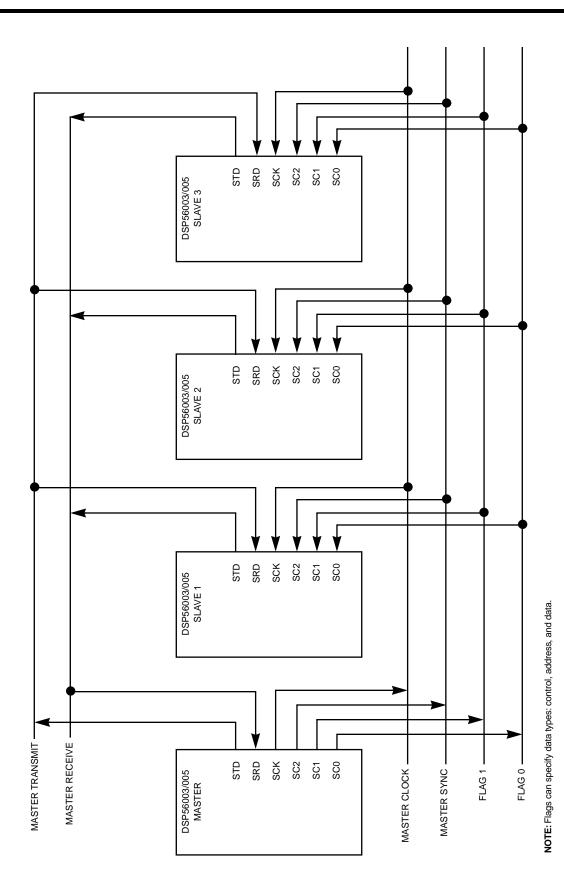

| 7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.3<br>7.3.1<br>7.3.1.1<br>7.3.1.2           | INTRODUCTION.  GENERAL-PURPOSE I/O (PORT C)  Programming General Purpose I/O  Port C General Purpose I/O Timing.  SYNCHRONOUS SERIAL INTERFACE (SSI)  SSI Data and Control Pins.  Serial Transmit Data Pin (STD)  Serial Receive Data Pin (SRD) | 7-4<br>7-5<br>7-8<br>7-10<br>7-12<br>. 7-13  |

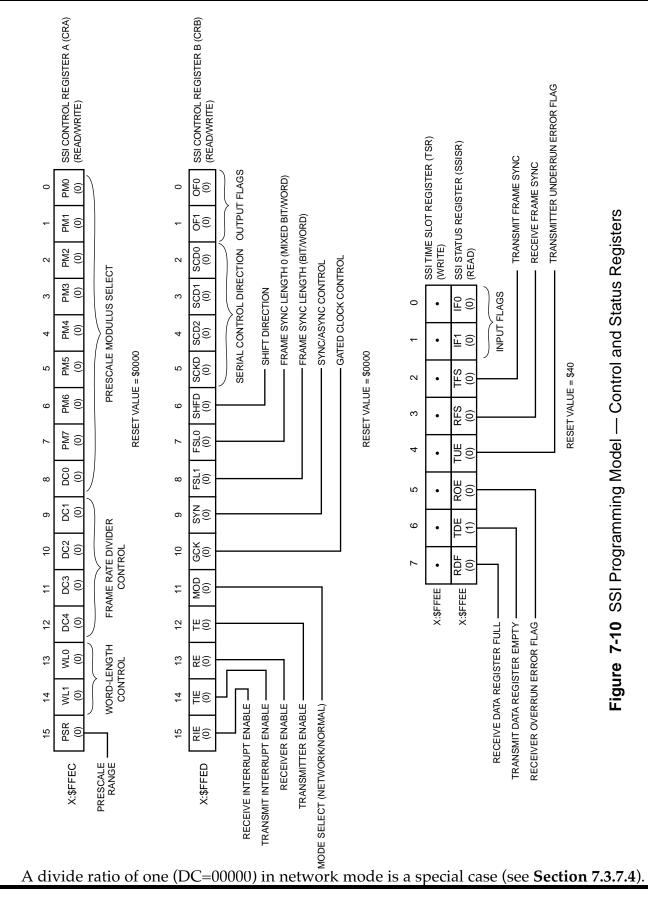

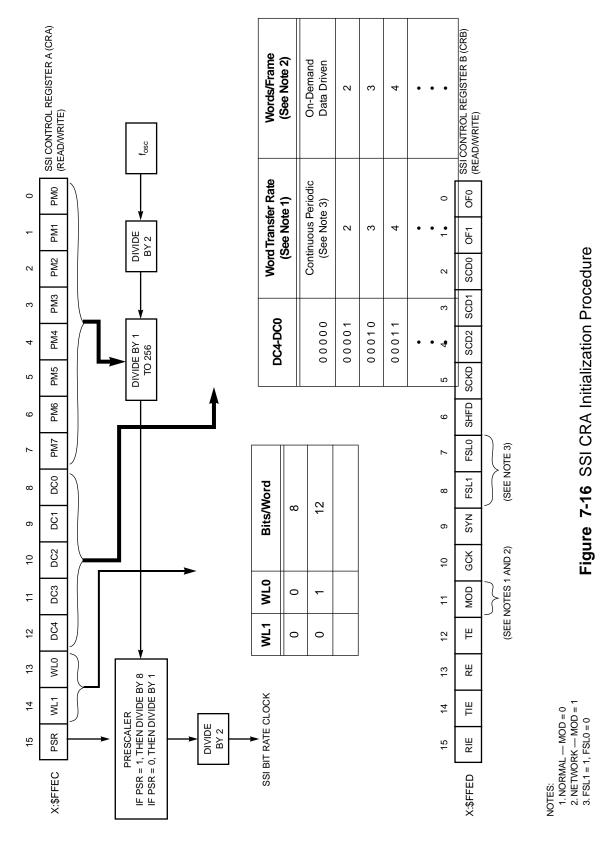

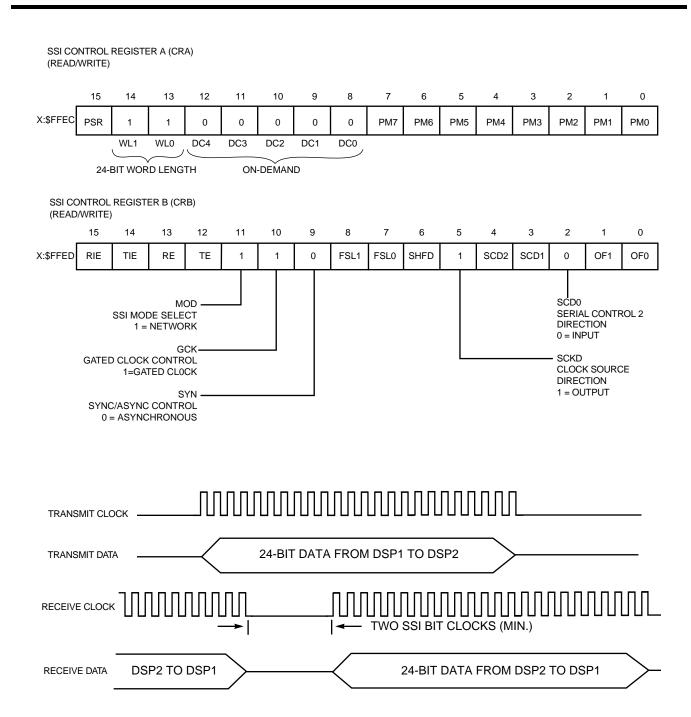

| 7.3.1.3<br>7.3.1.4<br>7.3.1.5<br>7.3.1.6<br>7.3.2<br>7.3.2.1                 | Serial Clock (SCK) Serial Control Pin (SC0) Serial Control Pin (SC1) Serial Control Pin (SC2) SSI Programming Model SSI Control Register A (CRA)                                                                                                | . 7-15<br>. 7-16<br>. 7-16<br>7-17<br>. 7-17 |

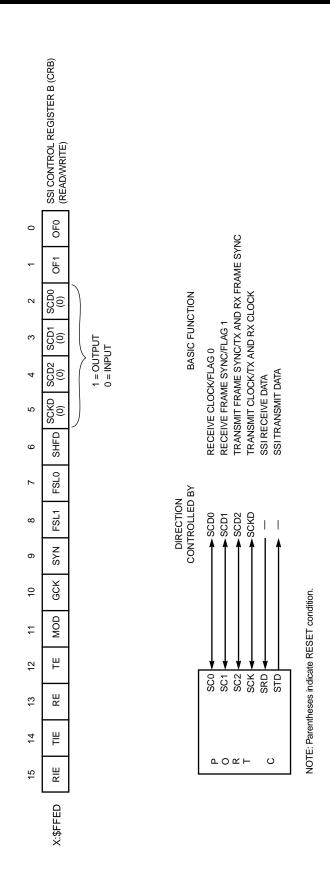

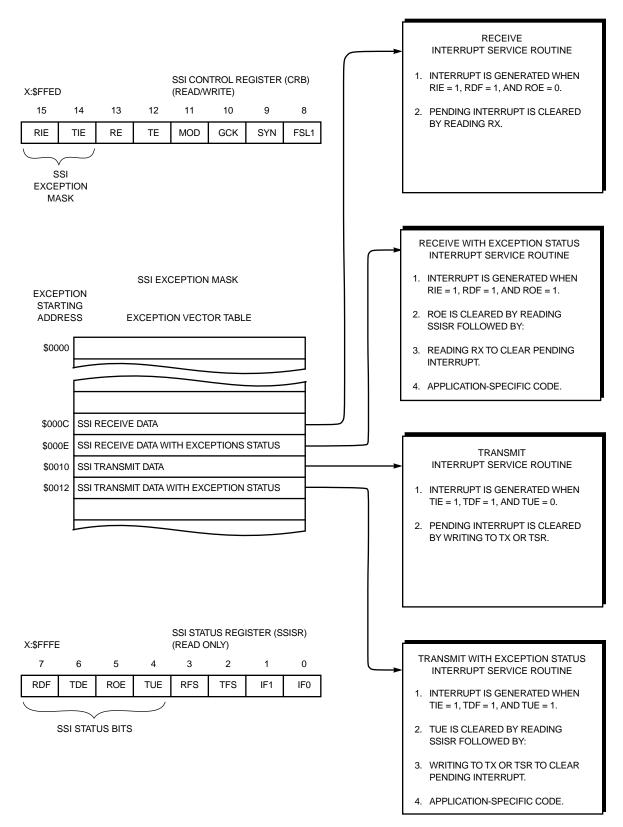

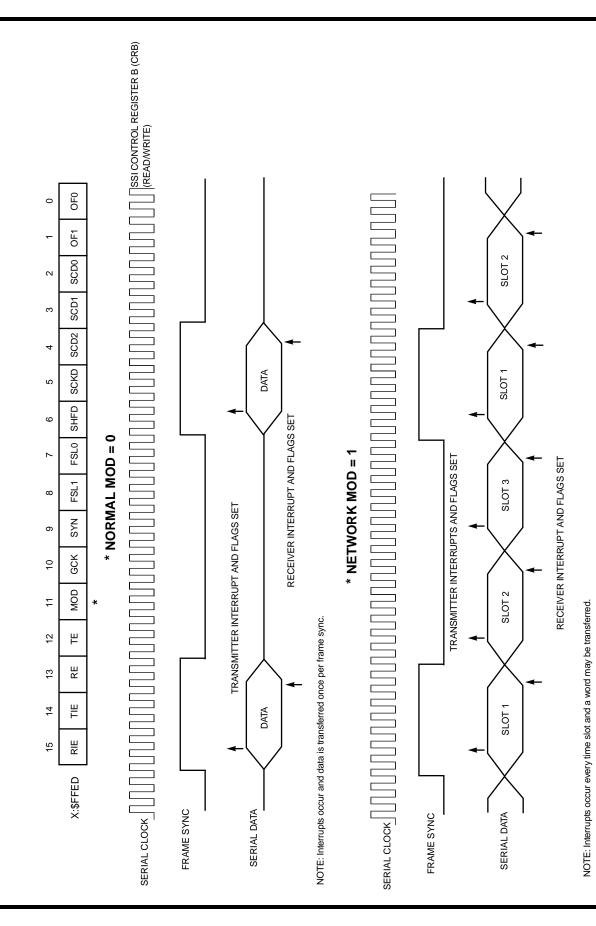

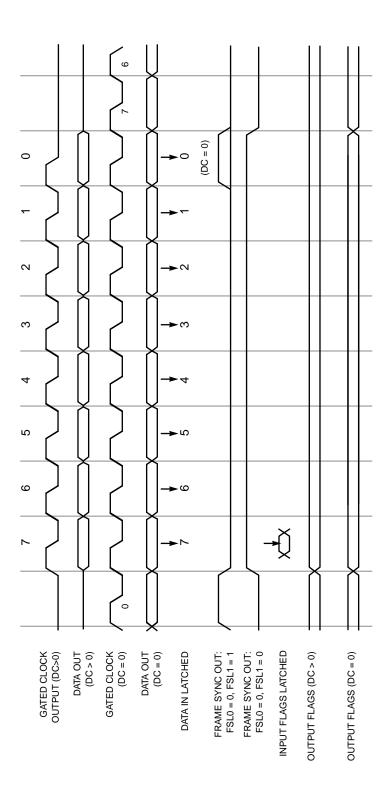

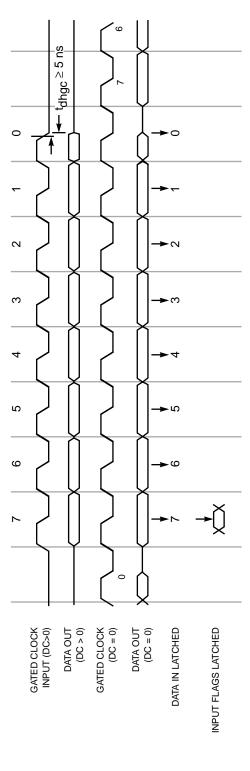

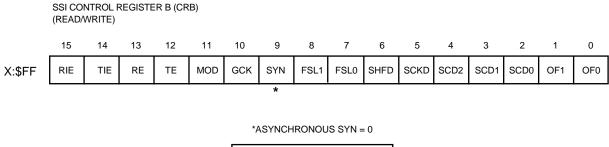

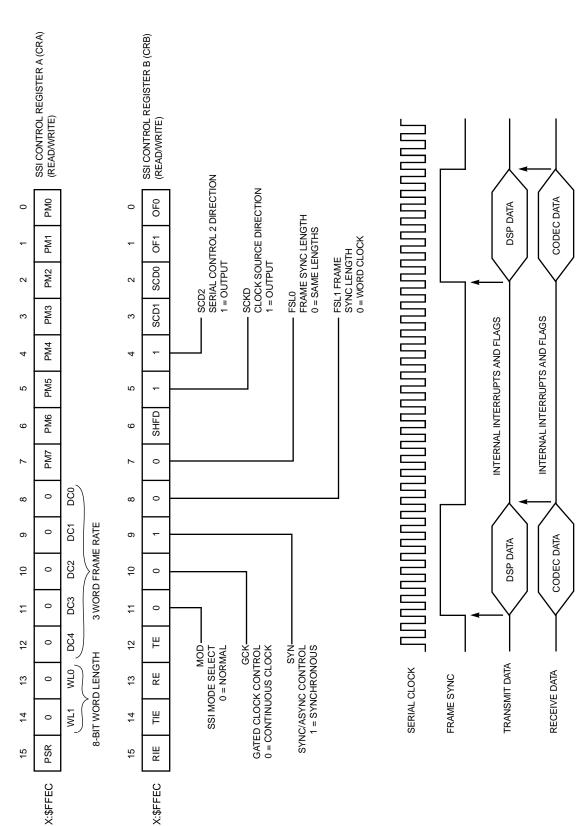

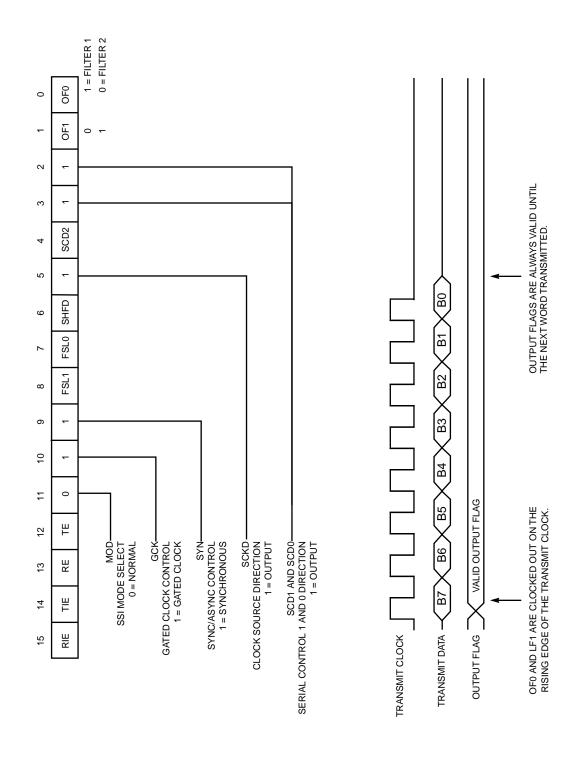

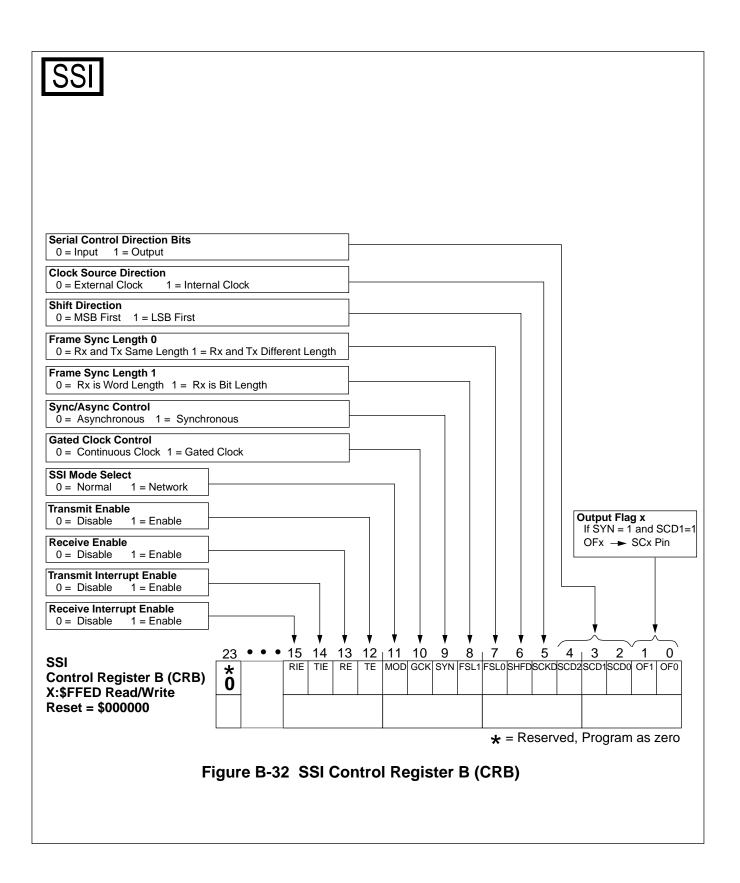

| 7.3.2.1.1<br>7.3.2.1.2<br>7.3.2.1.3<br>7.3.2.1.4<br>7.3.2.2                  | CRA Prescale Modulus Select (PM7–PM0) Bits 0–7                                                                                                                                                                                                  | . 7-17<br>. 7-21<br>. 7-21<br>. 7-21         |

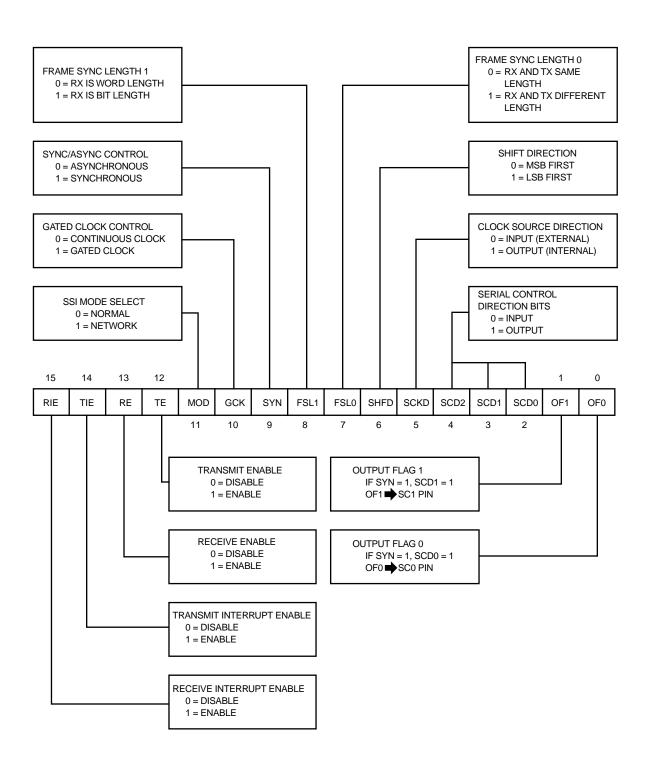

| 7.3.2.2.1<br>7.3.2.2.2<br>7.3.2.2.3<br>7.3.2.2.4<br>7.3.2.2.5                | CRB Serial Output Flag 0 (OF0) Bit 0                                                                                                                                                                                                            | . 7-22<br>. 7-22<br>. 7-22<br>. 7-22         |

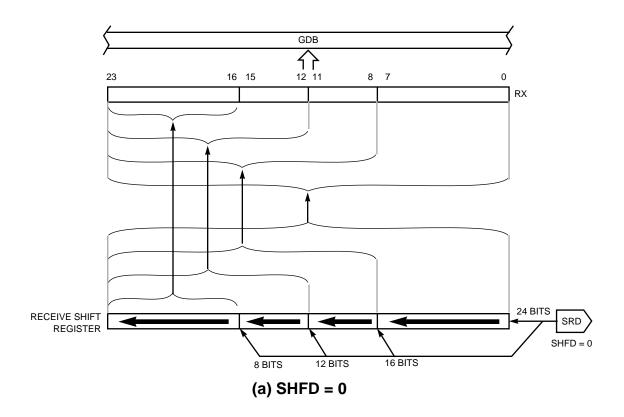

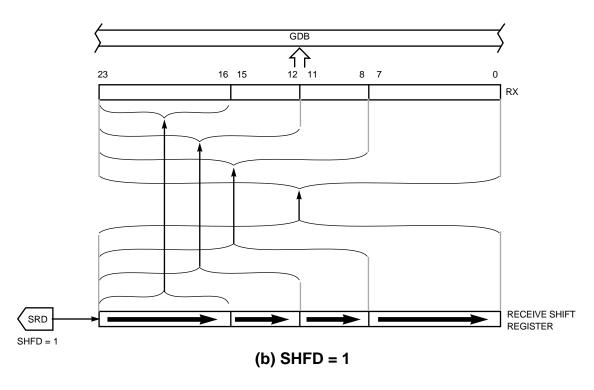

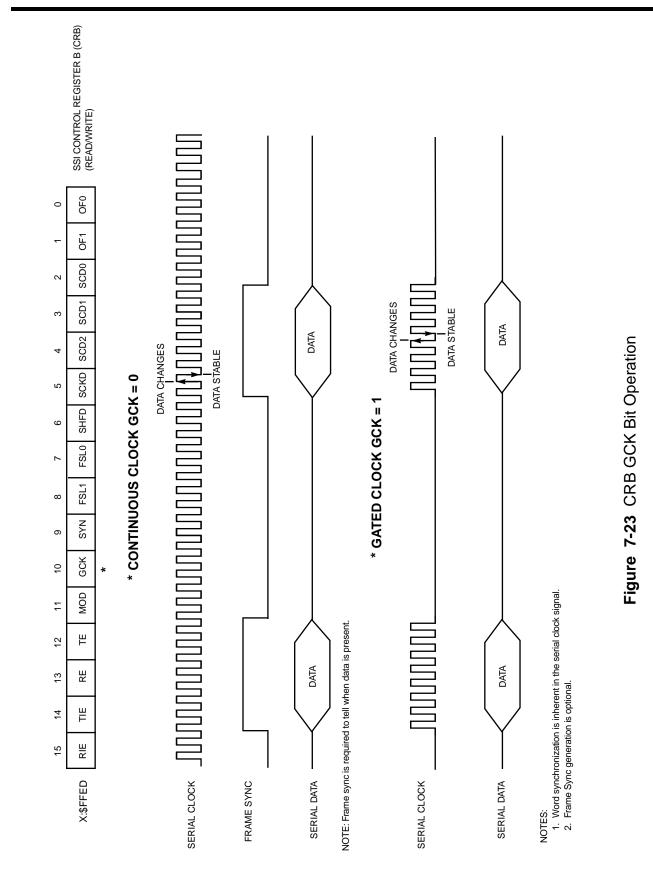

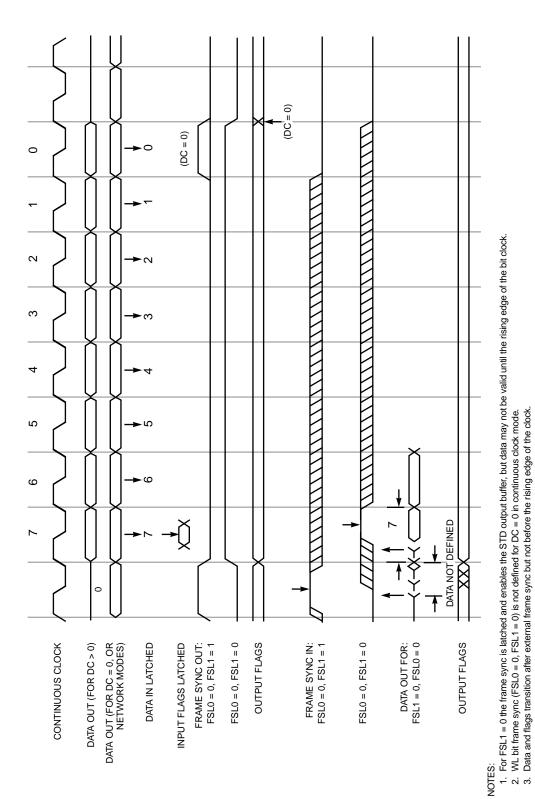

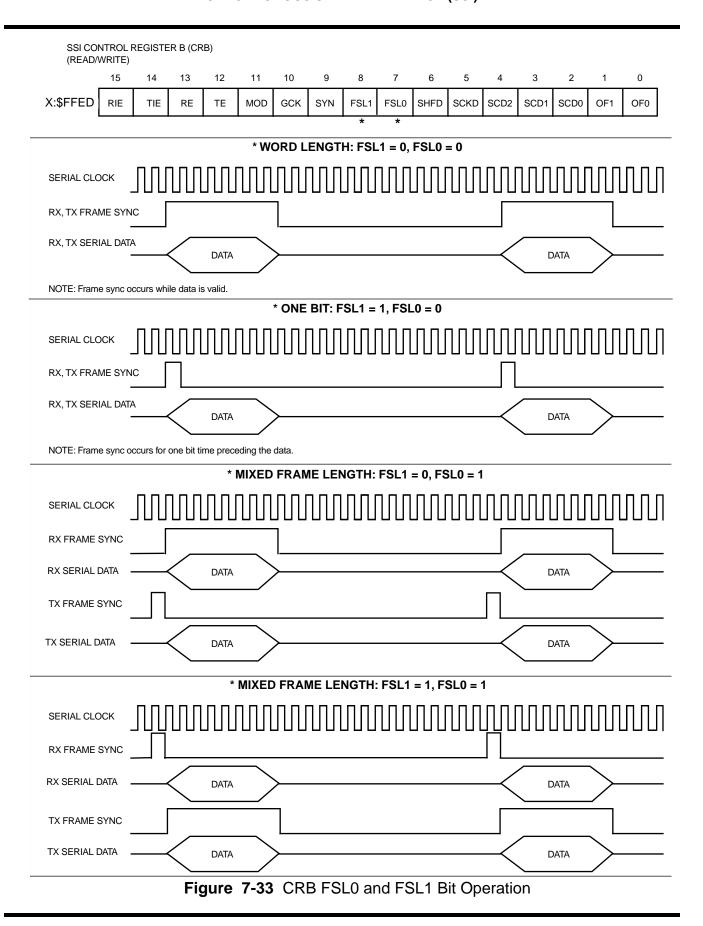

| 7.3.2.2.6<br>7.3.2.2.7<br>7.3.2.2.8<br>7.3.2.2.9<br>7.3.2.2.10<br>7.3.2.2.11 | CRB Clock Source Direction (SCKD) Bit 5  CRB Shift Direction (SHFD) Bit 6  CRB Frame Sync Length (FSL0 and FSL1) Bits 7 and 8  CRB Sync/Async (SYN) Bit 9  CRB Gated Clock Control (GCK) Bit 10  CRB SSI Mode Select (MOD) Bit 11               | . 7-24<br>. 7-24<br>. 7-24<br>. 7-25         |

| 7.3.2.2.12                                                                   | CRB SSI Transmit Enable (TE) Bit 12                                                                                                                                                                                                             |                                              |

|                     | Table of Contents (Continued)                      |                |

|---------------------|----------------------------------------------------|----------------|

| Paragraph<br>Number | Title                                              | Page<br>Number |

|                     |                                                    |                |

| 7.3.2.2.13          | CRB SSI Receive Enable (RE) Bit 13                 | 7-26           |

| 7.3.2.2.14          | CRB SSI Transmit Interrupt Enable (TIE) Bit 14     |                |

| 7.3.2.2.15          | CRB SSI Receive Interrupt Enable (RIE) Bit 15      |                |

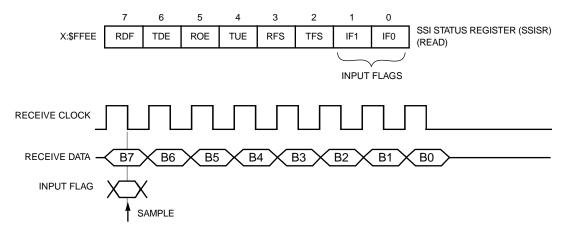

| 7.3.2.3             | SSI Status Register (SSISR)                        |                |

| 7.3.2.3.1           | SSISR Serial Input Flag 0 (IF0) Bit 0              |                |

| 7.3.2.3.2           | SSISR Serial Input Flag 1 (IF1) Bit 1              |                |

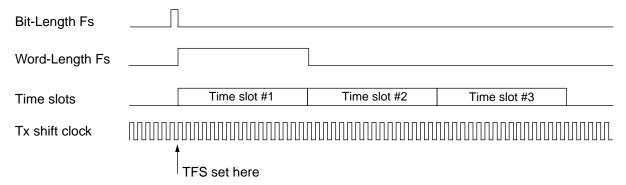

| 7.3.2.3.3           | SSISR Transmit Frame Sync Flag (TFS) Bit 2         |                |

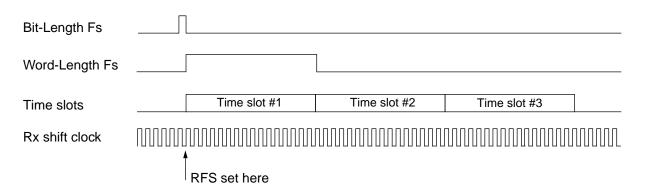

| 7.3.2.3.4           | SSISR Receive Frame Sync Flag (RFS) Bit 3          |                |

| 7.3.2.3.5           | SSISR Transmitter Underrun Error Flag (TUE) Bit 4  |                |

| 7.3.2.3.6           | SSISR Receiver Overrun Error Flag (ROE) Bit 5      |                |

| 7.3.2.3.7           | SSISR SSI Transmit Data Register Empty (TDE) Bit 6 | 7-30           |

| 7.3.2.3.8           | SSISR SSI Receive Data Register Full (RDF) Bit 7   | 7-30           |

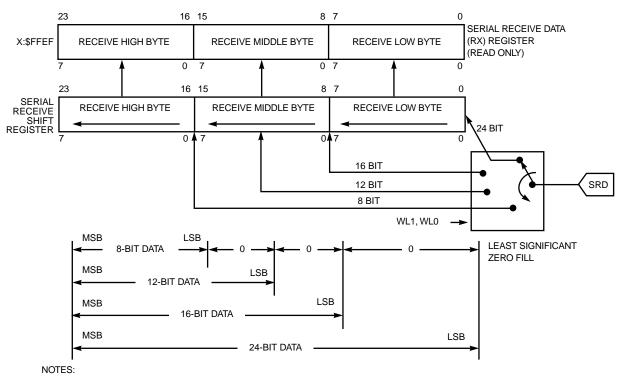

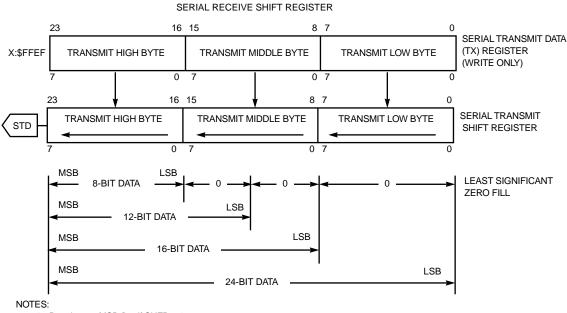

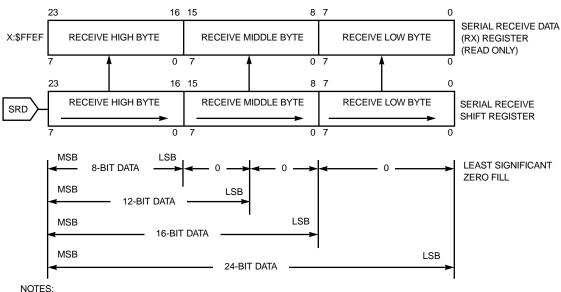

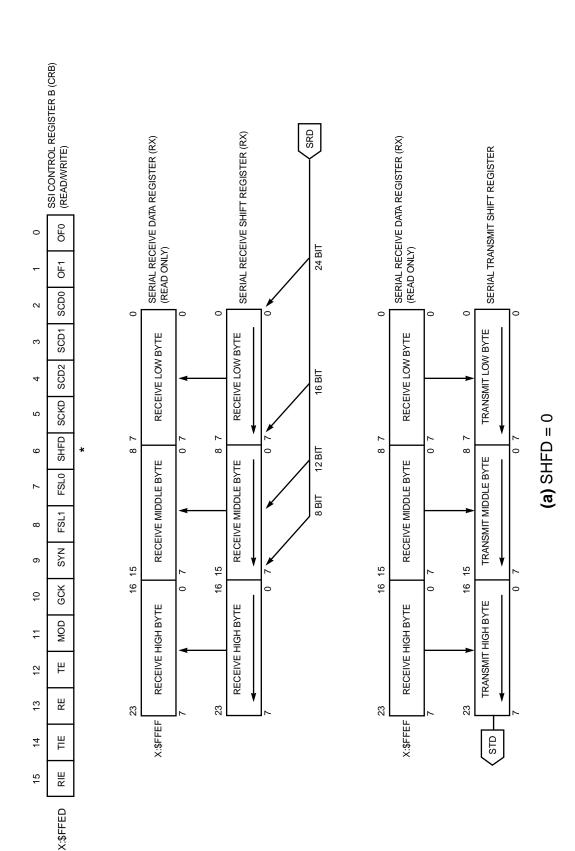

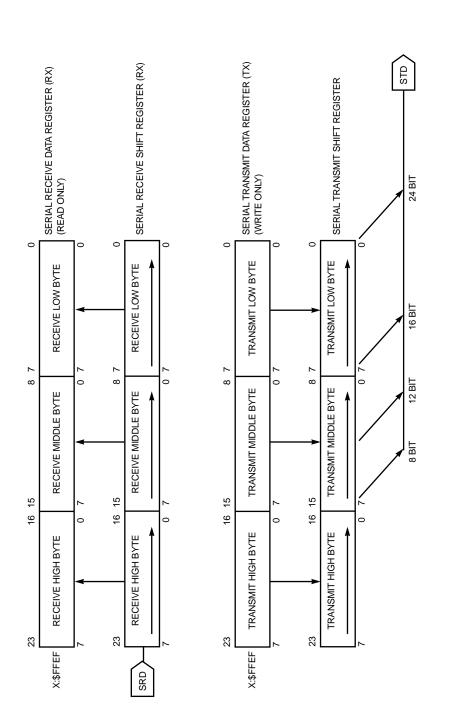

| 7.3.2.4             | SSI Receive Shift Register                         | 7-30           |

| 7.3.2.5             | SSI Receive Data Register (RX)                     | 7-32           |

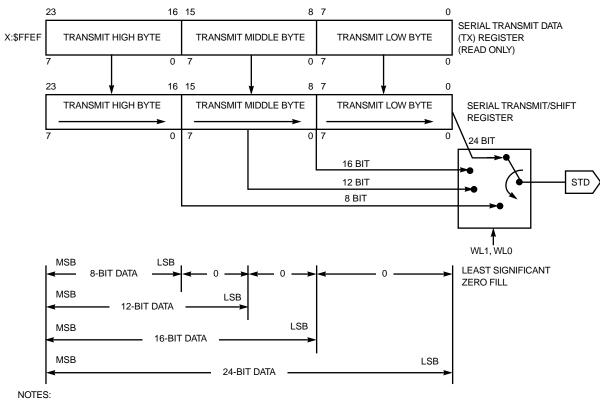

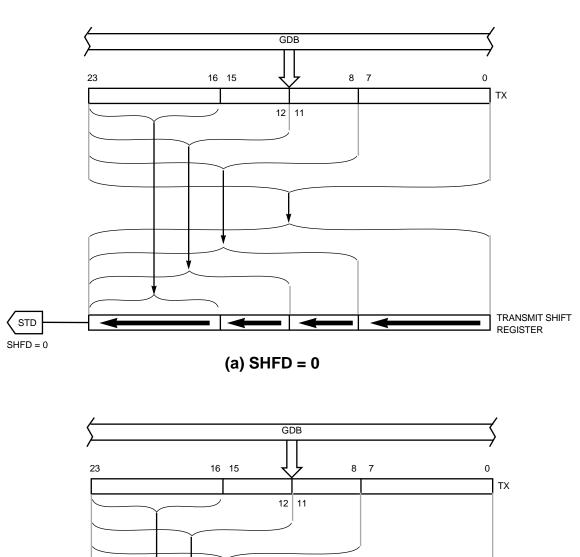

| 7.3.2.6             | SSI Transmit Shift Register                        | 7-32           |

| 7.3.2.7             | SSI Transmit Data Register (TX)                    | 7-32           |

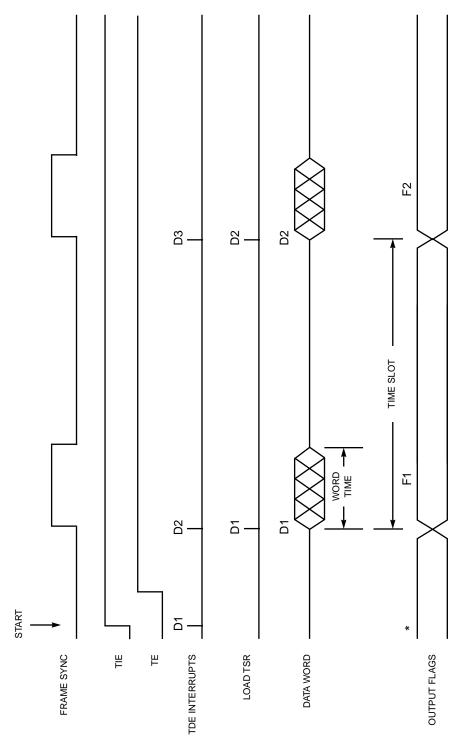

| 7.3.2.8             | Time Slot Register (TSR)                           |                |

| 7.3.3               | Operational Modes and Pin Definitions              | 7-34           |

| 7.3.4               | Registers After Reset                              | 7-35           |

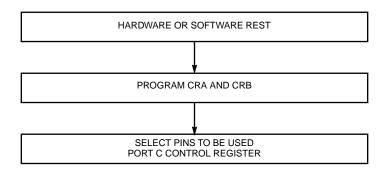

| 7.3.5               | SSI Initialization                                 | 7-37           |

| 7.3.6               | SSI Exceptions                                     |                |

| 7.3.7               | Operating Modes – Normal, Network, and On-Demand   |                |

| 7.3.7.1             | Data/Operation Formats                             |                |

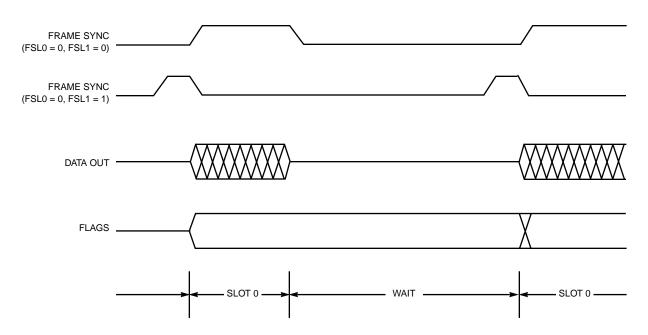

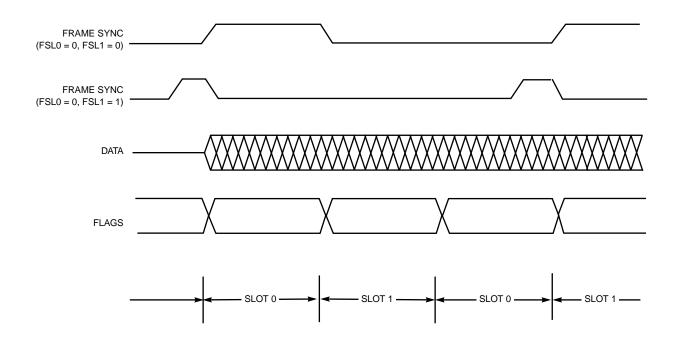

| 7.3.7.1.1           | Normal/Network Mode Selection                      |                |

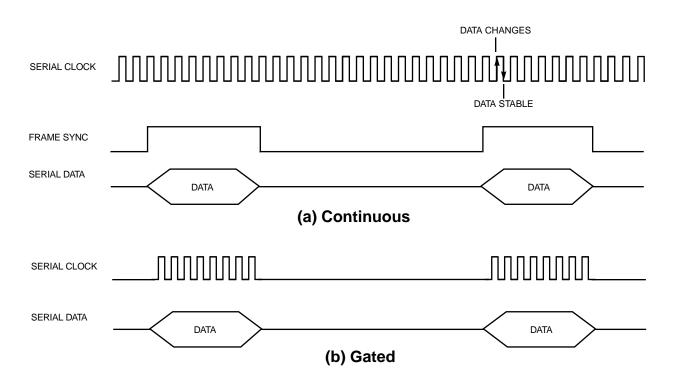

| 7.3.7.1.2           | Continuous/Gated Clock Selection                   | 7-45           |

| 7.3.7.1.3           | Synchronous/Asynchronous Operating Modes           |                |

| 7.3.7.1.4           | Frame Sync Selection                               | 7-55           |

| 7.3.7.1.5           | Shift Direction Selection                          | 7-59           |

| 7.3.7.2             | Normal Mode Examples                               |                |

| 7.3.7.2.1           | Normal Mode Transmit                               |                |

| 7.3.7.2.2           | Normal Mode Receive                                |                |

| 7.3.7.3             | Network Mode Examples                              |                |

| 7.3.7.3.1           | Network Mode Transmit                              |                |

| 7.3.7.3.2           | Network Mode Receive                               |                |

| 7.3.7.4             | On-Demand Mode Examples                            |                |

| 7.3.7.4.1           | On-Demand Mode – Continuous Clock                  |                |

| 7.3.7.4.2           | On-Demand Mode – Gated Clock                       |                |

| 7.3.8               | Flags                                              |                |

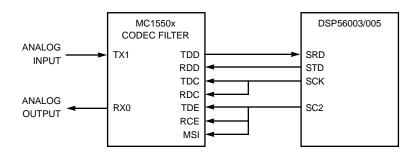

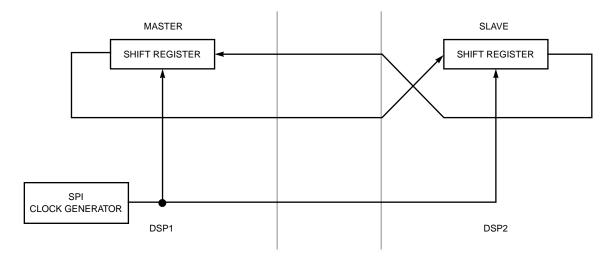

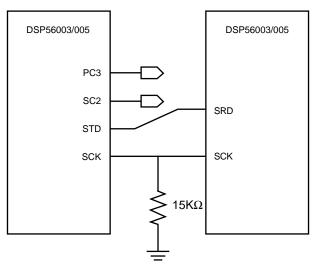

| 7.3.9               | Example Circuits                                   | 7-87           |

| Table of Contents (Continued) |                                                              |                               |

|-------------------------------|--------------------------------------------------------------|-------------------------------|

| Paragraph<br>Number           | Title                                                        | Page<br>Number                |

|                               | SECTION 8                                                    |                               |

|                               | TIMER/EVENT COUNTER                                          |                               |

| 8.1                           | INTRODUCTION                                                 |                               |

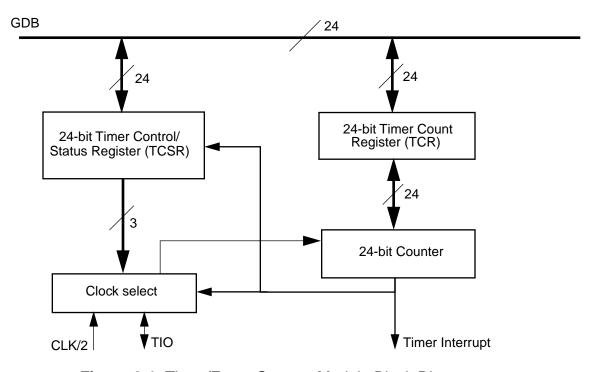

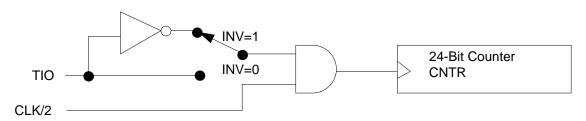

| 8.2                           | TIMER/EVENT COUNTER BLOCK DIAGRAM                            |                               |

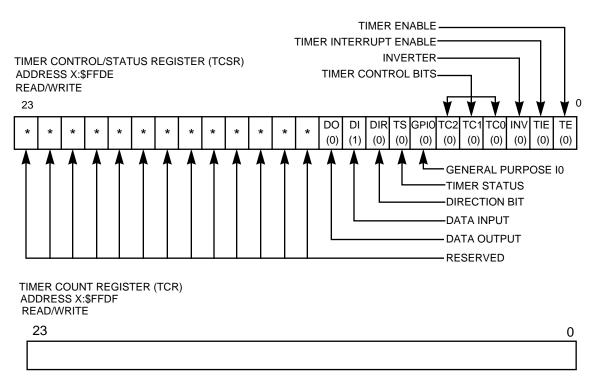

| 8.3                           | TIMER COUNT REGISTER (TCR)                                   |                               |

| 8.4                           | TIMER CONTROL/STATUS REGISTER (TCSR)                         |                               |

| 8.4.1                         | TCSR Timer Enable (TE) Bit 0                                 |                               |

| 8.4.2                         | TCSR Timer Interrupt Enable (TIE) Bit 1                      |                               |

| 8.4.3                         | TCSR Inverter (INV) Bit 2                                    | 8-5                           |

| 8.4.4                         | TCSR Timer Control (TC0-TC2) Bits 3-5                        |                               |

| 8.4.5                         | TCSR General Purpose I/O (GPIO) Bit 6                        | 8-6                           |

| 8.4.6                         | TCSR Timer Status (TS) Bit 7                                 |                               |

| 8.4.7                         | TCSR Direction (DIR) Bit 8                                   |                               |

| 8.4.8                         | TCSR Data Input (DI) Bit 9                                   | 8- <i>1</i>                   |

| 8.4.9<br>8.4.10               | TCSR Data Output (DO) Bit 10                                 | δ- <i>1</i><br>ο <del>7</del> |

| 8.5                           | TIMER/EVENT COUNTER MODES OF OPERATION                       |                               |

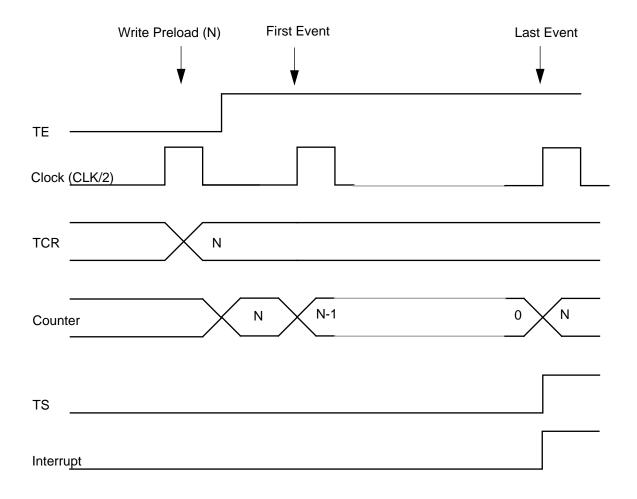

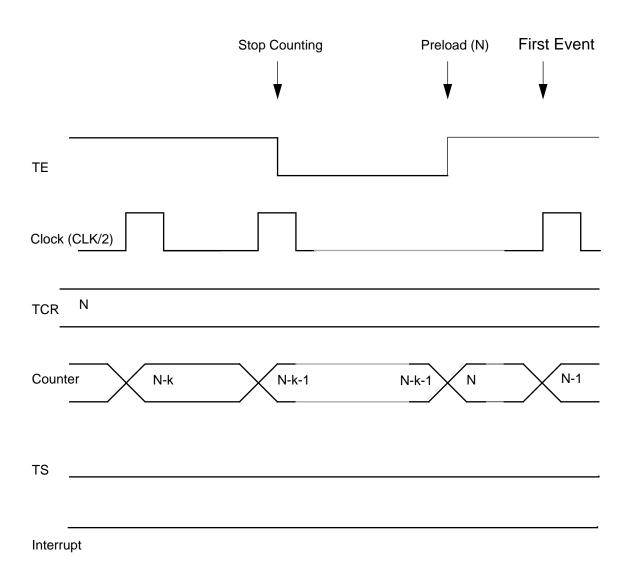

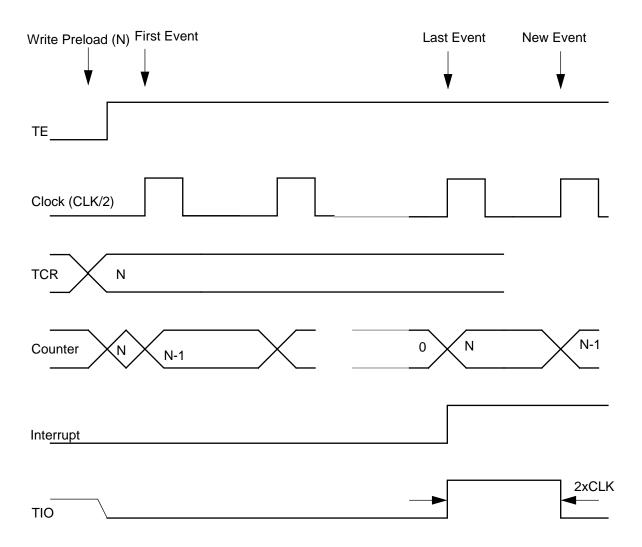

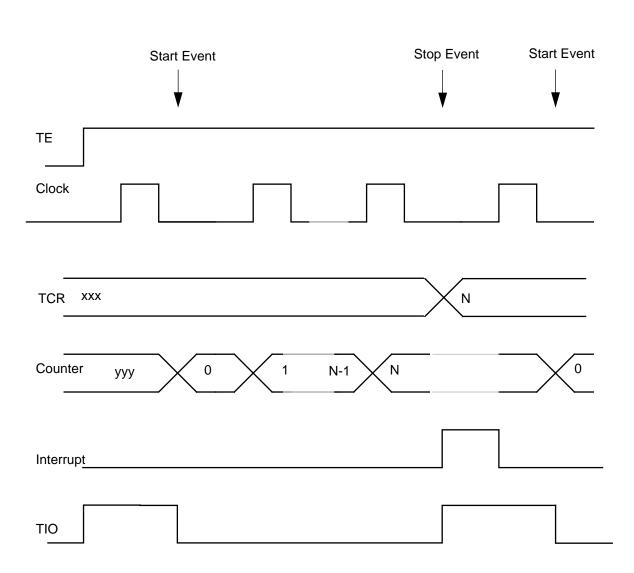

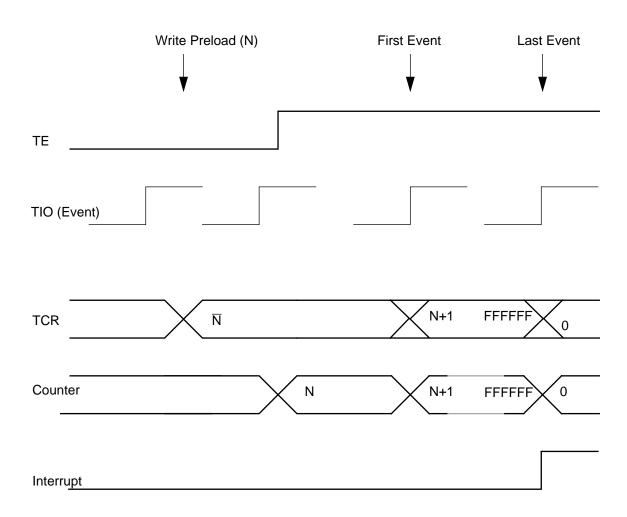

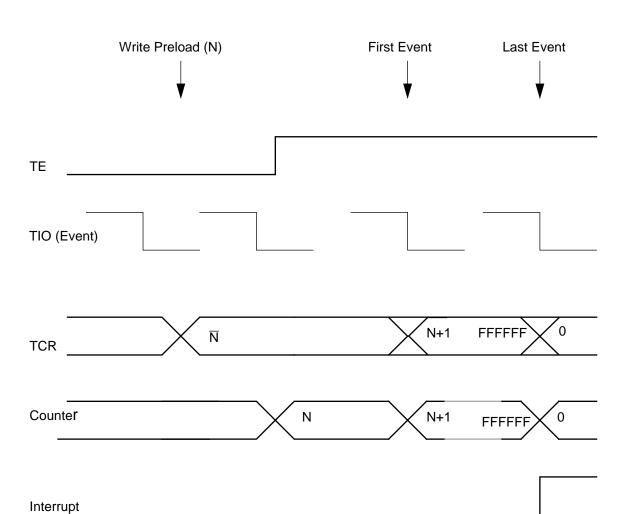

| 8.5.1                         | Timer Mode 0                                                 | 0-7                           |

| 0.5.1                         | (Standard Timer Mode, Internal Clock, No Timer Output)       | 8-8                           |

| 8.5.2                         | Timer Mode 1                                                 | 0 0                           |

| 0.0.2                         | (Standard Timer Mode, Internal Clock, Output Pulse Enabled)  | 8-10                          |

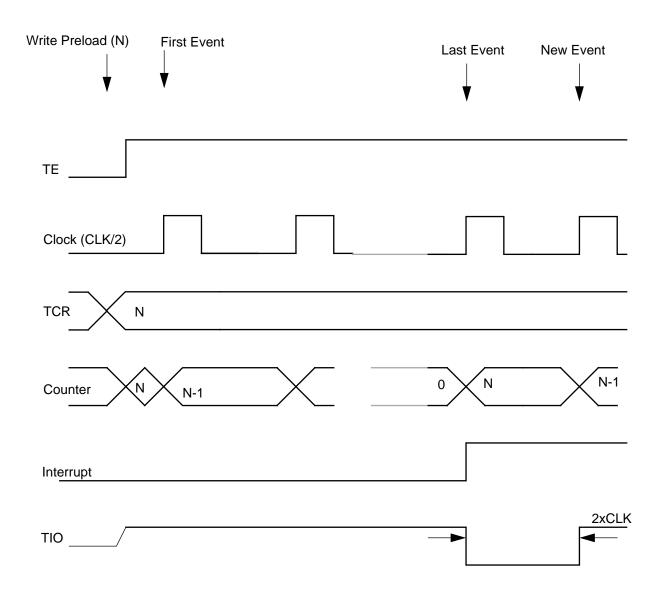

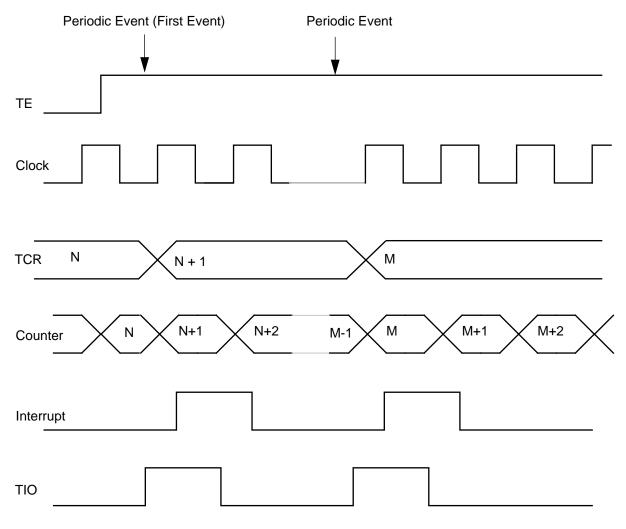

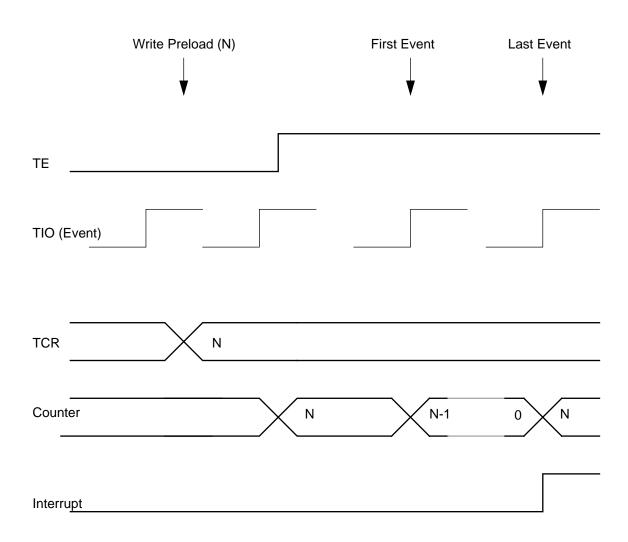

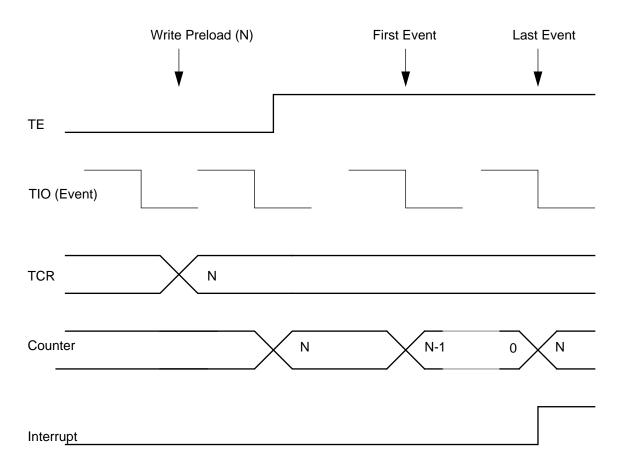

| 8.5.3                         | Timer Mode 2                                                 | 0 10                          |

| 0.0.0                         | (Standard Timer Mode, Internal Clock, Output Toggle Enabled) | 8-12                          |

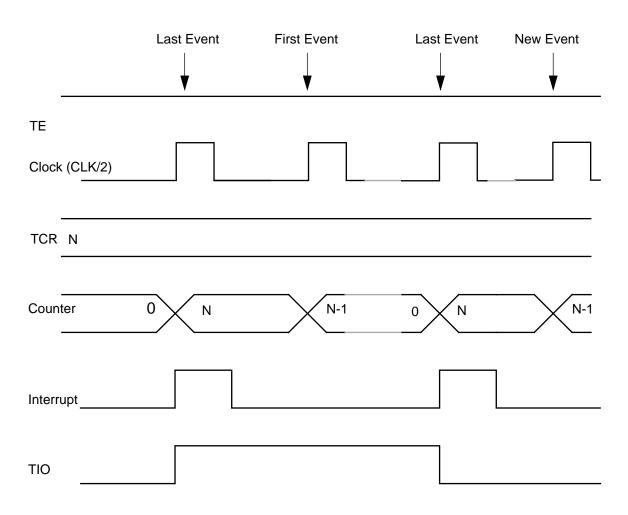

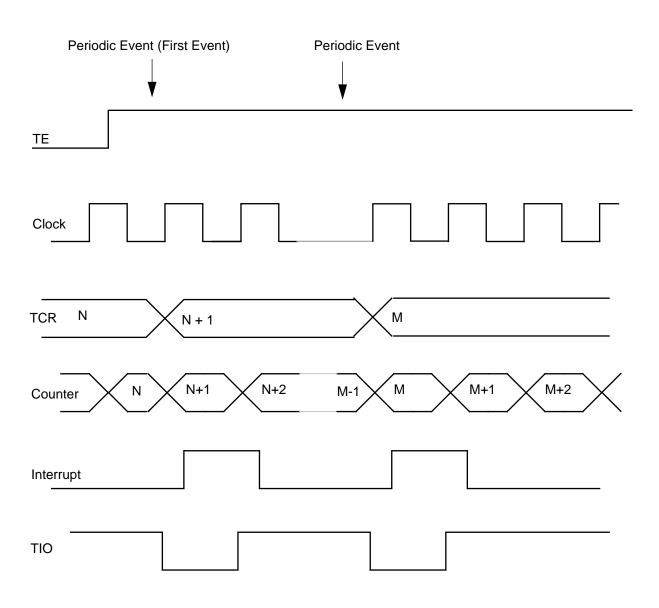

| 8.5.4                         | Timer Mode 4 (Pulse Width Measurement Mode)                  |                               |

| 8.5.5                         | Timer Mode 5 (Period Measurement Mode)                       |                               |

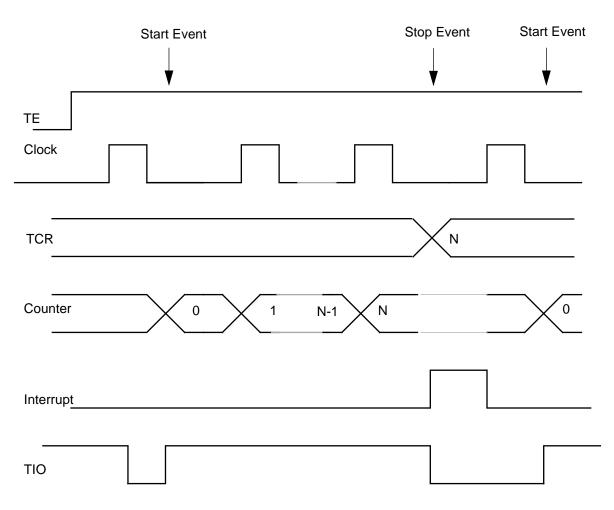

| 8.5.6                         | Timer Mode 6 (Standard Time Counter Mode, External Clock)    |                               |

| 8.5.7                         | Timer Mode 7 (Standard Timer Mode, External Clock)           | 8-19                          |

| 8.6                           | TIMER/EVENT COUNTER BEHAVIOR DURING WAIT AND STOP.           | 8-21                          |

| 8.7                           | OPERATING CONSIDERATIONS                                     | 8-21                          |

| 8.8                           | SOFTWARE EXAMPLES                                            |                               |

| 8.8.1                         | General Purpose I/O Input                                    |                               |

| 8.8.2                         | General Purpose I/O Output                                   |                               |

| 8.8.3                         | Timer Mode 0, Input Clock, GPIO Output, and No Timer Output  |                               |

| 8.8.4                         | Pulse Width Measurement Mode (Timer Mode 4)                  |                               |

| 8.8.5                         | Period Measurement Mode (Timer Mode 5)                       | 8-24                          |

|           | Table of Contents (Continued) | _      |

|-----------|-------------------------------|--------|

| Paragraph |                               | Page   |

| Number    | Title                         | Number |

### SECTION 9 PULSE WIDTH MODULATORS

| 9.1     | INTRODUCTION                                           |

|---------|--------------------------------------------------------|

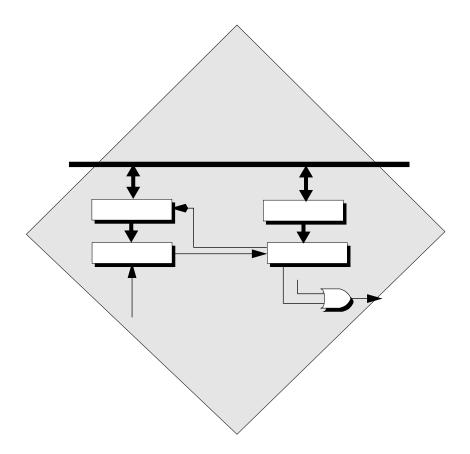

| 9.2     | PULSE WIDTH MODULATOR INTERNAL ARCHITECTURE 9-3        |

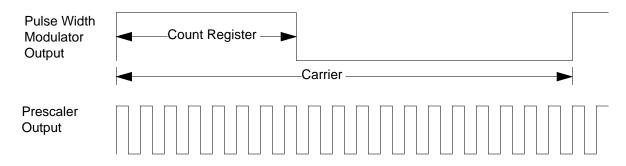

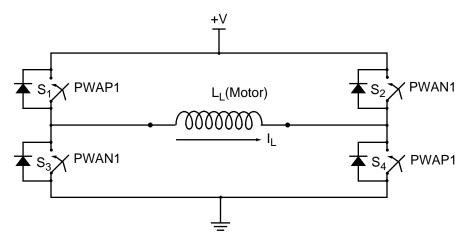

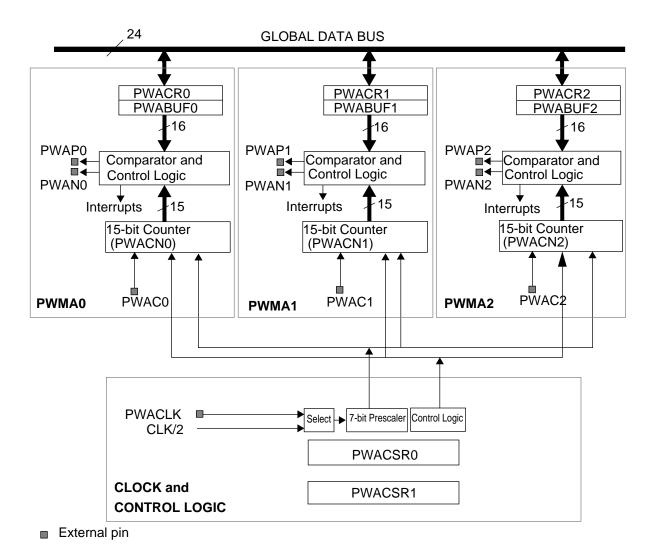

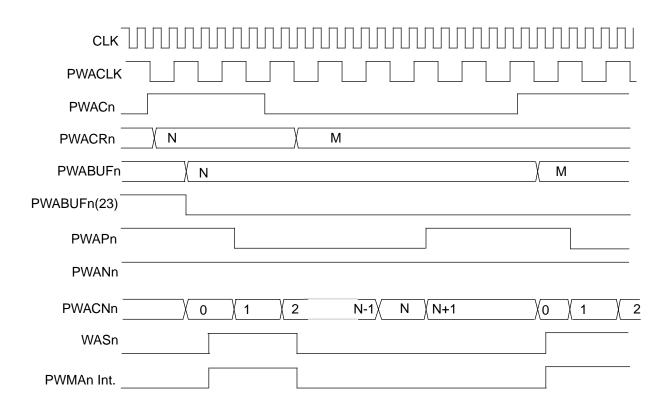

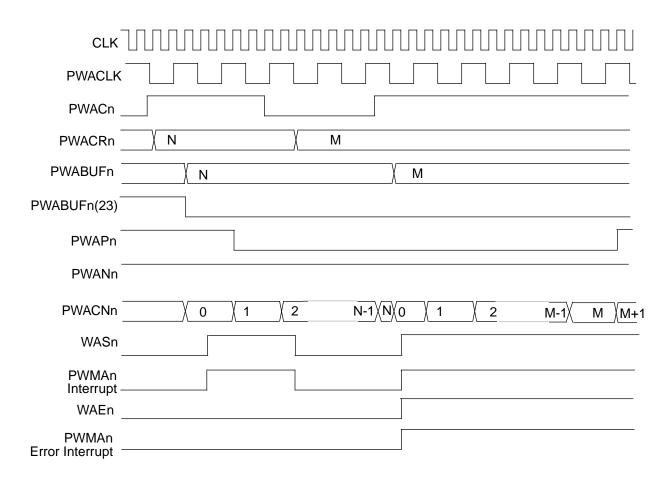

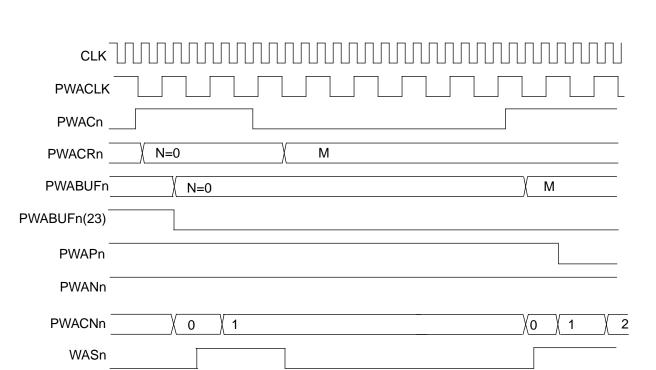

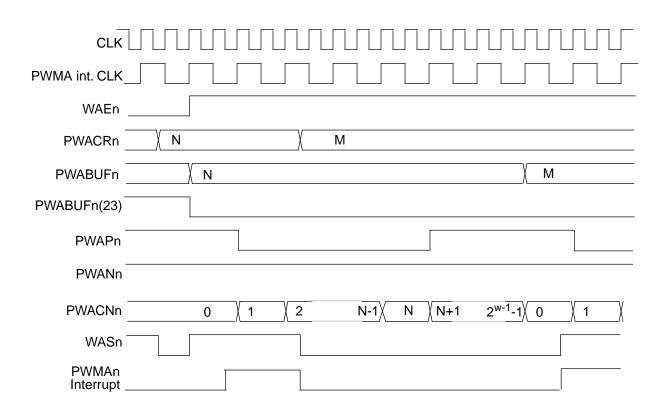

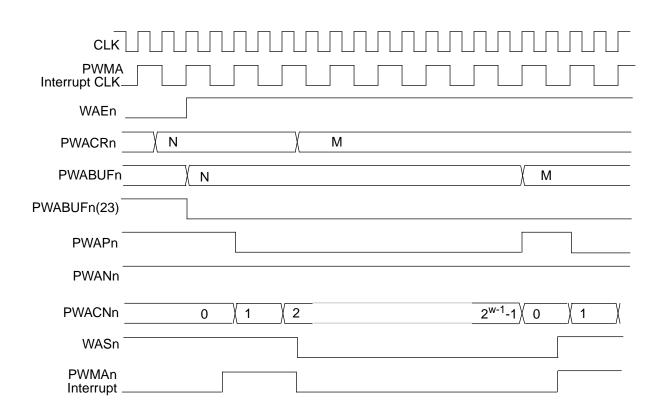

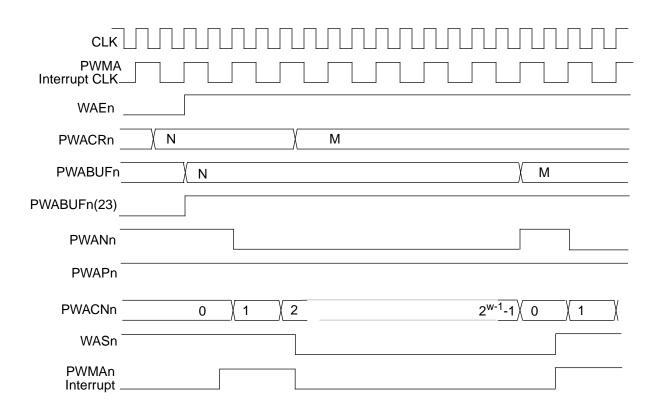

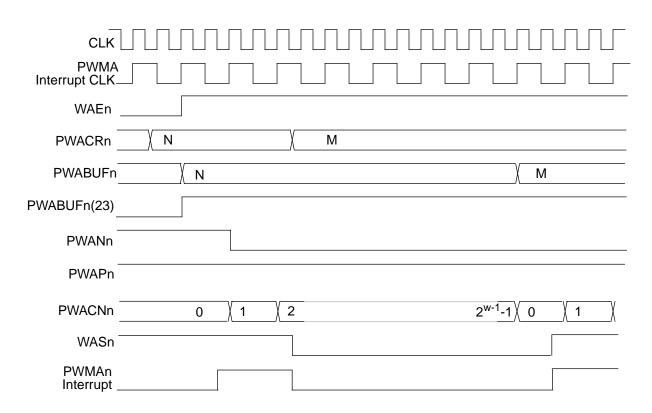

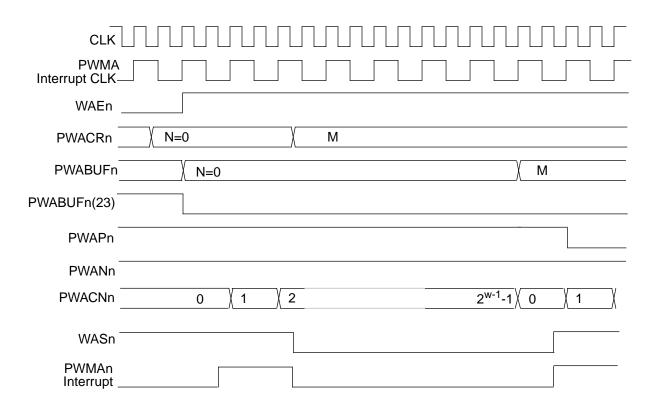

| 9.2.1   | Pulse Width Modulator A (PWMA) Overview                |

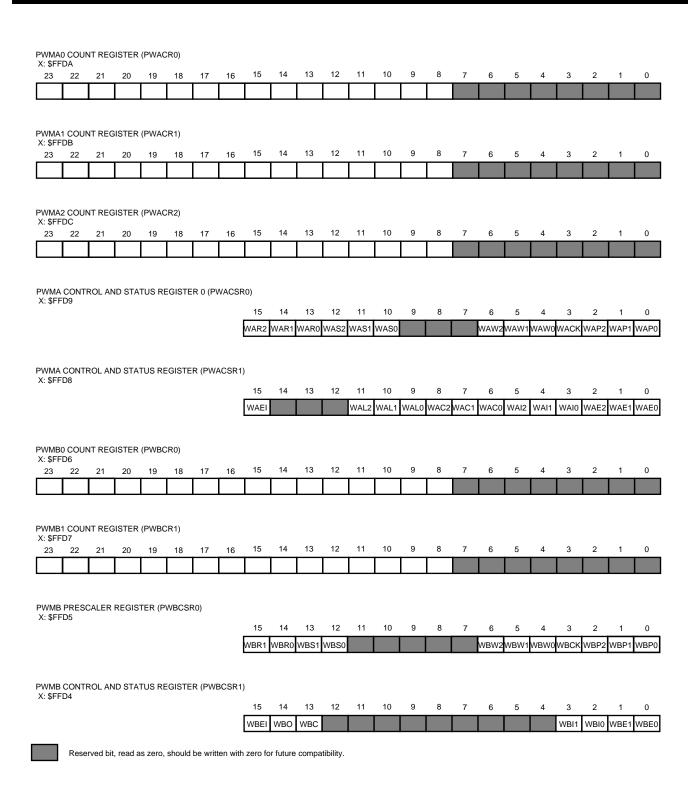

| 9.2.1.1 | PWMA Count Registers PWMA0, PWMA1, and PWMA2 9-4       |

| 9.2.1.1 | PWMA Clock and Control Logic                           |

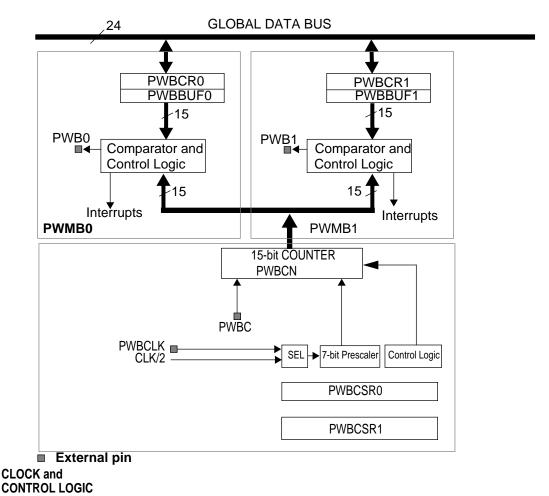

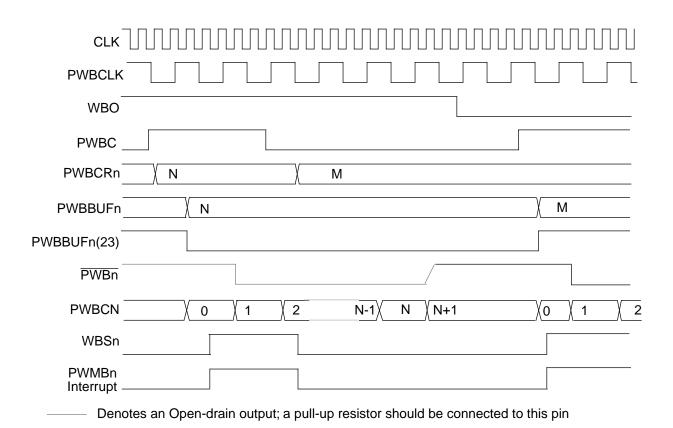

| 9.2.1.2 | Pulse Width Modulator B (PWMB) Overview                |

| 9.2.2.1 | PWMB Count Registers PWMB0 and PWMB19-6                |

| 9.2.2.1 | PWMB Clock and Control Logic                           |

| 9.2.2.2 | PULSE WIDTH MODULATOR PROGRAMMING MODEL 9-8            |

| 9.3.1   | PWMAn Count Registers — PWACR0, PWACR1, and PWACR2 9-8 |

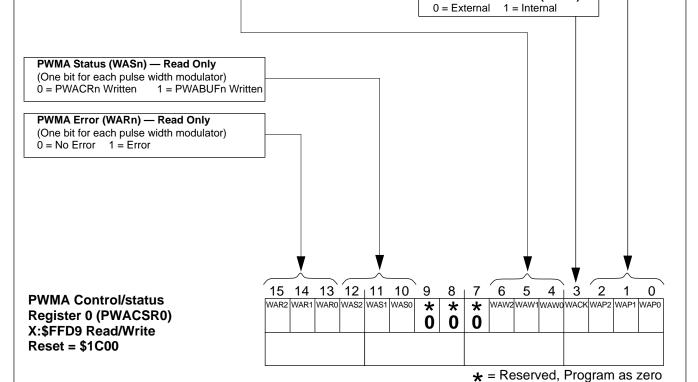

| 9.3.2   | PWMAn Control/Status Register 0 — PWACSR09-8           |

| 9.3.2.1 | PWMAn Prescale (WAP0-WAP2) Bits 0-2                    |

| 9.3.2.2 | PWMAn Clock Source (WACK) Bit 3                        |

| 9.3.2.3 | PWMAn Data Width (WAW0-WAW2) Bits 4-6                  |

| 9.3.2.4 | PWMAn PWACSR0 Reserved Bits 7-99-11                    |

| 9.3.2.5 | PWMAn Status (WAS0-WAS2) Bits 10-12                    |

| 9.3.2.6 | PWMAn Error (WAR0-WAR2) Bits 13-15                     |

| 9.3.3   | PWMA Control/Status Register 1 (PWACSR1)9-12           |

| 9.3.3.1 | PWACSR1 PWMAn Enable (WAEn) Bits 0-2                   |

| 9.3.3.2 | PWACSR1 PWMAn Interrupt Enable (WAIn) Bits 3-59-12     |

| 9.3.3.3 | PWACSR1 PWMAn Carrier Select (WACn) Bits 6-8 9-12      |

| 9.3.3.4 | PWACSR1 PWMAn Output Polarity (WALn) Bits 9-119-13     |

| 9.3.3.5 | PWACSR1 Reserved Bits 12-149-13                        |

| 9.3.3.6 | PWACSR1 PWMA Error Interrupt Enable (WAEI) Bit 15 9-13 |

| 9.3.4   | PWMB Count Registers — PWBCR0, PWBCR1 9-13             |

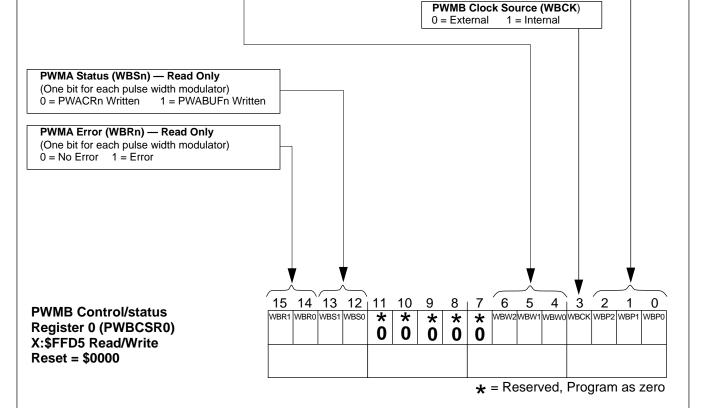

| 9.3.5   | PWMB Control/Status Register 0 — PWBCSR09-13           |

| 9.3.5.1 | PWBCSR0 PWMB Prescale (WBP0- WBP2) Bits 0-29-13        |

| 9.3.5.2 | PWBCSR0 PWMB Clock Source (WBCK) Bit 3                 |

| 9.3.5.3 | PWBCSR0 PWMB Data Width (WBW0-WBW2) Bits 4-6 9-14      |

| 9.3.5.4 | PWBCSR0 Reserved Bits 7-119-15                         |

| 9.3.5.5 | PWBCSR0 PWMBn Status (WBSn) Bits 12-139-15             |

| 9.3.5.6 | PWBCSR0 PWMBn Error (WBRn) Bit 14-159-15               |

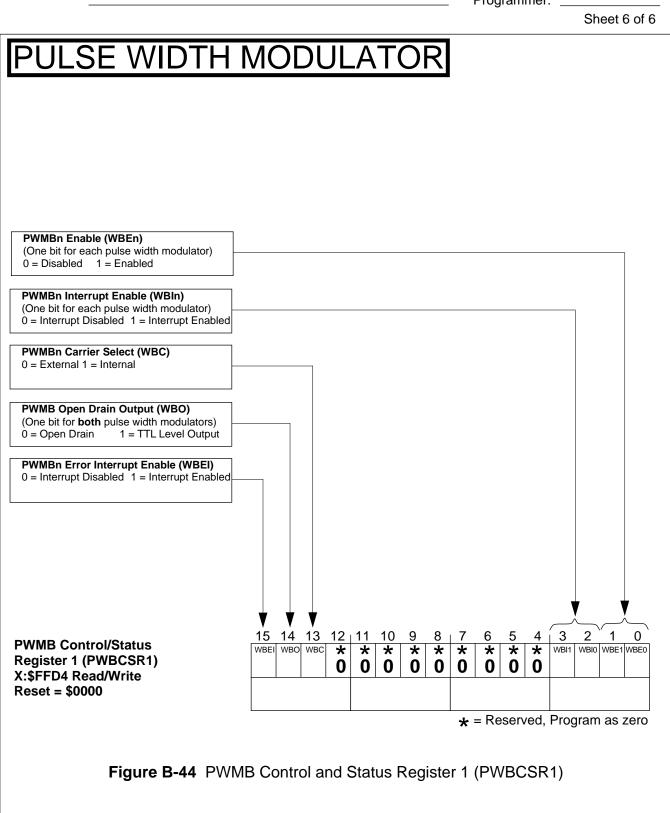

| 9.3.6   | PWMB Control/Status Register 1 — PWBCSR19-16           |

| 9.3.6.1 | PWBCSR1 PWMBn Enable (WBEn) Bits 0-1                   |

| 9.3.6.2 | PWBCSR1 PWMBn Interrupt Enable (WBIn) Bits 2-39-16     |

| 9.3.6.3 | PWBCSR1 Reserved Bits 4-129-16                         |

| 9.3.6.4 | PWBCSR1 PWMB Carrier Select (WBC) Bit 13               |

|         |                                                        |

| Table of Contents (Continued)                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                      |  |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|

| Paragraph<br>Number                                                                                                                  | n<br>Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page<br>Number                                                       |  |

| 9.3.6.5<br>9.3.6.6<br>9.4<br>9.4.1<br>9.4.2                                                                                          | PWBCSR1 PWMB Open Drain Output (WBO) Bit 14                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9-17<br>9-17<br>9-17                                                 |  |

|                                                                                                                                      | SECTION 10<br>WATCHDOG TIMER                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                      |  |

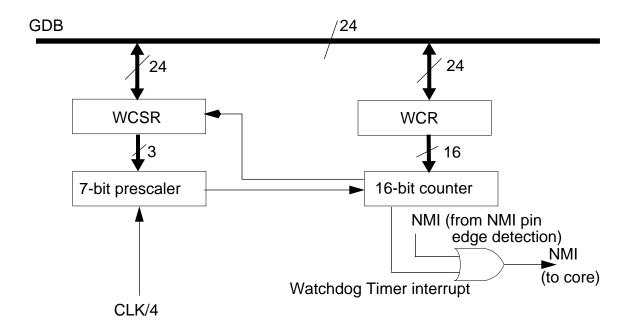

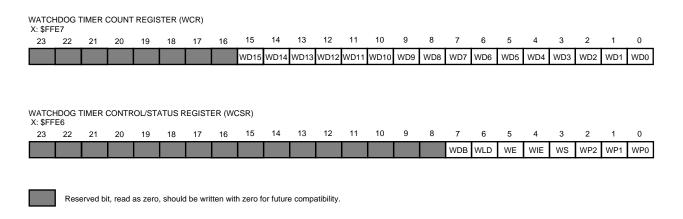

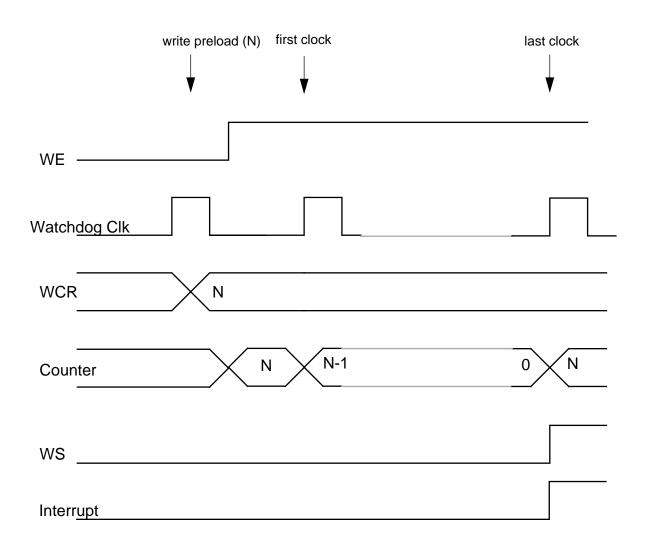

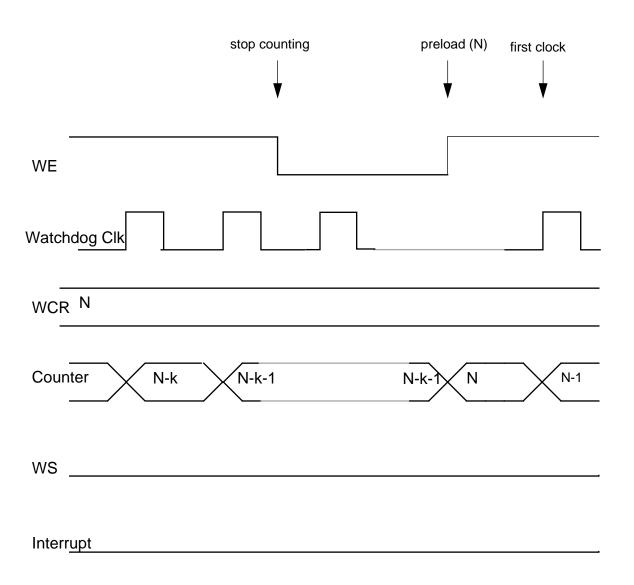

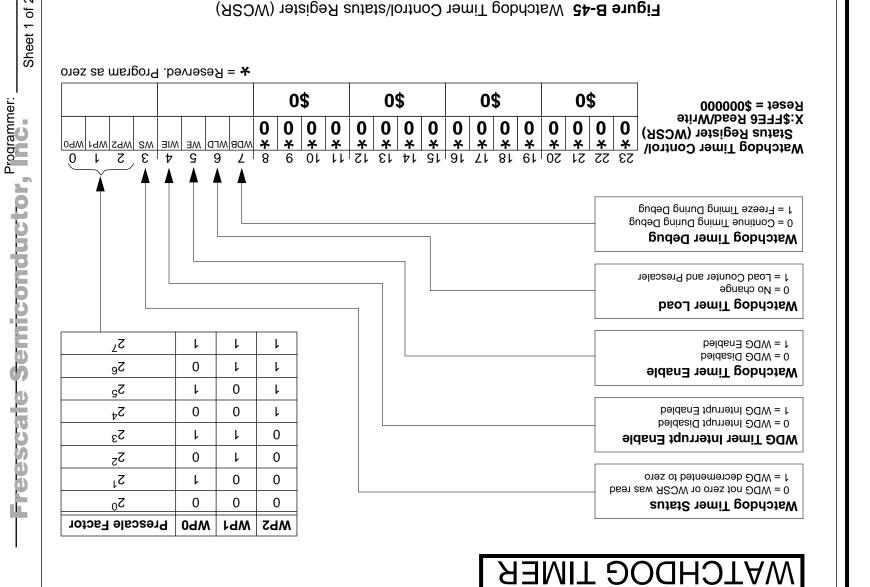

| 10.1<br>10.2<br>10.2.1<br>10.2.2<br>10.2.2.1<br>10.2.2.2<br>10.2.2.3<br>10.2.2.4<br>10.2.2.5<br>10.2.2.6<br>10.2.2.7<br>10.3<br>10.4 | INTRODUCTION.  WATCHDOG TIMER ARCHITECTURE  Watchdog Timer Count Register (WCR)  Watchdog Timer Control/status Register (WCSR)  WCSR Watchdog Timer Prescale (WPO-WP2) Bits 0-2  WCSR Watchdog Timer status (WS) Bit 3  WCSR Watchdog Timer Interrupt Enable (WIE) Bit 4  WCSR Watchdog Timer Enable (WE) Bit 5  WCSR Watchdog Timer Load (WLD) Bit 6  WCSR Watchdog Timer Debug (WDB) Bit 7  WCSR Reserved Bits 8-15  WATCHDOG TIMER FUNCTIONAL DESCRIPTION  PROGRAMMING CONSIDERATIONS. | 10-3<br>10-4<br>10-5<br>10-5<br>10-5<br>10-6<br>10-6<br>10-6<br>10-6 |  |

|                                                                                                                                      | APPENDIX A<br>BOOTSTRAP PROGRAM AND<br>DATA ROM LISTINGS                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                      |  |

| A.1<br>A.2<br>A.3<br>A.4                                                                                                             | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | A-4<br>A-7                                                           |  |

| <u> </u>                                                                                   |                                                                           |

|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| ## PROGRAMMING SHEETS    B.1                                                               | Page<br>lumber                                                            |

| B.2                                                                                        |                                                                           |

| C.1 INTRODUCTION C.2 DIFFERENCES C.3 SIGNAL DESCRIPTIONS C.3.1 (2.2.2.1) Bus Needed (BN) — | B-4<br>B-5<br>B-6<br>B-11<br>B-15<br>B-17<br>B-22<br>B-25<br>B-28<br>B-29 |

| C.2 DIFFERENCES                                                                            |                                                                           |

| active low output — DSP56003 Only                                                          | . C-3                                                                     |

| C.3.3 (2.2.2.3) Bus Grant ( <del>BG</del> ) — active low output — DSP56003 Only            |                                                                           |

| ·                                                                                          |                                                                           |

| active low output — DSP56003 Only                                                          |                                                                           |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                       | C-8<br>C-8<br>C-8                                                         |

| input — DSP56003 Only                                                                      | C-10                                                                      |

| Table of Contents (Continued) |                                                                                                         |                |  |

|-------------------------------|---------------------------------------------------------------------------------------------------------|----------------|--|

| Paragraph<br>Number           | ,                                                                                                       | Page<br>Number |  |

| C.4.1                         | Bus Control                                                                                             | C-10           |  |

| C.4.2                         | External Memory Interface Wait States                                                                   |                |  |

| C.4.3                         | PLL and Clock Signal Applications                                                                       |                |  |

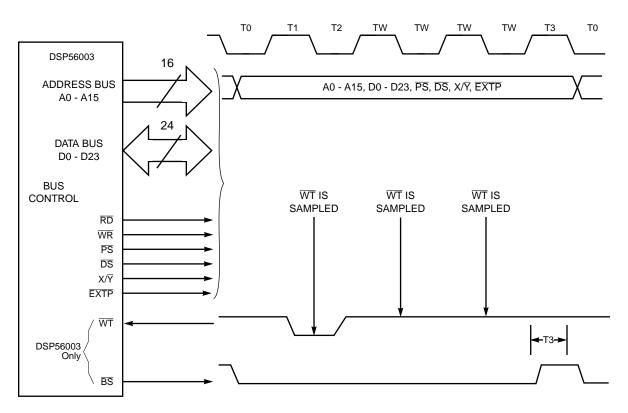

| C.5                           | (4.6) BUS STROBE AND WAIT PINS — DSP56003 Only                                                          |                |  |

| C.6                           | (4.7) BUS ARBITRATION AND SHARED MEMORY —                                                               |                |  |

|                               | DSP56003 Only                                                                                           | C-12           |  |

| C.6.1                         | (4.7.1) Bus Arbitration Using Only BR and BG                                                            |                |  |

|                               | With Internal Control — DSP56003 Only                                                                   | C-14           |  |

| C.6.2                         | (4.7.2) Bus Arbitration Using BN, BR, and BG                                                            |                |  |

|                               | With External Control — DSP56003 Only                                                                   | C-16           |  |

| C.6.3                         | (4.7.3) Arbitration Using $\overline{BR}$ and $\overline{BG}$ , and $\overline{WT}$ and $\overline{BS}$ |                |  |

|                               | With No Overhood DSP56003 Only                                                                          | C 16           |  |

# **LIST of FIGURES**

| Figu<br>Num                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Page<br>Number                                                          |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 4.4                                                                                 | DODEGOOO/OOF DIVIL D'AVANA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4.40                                                                    |

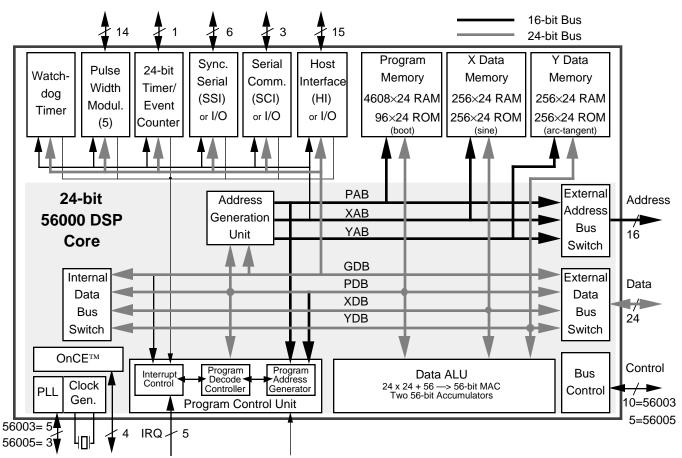

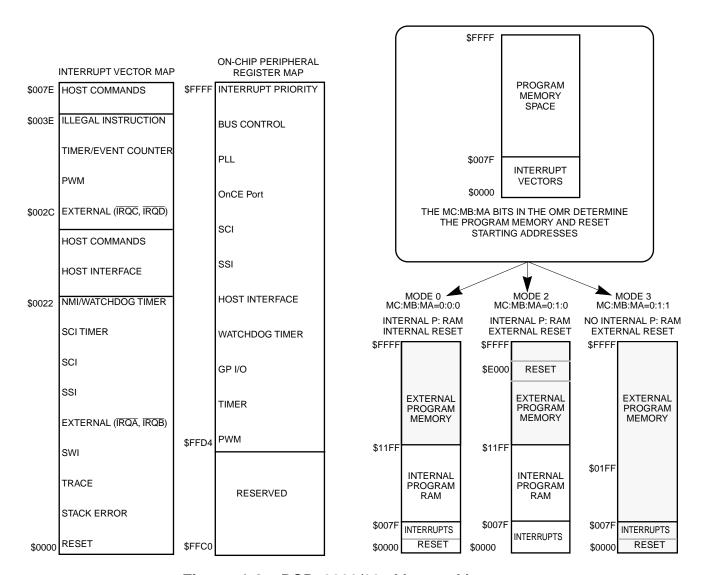

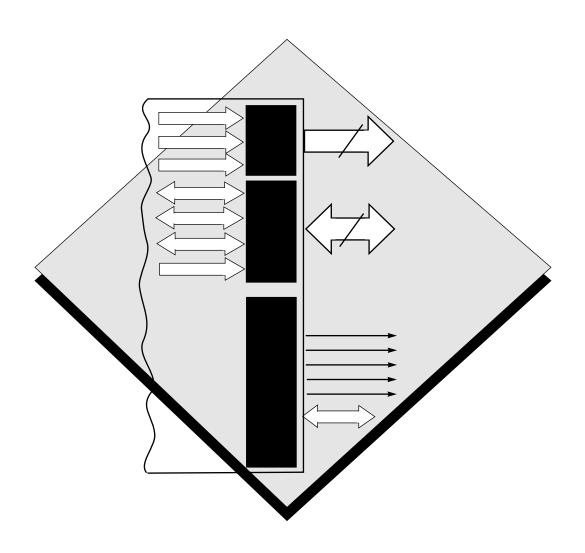

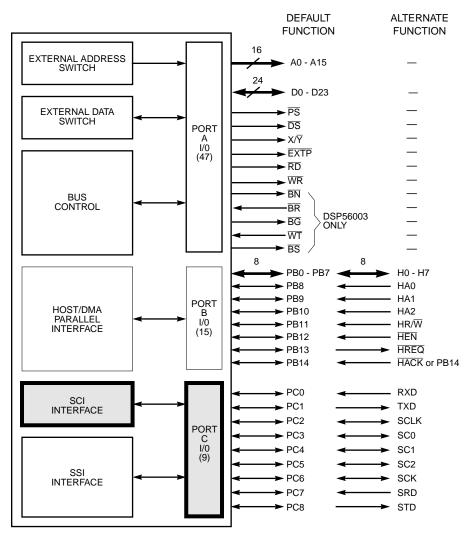

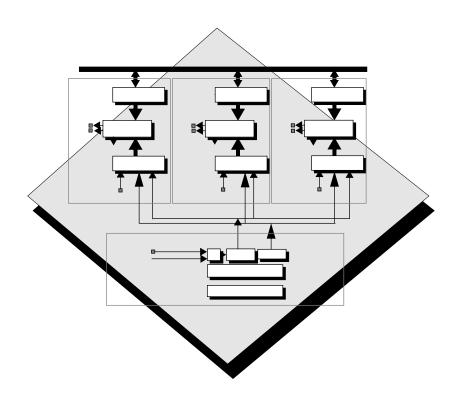

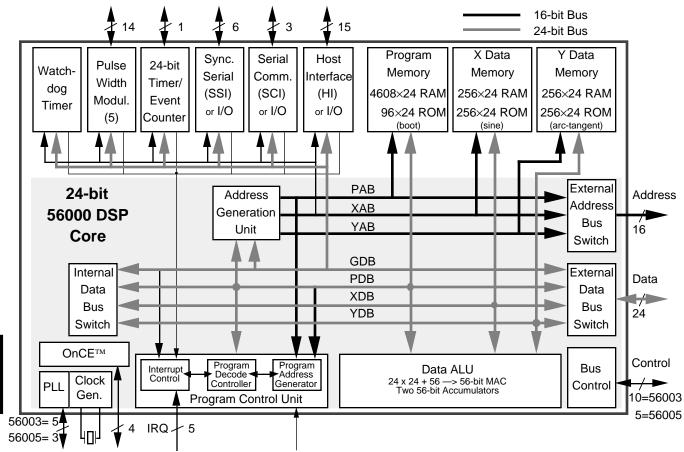

| 1-1<br>1-2a<br>1-2b                                                                 | DSP56003/005 Block Diagram DSP56003/005 Memory Maps DSP56003/005 Memory Maps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-16                                                                    |

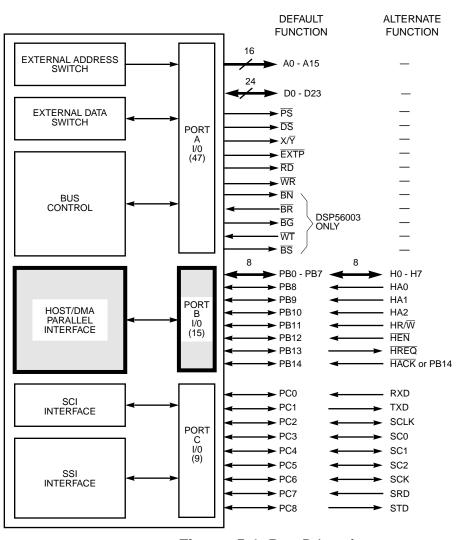

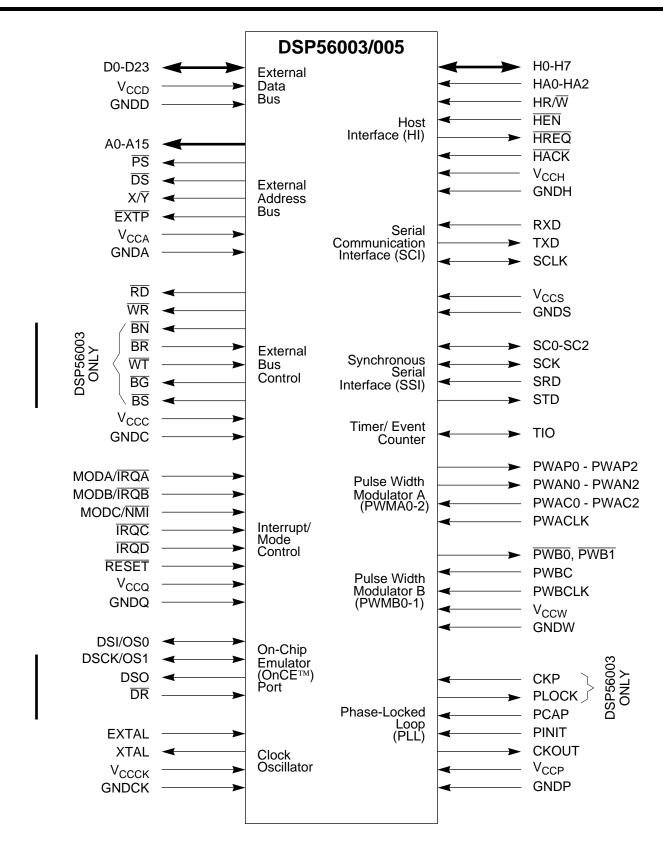

| 2-1                                                                                 | DSP56003/005 Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-4                                                                     |

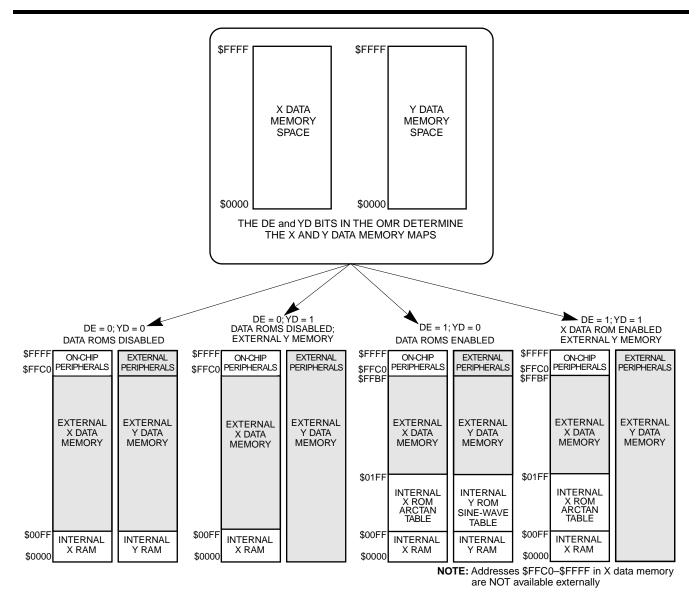

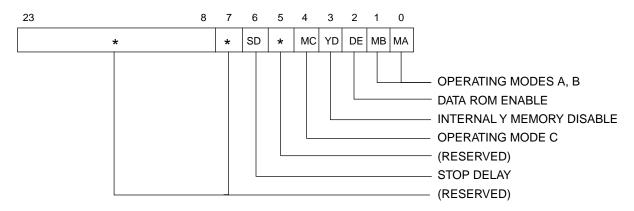

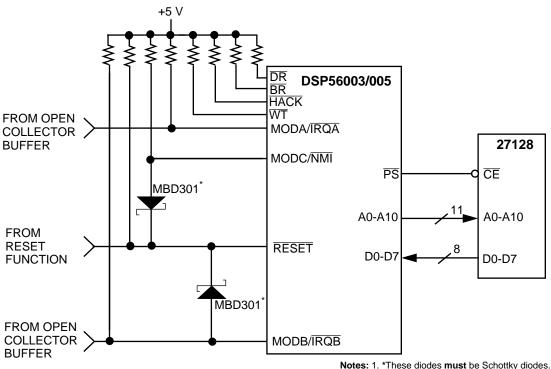

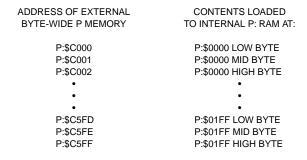

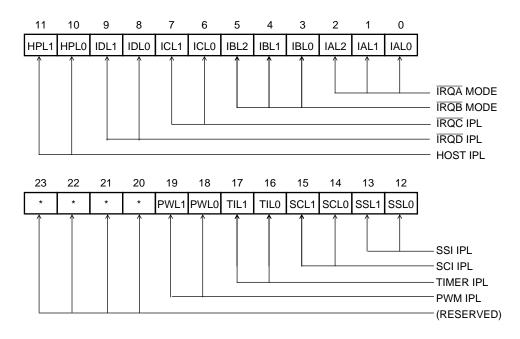

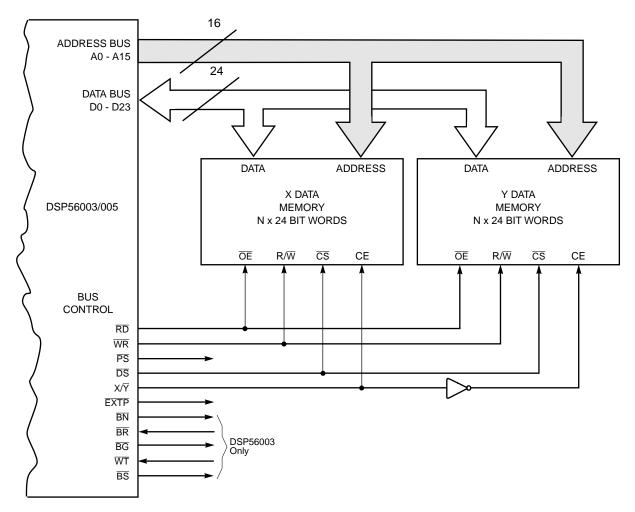

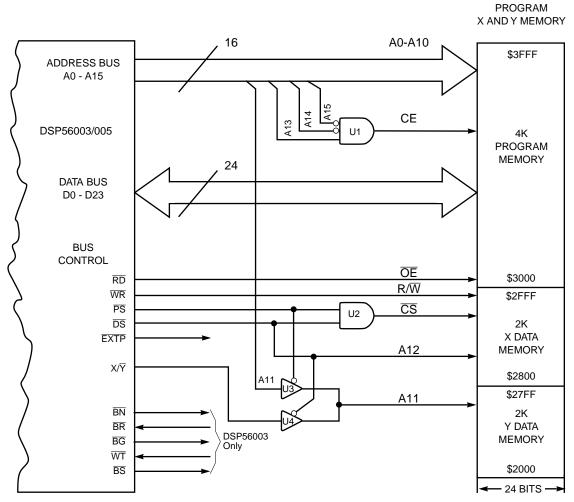

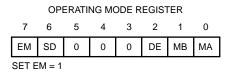

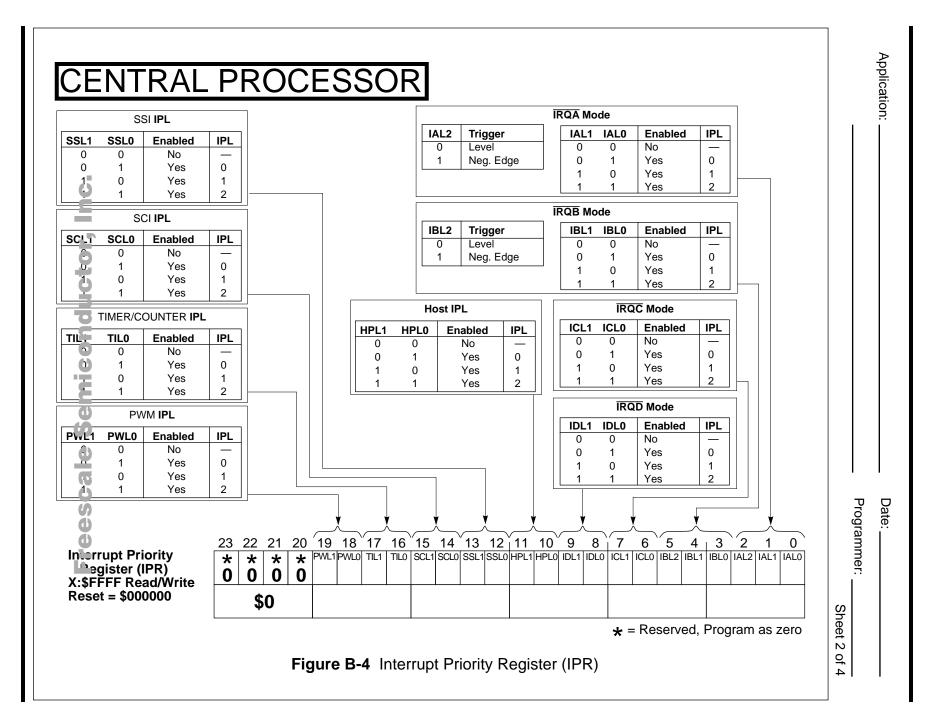

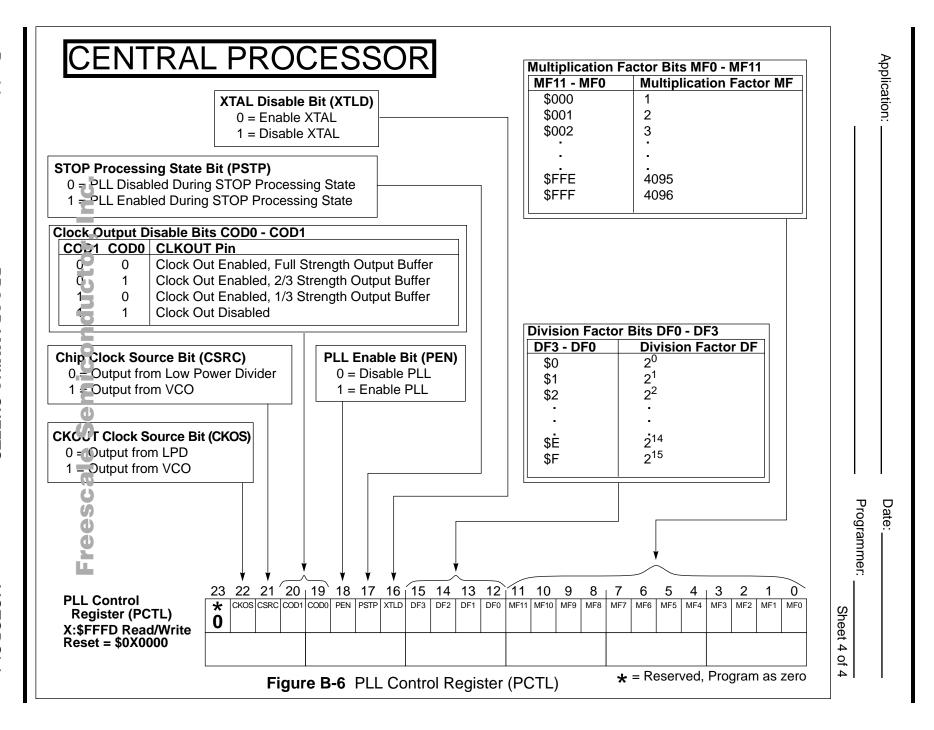

| 3-1a<br>3-1b<br>3-2<br>3-3<br>3-4                                                   | DSP56003/005 Memory Maps DSP56003/005 Memory Maps OMR Format Port A Bootstrap Circuit (Mode 1) DSP56003/005 Interrupt Priority Register                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3-5<br>3-6<br>3-9                                                       |

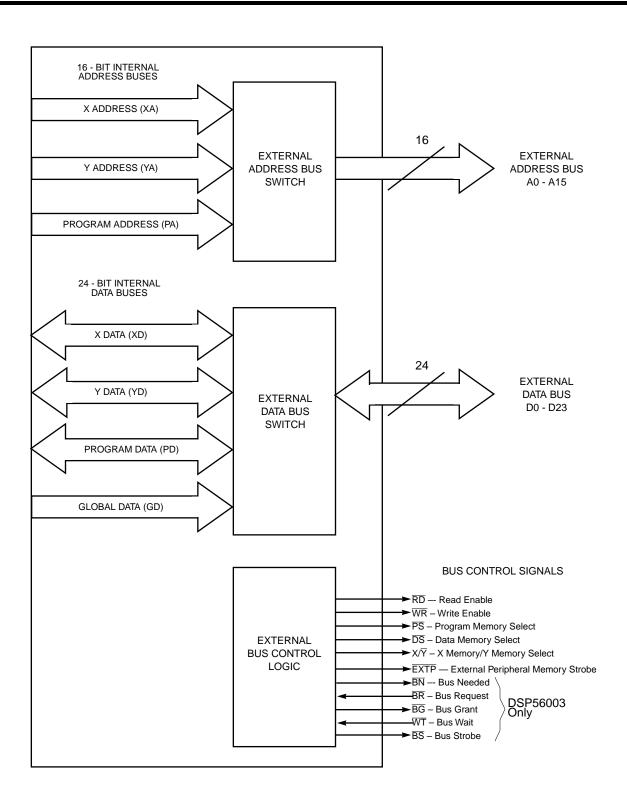

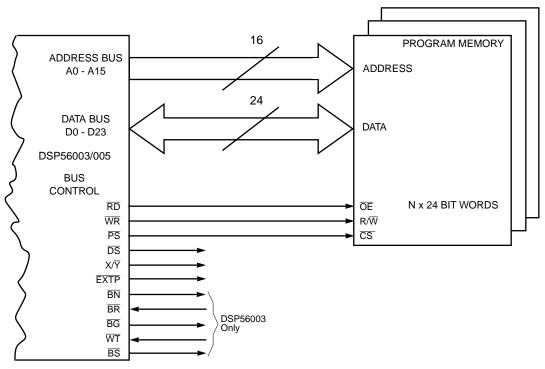

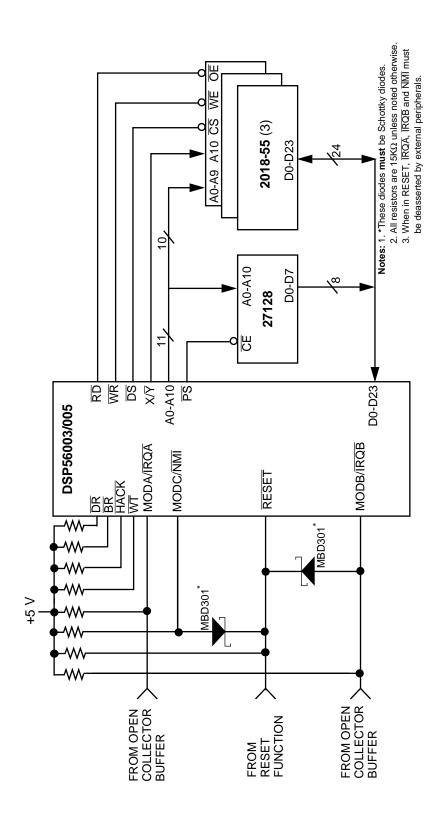

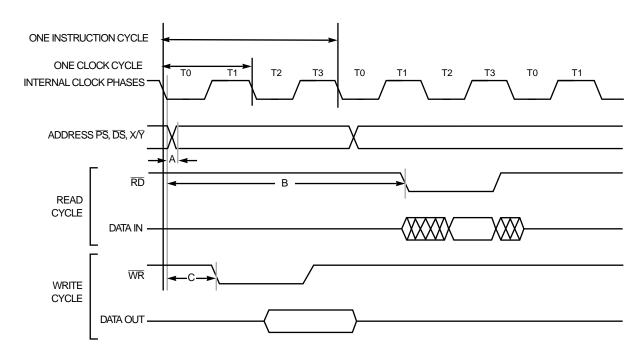

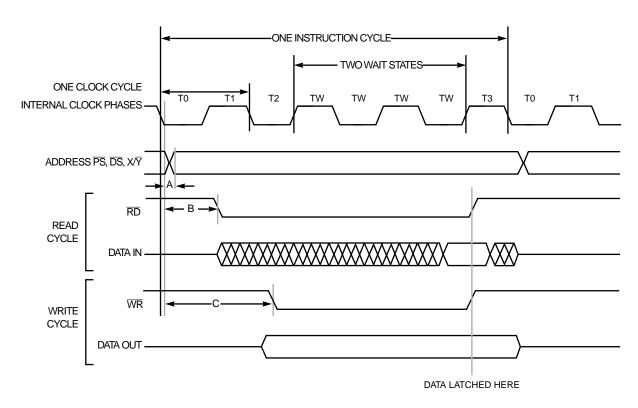

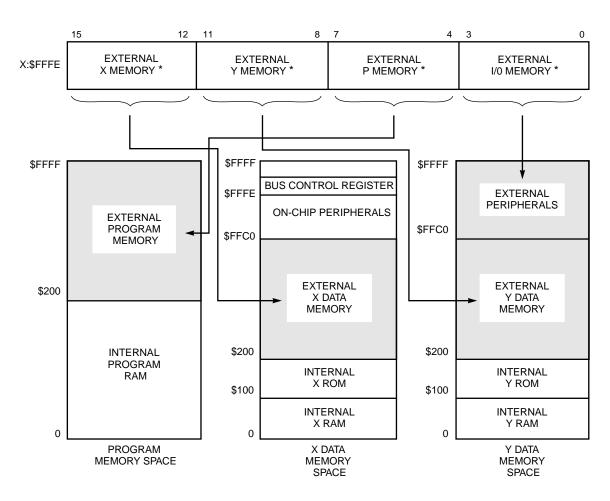

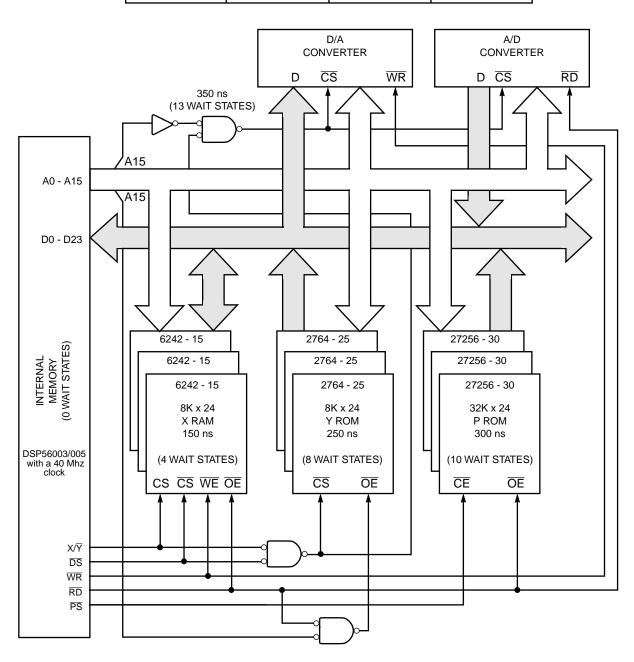

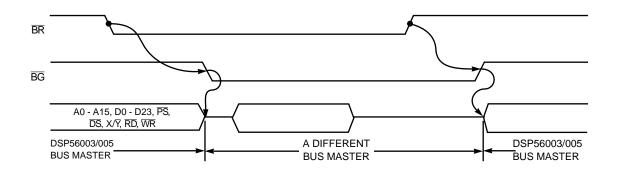

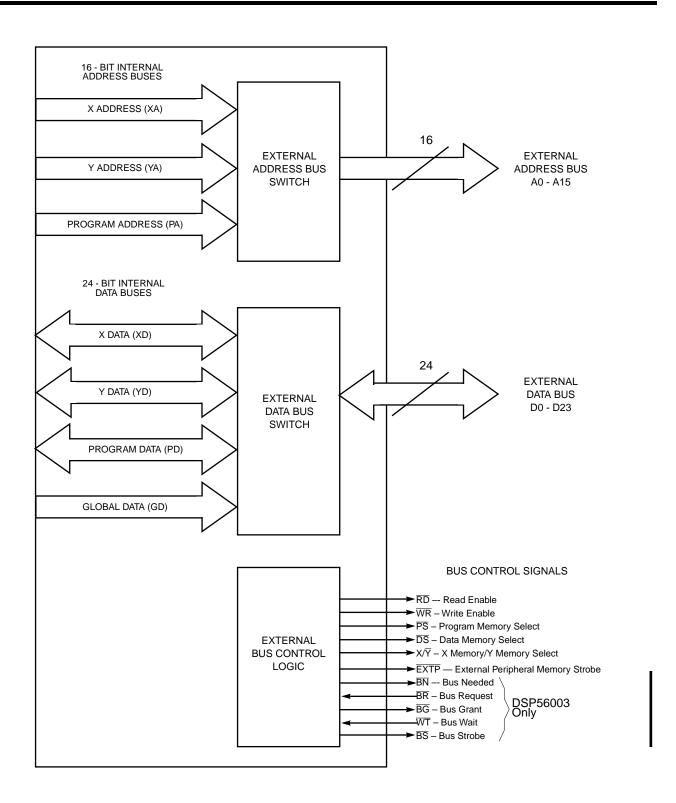

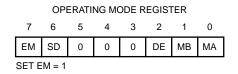

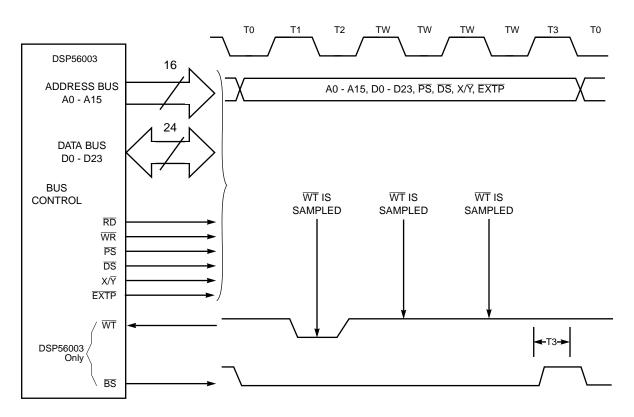

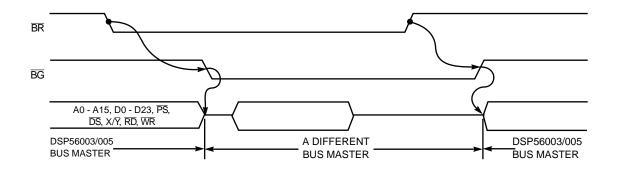

| 4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-8<br>4-9<br>4-10<br>4-11<br>4-12 | External Memory Interface Signals  External Program Space  External X and Y Data Space  Memory Segmentation  External Memory Interface Bootstrap ROM with X and Y RAM  External Memory Interface Bus Operation with No Wait States  External Memory Interface Bus Operation with Two Wait States  External Memory Interface Bus Operation with Two Wait States  Bus Control Register  Mixed-Speed Expanded System  Bus Strobe/Wait Sequence — DSP56003 Only  Bus Request/Bus Grant Sequence — DSP56003 Only  Bus Arbitration Using Only BR and BG with Internal Control —  DSP56003 Only | 4-5<br>4-6<br>4-7<br>4-8<br>4-9<br>4-10<br>4-13<br>4-14<br>4-15<br>4-17 |

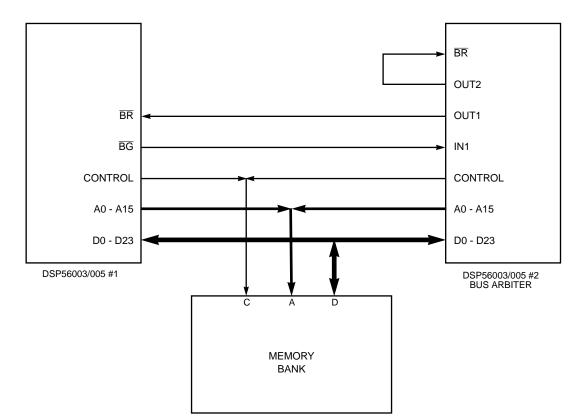

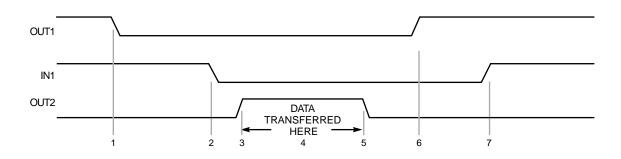

| 4-13<br>4-14                                                                        | Two DSPs with External Bus Arbitration Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-19                                                                    |

| 4-15<br>4-16<br>4-17                                                                | Bus Arbitration Using BR and BG, and WT and BS with No Overhead — DSP56003 Only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-21<br>4-22                                                            |

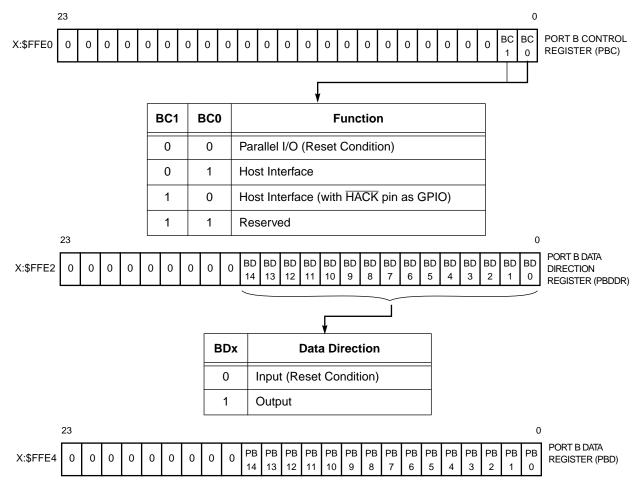

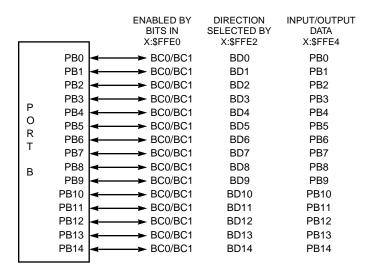

| 5-1<br>5-2<br>5-3                                                                   | Port B Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5-4                                                                     |

|                          | List of Figures (Continued)                          |                |

|--------------------------|------------------------------------------------------|----------------|

| Figure Number            |                                                      | Page<br>Number |

| Numb                     | er ritie                                             | Numbe          |

| - 4                      |                                                      | - 0            |

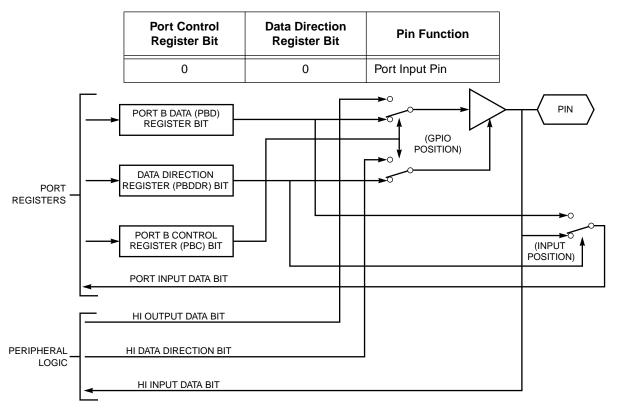

| 5-4                      | Port B I/O Pin Control Logic                         |                |

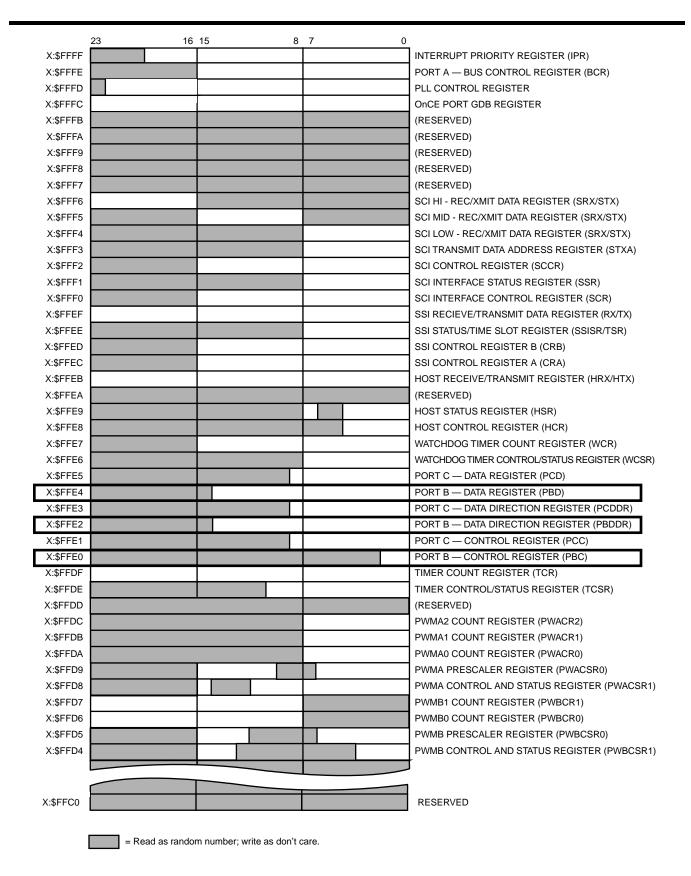

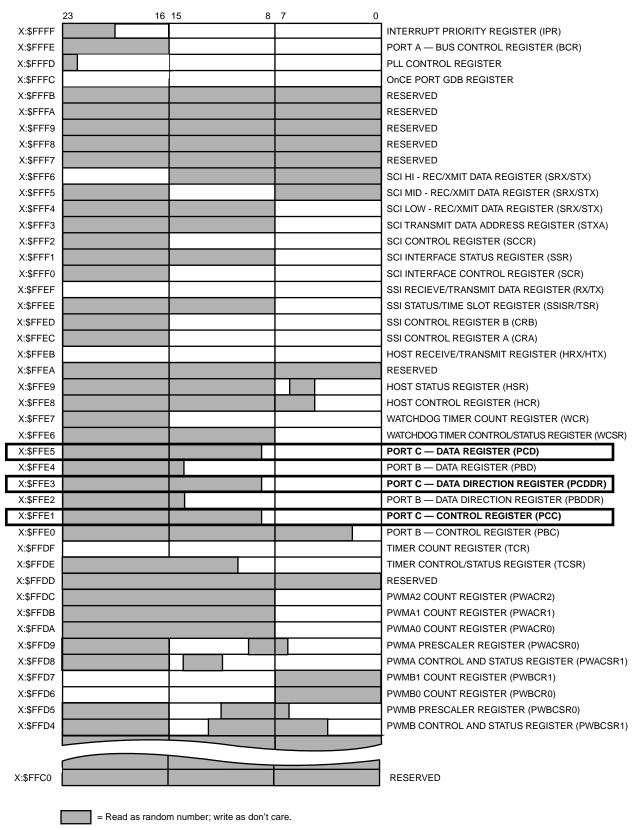

| 5-5                      | On-Chip Peripheral Memory Map                        |                |

| 5-6                      | Instructions to Write/Read Parallel Data with Port B |                |

| 5-7                      | I/O Port B Configuration                             |                |

| 5-8                      | HI Block Diagram                                     |                |

| 5-9                      | Host Interface Programming Model — DSP Viewpoint     |                |

| 5-10                     | Host Flag Operation                                  |                |

| 5-11                     | HSR–HCR Operation                                    |                |

| 5-12                     | Host Processor Programming Model — Host Side         |                |

| 5-13                     | HI Register Map                                      |                |

| 5-14                     | Command Vector Register                              |                |

| 5-15                     | Host Processor Transfer Timing                       |                |

| 5-16                     | Interrupt Vector Register Read Timing                |                |

| 5-17                     | HI Interrupt Structure                               |                |

| 5-18                     | DMA Transfer Logic and Timing                        |                |

| 5-19<br>5-20             | HI Initialization Flowchart                          |                |

| 5-20                     | HI Initialization — DSP Side                         |                |

|                          | HI Configuration — Host Side                         |                |

|                          | HI Initialization — Host Side, Polling Mode          |                |

|                          | HI Initialization — Host Side, Interrupt Mode        |                |

|                          | HI Initialization — Host Side, DMA Mode              |                |

| 5-22<br>5-23             | Host Mode and INIT Bits                              |                |

| 5-23<br>5-24             | Bits Used for Host-to-DSP Transfer                   |                |

| 5-2 <del>4</del><br>5-25 |                                                      |                |

| 5-25<br>5-26             | Receive Data from Host — Main Program                |                |

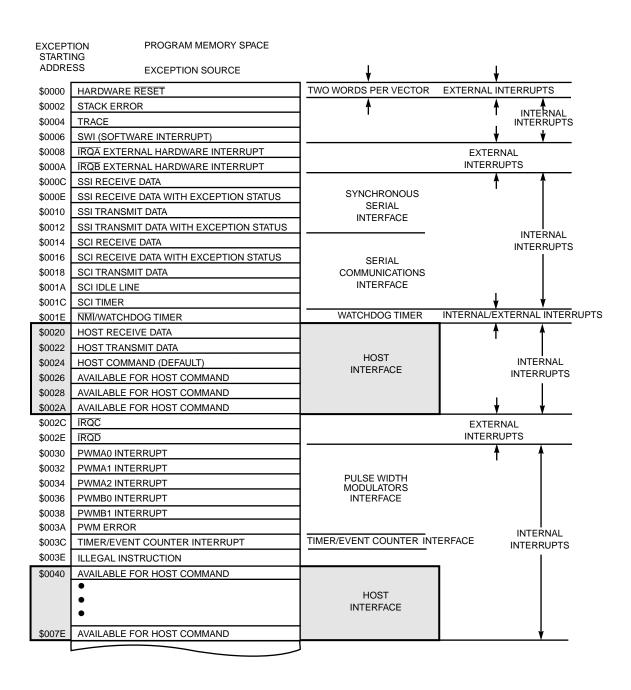

| 5-26<br>5-27             | HI Exception Vector Locations                        |                |

| 5-27<br>5-28             | Host Command                                         |                |

| 5-28<br>5-29             | Bootstrap Using the HI                               |                |

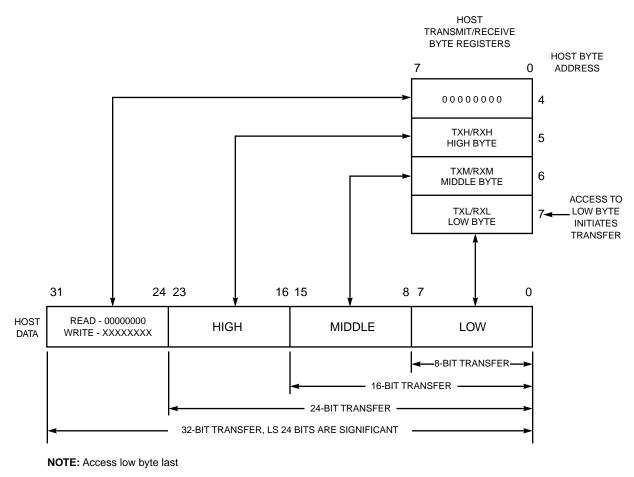

| 5-29<br>5-30             | Transmit/Receive Byte Registers                      |                |

| 5-30<br>5-31             | Bootstrap Code Fragment                              |                |

| 5-32                     | Bits Used for DSP to Host Transfer                   |                |

| 5-32<br>5-33             | Data Transfer from DSP to Host                       |                |

| 5-34                     | Main Program — Transmit 24-Bit Data to Host          |                |

| 5-3 <del>4</del><br>5-35 | Transmit to HI Routine                               |                |

| 5-36                     | HI Hardware — DMA Mode                               |                |

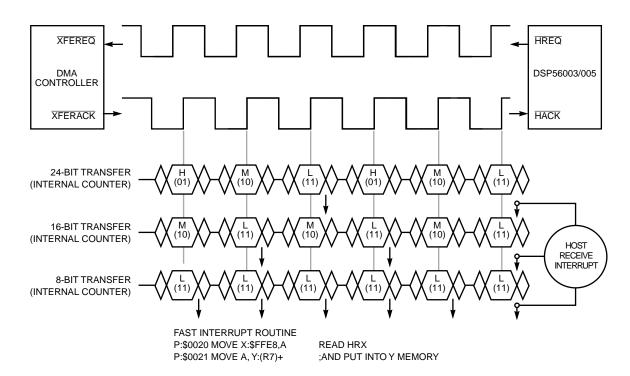

| 5-30<br>5-37             | DMA Transfer and Host Interrupts                     |                |

| 5-37<br>5-38             | Host-to-DSP DMA Procedure                            |                |

| 5-39                     | Host Bits with TREQ and RREQ                         |                |

| 5-40                     | DSP to Host DMA Procedure                            |                |

| J 70                     | DOI TO HOOF DIWING HOOGGID                           |                |

| List of Figures (Continued) |                                                           |        |  |

|-----------------------------|-----------------------------------------------------------|--------|--|

| Figu                        |                                                           | Page   |  |

| Num                         | ber Title                                                 | Number |  |

|                             |                                                           |        |  |

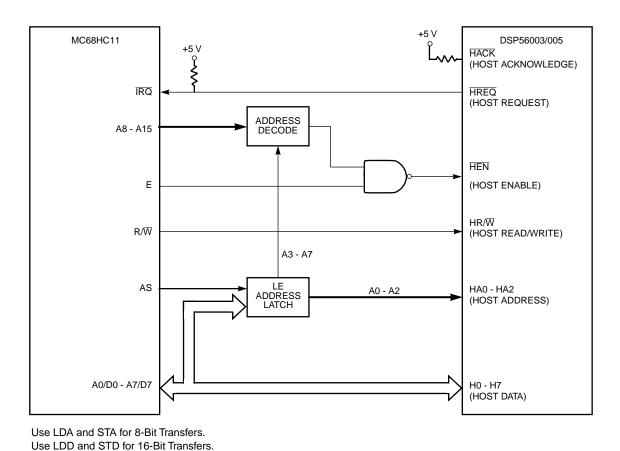

| 5-41                        | MC68HC11 to DSP56003/005 Host Interface                   |        |  |