## DSP56800

Family Manual

16-Bit Digital Signal Controllers

DSP56800FM Rev. 3.1 11/2005

freescale.com

## **Contents**

# **Chapter 1** Introduction

| 1.1   | DSP56800 Family Architecture               | . 1-1 |

|-------|--------------------------------------------|-------|

|       | Core Overview                              |       |

| 1.1.2 | Peripheral Blocks                          | . 1-3 |

| 1.1.3 | Family Members                             | . 1-5 |

| 1.2   | Introduction to Digital Signal Processing. | . 1-5 |

| 1.3   | Summary of Features                        | . 1-9 |

| 1.4   | For the Latest Information                 | 1-10  |

# **Chapter 2** Core Architecture Overview

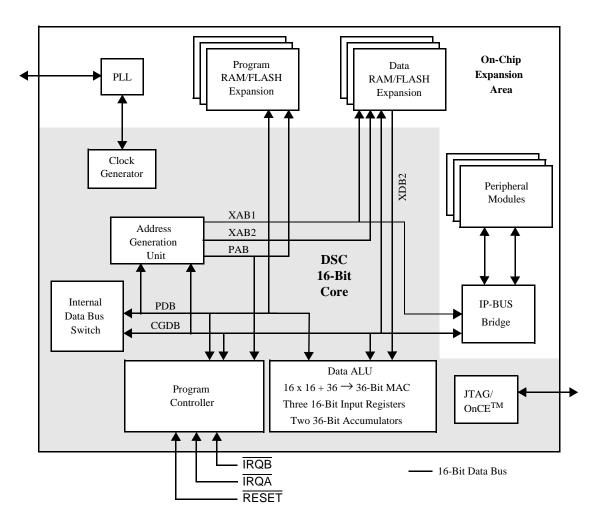

| Core Block Diagram                           | 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

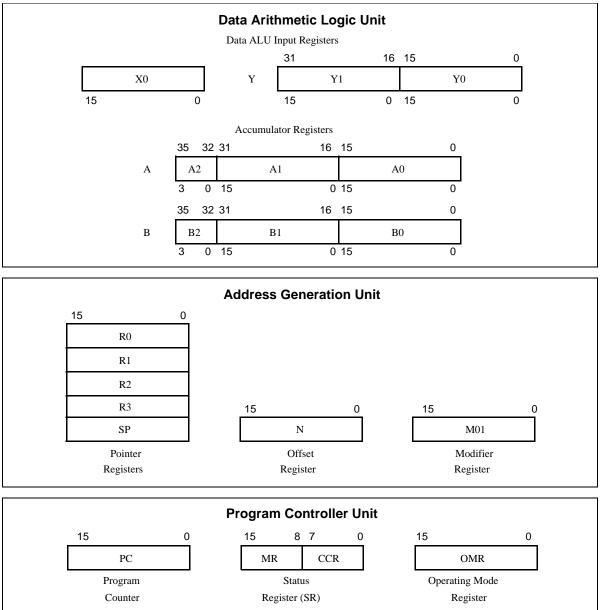

| Data Arithmetic Logic Unit (ALU)             | 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

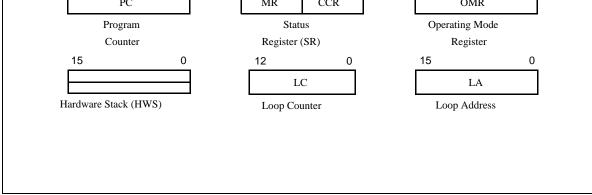

| Address Generation Unit (AGU)                | 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

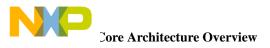

| Program Controller and Hardware Looping Unit | 2-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Bus and Bit-Manipulation Unit.               | 2-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| On-Chip Emulation (OnCE) Unit                | 2-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Address Buses                                | 2-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Data Buses                                   | 2-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Memory Architecture                          | 2-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Blocks Outside the DSP56800 Core             | 2-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| External Data Memory                         | 2-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Program Memory                               | 2-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Bootstrap Memory                             | 2-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| IP-BUS Bridge                                | 2-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Phase Lock Loop (PLL)                        | 2-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DSP56800 Core Programming Model              | 2-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                              | Core Block Diagram.<br>Data Arithmetic Logic Unit (ALU)<br>Address Generation Unit (AGU)<br>Program Controller and Hardware Looping Unit.<br>Bus and Bit-Manipulation Unit.<br>On-Chip Emulation (OnCE) Unit.<br>Address Buses.<br>Data Buses<br>Data Buses<br>Memory Architecture<br>Blocks Outside the DSP56800 Core<br>External Data Memory<br>Program Memory<br>Bootstrap Memory<br>IP-BUS Bridge<br>Phase Lock Loop (PLL).<br>DSP56800 Core Programming Model |

# **Chapter 3** Data Arithmetic Logic Unit

| 3.1   | Overview and Architecture                 | 3-2 |

|-------|-------------------------------------------|-----|

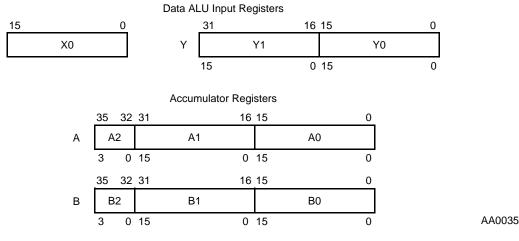

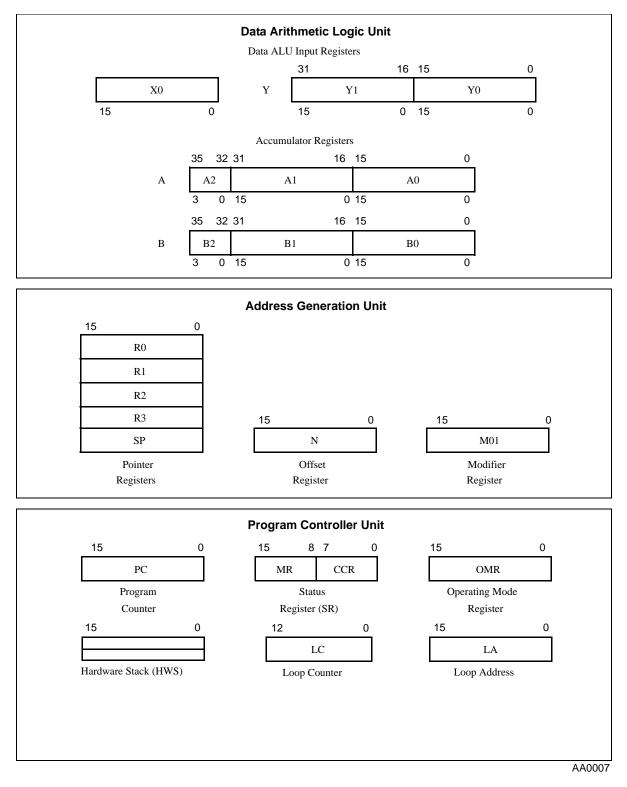

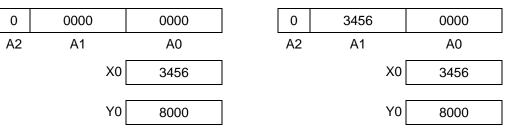

| 3.1.1 | Data ALU Input Registers (X0, Y1, and Y0) | 3-4 |

| 3.1.2 | Data ALU Accumulator Registers            | 3-4 |

| 3.1.3 | Multiply-Accumulator (MAC) and Logic Unit | 3-5 |

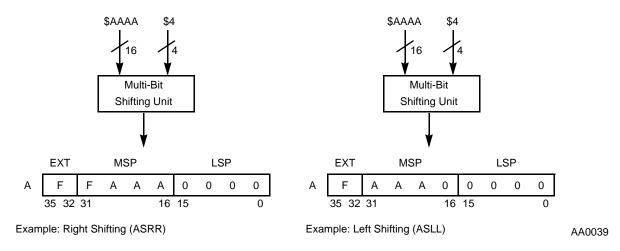

| 3.1.4 | Barrel Shifter.                           | 3-5 |

| 3.1.5 | Accumulator Shifter                       |     |

| 3.1.6 | Data Limiter and MAC Output Limiter       | 3-6 |

| 3.2     | Accessing the Accumulator Registers                     |  |

|---------|---------------------------------------------------------|--|

| 3.2.1   | Accessing an Accumulator by Its Individual Portions     |  |

| 3.2.2   | Accessing an Entire Accumulator.                        |  |

| 3.2.2.1 | Accessing for Data ALU Operations                       |  |

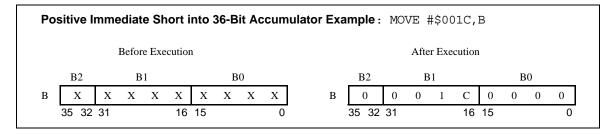

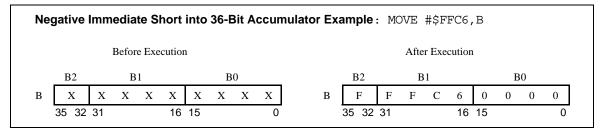

| 3.2.2.2 | Writing an Accumulator with a Small Operand             |  |

| 3.2.2.3 | Extension Registers as Protection Against Overflow      |  |

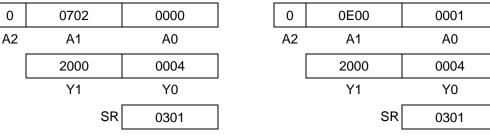

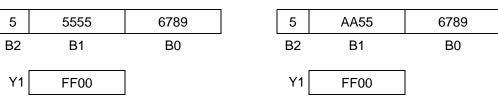

| 3.2.2.4 | Examples of Writing the Entire Accumulator              |  |

| 3.2.3   | General Integer Processing                              |  |

| 3.2.3.1 | Writing Integer Data to an Accumulator                  |  |

| 3.2.3.2 | Reading Integer Data from an Accumulator                |  |

| 3.2.4   | Using 16-Bit Results of DSC Algorithms.                 |  |

| 3.2.5   | Saving and Restoring Accumulators                       |  |

| 3.2.6   | Bit-Field Operations on Integers in Accumulators        |  |

| 3.2.7   | Converting from 36-Bit Accumulator to 16-Bit Portion    |  |

| 3.3     | Fractional and Integer Data ALU Arithmetic              |  |

| 3.3.1   | Interpreting Data                                       |  |

| 3.3.2   | Data Formats                                            |  |

| 3.3.2.1 | Signed Fractional                                       |  |

| 3.3.2.2 | Unsigned Fractional                                     |  |

| 3.3.2.3 | Signed Integer                                          |  |

| 3.3.2.4 | Unsigned Integer                                        |  |

| 3.3.3   | Addition and Subtraction                                |  |

| 3.3.4   | Logical Operations                                      |  |

| 3.3.5   | Multiplication                                          |  |

| 3.3.5.1 |                                                         |  |

| 3.3.5.2 | Integer Multiplication                                  |  |

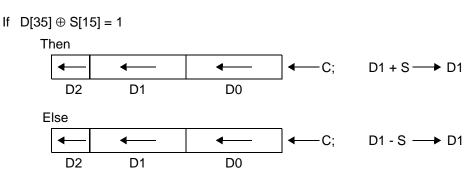

| 3.3.6   | Division                                                |  |

| 3.3.7   | Unsigned Arithmetic                                     |  |

| 3.3.7.1 | Conditional Branch Instructions for Unsigned Operations |  |

| 3.3.7.2 | Unsigned Multiplication                                 |  |

| 3.3.8   | Multi-Precision Operations.                             |  |

| 3.3.8.1 | Multi-Precision Addition and Subtraction                |  |

| 3.3.8.2 | Multi-Precision Multiplication                          |  |

| 3.4     | Saturation and Data Limiting                            |  |

| 3.4.1   | Data Limiter                                            |  |

| 3.4.2   | MAC Output Limiter                                      |  |

| 3.4.3   | Instructions Not Affected by the MAC Output Limiter     |  |

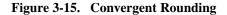

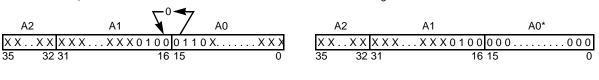

| 3.5     | Rounding                                                |  |

| 3.5.1   | Convergent Rounding                                     |  |

| 3.5.2   | Two's-Complement Rounding                               |  |

| 3.6     | Condition Code Generation                               |  |

| 3.6.1   | 36-Bit Destinations — CC Bit Cleared                    |  |

| 3.6.2   | 36-Bit Destinations — CC Bit Set                        |  |

| 3.6.3   | 20-Bit Destinations — CC Bit Cleared                    |  |

| 3.6.4   | 20-Bit Destinations — CC Bit Set                        |  |

| 3.6.5   | 16-Bit Destinations                                     |  |

| 3.6.6   | Special Instruction Types                               |  |

| 3.6.7 | TST and TSTW Instructions |      |

|-------|---------------------------|------|

| 3.6.8 | Unsigned Arithmetic       | 3-36 |

# **Chapter 4** Address Generation Unit

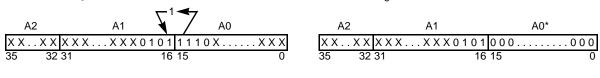

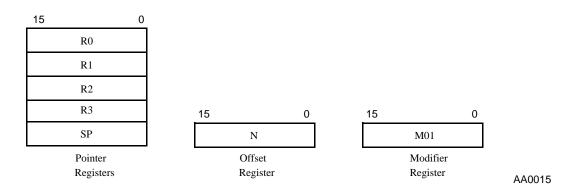

| 4.1     | Architecture and Programming Model               | 4-2  |

|---------|--------------------------------------------------|------|

| 4.1.1   | Address Registers (R0-R3)                        | 4-4  |

| 4.1.2   | Stack Pointer Register (SP)                      | 4-4  |

| 4.1.3   | Offset Register (N)                              | 4-4  |

| 4.1.4   | Modifier Register (M01)                          | 4-5  |

| 4.1.5   | Modulo Arithmetic Unit                           | 4-5  |

| 4.1.6   | Incrementer/Decrementer Unit                     | 4-5  |

| 4.2     | Addressing Modes                                 | 4-6  |

| 4.2.1   | Register-Direct Modes                            | 4-7  |

| 4.2.1.1 | Data or Control Register Direct                  | 4-7  |

| 4.2.1.2 | Address Register Direct                          | 4-7  |

| 4.2.2   | Address-Register-Indirect Modes                  | 4-7  |

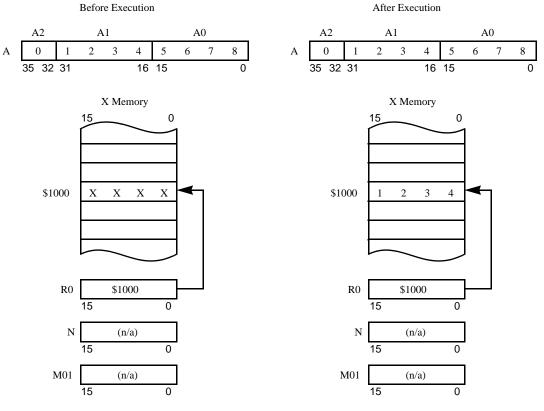

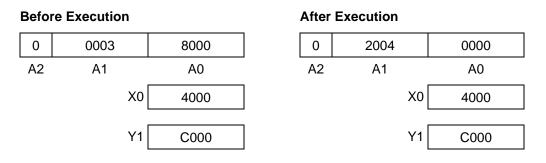

| 4.2.2.1 | No Update: (Rj), (SP)                            | 4-9  |

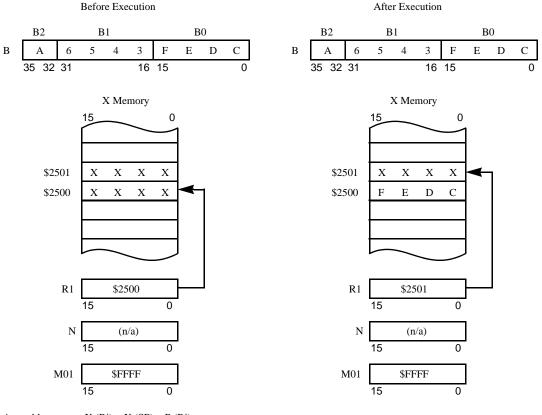

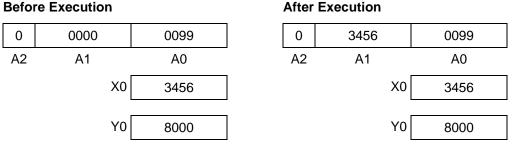

| 4.2.2.2 | Post-Increment by 1: (Rj)+, (SP)+                | 4-11 |

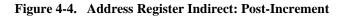

| 4.2.2.3 | Post-Decrement by 1: (Rn)-, (SP)                 | 4-12 |

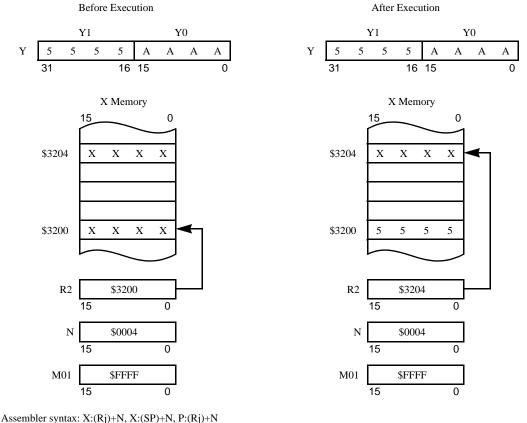

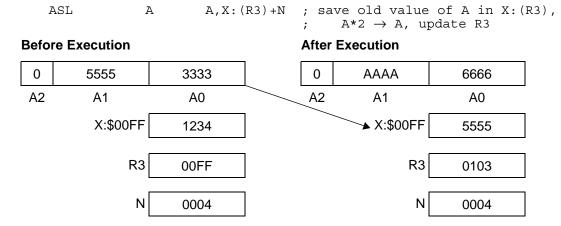

| 4.2.2.4 | Post-Update by Offset N: (Rj)+N, (SP)+N          | 4-13 |

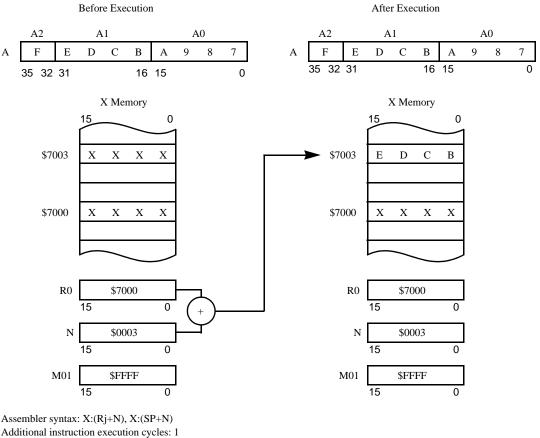

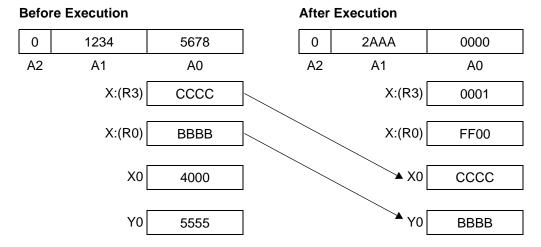

| 4.2.2.5 | Index by Offset N: (Rj+N), (SP+N)                | 4-14 |

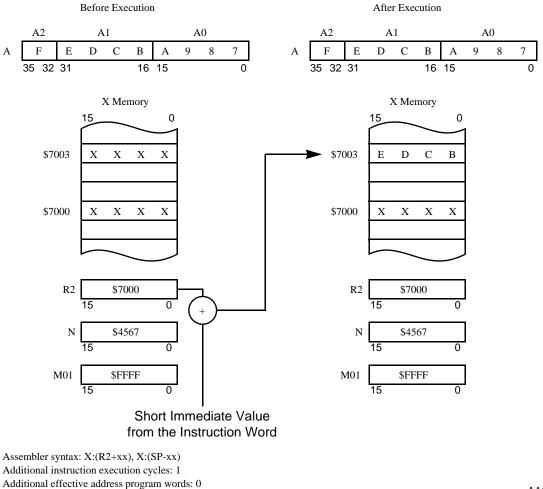

| 4.2.2.6 | Index by Short Displacement: (SP-xx), (R2+xx)    | 4-15 |

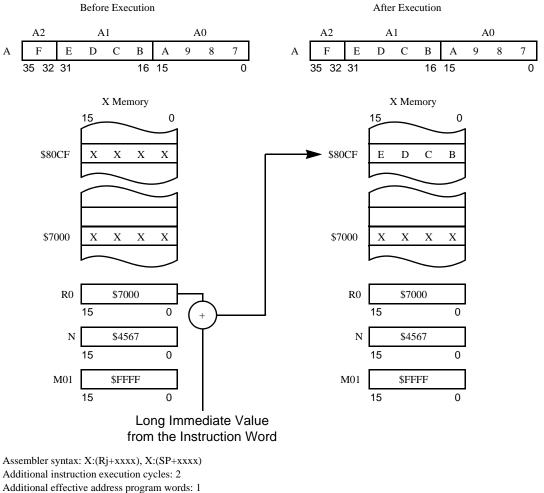

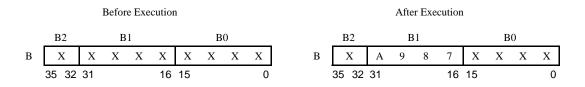

| 4.2.2.7 | Index by Long Displacement: (Rj+xxxx), (SP+xxxx) | 4-16 |

| 4.2.3   | Immediate Data Modes                             | 4-17 |

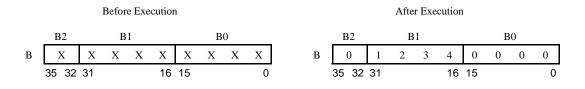

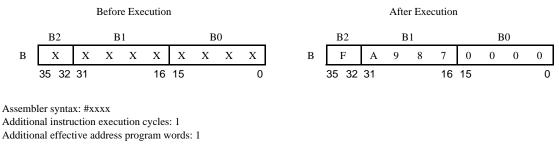

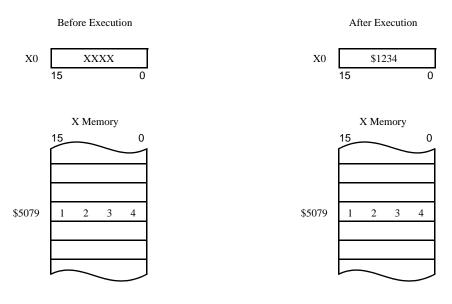

| 4.2.3.1 | Immediate Data: #xxxx                            | 4-18 |

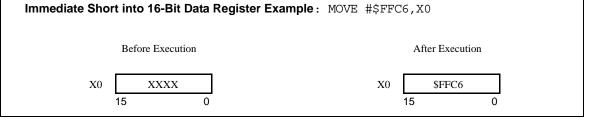

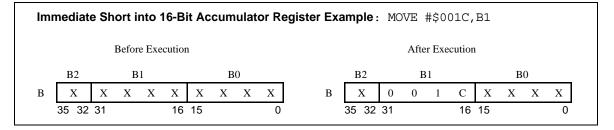

| 4.2.3.2 | Immediate Short Data: #xx                        | 4-20 |

| 4.2.4   | Absolute Addressing Modes                        | 4-20 |

| 4.2.4.1 | Absolute Address (Extended Addressing): xxxx     | 4-21 |

| 4.2.4.2 | (                                                |      |

| 4.2.4.3 | I/O Short Address (Direct Addressing): <pp></pp> | 4-23 |

| 4.2.5   | Implicit Reference.                              | 4-23 |

| 4.2.6   | Addressing Modes Summary                         | 4-23 |

| 4.3     | AGU Address Arithmetic                           | 4-25 |

| 4.3.1   | Linear Arithmetic                                | 4-25 |

| 4.3.2   | Modulo Arithmetic                                | 4-25 |

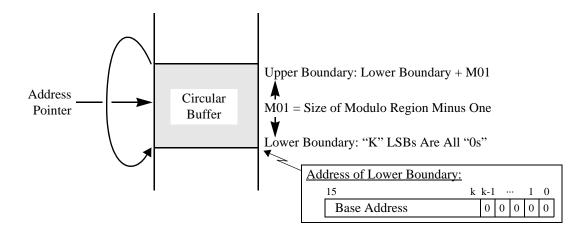

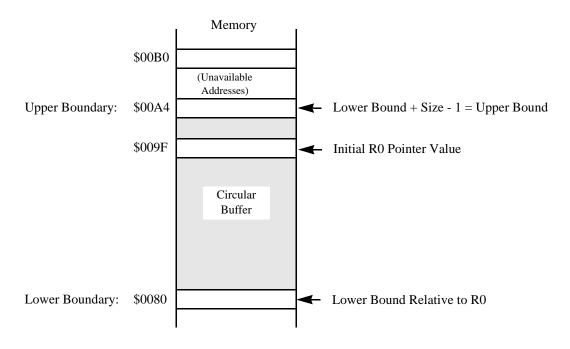

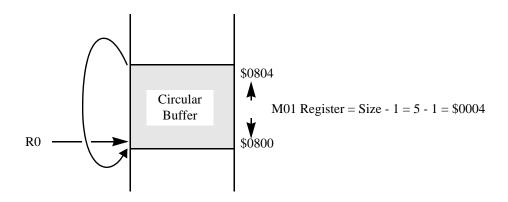

| 4.3.2.1 | Modulo Arithmetic Overview                       | 4-25 |

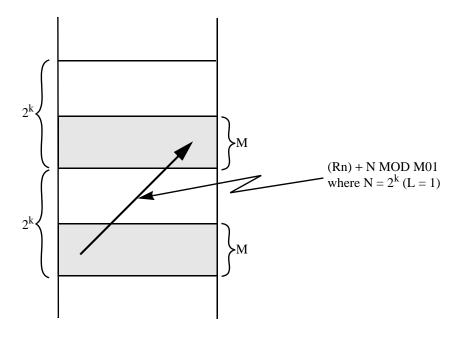

| 4.3.2.2 | Configuring Modulo Arithmetic                    | 4-27 |

| 4.3.2.3 | Supported Memory Access Instructions             | 4-29 |

| 4.3.2.4 | Simple Circular Buffer Example                   | 4-29 |

| 4.3.2.5 | Setting Up a Modulo Buffer                       | 4-30 |

| 4.3.2.6 |                                                  |      |

| 4.3.2.7 | Side Effects of Modulo Arithmetic                | 4-32 |

| 4.3.2.7 |                                                  |      |

| 4.3.2.7 | 0                                                |      |

| 4.3.2.7 | ······································           |      |

| 4.4     | Pipeline Dependencies                            | 4-33 |

# **Chapter 5 Program Controller**

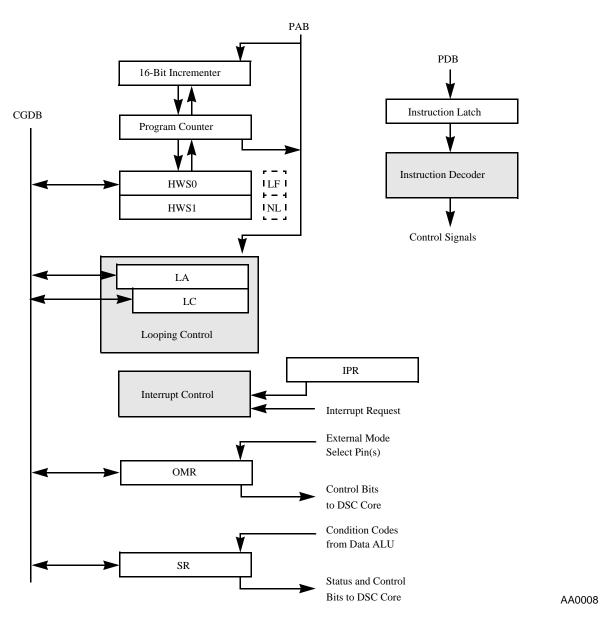

| 5.1     | Architecture and Programming Model         | 5-1 |

|---------|--------------------------------------------|-----|

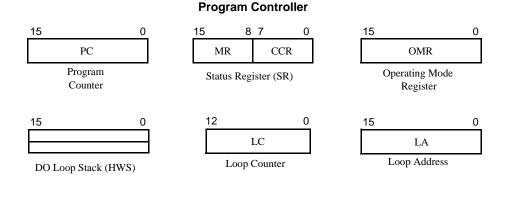

| 5.1.1   | Program Counter.                           | 5-3 |

| 5.1.2   | Instruction Latch and Instruction Decoder  | 5-3 |

| 5.1.3   | Interrupt Control Unit                     | 5-3 |

| 5.1.4   | Looping Control Unit                       | 5-4 |

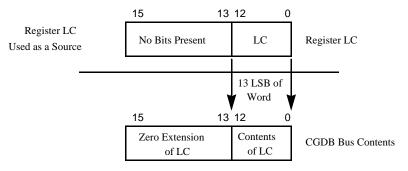

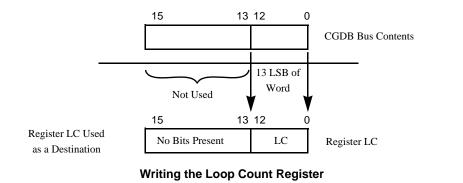

| 5.1.5   | Loop Counter                               | 5-4 |

| 5.1.6   | Loop Address                               | 5-5 |

| 5.1.7   | Hardware Stack                             | 5-6 |

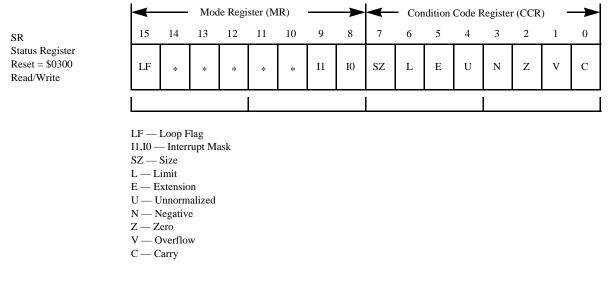

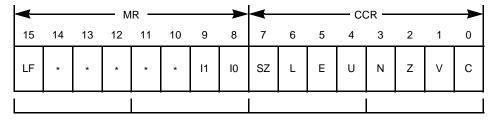

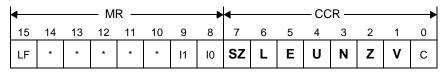

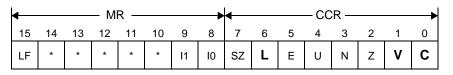

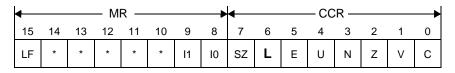

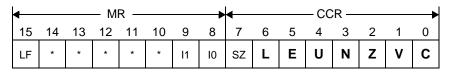

| 5.1.8   | Status Register                            | 5-6 |

| 5.1.8.1 | Carry (C) — Bit 0                          | 5-7 |

| 5.1.8.2 | Overflow (V) — Bit 1                       | 5-7 |

| 5.1.8.3 |                                            |     |

| 5.1.8.4 | Negative (N) — Bit 3                       | 5-7 |

| 5.1.8.5 | Unnormalized (U) — Bit 4                   | 5-8 |

| 5.1.8.6 | Extension (E) — Bit 5                      | 5-8 |

| 5.1.8.7 | Limit (L) — Bit 6                          | 5-8 |

| 5.1.8.8 | Size (SZ) — Bit 7                          | 5-8 |

| 5.1.8.9 |                                            |     |

| 5.1.8.1 |                                            |     |

| 5.1.8.1 | 1 Loop Flag (LF) — Bit 15                  | 5-9 |

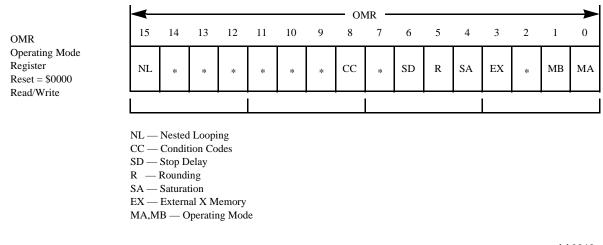

| 5.1.9   | Operating Mode Register                    | -10 |

| 5.1.9.1 | Operating Mode Bits (MB and MA) — Bits 1–0 | -10 |

| 5.1.9.2 | External X Memory Bit (EX) — Bit 3         | -11 |

| 5.1.9.3 | Saturation (SA) — Bit 4                    | -11 |

| 5.1.9.4 | Rounding Bit (R) — Bit 5                   | -12 |

| 5.1.9.5 | Stop Delay Bit (SD) — Bit 6                | -12 |

| 5.1.9.6 |                                            |     |

| 5.1.9.7 | Nested Looping Bit (NL) — Bit 15           | -13 |

| 5.1.9.8 | Reserved OMR Bits — Bits 2, 7 and 9–145    | -13 |

| 5.2     | Software Stack Operation                   | -13 |

| 5.3     | Program Looping                            | -14 |

| 5.3.1   | Repeat (REP) Looping                       | -14 |

| 5.3.2   | DO Looping                                 | -15 |

| 5.3.3   | Nested Hardware DO and REP Looping5        | -15 |

| 5.3.4   | Terminating a DO Loop                      | -16 |

# **Chapter 6** Instruction Set Introduction

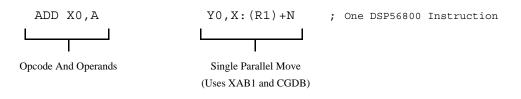

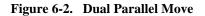

| 6.1   | Introduction to Moves and Parallel Moves | 6-1 |

|-------|------------------------------------------|-----|

| 6.2   | Instruction Formats                      | 6-3 |

| 6.3   | Programming Model                        | 6-5 |

| 6.4   | Instruction Groups                       | 6-6 |

|       | Arithmetic Instructions                  |     |

| 6.4.2 | Logical Instructions                     | 6-7 |

| 6.4.3 | Bit-Manipulation Instructions        |      |

|-------|--------------------------------------|------|

| 6.4.4 | Looping Instructions                 |      |

| 6.4.5 | Move Instructions                    |      |

| 6.4.6 | Program Control Instructions         |      |

| 6.5   | Instruction Aliases                  |      |

| 6.5.1 | ANDC, EORC, ORC, and NOTC Aliases    |      |

| 6.5.2 | LSLL Alias                           |      |

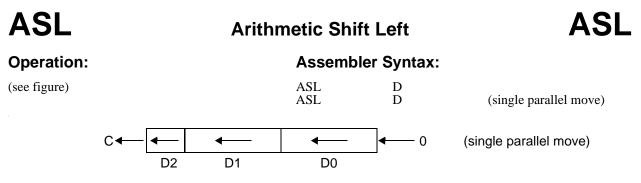

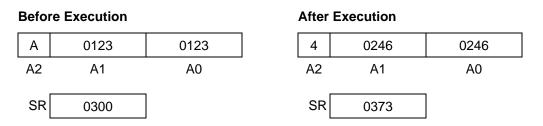

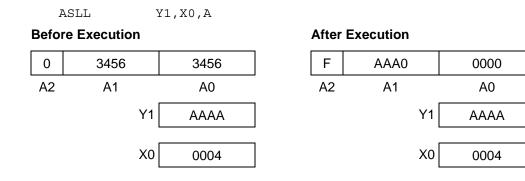

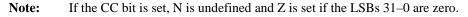

| 6.5.3 | ASL Alias                            | 6-12 |

| 6.5.4 | CLR Alias                            |      |

| 6.5.5 | POP Alias                            |      |

| 6.6   | DSP56800 Instruction Set Summary     |      |

| 6.6.1 | Register Field Notation.             | 6-14 |

| 6.6.2 | Immediate Value Notation             |      |

| 6.6.3 | Using the Instruction Summary Tables |      |

| 6.6.4 | Instruction Summary Tables           |      |

| 6.7   | The Instruction Pipeline             |      |

| 6.7.1 | Instruction Processing.              | 6-30 |

| 6.7.2 | Memory Access Processing             | 6-31 |

# **Chapter 7** Interrupts and the Processing States

| 7.1     | Reset Processing State                               | .7-1 |

|---------|------------------------------------------------------|------|

| 7.2     | Normal Processing State                              |      |

| 7.2.1   | Instruction Pipeline Description                     |      |

| 7.2.2   | Instruction Pipeline with Off-Chip Memory Accesses   | .7-3 |

| 7.2.3   | Instruction Pipeline Dependencies and Interlocks     |      |

| 7.3     | Exception Processing State                           |      |

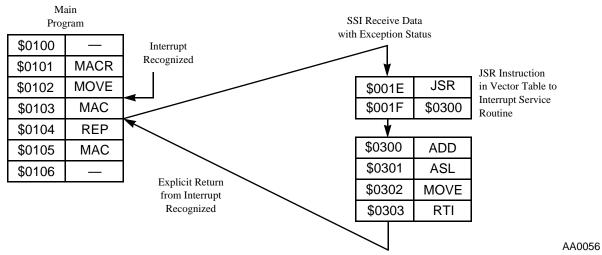

| 7.3.1   | Sequence of Events in the Exception Processing State |      |

| 7.3.2   | Reset and Interrupt Vector Table                     |      |

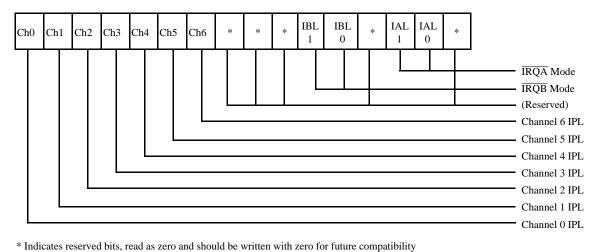

| 7.3.3   | Interrupt Priority Structure                         |      |

| 7.3.4   | Configuring Interrupt Sources                        |      |

| 7.3.5   | Interrupt Sources.                                   |      |

| 7.3.5.1 | External Hardware Interrupt Sources                  |      |

| 7.3.5.2 | -                                                    |      |

| 7.3.5.3 | -                                                    |      |

| 7.3.6   | Interrupt Arbitration                                |      |

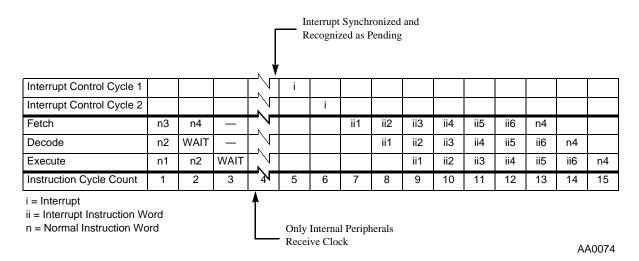

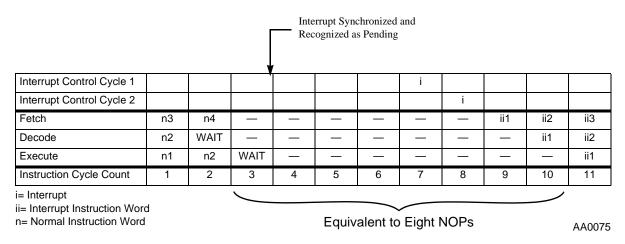

| 7.3.7   | The Interrupt Pipeline                               | /-14 |

| 7.3.8   | Interrupt Latency                                    |      |

| 7.4     | Wait Processing State                                |      |

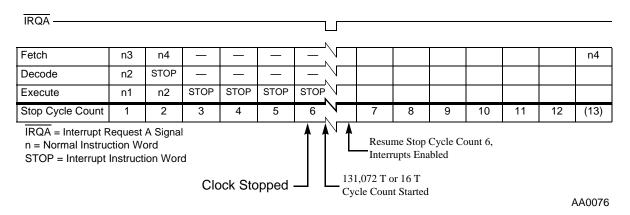

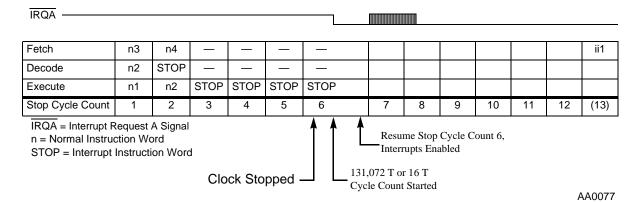

| 7.5     | Stop Processing State                                |      |

| 7.6     | Debug Processing State                               |      |

# **Chapter 8** Software Techniques

| 8.1   | Useful Instruction Operations | 8-1 |

|-------|-------------------------------|-----|

| 8.1.1 | Jumps and Branches            | 8-2 |

| 8.1.1.1 | JRSET and JRCLR Operations                        |  |

|---------|---------------------------------------------------|--|

| 8.1.1.2 | BR1SET and BR1CLR Operations                      |  |

| 8.1.1.3 | JR1SET and JR1CLR Operations                      |  |

| 8.1.1.4 | =                                                 |  |

| 8.1.1.5 | Other Jumps and Branches on Condition Codes       |  |

| 8.1.2   | Negation Operations                               |  |

| 8.1.2.1 | NEGW Operation                                    |  |

| 8.1.2.2 | -                                                 |  |

| 8.1.2.3 |                                                   |  |

| 8.1.2.4 |                                                   |  |

| 8.1.3   | Register Exchanges                                |  |

| 8.1.4   | Minimum and Maximum Values                        |  |

| 8.1.4.1 | MAX Operation                                     |  |

| 8.1.4.2 |                                                   |  |

| 8.1.5   | Accumulator Sign Extend.                          |  |

| 8.1.6   | Unsigned Load of an Accumulator                   |  |

| 8.2     | 16- and 32-Bit Shift Operations                   |  |

| 8.2.1   | Small Immediate 16- or 32-Bit Shifts.             |  |

| 8.2.2   | General 16-Bit Shifts                             |  |

| 8.2.3   | General 32-Bit Arithmetic Right Shifts            |  |

| 8.2.4   | General 32-Bit Logical Right Shifts               |  |

| 8.2.5   | Arithmetic Shifts by a Fixed Amount.              |  |

| 8.2.5.1 | Right Shifts (ASR12–ASR20)                        |  |

| 8.2.5.2 | <b>e</b>                                          |  |

| 8.3     | Incrementing and Decrementing Operations          |  |

| 8.4     | Division.                                         |  |

| 8.4.1   | Positive Dividend and Divisor with Remainder      |  |

| 8.4.2   | Signed Dividend and Divisor with No Remainder     |  |

| 8.4.3   | Signed Dividend and Divisor with Remainder        |  |

| 8.4.4   | Algorithm Examples                                |  |

| 8.4.5   | Overflow Cases.                                   |  |

| 8.5     | Multiple Value Pushes                             |  |

| 8.6     | Loops                                             |  |

| 8.6.1   | Large Loops (Count Greater Than 63)               |  |

| 8.6.2   | Variable Count Loops                              |  |

| 8.6.3   | Software Loops                                    |  |

| 8.6.4   | Nested Loops                                      |  |

| 8.6.4.1 | Recommendations                                   |  |

| 8.6.4.2 |                                                   |  |

| 8.6.4.3 | L                                                 |  |

| 8.6.5   | Hardware DO Looping in Interrupt Service Routines |  |

| 8.6.6   | Early Termination of a DO Loop                    |  |

| 8.7     | Array Indexes                                     |  |

| 8.7.1   | Global or Fixed Array with a Constant.            |  |

| 8.7.2   | Global or Fixed Array with a Variable             |  |

| 8.7.3   | Local Array with a Constant.                      |  |

| 8.7.4   | Local Array with a Variable                       |  |

|         |                                                   |  |

# Chapter 9 JTAG and On-Chip Emulation (OnCE™)

| 9.1     | Combined JTAG and OnCE Interface9-1 |

|---------|-------------------------------------|

| 9.2     | JTAG Port                           |

| 9.2.1   | JTAG Capabilities                   |

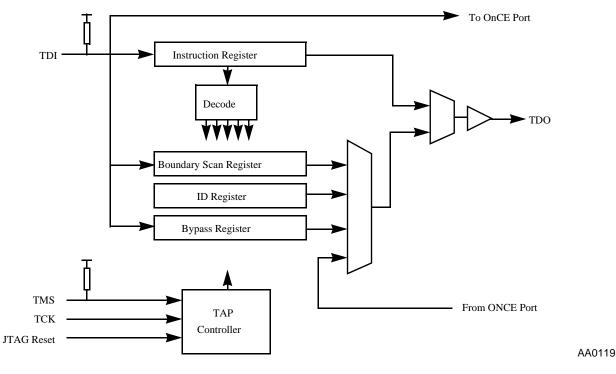

| 9.2.2   | JTAG Port Architecture              |

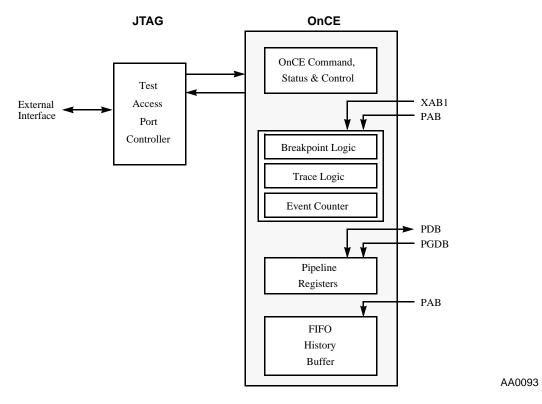

| 9.3     | OnCE Port                           |

| 9.3.1   | OnCE Port Capabilities              |

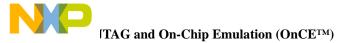

| 9.3.2   | OnCE Port Architecture              |

| 9.3.2.1 | Command, Status, and Control        |

| 9.3.2.2 | Breakpoint and Trace                |

| 9.3.2.3 | Pipeline Save and Restore           |

| 9.3.2.4 | FIFO History Buffer                 |

|         |                                     |

# **Appendix A** Instruction Set Details

| A.1     | Notation A-1                                         |

|---------|------------------------------------------------------|

| A.2     | Programming Model                                    |

| A.3     | Addressing Modes A-6                                 |

| A.4     | Condition Code Computation                           |

| A.4.1   | The Condition Code Bits A-7                          |

| A.4.1.1 | Size (SZ) — Bit 7                                    |

| A.4.1.2 | Limit (L) — Bit 6                                    |

| A.4.1.3 | Extension in Use (E) — Bit 5                         |

| A.4.1.4 | Unnormalized (U) — Bit 4 A-9                         |

| A.4.1.5 | Negative (N) — Bit 3                                 |

| A.4.1.6 | 5 Zero (Z) — Bit 2 A-10                              |

| A.4.1.7 | V Overflow (V) — Bit 1 A-10                          |

| A.4.1.8 | Carry (C) — Bit 0 A-10                               |

| A.4.2   | Effects of the Operating Mode Register's SA Bit A-11 |

|         |                                                      |

| A.4.3 | Effects of the OMR's CC Bit A-11           |

|-------|--------------------------------------------|

| A.4.4 | Condition Code Summary by Instruction A-12 |

| A.5   | Instruction Timing A-16                    |

| A.6   | Instruction Set Restrictions A-26          |

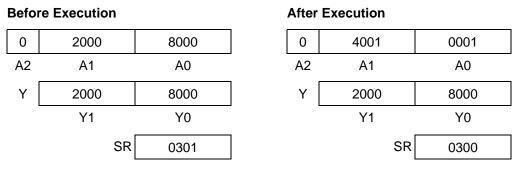

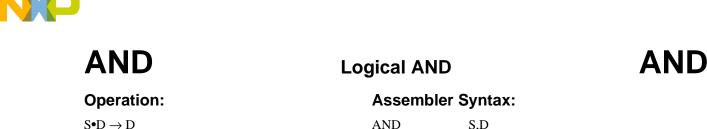

| A.7   | Instruction Descriptions A-27              |

# Appendix B DSC Benchmarks

| B.1            | Benchmark Code                                         | B-2           |

|----------------|--------------------------------------------------------|---------------|

| B.1.1          | Real Correlation or Convolution (FIR Filter)           | B-5           |

| B.1.2          | N Complex Multiplication                               |               |

| B.1.3          | Complex Correlation Or Convolution (Complex FIR)       | B-6           |

| B.1.4          | Nth Order Power Series (Real, Fractional Data)         | B-7           |

| B.1.5          | N Cascaded Real Biquad IIR Filters (Direct Form II)    | B-8           |

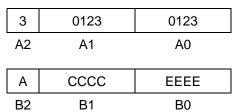

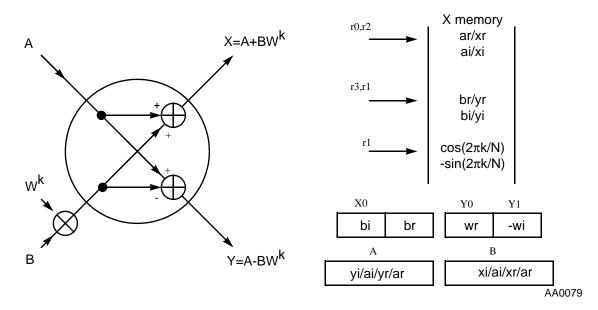

| B.1.6          | N Radix 2 FFT Butterflies                              | B-10          |

| B.1.7          | LMS Adaptive Filter                                    | B-12          |

| B.1.7.1        | Single Precision                                       | B-14          |

| B.1.7.2        | Double Precision                                       | B-16          |

| B.1.7.3        | Double Precision Delayed                               | B-18          |

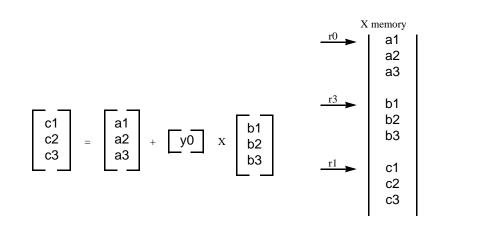

| B.1.8          | Vector Multiply-Accumulate                             | B-20          |

| B.1.9          | Energy in a Signal                                     | B-21          |

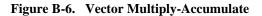

| B.1.10         | [3x3][3x1] Matrix Multiply                             | B-22          |

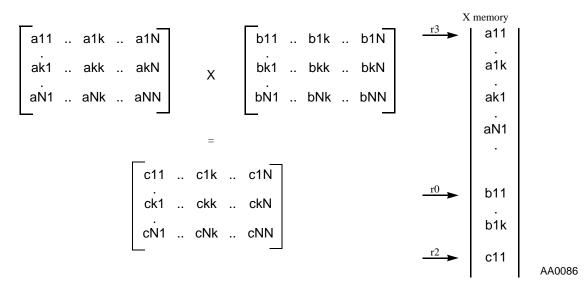

| <b>B</b> .1.11 | [NxN][NxN] Matrix Multiply (for fractional elements)   | B-23          |

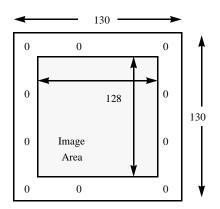

| B.1.12         | N Point 3x3 2-D FIR Convolution                        | B-26          |

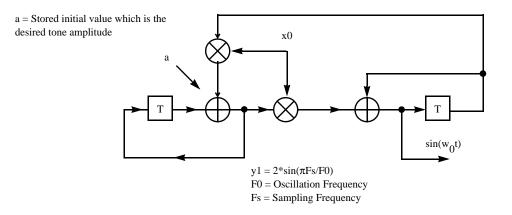

| B.1.13         | Sine-Wave Generation                                   | B-28          |

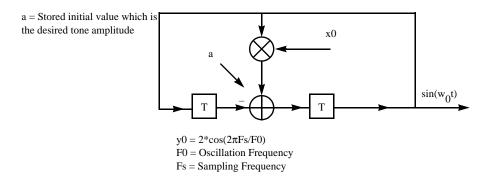

| B.1.13.        | 1 Double Integration Technique                         | B-28          |

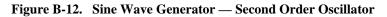

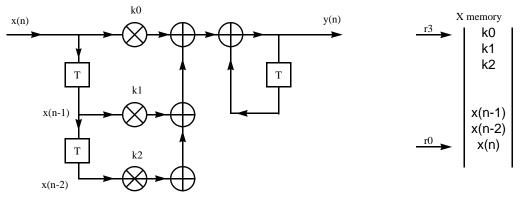

| B.1.13.        | 2 Second Order Oscillator                              | B-29          |

| <b>B</b> .1.14 | Array Search                                           | B-30          |

| B.1.14.        | I Index of the Highest Signed Value                    | B-30          |

| B.1.14.        | 2 Index of the Highest Positive Value                  | B-30          |

| B.1.15         | Proportional Integrator Differentiator (PID) Algorithm | <b> B-3</b> 1 |

| B.1.15.        | 1 PID (Version 1)                                      | <b>B-3</b> 1  |

| B.1.15.        | 2 PID (Version 2)                                      | B-32          |

| B.1.16         | Autocorrelation Algorithm                              | B-33          |

## **List of Tables**

| Table 3-1  | Accessing the Accumulator Registers                    | 3-7  |

|------------|--------------------------------------------------------|------|

| Table 3-2  | Interpretation of 16-Bit Data Values                   | 3-16 |

| Table 3-3  | Interpretation of 36-bit Data Values                   | 3-16 |

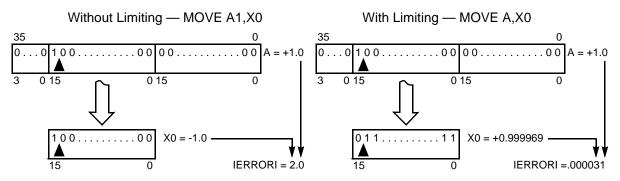

| Table 3-4  | Saturation by the Limiter Using the MOVE Instruction   | 3-27 |

| Table 3-5  | MAC Unit Outputs with Saturation Enabled               | 3-29 |

| Table 4-1  | Addressing Mode Forcing Operators                      | 4-6  |

| Table 4-2  | Jump and Branch Forcing Operators                      | 4-6  |

| Table 4-3  | Addressing Mode — Register Direct                      | 4-7  |

| Table 4-4  | Addressing Mode — Address Register Indirect            | 4-8  |

| Table 4-5  | Address-Register-Indirect Addressing Modes Available   | 4-9  |

| Table 4-6  | Addressing Mode — Immediate                            | 4-17 |

| Table 4-7  | Addressing Mode — Absolute                             | 4-20 |

| Table 4-8  | Addressing Mode Summary                                | 4-24 |

| Table 4-9  | Programming M01 for Modulo Arithmetic                  | 4-27 |

| Table 5-1  | Interrupt Mask Bit Definition                          | 5-9  |

| Table 5-2  | Program RAM Operating Modes                            | 5-10 |

| Table 5-3  | Program FLASH Operating Modes                          | 5-11 |

| Table 5-4  | MAC Unit Outputs With Saturation Mode Enabled (SA = 1) | 5-12 |

| Table 5-5  | Looping Status                                         | 5-13 |

| Table 6-1  | Memory Space Symbols                                   | 6-2  |

| Table 6-2  | Instruction Formats                                    | 6-4  |

| Table 6-3  | Arithmetic Instructions List                           | 6-6  |

| Table 6-4  | Logical Instructions List                              | 6-8  |

| Table 6-5  | Bit-Field Instruction List                             | 6-8  |

| Table 6-6  | Loop Instruction List                                  | 6-9  |

| Table 6-7  | Move Instruction List                                  | 6-10 |

| Table 6-8  | Program Control Instruction List                       | 6-10 |

| Table 6-9  | Aliases for Logical Instructions with Immediate Data   | 6-11 |

| Table 6-10 | LSLL Instruction Alias                                 | 6-12 |

| Table 6-11 | ASL Instruction Remapping                              | 6-12 |

| Table 6-12 | Clear Instruction Alias                                | 6-13 |

| Table 6-13 | Move Word Instruction Alias — Data Memory              | 6-13 |

| Table 6-14 | Register Fields for General-Purpose Writes and Reads   | 6-14 |

| Table 6-15 | Address Generation Unit (AGU) Registers                | 6-14 |

| Table 6-16 | Data ALU Registers                                       |

|------------|----------------------------------------------------------|

| Table 6-17 | Immediate Value Notation                                 |

| Table 6-18 | Move Word Instructions                                   |

| Table 6-19 | Immediate Move Instructions                              |

| Table 6-20 | Register-to-Register Move Instructions                   |

| Table 6-21 | Move Word Instructions — Program Memory                  |

| Table 6-22 | Conditional Register Transfer Instructions               |

| Table 6-23 | Data ALU Multiply Instructions                           |

| Table 6-24 | Data ALU Extended Precision Multiplication Instructions  |

| Table 6-25 | Data ALU Arithmetic Instructions                         |

| Table 6-26 | Data ALU Miscellaneous Instructions                      |

| Table 6-27 | Data ALU Logical Instructions 6-23                       |

| Table 6-28 | Data ALU Shifting Instructions                           |

| Table 6-29 | AGU Arithmetic Instructions                              |

| Table 6-30 | Bit-Manipulation Instructions                            |

| Table 6-31 | Branch on Bit-Manipulation Instructions                  |

| Table 6-32 | Change of Flow Instructions                              |

| Table 6-33 | Looping Instructions                                     |

| Table 6-34 | Control Instructions                                     |

| Table 6-35 | Data ALU Instructions — Single Parallel Move             |

| Table 6-36 | Data ALU Instructions — Dual Parallel Read               |

| Table 7-1  | Processing States                                        |

| Table 7-2  | Instruction Pipelining                                   |

| Table 7-3  | Additional Cycles for Off-Chip Memory Accesses           |

| Table 7-4  | DSP56800 Core Reset and Interrupt Vector Table           |

| Table 7-5  | Interrupt Priority Level Summary                         |

| Table 7-6  | Interrupt Mask Bit Definition in the Status Register     |

| Table 7-7  | Fixed Priority Structure Within an IPL                   |

| Table 8-1  | Operations Synthesized Using DSP56800 Instructions 8-1   |

| Table A-1  | Register Fields for General-Purpose Writes and Reads A-1 |

| Table A-2  | Address Generation Unit (AGU) Registers A-2              |

| Table A-3  | Data ALU Registers                                       |

| Table A-4  | Address Operands                                         |

| Table A-5  | Addressing Mode Operators                                |

| Table A-6  | Miscellaneous Operands                                   |

| Table A-7  | Other Symbols                                            |

| Table A-8  | Notation Used for the Condition Code Summary Table A-12  |

| Table A-9  | Condition Code Summary A-13                              |

| Table A-10 | Instruction Timing Symbols A-17                          |

| Table A-11 | Instruction Timing Summary A-18             |

|------------|---------------------------------------------|

| Table A-12 | Parallel Move Timing                        |

| Table A-13 | MOVEC Timing Summary A-20                   |

| Table A-14 | MOVEM Timing Summary A-20                   |

| Table A-15 | Bit-Field Manipulation Timing Summary A-20  |

| Table A-16 | Branch/Jump Instruction Timing Summary A-20 |

| Table A-17 | RTS Timing Summary A-21                     |

| Table A-18 | TSTW Timing Summary A-21                    |

| Table A-19 | Addressing Mode Timing Summary A-21         |

| Table A-20 | Memory Access Timing Summary A-22           |

| Table B-1  | Benchmark Summary B-1                       |

| Table B-2  | Variable Descriptions                       |

# **List of Figures**

| Figure 1-1  | DSP56800-Based DSC Microcontroller Chip                       | 1-1  |

|-------------|---------------------------------------------------------------|------|

| Figure 1-2  | DSP56800 Core Block Diagram                                   | 1-3  |

| Figure 1-3  | Example of Chip Built Around the DSP56800 Core                | 1-5  |

| Figure 1-4  | Analog Signal Processing                                      | 1-6  |

| Figure 1-5  | Digital Signal Processing                                     | 1-7  |

| Figure 1-6  | Mapping DSC Algorithms into Hardware                          | 1-8  |

| Figure 2-1  | DSP56800 Core Block Diagram                                   | 2-2  |

| Figure 2-2  | DSP56800 Memory Spaces                                        | 2-6  |

| Figure 2-3  | Sample DSP56800-Family Chip Block Diagram                     | 2-7  |

| Figure 2-4  | DSP56800 Core Programming Model                               | 2-9  |

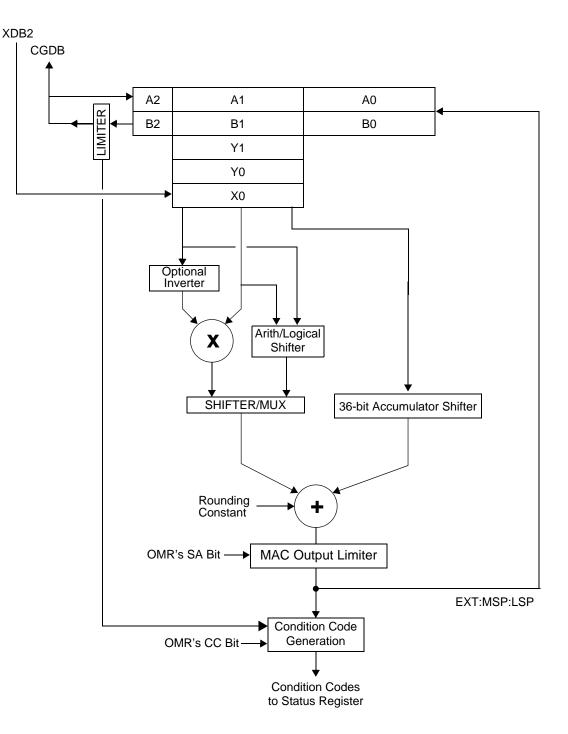

| Figure 3-1  | Data ALU Block Diagram                                        | 3-3  |

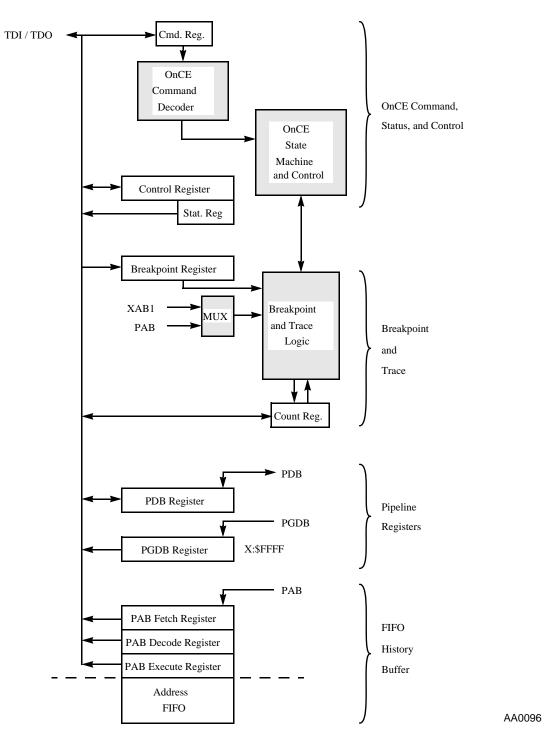

| Figure 3-2  | Data ALU Programming Model                                    | 3-4  |

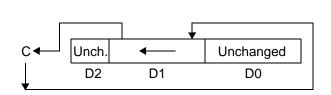

| Figure 3-3  | Right and Left Shifts Through the Multi-Bit Shifting Unit     | 3-6  |

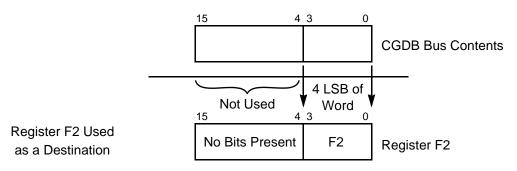

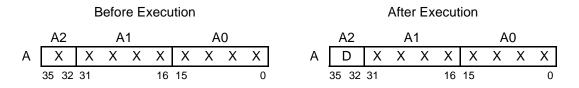

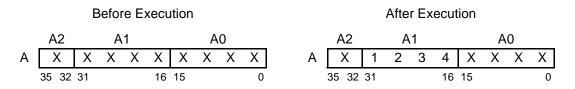

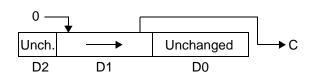

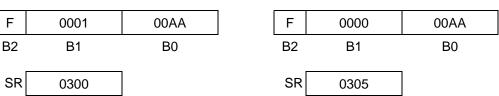

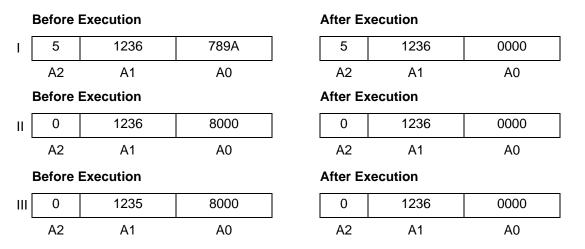

| Figure 3-4  | Writing the Accumulator Extension Registers (F2)              | 3-8  |

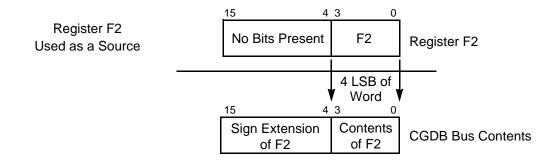

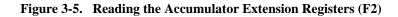

| Figure 3-5  | Reading the Accumulator Extension Registers (F2)              | 3-9  |

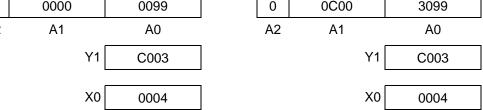

| Figure 3-6  | Writing the Accumulator by Portions                           | 3-9  |

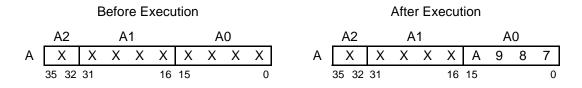

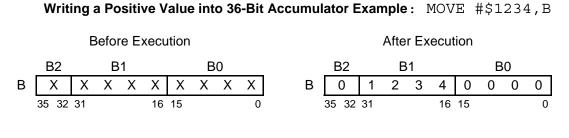

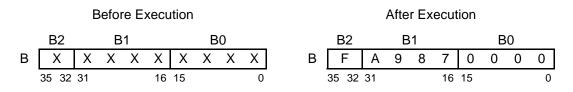

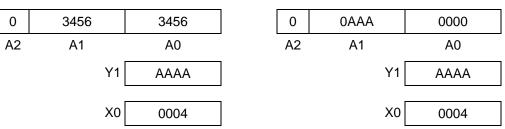

| Figure 3-7  | Writing the Accumulator as a Whole                            | 3-11 |

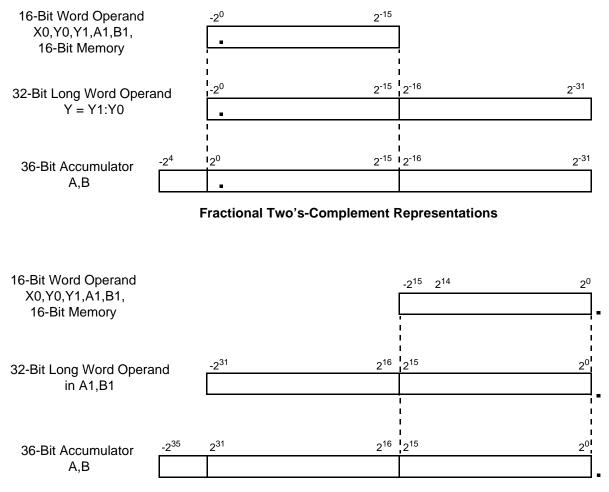

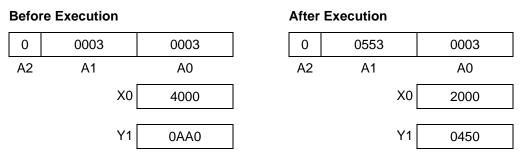

| Figure 3-8  | Bit Weightings and Operand Alignments                         | 3-15 |

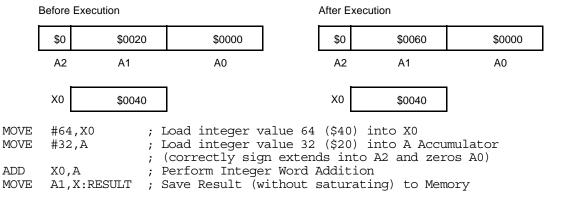

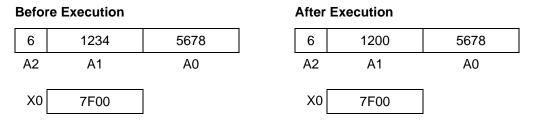

| Figure 3-9  | Word-Sized Integer Addition Example                           | 3-18 |

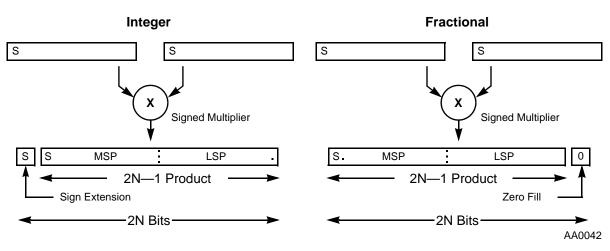

| Figure 3-10 | Comparison of Integer and Fractional Multiplication           | 3-19 |

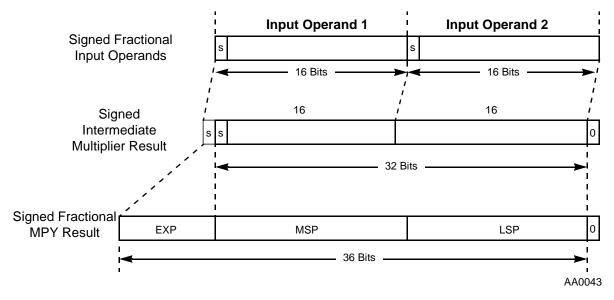

| Figure 3-11 | MPY Operation — Fractional Arithmetic                         | 3-20 |

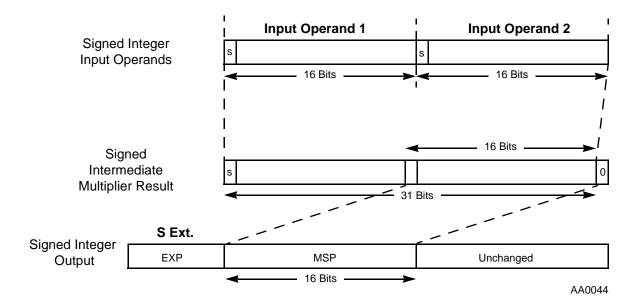

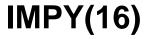

| Figure 3-12 | Integer Multiplication (IMPY)                                 | 3-21 |

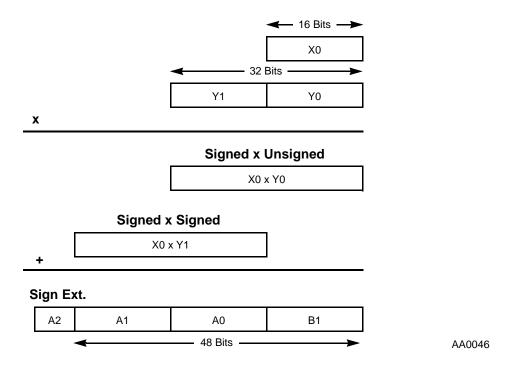

| Figure 3-13 | Single-Precision Times Double-Precision Signed Multiplication | 3-24 |

| Figure 3-14 | Example of Saturation Arithmetic                              | 3-28 |

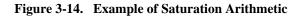

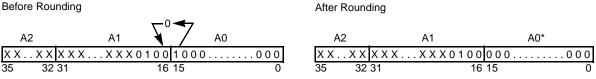

| Figure 3-15 | Convergent Rounding                                           | 3-31 |

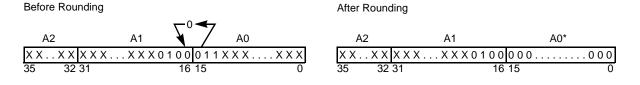

| Figure 3-16 | Two's-Complement Rounding                                     | 3-32 |

| Figure 4-1  | Address Generation Unit Block Diagram                         | 4-3  |

| Figure 4-2  | Address Generation Unit Programming Model                     | 4-3  |

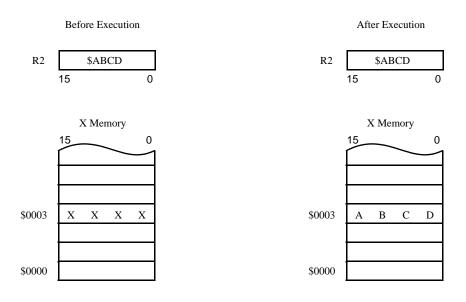

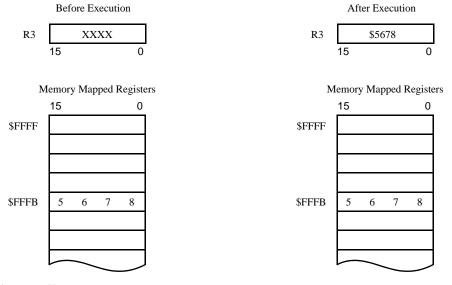

| Figure 4-3  | Address Register Indirect: No Update                          | 4-10 |

| Figure 4-4  | Address Register Indirect: Post-Increment                     | 4-11 |

| Figure 4-5  | Address Register Indirect: Post-Decrement                     | 4-12 |

| Figure 4-6  | Address Register Indirect: Post-Update by Offset N            | 4-13 |

| Figure 4-7  | Address Register Indirect: Indexed by Offset N                | 4-14 |

| Figure 4-8  | Address Register Indirect: Indexed by Short Displacement      | 4-15 |

| Figure 4-9  | Address Register Indirect: Indexed by Long Displacement 4-16 |

|-------------|--------------------------------------------------------------|

| Figure 4-10 | Special Addressing: Immediate Data 4-18                      |

| Figure 4-11 | Special Addressing: Immediate Short Data 4-19                |

| Figure 4-12 | Special Addressing: Absolute Address                         |

| Figure 4-13 | Special Addressing: Absolute Short Address 4-22              |

| Figure 4-14 | Special Addressing: I/O Short Address 4-23                   |

| Figure 4-15 | Circular Buffer                                              |

| Figure 4-16 | Circular Buffer with Size M=37 4-27                          |

| Figure 4-17 | Simple Five-Location Circular Buffer 4-29                    |

| Figure 4-18 | Linear Addressing with a Modulo Modifier                     |

| Figure 5-1  | Program Controller Block Diagram                             |

| Figure 5-2  | Program Controller Programming Model 5-3                     |

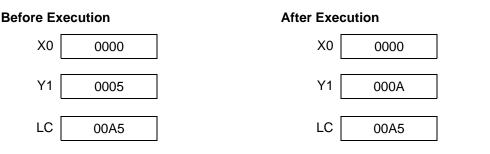

| Figure 5-3  | Accessing the Loop Count Register (LC) 5-5                   |

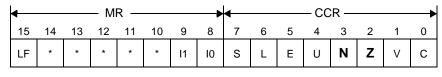

| Figure 5-4  | Status Register Format 5-7                                   |

| Figure 5-5  | Operating Mode Register (OMR) Format                         |

| Figure 6-1  | Single Parallel Move                                         |

| Figure 6-2  | Dual Parallel Move    6-3                                    |

| Figure 6-3  | DSP56800 Core Programming Model                              |

| Figure 6-4  | Pipelining                                                   |

| Figure 7-1  | Interrupt Processing                                         |

| Figure 7-2  | Example Interrupt Priority Register                          |

| Figure 7-3  | Example On-Chip Peripheral and IRQ Interrupt Programming     |

| Figure 7-4  | Illegal Instruction Interrupt Servicing                      |

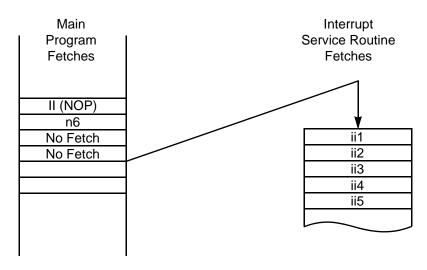

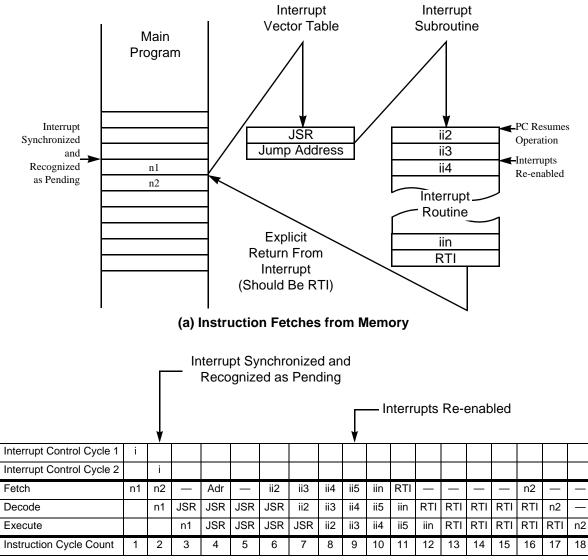

| Figure 7-5  | Interrupt Service Routine                                    |

| Figure 7-6  | Repeated Illegal Instruction                                 |

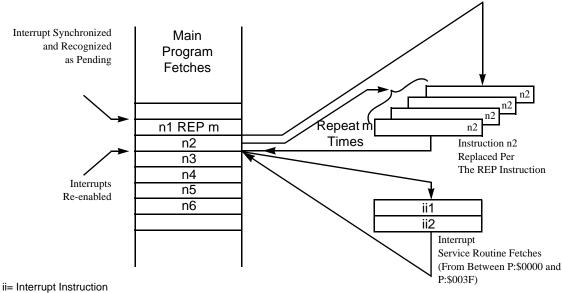

| Figure 7-7  | Interrupting a REP Instruction                               |

| Figure 7-8  | Wait Instruction Timing                                      |

| Figure 7-9  | Simultaneous Wait Instruction and Interrupt                  |

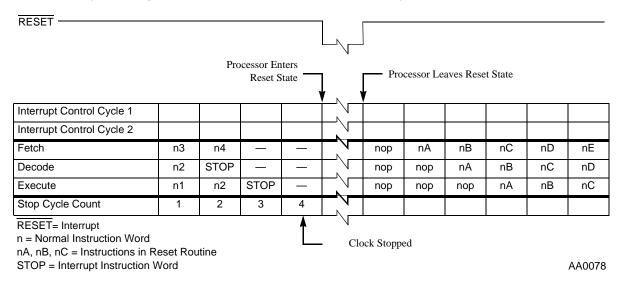

| Figure 7-10 | STOP Instruction Sequence                                    |

| Figure 7-11 | STOP Instruction Sequence                                    |

| Figure 7-12 | STOP Instruction Sequence Recovering with RESET              |

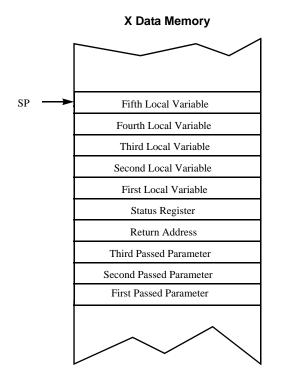

| Figure 8-1  | Example of a DSP56800 Stack Frame 8-29                       |

| Figure 9-1  | JTAG/OnCE Interface Block Diagram                            |

| Figure 9-2  | JTAG Block Diagram                                           |

| Figure 9-3  | OnCE Block Diagram                                           |

| Figure A-1  | DSP56800 Core Programming Model A-5                          |

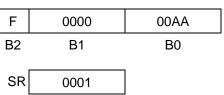

| Figure A-2  | Status Register (SR)                                         |

| Figure B-1  | N Radix 2 FFT Butterflies Memory Map B-10                    |

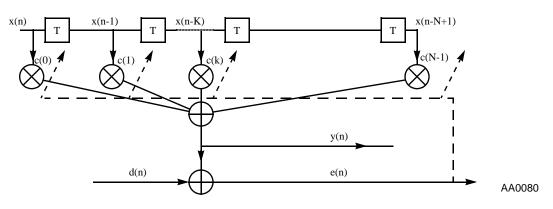

| Figure B-2  | LMS Adaptive Filter Graphic Representation B-12              |

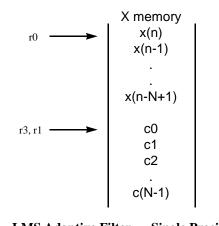

| Figure B-3  | LMS Adaptive Filter — Single Precision Memory Map              |

|-------------|----------------------------------------------------------------|

| Figure B-4  | LMS Adaptive Filter — Double Precision Memory Map B-16         |

| Figure B-5  | LMS Adaptive Filter — Double Precision Delayed Memory Map B-18 |

| Figure B-6  | Vector Multiply-Accumulate B-20                                |

| Figure B-7  | [3x3][1x3] Matrix Multiply B-22                                |

| Figure B-8  | [NxN][NxN] Matrix Multiply B-23                                |

| Figure B-9  | 3x3 Coefficient Mask B-26                                      |

| Figure B-10 | Image Stored as 130x130 ArrayB-26                              |

| Figure B-11 | Sine Wave Generator — Double Integration Technique B-28        |

| Figure B-12 | Sine Wave Generator — Second Order Oscillator B-29             |

| Figure B-13 | Proportional Integrator Differentiator Algorithm               |

|             |                                                                |

## **List of Examples**

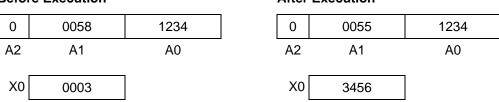

| Example 3-1  | Loading an Accumulator with a Word for Integer Processing 3-11                |

|--------------|-------------------------------------------------------------------------------|

| Example 3-2  | Reading a Word from an Accumulator for Integer Processing 3-12                |

| Example 3-3  | Correctly Reading a Word from an Accumulator to a D/A $\dots 3-12$            |

| Example 3-4  | Correct Saving and Restoring of an Accumulator — Word Accesses 3-13           |

| Example 3-5  | Bit Manipulation on an Accumulator 3-13                                       |

| Example 3-6  | Converting a 36-Bit Accumulator to a 16-Bit Value                             |

|              | Fractional Arithmetic Examples 3-14                                           |

| Example 3-8  | Integer Arithmetic Examples                                                   |

| Example 3-9  | Multiplying Two Signed Integer Values with Full Precision                     |

| Example 3-10 | Fast Integer MACs using Fractional Arithmetic.    3-21                        |

| Example 3-11 | Multiplying Two Unsigned Fractional Values                                    |

| Example 3-12 | 64-Bit Addition                                                               |

| Example 3-13 | 64-Bit Subtraction                                                            |

| Example 3-14 | Fractional Single-Precision Times Double-Precision Value — Both Signed . 3-24 |

| Example 3-15 | Integer Single-Precision Times Double-Precision Value — Both Signed 3-24      |

| Example 3-16 | Multiplying Two Fractional Double-Precision Values                            |

| Example 3-17 | Demonstrating the Data Limiter — Positive Saturation 3-26                     |

| Example 3-18 | Demonstrating the Data Limiter — Negative Saturation                          |

| Example 3-19 | Demonstrating the MAC Output Limiter 3-28                                     |

| Example 4-1  | Initializing the Circular Buffer                                              |

| Example 4-2  | Accessing the Circular Buffer                                                 |

| Example 4-3  | Accessing the Circular Buffer with Post-Update by Three 4-30                  |

|              | No Dependency with the Offset Register 4-33                                   |

| Example 4-5  | No Dependency with an Address Pointer Register 4-33                           |

| Example 4-6  | No Dependency with No Address Arithmetic Calculation 4-34                     |

| Example 4-7  | No Dependency with (Rn+xxx) 4-34                                              |

| Example 4-8  | Dependency with a Write to the Offset Register 4-34                           |

| Example 4-9  | Dependency with a Bit-Field Operation on the Offset Register 4-34             |

| Example 4-10 | Dependency with a Write to an Address Pointer Register 4-34                   |

| Example 4-11 | Dependency with a Write to the Modifier Register 4-34                         |

| Example 4-12 | Dependency with a Write to the Stack Pointer Register                         |

| Example 4-13 | Dependency with a Bit-Field Operation and DO Loop 4-35                        |

| Example 5-1 | Disabling Maskable Interrupts 5-9               |

|-------------|-------------------------------------------------|

| Example 6-1 | MOVE Instruction Types 6-1                      |

| Example 6-2 | Logical OR with a Data Memory Location          |

| Example 6-3 | Valid Instructions                              |

| Example 6-4 | Invalid Instruction                             |

| Example 6-5 | Examples of Single Parallel Moves               |

| Example 7-1 | Pipeline Dependencies in Similar Code Sequences |

| Example 7-2 | Common Pipeline Dependency Code Sequence        |

| Example 8-1 | JRSET and JRCLR                                 |

| Example 8-2 | BR1SET and BR1CLR 8-3                           |

| Example 8-3 | JR1SET and JR1CLR 8-3                           |

| Example 8-4 | JVS, JVC, BVS and BVC 8-4                       |

| Example 8-5 | JPL and BES                                     |

| Example 8-6 | Simple Fractional Division                      |

| Example 8-7 | Signed Fractional Division                      |

| Example 8-8 | Simple Integer Division 8-18                    |

| Example 8-9 | Signed Integer Division 8-18                    |

| Example A-1 | Arithmetic Instruction with Two Parallel Reads  |

| Example A-2 | Jump Instruction                                |

| Example A-3 | RTS Instruction                                 |

| Example B-1 | Source Code Layout                              |

## About This Book

This manual describes the central processing unit of the DSP56800 Family in detail. It is intended to be used with the appropriate DSP56800 Family member user's manual, which describes the central processing unit, programming models, and details of the instruction set. The appropriate DSP56800 Family member technical data sheet provides timing, pinout, and packaging descriptions.

This manual provides practical information to help the user accomplish the following:

- Understand the operation and instruction set of the DSP56800 Family

- Write code for DSC algorithms

- Write code for general control tasks

- Write code for communication routines

- Write code for data manipulation algorithms

### Audience

The information in this manual is intended to assist design and software engineers with integrating a DSP56800 Family device into a design and with developing application software.

## Organization

Information in this manual is organized into chapters by topic. The contents of the chapters are as follows:

**Chapter 1, "Introduction."** This section introduces the DSP56800 core architecture and its application. It also provides the novice with a brief overview of digital signal processing.

**Chapter 2, "Core Architecture Overview."** The DSP56800 core architecture consists of the data arithmetic logic unit (ALU), address generation unit (AGU), program controller, bus and bit-manipulation unit, and a JTAG/On-Chip Emulation ( $OnCE^{TM}$ ) port. This section describes each subsystem and the buses interconnecting the major components in the DSP56800 central processing module.

**Chapter 3, "Data Arithmetic Logic Unit."** This section describes the data ALU architecture, its programming model, an introduction to fractional and integer arithmetic, and a discussion of other topics such as unsigned and multi-precision arithmetic on the DSP56800 Family.

**Chapter 4, "Address Generation Unit."** This section specifically describes the AGU architecture and its programming model, addressing modes, and address modifiers.

**Chapter 5, "Program Controller."** This section describes in detail the program controller architecture, its programming model, and hardware looping. Note, however, that the different processing states of the DSP56800 core, including interrupt processing, are described in Chapter 7, "Interrupts and the Processing States."

**Chapter 6, "Instruction Set Introduction."** This section presents an introduction to parallel moves and a brief description of the syntax, instruction formats, operand and memory references, data organization, addressing modes, and instruction set. It also includes a summary of the instruction set, showing the registers and addressing modes available to each instruction. A detailed description of each instruction is given in Appendix A, "Instruction Set Details."

**Chapter 7, "Interrupts and the Processing States."** This section describes five of the six processing states (normal, exception, reset, wait, and stop). The sixth processing state (debug) is covered more completely in Chapter 9, "JTAG and On-Chip Emulation (OnCE<sup>TM</sup>)."

**Chapter 8, "Software Techniques."** This section teaches the advanced user techniques for more efficient programming of the DSP56800 Family. It includes a description of useful instruction sequences and macros, optimal loop and interrupt programming, topics related to the stack of the DSP56800, and other useful software topics.

**Chapter 9, "JTAG and On-Chip Emulation (OnCE**<sup>TM</sup>)." This section describes the combined JTAG/OnCE port and its functions. These two are integrally related, sharing the same pins for I/O, and are presented together in this section.

**Appendix A, "Instruction Set Details."** This section presents a detailed description of each DSP56800 Family instruction, its use, and its effect on the processor.

**Appendix B, "DSP Benchmarks."** DSP56800 Family benchmark example programs and results are listed in this appendix.

## Suggested Reading

A list of DSC-related books is included here as an aid for the engineer who is new to the field of DSC:

Advanced Topics in Signal Processing, Jae S. Lim and Alan V. Oppenheim (Prentice-Hall: 1988).

Applications of Digital Signal Processing, A. V. Oppenheim (Prentice-Hall: 1978).

Digital Processing of Signals: Theory and Practice, Maurice Bellanger (John Wiley and Sons: 1984).

Digital Signal Processing, Alan V. Oppenheim and Ronald W. Schafer (Prentice-Hall: 1975).

*Digital Signal Processing: A System Design Approach,* David J. DeFatta, Joseph G. Lucas, and William S. Hodgkiss (John Wiley and Sons: 1988).

Discrete-Time Signal Processing, A. V. Oppenheim and R.W. Schafer (Prentice-Hall: 1989).

Foundations of Digital Signal Processing and Data Analysis, J. A. Cadzow (Macmillan: 1987).

Handbook of Digital Signal Processing, D. F. Elliott (Academic Press: 1987).

Introduction to Digital Signal Processing, John G. Proakis and Dimitris G. Manolakis (Macmillan: 1988).

Multirate Digital Signal Processing, R. E. Crochiere and L. R. Rabiner (Prentice-Hall: 1983).

Signal Processing Algorithms, S. Stearns and R. Davis (Prentice-Hall: 1988).

Signal Processing Handbook, C. H. Chen (Marcel Dekker: 1988).

Signal Processing: The Modern Approach, James V. Candy (McGraw-Hill: 1988).

*Theory and Application of Digital Signal Processing*, Lawrence R. Rabiner and Bernard Gold (Prentice-Hall: 1975).

### Conventions

This document uses the following notational conventions:

- Bits within registers are always listed from most significant bit (MSB) to least significant bit (LSB).

- Bits within a register are formatted AA[n:0] when more than one bit is involved in a description. For purposes of description, the bits are presented as if they are contiguous within a register. However, this is not always the case. Refer to the programming model diagrams or to the programmer's sheets to see the exact location of bits within a register.

- When a bit is described as "set," its value is set to 1. When a bit is described as "cleared," its value is set to 0.

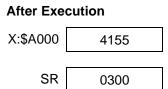

- Memory addresses in the separate program and data memory spaces are differentiated by a one-letter prefix. Data memory addresses are preceded by "X:" while program memory addresses have a "P:" prefix. For example, "P:\$0200" indicates a location in program memory.

- Hex values are indicated with a dollar sign (\$) preceding the hex value, as follows: \$FFFB is the X memory address for the Interrupt Priority Register (IPR).

- Code examples are displayed in a monospaced font, as follows:

| BFSET #\$0007,X:PCC | ; Configure:                        | line 1 |

|---------------------|-------------------------------------|--------|

|                     | ; MISOO, MOSIO, SCKO for SPI master | line 2 |

|                     | ; ~SSO as PC3 for GPIO              | line 3 |

## Definitions, Acronyms, and Abbreviations

The following terms appear frequently in this manual:

| DSC    | digital signal controller |

|--------|---------------------------|

| JTAG   | Joint Test Action Group   |

| OnCETM | <b>On-Chip Emulation</b>  |

| ALU    | arithmetic logic unit     |

| AGU    | address generation unit   |

|        |                           |

A complete list of relevant terms is included in the Glossary at the end of this manual.

## **Chapter 1** Introduction

The DSP56800 Digital Signal Controllers provide low cost, low power, mid-performance computing, combining DSC power and parallelism with MCU-like programming simplicity. The DSP56800 core is a general-purpose central processing unit, designed for both efficient digital signal processing and a variety of controller operations.

## **1.1 DSP56800 Family Architecture**

The DSP56800 Family uses the DSP56800 16-bit DSC core. This core is a general-purpose central processing unit (CPU), designed for both efficient DSC and controller operations. Its instruction-set efficiency as a DSC is superior to other low-cost DSC architectures and has been designed for efficient, straightforward coding of controller-type tasks.

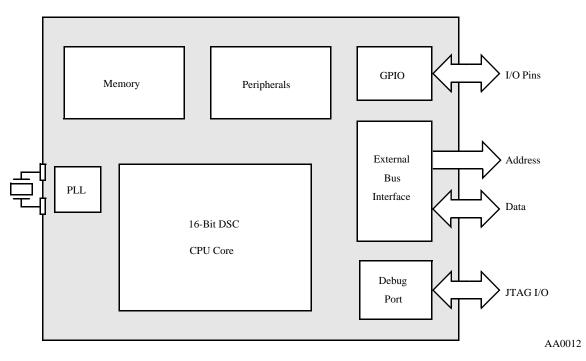

Figure 1-1. DSP56800-Based DSC Microcontroller Chip

The general-purpose MCU-style instruction set, with its powerful addressing modes and bit-manipulation instructions, enables a user to begin writing code immediately, without having to worry about the complexities previously associated with DSCs. A software stack allows for unlimited interrupt and subroutine nesting, as well as support for structured programming techniques such as parameter passing

Freescale Semiconductor

and the use of local variables. The veteran DSC programmer sees a powerful DSC instruction set with many different arithmetic operations and flexible single- and dual-memory moves that can occur in parallel with an arithmetic operation. The general-purpose nature of the instruction set also allows for an efficient compiler implementation.

A variety of standard peripherals can be added around the DSP56800 core (see Figure 1-1 on page 1-1) such as serial ports, general-purpose timers, real-time and watchdog timers, different memory configurations (RAM, FLASH, or both), and general-purpose I/O (GPIO) ports.

On-Chip Emulation (OnCE<sup>TM</sup>) capability is provided through a debug port conforming to the Joint Test Action Group (JTAG) standard. This provides real-time, embedded system debugging with on-chip emulation capability through the five-pin JTAG interface. A user can set hardware and software breakpoints, display and change registers and memory locations, and single step or step through multiple instructions in an application.

The DSP56800's efficient instruction set, multiple internal buses, on-chip program and data memories, external bus interface, standard peripherals, and industry-standard debug support make the DSP56800 Family an excellent solution for real-time embedded control tasks. It is an excellent fit for wireless or wireline DSC applications, digital control, and controller applications in need of more processing power.

### **1.1.1** Core Overview

The DSP56800 core is a programmable 16-bit CMOS digital signal controller that consists of a 16-bit data arithmetic logic unit (ALU), a 16-bit address generation unit (AGU), a program decoder, On-Chip Emulation (OnCE), associated buses, and an instruction set. Figure 1-2 on page 1-3 shows a block diagram of the DSP56800 core. The main features of the DSP56800 core include the following:

- Processing capability of up to 35 million instructions per second (MIPS) at 70 MHz

- Requires only 2.7–3.6 V of power

- Single-instruction cycle 16-bit x 16-bit parallel multiply-accumulator

- Two 36-bit accumulators including extension bits

- Single-instruction 16-bit barrel shifter

- Parallel instruction set with unique DSC addressing modes

- Hardware DO and REP loops

- Two external interrupt request pins

- Four 16-bit internal core data buses

- Three 16-bit internal address buses

- Instruction set that supports both DSC and controller functions

- Controller-style addressing modes and instructions for smaller code size

- Efficient C compiler and local variable support

- Software subroutine and interrupt stack with unlimited depth

- On-Chip Emulation for unobtrusive, processor-speed-independent debugging

- Low-power wait and stop modes

- Operating frequency down to DC

- Single power supply

AA0006

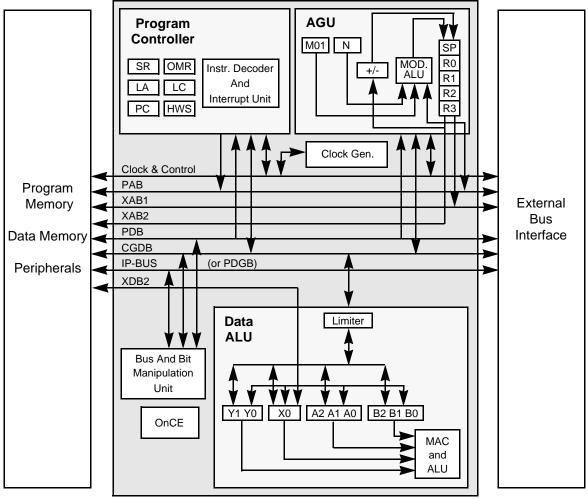

Figure 1-2. DSP56800 Core Block Diagram

### **1.1.2** Peripheral Blocks

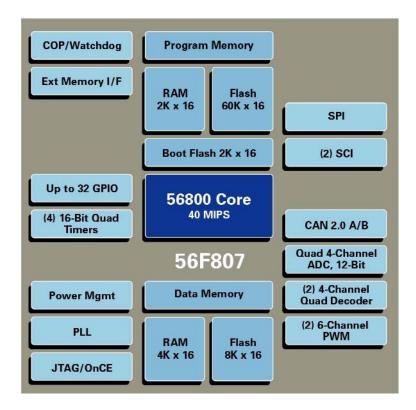

The following peripheral blocks are available for members of the DSP56800 16-bit Family:

- Program FLASH and RAM modules

- Bootstrap FLASH for program RAM parts

- Data FLASH and RAM modules

- Phase-locked loop (PLL) module

- General purpose Quad Timers

- Computer operating properly (COP) module

- Serial Communication Interfaces (SCIs)

- Synchronous serial interface module (SSI)

- Serial peripheral interface (SPI)

- Quadrature Decoders

- Controller Area Network (CAN) Modules

- Multiple channels Pulse Width Modulation (PWM) Modules

- External Memory Interface (EMI)

- Multiple channels Analog-to-Digital Converters (ADC)

- Programmable general-purpose I/O (dedicated & shared)

- JTAG/OnCE port for debugging

More blocks will be defined in the future to meet customer needs.

### **1.1.3** Family Members

The DSP56800 core processor is designed as a core processor for a family of Freescale DSCs. An example of a chip (56F807) built with this core is shown in Figure 1-3.

Figure 1-3. Example of Chip Built Around the DSP56800 Core

## **1.2** Introduction to Digital Signal Processing

DSC is the arithmetic processing of real-time signals sampled at regular intervals and digitized. Examples of DSC processing include the following:

- Filtering

- Convolution (mixing two signals)

- Correlation (comparing two signals)

- Rectification, amplification, and transformation

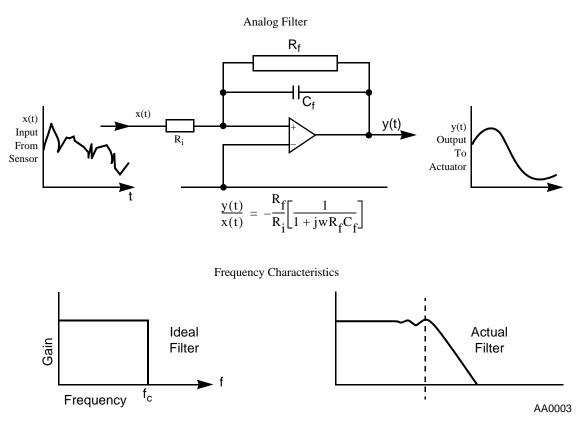

Figure 1-4 on page 1-6 shows an example of analog signal processing. The circuit in the illustration filters a signal from a sensor using an operational amplifier and controls an actuator with the result. Since the ideal filter is impossible to design, the engineer must design the filter for acceptable response by considering variations in temperature, component aging, power-supply variation, and component accuracy. The resulting circuit typically has low noise immunity, requires adjustments, and is difficult to modify.

Figure 1-4. Analog Signal Processing

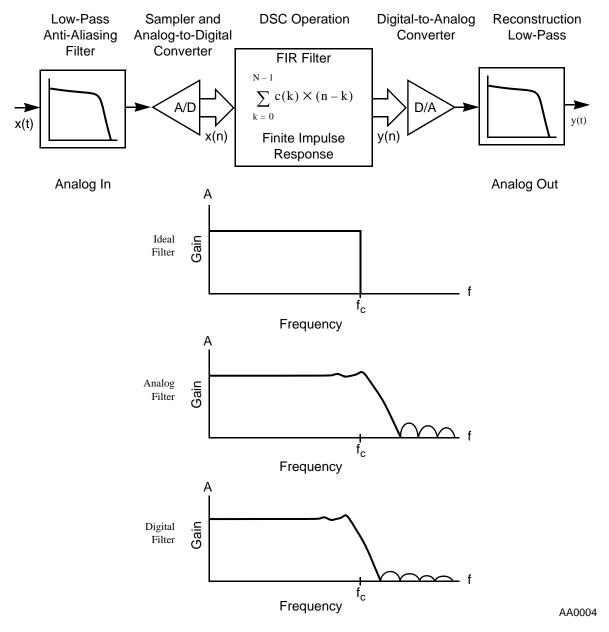

The equivalent circuit using a DSC is shown in Figure 1-5 on page 1-7. This application requires an analog-to-digital (A/D) converter and digital-to-analog (D/A) converter in addition to the DSC. Even with these additional parts, the component count can be lower using a DSC due to the high integration available with current components.

Figure 1-5. Digital Signal Processing

Processing in this circuit begins by band limiting the input signal with an anti-alias filter, eliminating out-of-band signals that can be aliased back into the pass band due to the sampling process. The signal is then sampled, digitized with an A/D converter, and sent to the DSC.

The filter implemented by the DSC is strictly a matter of software. The DSC can directly employ any filter that can also be implemented using analog techniques. Also, adaptive filters can be easily put into practice using DSC, whereas these filters are extremely difficult to implement using analog techniques. (Similarly, compression can also be implemented on a DSC.)

The DSC output is processed by a D/A converter and is low-pass filtered to remove the effects of digitizing. In summary, the advantages of using the DSC include the following:

- Fewer components

- Stable, deterministic performance

- No filter adjustments

- Wide range of applications

- Filters with much closer tolerances

- High noise immunity

- Adaptive filters easily implemented

- Self-test can be built in

- Better power-supply rejection

The DSP56800 Family is not a custom IC designed for a particular application; it is designed as a general-purpose DSC architecture to efficiently execute commonly used DSC benchmarks and controller code in minimal time.

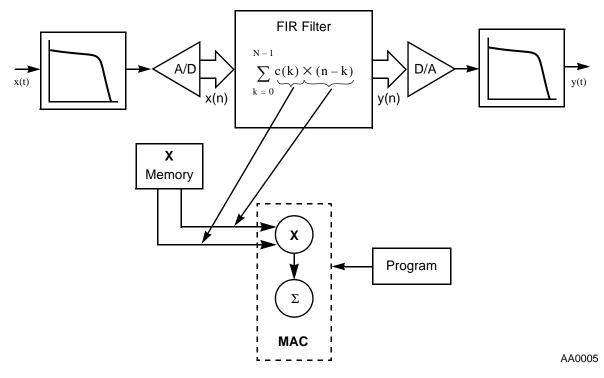

As shown in Figure 1-6, the key attributes of a DSC are as follows:

- Multiply/accumulate (MAC) operation

- Fetching up to two operands per instruction cycle for the MAC

- Program control to provide versatile operation

- Input/output to move data in and out of the DSC

Figure 1-6. Mapping DSC Algorithms into Hardware

The multiply-accumulation (MAC) operation is the fundamental operation used in DSC. The DSP56800 Family of processors has a dual Harvard architecture optimized for MAC operations. Figure 1-6 on page 1-8 shows how the DSP56800 architecture matches the shape of the MAC operation. The two operands, c() and x(), are directed to a multiply operation, and the result is summed. This process is built into the chip by allowing two separate data-memory accesses to feed a single-cycle MAC. The entire process must occur under program control to direct the correct operands to the multiplier and save the accumulated result as needed. Since the memory and the MAC are independent, the DSC can perform two memory moves, a multiply and an accumulate, and two address updates in a single operation. As a result, many DSC benchmarks execute very efficiently for a single-multiplier architecture.

## **1.3** Summary of Features

The high throughput of the DSP56800 Family processors makes them well-suited for wireless and wireline communication, high-speed control, low-cost voice processing, numeric processing, and computer and audio applications. The main features that contribute to this high throughput include the following:

- **Speed**—The DSP56800 supports most mid-performance DSC applications.

- **Precision**—The data paths are 16 bits wide, providing 96 dB of dynamic range; intermediate results held in the 36-bit accumulators can range over 216 dB.

- **Parallelism**—Each on-chip execution unit, memory, and peripheral operates independently and in parallel with the other units through a sophisticated bus system. The data ALU, AGU, and program controller operate in parallel so that the following can be executed in a single instruction:

- An instruction pre-fetch

- A 16-bit x 16-bit multiplication

- A 36-bit addition

- Two data moves

- Two address-pointer updates using one of two types of arithmetic (linear or modulo)

- Sending and receiving full-duplex data by the serial ports

- Timers continuing to count in parallel

- **Flexibility**—While many other DSCs need external communications circuitry to interface with peripheral circuits (such as A/D converters, D/A converters, or host processors), the DSP56800 Family provides on-chip serial and parallel interfaces that can support various configurations of memory and peripheral modules. The peripherals are interfaced to the DSP56800 core through a peripheral interface bus, designed to provide a common interface to many different peripherals.

- **Sophisticated debugging** Freescale's On-Chip Emulation technology (OnCE) allows simple, inexpensive, and speed-independent access to the internal registers for debugging. OnCE tells application programmers exactly what the status is within the registers, memory locations, and even the last instructions that were executed.

- **Phase-locked loop (PLL)–based clocking**—The PLL allows the chip to use almost any available external system clock for full-speed operation while also supplying an output clock synchronized to a synthesized internal core clock. It improves the synchronous timing of the processors' external memory port, eliminating the timing skew common on other processors.

- **Invisible pipeline**—The three-stage instruction pipeline is essentially invisible to the programmer, allowing straightforward program development in either assembly language or high-level languages such as C or C++.

- **Instruction set**—The instruction mnemonics are MCU-like, making the transition from programming microprocessors to programming the chip as easy as possible. New microcontroller instructions, addressing modes, and bit-field instructions allow for significant decreases in program code size. The orthogonal syntax controls the parallel execution units. The hardware DO loop instruction and the repeat (REP) instruction make writing straight-line code obsolete.

- **Low power**—Designed in CMOS, the DSP56800 Family inherently consumes very low power. Two additional low power modes, stop and wait, further reduce power requirements. Wait is a low-power mode where the DSP56800 core is shut down but the peripherals and interrupt controller continue to operate so that an interrupt can bring the chip out of wait mode. In stop mode, even more of the circuitry is shut down for the lowest power-consumption mode. There are also several different ways to bring the chip out of stop mode.

## **1.4** For the Latest Information

For the latest electronic version of this document, as well as other DSC documentation (including user's manuals, product briefs, data sheets, and errata) please consult the inside front cover of this manual for contact information for the following services:

- Freescale DSC World Wide Web site

- Freescale DSC Helpline

The DSC Web site maintain the most current specifications, documents, and drawings.

## **Chapter 2 Core Architecture Overview**

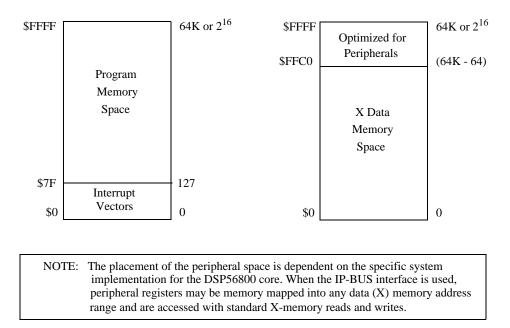

The DSP56800 core architecture is a 16-bit multiple-bus processor designed for efficient real-time digital signal processing and general purpose computing. The architecture is designed as a standard programmable core from which various DSC integrated circuit family members can be designed with different on-chip and off-chip memory sizes and on-chip peripheral requirements. This chapter presents the overall core architecture and the general programming model. More detailed information on the data ALU, AGU, program controller, and JTAG/OnCE blocks within the architecture are found in later chapters.

## 2.1 Core Block Diagram

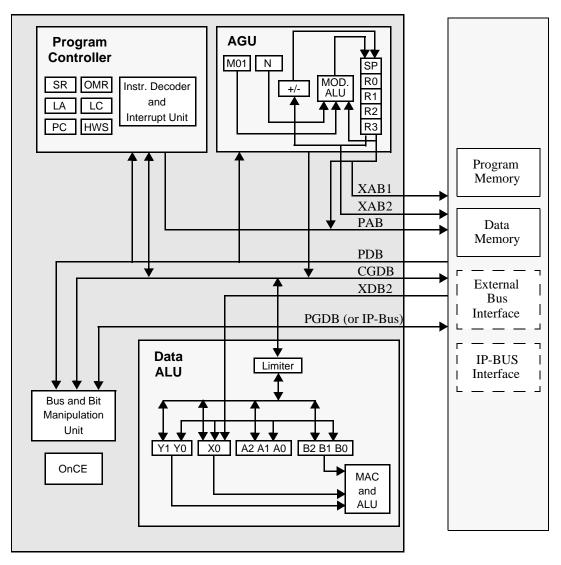

The DSP56800 core is composed of functional units that operate in parallel to increase the throughput of the machine. The program controller, AGU, and data ALU each contain their own register set and control logic, so each may operate independently and in parallel with the other two. Likewise, each functional unit interfaces with other units, with memory, and with memory-mapped peripherals over the core's internal address and data buses. The architecture is pipelined to take advantage of the parallel units and significantly decrease the execution time of each instruction.

For example, it is possible for the data ALU to perform a multiplication in a first instruction, for the AGU to generate up to two addresses for a second instruction, and for the program controller to be fetching a third instruction. In a similar manner, it is possible for the bit-manipulation unit to perform an operation of the third instruction described above in place of the multiplication in the data ALU.

The major components of the core are the following:

- Data ALU

- AGU

- Program controller and hardware looping unit

- Bus and bit-manipulation unit

- OnCE debug port

- Address buses

- Data buses

Figure 2-1 on page 2-2 shows a block diagram of the CPU architecture.

**Core Architecture Overview**

Figure 2-1. DSP56800 Core Block Diagram

Note that Figure 2-1 illustrates two methods for connecting peripherals to the DSP56800 core: using the Freescale-standard IP-BUS interface or via a dedicated Peripheral Global Data Bus (PGDB). The interface method used to connect to peripherals is dependent on the specific DSP56800-based device being used. The latest products have chosen the IP-BUS interface. Consult your device user's manual for more information on peripheral interfacing.

## 2.1.1 Data Arithmetic Logic Unit (ALU)

The data arithmetic logic unit (ALU) performs all of the arithmetic and logical operations on data operands. It consists of the following:

- Three 16-bit input registers (X0, Y0, and Y1)

- Two 36-bit accumulator registers (A and B)

- 16-bit registers (A0 and B0)

- 16-bit registers (A1 and B1)

- 4-bit extension registers (A2 and B2)

- An accumulator shifter (AS)

- One data limiter

- One 16-bit barrel shifter

- One parallel (single cycle, non-pipelined) multiply-accumulator (MAC) unit

The data ALU is capable of multiplication, multiply-accumulation (with positive or negative accumulation), addition, subtraction, shifting, and logical operations in one instruction cycle. Arithmetic operations are done using two's-complement fractional or integer arithmetic. Support is also provided for unsigned and multi-precision arithmetic.

Data ALU source operands may be 16, 32, or 36 bits and may individually originate from input registers, memory locations, immediate data, or accumulators. ALU results are stored in one of the accumulators. In addition, some arithmetic instructions store their 16-bit results either in one of the three data ALU input registers or directly in memory. Arithmetic operations and shifts can have a 16-bit or a 36-bit result. Logical operations are performed on 16-bit operands and always yield 16-bit results.

Data ALU register values can be transferred (read or write) across the core global data bus (CGDB) as 16-bit operands. The X0 register value can also be written by X memory data bus two (XDB2) as a 16-bit operand. Refer to Chapter 3, "Data Arithmetic Logic Unit," for a detailed description of the data ALU.

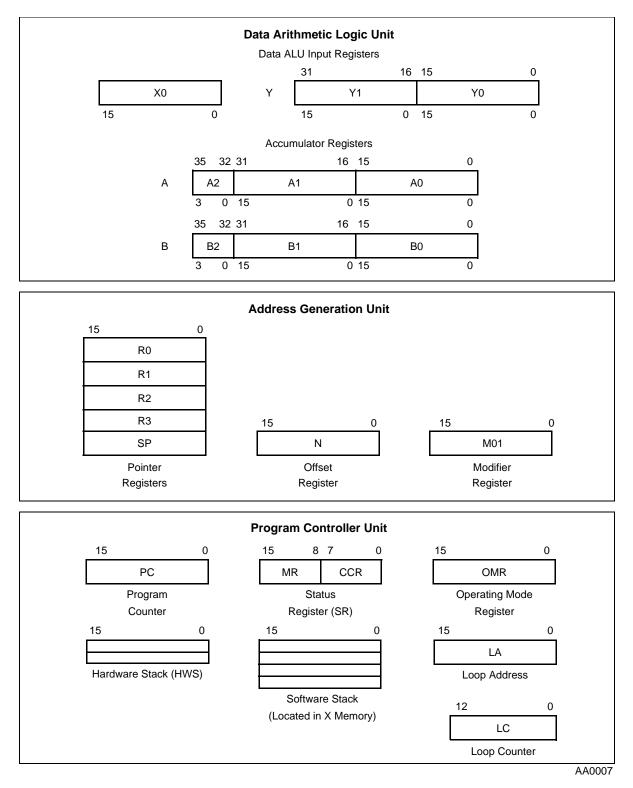

### 2.1.2 Address Generation Unit (AGU)

The address generation unit (AGU) performs all of the effective address calculations and address storage necessary to address data operands in memory. The AGU operates in parallel with other chip resources to minimize address-generation overhead. It contains two ALUs, allowing the generation of up to two 16-bit addresses every instruction cycle: one for either X memory address bus one (XAB1) or program address bus (PAB) and one for X memory address bus two (XAB2). The ALU can directly address 65,536 locations on the XAB1 or XAB2 and 65,536 locations on the PAB, totaling 131,072 sixteen-bit data words. It supports a complete set of addressing modes. Its arithmetic unit can perform both linear and modulo arithmetic.

The AGU contains the following registers:

- Four address registers (R0-R3)

- A stack pointer register (SP)

- An offset register (N)

- A modifier register (M01)

- A modulo arithmetic unit

- An incrementer/decrementer unit

# Core Architecture Overview

The address registers are 16-bit registers that may contain an address or data. Each address register can provide an address for the XAB1 and PAB address buses. For instructions that read two values from X data memory, R3 provides an address for the XAB2, and R0 or R1 provides an address for the XAB1. The modifier and offset registers are 16-bit registers that control updating of the address registers. The offset register can also be used to store 16-bit data. AGU registers may be read or written by the CGDB as 16-bit operands. Refer to Chapter 4, "Address Generation Unit," for a detailed description of the AGU.

## 2.1.3 Program Controller and Hardware Looping Unit

The program controller performs the following:

- Instruction prefetch

- Instruction decoding

- Hardware loop control

- Interrupt (exception) processing

Instruction execution is carried out in other core units such as the data ALU, AGU, or bit-manipulation unit. The program controller consists of the following: