# **DSTD-703**

MULTI FUNCTIONAL CALENDAR/CLOCK CARD

#### NOTICE

The proprietary information contained in this document must not be disclosed to others for any purpose, nor used for manufacturing purposes, without written permission of dy-4 SYSTEMS INC. The acceptance of this document will be construed as an acceptance of the foregoing condition.

# TABLE OF CONTENTS

| PARAGRAPH<br>NUMBER                                                         | TITLE                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                    |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

|                                                                             | GENERAL INFORMATION                                                                                                                                                                                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                  |

| 1.1<br>1.2<br>1.3                                                           | Introduction DSTD Series General Description DSTD-703 Features                                                                                                                                                                                                                                                  | 1<br>1<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -<br>-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1<br>1<br>1                        |

|                                                                             | FUNCTIONAL HARDWARE DESCRIPTION                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                    |

| 2.2<br>2.2.1<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.6<br>2.2.7<br>2.2.8<br>2.2.9 | Introduction Block Diagram Description STD BUS Interface Memory Decode Logic Memory I/O Decode Logic Counter/Timer Controller Parallel Ports Real Time Clock Battery Back Up Brown-Out Detector Z80 Interrupts Interrupt Overview Priority Daisy-Chain I/O Port Address Summary                                 | 22222222222222                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 111122222333335                    |

|                                                                             | USER SELECTABLE OPTIONS                                                                                                                                                                                                                                                                                         | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                  |

| 3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.5<br>3.6                     | Transparent Input Mode Latched Output Transparent Output Latched Bi-directional Mode Transparent Bi-directional Mode +5V Only Charge Option (JB5) Bytewide Memory Socket Configuration (JB6, JB7, JB8, JB9) On-Board Battery Select (JB10) Memory Base Address Select (JB11) Memory Option Configuration (JB12) | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1123445555699 11122                |

|                                                                             | NUMBER  1.123 1.23456789 1.21.3 2.222222222222222222222222222222                                                                                                                                                                                                                                                | GENERAL INFORMATION  1.1 Introduction 1.2 DSTD Series General Description 1.3 DSTD-703 Features  FUNCTIONAL HARDWARE DESCRIPTION  2.1 Introduction 2.2 Block Diagram Description 2.2.1 STD BUS Interface 2.2.2 Memory Decode Logic 2.2.3 Memory 2.2.4 I/O Decode Logic 2.2.5 Counter/Timer Controller 2.2.6 Parallel Ports 2.2.7 Real Time Clock 2.2.8 Battery Back Up 2.2.9 Brown-Out Detector 2.3 Z80 Interrupts 2.3.1 Interrupt Overview 2.3.2 Priority Daisy-Chain 2.4 I/O Port Address Summary  USER SELECTABLE OPTIONS  3.1 Introduction 3.2 Counter/Timer Configuration (JB1) 3.3 I/O Base Address Select 3.4 Parallel Ports (JB3,JB4) 3.4.1 Modes of Operation 3.4.2 Latch Input 3.4.3 Transparent Input Mode 3.4.4 Transparent Output 3.4.5 Transparent Output 3.4.5 Transparent Output 3.4.5 Transparent Bi-directional Mode 3.4.7 Transparent Bi-directional Mode 3.4.7 Transparent Bi-directional Mode 3.4.7 Transparent Bi-directional Mode 3.5 +5V Only Charge Option (JB5) 3.6 Bytewide Memory Socket Configuration (JB6,JB7,JB8,JB9) 3.7 On-Board Battery Select (JB10) 3.8 Memory Base Address Select (JB11) 3.9 Memory Option Configuration (JB12) | GENERAL INFORMATION  1.1 Introduction 1.2 DSTD Series General Description 1.3 DSTD-703 Features  FUNCTIONAL HARDWARE DESCRIPTION  2.1 Introduction 2.2 Block Diagram Description 2.2.1 STD BUS Interface 2.2.2 Memory Decode Logic 2.2.3 Memory 2.2.4 I/O Decode Logic 2.2.5 Counter/Timer Controller 2.2.6 Parallel Ports 2.2.7 Real Time Clock 2.2.8 Battery Back Up 2.2.9 Brown-Out Detector 2.3 Z80 Interrupts 2.3.1 Interrupt Overview 2.3.2 Priority Daisy-Chain 2.4 I/O Port Address Summary  USER SELECTABLE OPTIONS  3.1 Introduction 3.2 Counter/Timer Configuration (JB1) 3.3 I/O Port Address Select 3.4 Parallel Ports (JB3,JB4) 3.4.1 Modes of Operation 3.4.2 Latch Input 3.4.3 Transparent Input Mode 3.4.4 Latched Output 3.4.5 Transparent Input Mode 3.4.5 Transparent Dutput 3.4.6 Latched Bi-directional Mode 3.4.7 Transparent Bi-directional Mode 3.4.7 Transparent Bi-directional Mode 3.5 +5V Only Charge Option (JB5) 3.6 Bytewide Memory Socket Configuration (JB6,JB7,JB8,JB9) 3.7 On-Board Battery Select (JB11) 3.9 Memory Base Address Select (JB11) 3.9 Memory Base Address Select (JB11) 3.9 Memory Option Configuration (JB12) | NUMBER   GENERAL INFORMATION   1 - |

| 4.0      |                                                                                                          | SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                          | 4 - 1                                   |  |

|----------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--|

|          | 4.1.3<br>4.1.5<br>4.1.5<br>4.1.7<br>4.1.8<br>4.2.1<br>4.2.3<br>4.3.3<br>4.3.3<br>4.3.3<br>4.3.3<br>4.3.3 | Functional Specifications Word Size Cycle Time I/O Port Addressing Real Time Clock Memory Enable Bit Eight Bit Parallel Ports Counter/Timer Interrupts Electrical Specifications STD BUS Interface Operating Temperature Power Supply Requirements Mechanical Specification Card Dimensions STD BUS Edge Connector Mating BUS Connector Counter/Timer Connector Mating Connector Parallel Port Connector Parallel Port Mating Connector | 111112222222233333333333333333333333333 |  |

| 5.0      |                                                                                                          | FACTORY NOTICES                                                                                                                                                                                                                                                                                                                                                                                                                         | 5 - 1                                   |  |

|          | 5.1<br>5.2                                                                                               | Factory Repair Service<br>Limited Warranty                                                                                                                                                                                                                                                                                                                                                                                              | 5 <b>-</b> 1<br>5 <b>-</b> 1            |  |

|          |                                                                                                          | APPENDICES                                                                                                                                                                                                                                                                                                                                                                                                                              |                                         |  |

| APPENDIX | A                                                                                                        | Option Jumper Summary                                                                                                                                                                                                                                                                                                                                                                                                                   |                                         |  |

| APPENDIX | В                                                                                                        | STD-Z80 BUS Signals                                                                                                                                                                                                                                                                                                                                                                                                                     |                                         |  |

| APPENDIX | С                                                                                                        | Parts List                                                                                                                                                                                                                                                                                                                                                                                                                              |                                         |  |

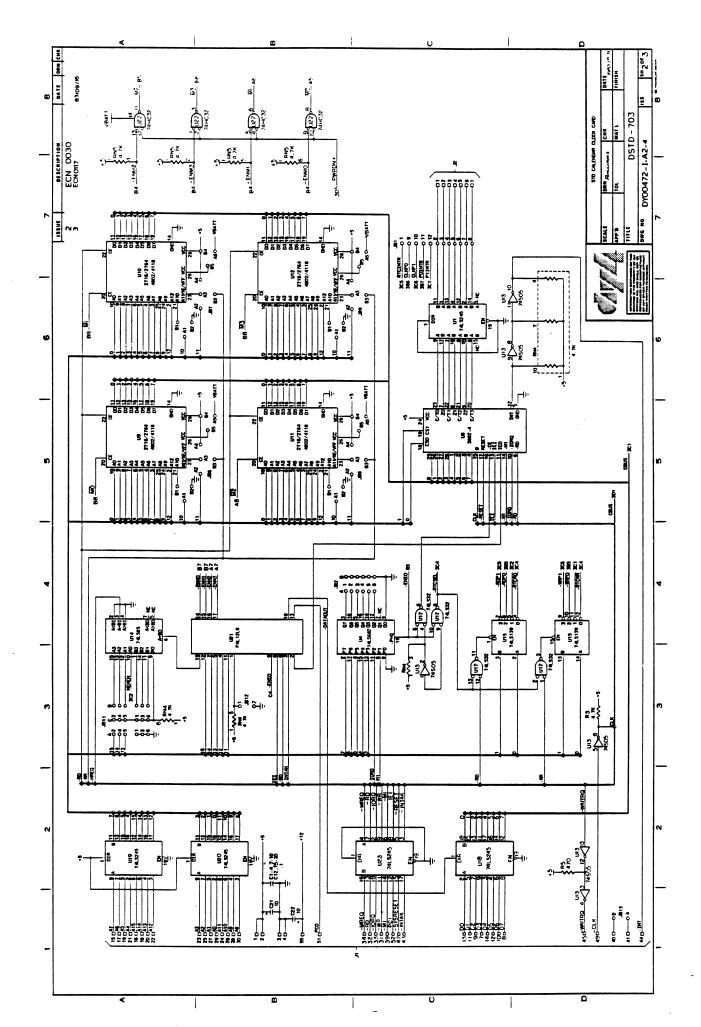

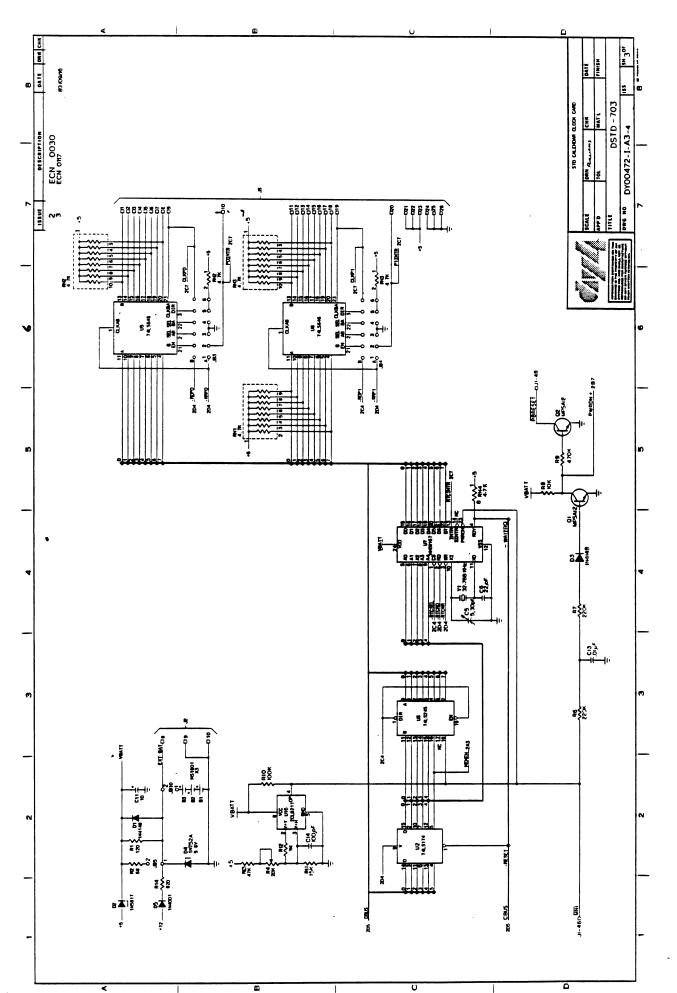

| APPENDIX | D                                                                                                        | Schematic                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         |  |

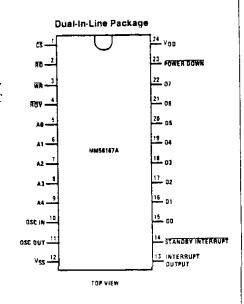

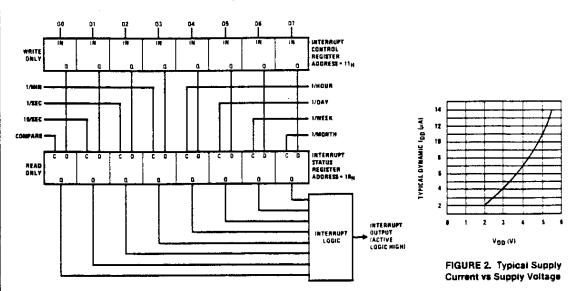

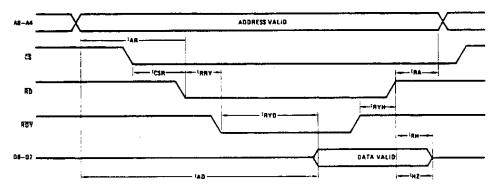

| APPENDIX | E                                                                                                        | Data Sheets MM58167A Real Time Cloc<br>Data Sheets 74LS64X Parallel Port D                                                                                                                                                                                                                                                                                                                                                              |                                         |  |

|          |                                                                                                          | LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                         |                                         |  |

| Figure 1 | -1                                                                                                       | DSTD-703 MODULE                                                                                                                                                                                                                                                                                                                                                                                                                         | 1 - 3                                   |  |

| Figure 2 | <b>-</b> 1                                                                                               | DSTD-703 FUNCTIONAL BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                       | 2 - 4                                   |  |

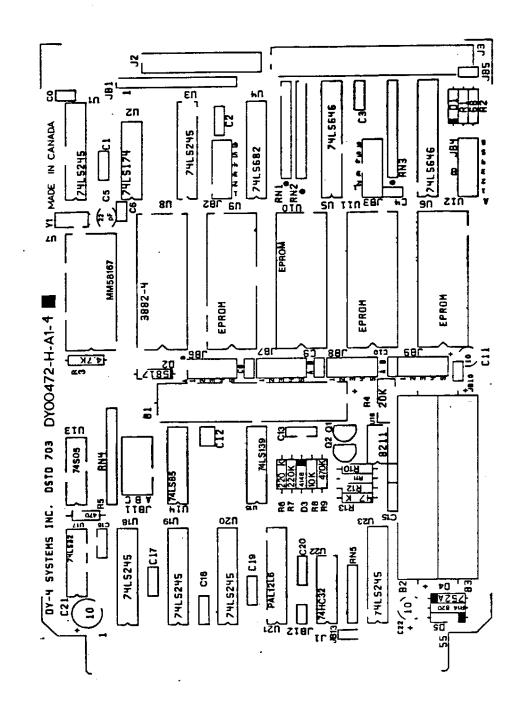

| Figure C | <b>-</b> 1                                                                                               | DSTD-703 Silk Screen                                                                                                                                                                                                                                                                                                                                                                                                                    | c <b>-</b> 3                            |  |

\* =

# LIST OF TABLES

| Table 2-1  | Port Assignments and Definitions  | 2 | _ | 5  |

|------------|-----------------------------------|---|---|----|

| Table 3-1  | CTC Connector Pin Assignment      | 3 | - | 1  |

| Table 3-2  | JB2 Port Address Pin Assignments  | 3 | - | 2  |

| Table 3-3  | I/O Port Configuration            | 3 | _ | 3  |

| Table 3-4  | I/O Port Device Selection Options | 3 | _ | 3  |

| Table 3-5  | Port Connector Pin Assignment     | _ | - |    |

| Table 3-6  | Jumper Block (JB6 and JB9)        | 3 | _ | 6  |

|            | Pin Assignment                    |   |   |    |

| Table 3-7  | Sample Port Configuration         |   | - |    |

| Table 3-8  | Memory Socket/Jumper Block        | 3 | - | 9  |

|            | Assignment                        |   |   |    |

| Table 3-9  | Memory Socket Configuration       |   |   | 10 |

| Table 3-10 | Memory Range Select               |   |   | 11 |

| Table 3-11 | Memory Base Address Select        | 3 | _ | 11 |

#### SECTION 1

#### 1.0 GENERAL INFORMATION

#### 1.1 Introduction

The DSTD-703 provides a Real Time Calendar Clock, two fully buffered 8 bit parallel ports and a 4 channel Counter/Timer.

These are also provisions for 4 bytewide sockets which may be placed anywhere in the processor memory space Modulo 8K.

Full Z80 mode 2 interrupts are supported by the DSTD-703.

The Brown-out detector causes a "System Reset" when +5 volt rail dips below 4.7Volts. This ensures that the computer system does not latch up in an unknown state due to momentary power dips.

#### 1.2 DSTD Series General Description

The DSTD was designed to satisfy the need for low cost OEM microcomputer modules. The DSTD-Z80 BUS uses a motherboard interconnect system concept. The modules for the STD-Z80 BUS are a compact 4.5 x 6.5 inches which provides for system partitioning by function, e.g. CPU, Memory, I/O, etc. This smaller module size makes system packaging easier, while increasing MOS-LSI densities provide high functionality per module.

#### 1.3 DSTD-703 Features

- Calendar/Clock with MONTH, DAY of month, DAY of week, HR, MIN, SEC, 1/100 SEC, 1/10000 SEC,

- 56 bits of battery-back up RAM available on the clock chip

- Ni-Cad battery backup @ 200 mAHr configurable for external battery

- 4 independent programmable interval timers/counters

- Daisy-chain Interrupt capability

- Brown-out detector

- 4-28 pin sockets for bytewide ROM/EPROM and RAM

- bytewide memory may be enabled/disabled under software control

- 16 pin Bi-directional parallel port with interrupt capability. This can drive the DSTD-ACC-RDSM directly for a

date/time display

- STD BUS compatible board

1 - 2

FIGURE 1-1 DSTD-703 MODULE

#### SECTION 2

#### 2.0 FUNCTIONAL HARDWARE DESCRIPTION

#### 2.1 Introduction

The DSTD-703 contains a crystal controlled MM58167A Calendar/Clock chip to provide the date time function. With software support, this card can easily drive an external 7 segment LED display card (DSTD-ACC-RDSM) for a date and time display.

The fully charged Ni-Cad battery will run the Calendar/ Clock for over one year without need for recharge.

The programmable interrupt timer is implemented with a Z80-CTC. It may be connected to user devices via a 10 pin connector for Interrupt or counter capabilities.

The 16 bit parallel port is general purpose. A 26 pin connector is provided for interface purposes.

The Brown-out detector causes a "System Reset" when +5 volt rail dips below 4.7V. This ensures that the computer system does not latch up in an unknown state due to momentary power dips.

#### 2.2 Block Diagram Description

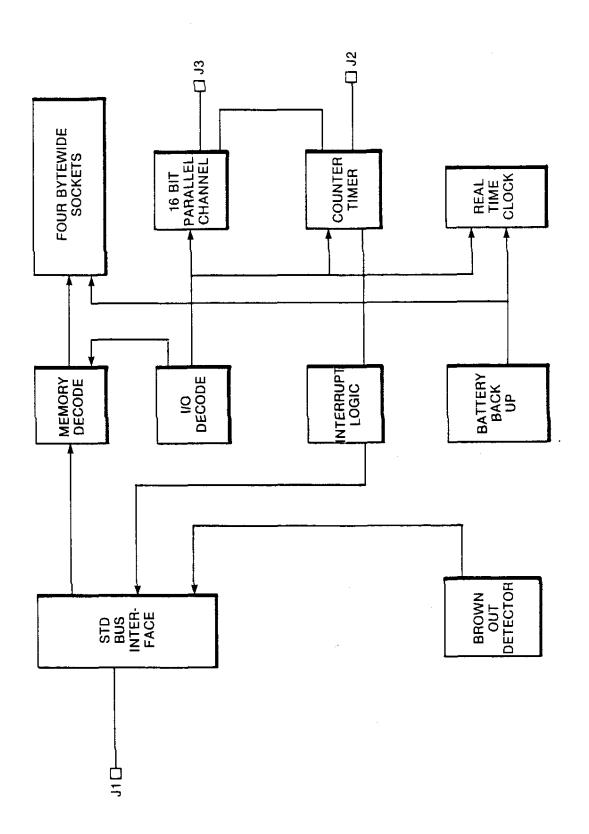

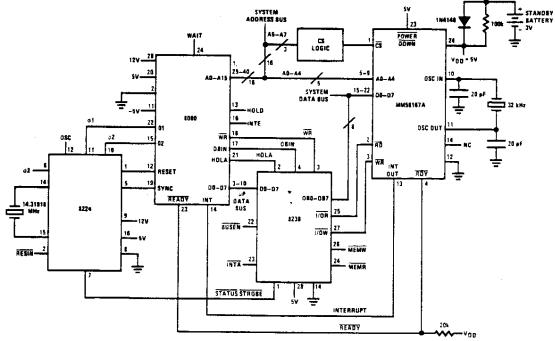

The block diagram of the DSTD-703, Figure 2-1, illustrates the flow of system address, data and control signals. The following paragraphs describe the function of each of the major blocks.

#### 2.2.1 STD BUS Interface

The STD BUS Interface consists of an assortment of circuitry which gates various bus control signals including interrupt requests, daisy-chained priority In/Out, Clock, system reset, M1, IORQ, read and interrupt acknowledge between the BUS and the onboard peripheral chips. The STD BUS Interface also includes address buffers, bi-directional data bus transceivers and I/O port address decoder with associated jumper block for I/O address programming by the user.

#### 2.2.2 Memory Decode Logic

This section consists of a 74LS85 and PAL. The 74LS85 configures the base memory address and memory address range for the DSTD-703. The PAL decodes the 5 high order memory addresses and generates the appropriate chip selects when the DSTD-703 memory is accessed. The PAL provides for two types of memory decoding.

The first assumes 2K devices in the memory sockets. The second is user definable. (see Section 3 for further details)

#### 2.2.3 Memory

The DSTD-703 has been designed to accommodate any combination of the bytewide RAM, ROM, and EPROM devices. Four 28-pin sockets have been provided, each of which may be strapped for any of the allowable memory types. These user-selectable options are fully described in Section 3.

#### 2.2.4 I/O Decode Logic

This section consists of a 74LS682, a 74LS139 and some SSI gates. It provides the chip select for the CTC and read and write strobes for the parallel port and (RTC) Real Time Clock.

#### 2.2.5 Counter/Timer Controller

The Counter/Timer Controller (MK3882/Z80-CTC) provides four independent, programmable channels for either software or hardware controlled counting and timing functions. Each channel can be configured by the CPU for various modes of operation and the built-in daisy-chain priority interrupt logic provides for automatic, independent interrupt vectoring.

The Trigger inputs and Zero Count outputs are buffered and brought out to a connector for external hardware control. A strapping option has also been included to permit any or all of the four CTC channels to be cascaded for long count sequences.

Section 3 provides the necessary information for utilizing this option. For a complete description of CTC operation, refer to the Mostek MK3882 or Zilog Z80-CTC Technical Manual or Appendix A-11 of this manual.

#### 2.2.6 Parallel Ports

The DSTD-703 has two parallel ports. These ports are implemented using octal transceiver chips. The jumper blocks associated with the ports are used to "program" the transceivers for appropriate operations. A data sheet for the 74LS646 is included in Appendix E of this manual.

#### 2.2.7 Real Time Clock

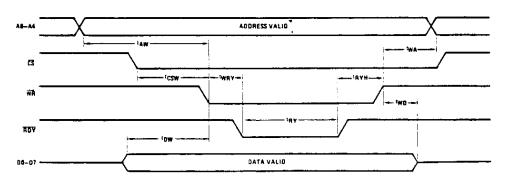

The Real Time Clock is implemented using an MM58167A calendar/clock chip. It also provides 56 bits of battery backed up RAM. Addressses to the RTC chip are first latched by a 74LS174 before they are presented to the RTC. This method takes up only

two I/O addresses to communicate to the RTC, therefore freeing I/O addresses on the STD BUS.

#### 2.2.8 Battery Back Up

Nickel-Cadmium batteries provide the battery back up function. The batteries will be charged continuously when power is applied to the DSTD-703.

#### 2.2.9 Brown-Out Detector

This circuit detects when voltage drops below 4.7V, when this occurs a push button reset is generated. The software when reset, should check for a brown-out condition by reading bit 7 of I/O address base +1; the software then continues with the reset routine or goes into the brown-out routine.

#### 2.3 Z80 Interrupts

#### 2.3.1 Interrupt Overview

Interrupt capability is provided to allow peripheral devices to suspend CPU operation in an orderly manner and force the Z80 processor to start executing a specific peripheral service routine. On completion of the service routine, the Z80 returns to the operation from which it was interrupted.

#### 2.3.2 Priority Daisy-Chain

The CTC is a Z80 peripheral device and as such includes daisy-chained priority interrupt logic which automatically provides the programmed interrupt vector (from the highest priority interrupting device) to the processor during an interrupt acknowledge. Look-ahead priority logic has been designed to ensure that more than one peripheral card (from an interrupt speed standpoint) may be included in a larger interrupt priority loop. This is accomplished by providing both ends of the board daisy chain logic (PCI and PCO) at the edge card connector J1, so that the card priority within a several card priority daisy-chained system may be implemented. The "high" and "low" state of the PCI and PCO determines the card priority in the same fashion as for the individual peripheral chips.

DSTD-703 BLOCK DIAGRAM

#### 2.4 I/O PORT DEFINITION SUMMARY

The I/O base address port is set at 50H by the factory. However this base address may be re-configured by the user.

The following table describes the port assignments and their use. The mnemonics used to represent the control functions of the individual bits are described at the end of the table.

TABLE 2 - 1

PORT ASSIGNMENTS AND DEFINITIONS

| ADDR       | ACCESS | BIT7  | BIT6        | BIT5     | BIT4    | BIT3   | BIT2  | BIT1        | BITO  |

|------------|--------|-------|-------------|----------|---------|--------|-------|-------------|-------|

|            |        |       | <del></del> |          |         |        |       | <del></del> |       |

| BASE<br>+0 | R/W    |       | Real Tin    | ne Clock | Chip Da | ata Po | rt    |             |       |

| +1         | R/W    |       |             | MEMEN    | RTCA4   | RTCA3  | TRCA2 | RTCA1       | RTCAO |

| +1         | R/O    | BRNOT |             |          |         |        |       |             |       |

| +2         | R/W    |       | Parallel    | Port 0 D | ata Po  | rt     |       |             |       |

| +3         | R/W    |       | Parallel    | Port 1 D | ata Po  | rt     |       |             |       |

| +4         | R/W    |       | CTC         | CHNL O   |         |        |       |             |       |

| +5         | R/W    |       | CTC         | CHNL 1   |         |        |       |             |       |

| +6         | R/W    |       | CTC         | CHNL 2   |         |        |       |             |       |

| +7         | R/W    |       | CTC         | CHNL 3   |         |        |       |             |       |

MEMEN: memory enable: is set High to enable on-board memory

RTCA4-0: RTC Address 4-0: is used to select the address for the Real Time Clock Chip.

BRNOT: Brown Out: is low when a brown out has occurred.

#### SECTION 3

#### 3.0 USER SELECTABLE OPTIONS

#### 3.1 Introduction

The DSTD-703 incorporates many strapping options to provide the user with a high degree of flexibility in system configurations. This section describes the use of the switch jumper option.

#### 3.2 Counter/Timer Configuration (JB1)

The four Counter/Timer channels may be cascaded for extended counting and timing functions. Table 3-1 shows the jumper pin numbers and the edge connector numbers for the CTC. Refer to the MK3882 Technical Manual or the Zilog Data Book for a complete description of CTC operation or Appendix A-11 of this manual.

TABLE 3 - 1

CTC CONNECTOR PIN ASSIGNMENT

| SIGNAL  |   | JUMPER | BLOCK | EDGE | CONNEC | TOR |

|---------|---|--------|-------|------|--------|-----|

| NAME    |   | JB1    |       |      | J2     |     |

| C/TO    | I | 2      |       |      | 1      |     |

| ZCO     | 0 | 3      |       |      | 2      |     |

| C/T1    | I | 4      |       |      | 3      |     |

| ZC1     | 0 | 5      |       |      | 4      |     |

| C/T2    | I | 6      |       |      | 5      |     |

| ZC2     | 0 | 7      |       |      | 6      |     |

| C/T3    | I | 8      |       |      | 7      |     |

| CLKPO   |   | 9      |       |      |        |     |

| CLKP1   |   | 10     |       |      |        |     |

| POINTR  |   | 11     |       |      |        |     |

| PIINTR  |   | 12     |       |      |        |     |

| RTCINTR |   | 13     |       |      |        |     |

The CTC may also be used to generate interrupts on status changes during parallel I/O transfers. This will be discussed in more detail in the following sections.

#### 3.3 I/O Base Address Select (JB2)

The DSTD-703 occupies 8 contiguous I/O addresses. Its position in the I/O address space is determined by JB2 connections. Table 3-2 shows the jumper block pin numbers and the corresponding processor address bits used in the comparison. Installing a jumper implies a logic '0'. No jumper implies a logic '1'.

#### Examples:

- 1) Base address B8H requires jumpers between pins 2A & 2B and 6A & 6B

- 2) Base address 50H requires jumpers between pins 1A & 1B, 3A & 3B, 5A & 5B and 6A & 6B

The board is shipped from the factory wired for address 50H.

Table 3 - 3 illustrates the function of each of the 8 individual I/O Ports assigned to the DSTD-703.

TABLE 3 - 2

JB2 PORT ADDRESS PIN ASSIGNMENTS

| PIN | ADDRESS BIT                               |

|-----|-------------------------------------------|

| 1   | A7                                        |

| 2   | A6                                        |

| 3   | A5                                        |

| 4   | A 4                                       |

| 5   | A3                                        |

| 6   | IORQ This jumper must always be installed |

Logic 'O' - Jumper installed

Logic '1' - No Jumper

#### TABLE 3 - 3

#### I/O PORT CONFIGURATION

| Por | rt 1 | Addı | res: | 3  |    |     |    | Port | Fun | ction   |

|-----|------|------|------|----|----|-----|----|------|-----|---------|

|     |      |      |      |    |    |     |    |      |     |         |

| A7  | A 6  | A5   | A4   | AЗ | A2 | A 1 | ΑO |      |     |         |

| Х   | X    | X    | X    | X  | 0  | 0   | 0  | RTC  | -   | Data    |

| X   | Х    | Х    | X    | X  | 0  | 0   | 0  | RTC  | _   | Control |

| Х   | X    | Х    | X    | X  | 0  | 1   | 0  | Port | 0 - |         |

| X   | X    | Χ    | X    | X  | 0  | 1   | 1  | Port | 1 - |         |

| Х   | X    | X    | X    | X  | 1  | 0   | 0  | CTC  | -   | Chan 0  |

| Х   | X    | Х    | X    | X  | 1  | 0   | 1  | CTC  | -   | Chan 1  |

| X   | X    | X    | X    | X  | 1  | 1   | 0  | CTC  | -   | Chan 2  |

| Х   | X    | X    | X    | X  | 1  | 1   | 1  | CTC  | _   | Chan 3  |

Refer to Table 2-1 for the data bit definitions.

#### 3.4 Parallel Ports (JB3, JB4)

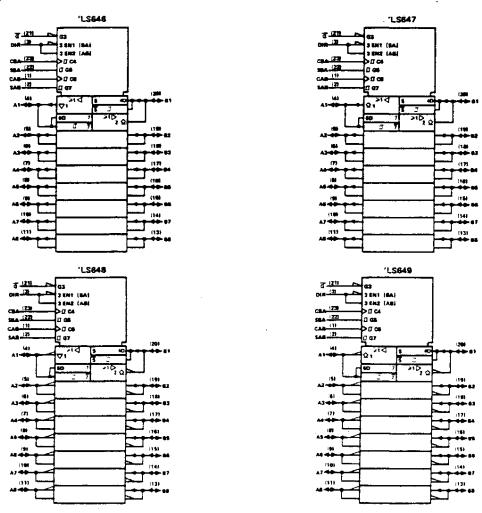

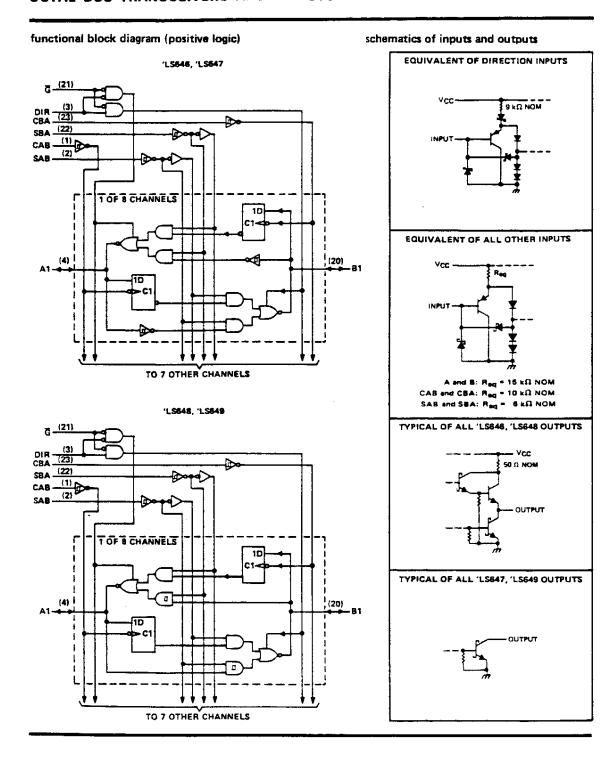

The DSTD-703 has two independent 8-bit parallel ports. These ports are implemented using the 74LS646 to 74LS649 series of integrated circuits. They are octal transceivers with latches. Table 3 - 4 lists the basic functions of these chips. (Refer to Appendix E).

TABLE 3 - 4

I/O PORT DEVICE SELECTION OPTIONS

|         | DATA PATH | OUTPUT         |

|---------|-----------|----------------|

| 74LS646 | TRUE      | 3 - State      |

| 74LS647 | TRUE      | Open Collector |

| 74LS648 | INVERTING | 3 State        |

| 74LS649 | INVERTING | Open Collector |

Note: When using open collector devices, Resister Network RN4 must be used.

Both parallel ports are accessed through one connector J3. Table 3-5 shows the pinouts for the connector.

TABLE 3 - 5

PORT CONNECTOR PIN ASSIGNMENT

| PORT SIGNAL                                             | PORT A                               | PORT B                                       |

|---------------------------------------------------------|--------------------------------------|----------------------------------------------|

| Data 0 Data 1 Data 2 Data 3 Data 4 Data 5 Data 6 Data 7 | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | 11<br>12<br>13<br>14<br>15<br>16<br>17<br>18 |

| CLKP<br>CONTROL<br>GND<br>+5V                           | 9<br>10<br>24,25,26<br>21,22,23      | 20                                           |

## 3.4.1 Modes of Operation

Each parallel port has six basic modes of operation. Those modes represent the most common configurations.

- 1) Latch Input Mode

- 2) Transparent Input Mode

- 3) Latch Output Mode

- 4) Transparent Output Mode

- 5) Latched Bi-directional Mode

- 6) Transparent Bi-directional Mode

Note that latched bi-directional mode typically uses both ports. Table 3 - 7 summarizes some of the port configurations discussed in the following section.

#### 3.4.2 Latch Input

In this mode data is clocked into the port register by an external device using the "CLKP" signal. Data is clocked on rising edge of "CLKP". In some applications it is necessary to inform the processor that valid or new data is available. This can be accomplished using the CTC.

Connect the "CLKP" signal to a channel on the counter/timer. The "CLKP" signal for port A is pin 9 and for port B is pin 10 on the CTC jumper block JB1. This pin can be connected to a free CTC channel (CH O / JB1-2; CH 1 / JB1 -4; CH 2 / JB1 -6; CH 3 / JB1-8). The CTC channel is then used in the counter mode to report positive transitions of the "CLKP" signal.

#### 3.4.3 Transparent Input Mode

In this mode the data is read directly from the port. This mode is typically used for scanning switches or other relatively static information - or when there is no clock available. Again the control signal, with the CTC may be used to indicate "valid data" as discussed in Section 3.5.2.

## 3.4.4 Latched Output

In this mode the processor writes data into the port. The CONTROL signal may be used in one of several ways. First, it may be used by the external device to enable the port. The CONTROL signal is connected to the ENABLE input of the port register. (Connect pins A2 and B2 on the appropriate port jumper block). Second, the control signal can be used as a strobe in the external device to indicate valid data. (Note that in latched output mode it cannot be used to clock data into the external device-use transparent output mode if this function is required). To use the CONTROL signal as a strobe connect pins A2 and A1 on the port jumper block. Third, the CONTROL signal may be connected to a channel of the CTC and used by the external device to inform the processor that it is ready for new data. The strapping options allow many other handshake arrangements including combinations of the above.

#### 3.4.5 Transparent Output

This mode is used when strobing data into an external device. The CONTROL signal is connected to the write port line (pins A2 and A1 of the port jumper block). In this mode the port acts simply as a buffer. Data is clocked on the rising edge of the CONTROL signal.

#### 3.4.6 Latched Bi-directional Mode

This mode typically requires the use of both ports. Port A for the OUT direction and Port B for the IN direction. The ports are connected together in the edge connector (J3). The external device controls the direction of the data flow on the bidirectional bus. The external device clocks data in the B port using CLKP.

CLKPB can be connected in the CTC to provide an indication to the processor that new valid data is available from the external

device. The /RDPB signal is connected to the CONTROL B signal to inform the external device when the processor has read the data from the port. The processor outputs data to the external device by writing it to Port A. /WRPA is connected to CLKPA (JB3-B6 to JB3-A1). This is used to inform the external device that new data is available from the processor. The external device enables the data onto the bus using the CONTROLA line. The CONTROLA line can be connected to a CTC channel to let the processor know when the external device has taken the data.

#### 3.4.7 Transparent Bi-directional Mode

This mode provides simple bi-directional capability. The port is enabled at all times and the direction is controlled by the RDPA signal; i.e., the direction is out unless the processor is "reading" the port. The /RDPA is also connected to the control signal to enable the drivers in the external device. The CLKPA line can be either connected to the CTC or to the /WRDA signal to provide handshake signals in the desired direction. Other configurations are possible. For example the out data can be latched instead of transparent.

Jumper blocks JB3 and JB4 are used to configure Port A and Port B respectively. Table 3-7 shows connector pinouts for both ports (J3).

Port A has the I/O address 52H and Port B has 53H.

Table 3 - 6 describes the Jumper Block pin functions.

TABLE 3 - 6

JUMPER BLOCK (JB3 AND JB4) PIN ASSSIGNMENT

| PIN | NAME          | FUNCTION                                                                                             |

|-----|---------------|------------------------------------------------------------------------------------------------------|

| B 1 | RDP (A/B)     | Read port signal from the processor-usually connected to the ENABLE or DIRECTION pins.               |

| A1  | WRP (A/B)     | Write port signal from the processor-usually connected to the CONTROL signal for handshake purposes. |

| B2  | ENABLE (A/B)  | Port chip enable - when low, enables the port.                                                       |

| A2  | CONTROL (A/B) | General purpose signal - for connecting-<br>to external device to CTC or ENABLE.                     |

| В3  | SEL AB        | When low, the "out" direction is transparent. When high, the "out"                                   |

|       |            | direction is latched - strobed by WRP (A/B).                                                                   |

|-------|------------|----------------------------------------------------------------------------------------------------------------|

| A3,A4 | GND        | Used for option selection.                                                                                     |

| В4    | SEL BA     | When low, the "in" direction is transparent. When high, the "in" direction is latched - strobed by CLKP (A/B)> |

| B5    | DIRECTION  | Controls the direction of the port when enabled - low is in, high is out.                                      |

| A5,A6 | +5V        |                                                                                                                |

| В6    | CLKP (A/B) | External strobe for clocking data into the port.                                                               |

TABLE 3 - 7

SAMPLE PORT CONFIGURATION

| MODE                          | JB6 AND/OR JB9<br>JUMPER CONNECT:                   |                         | FUNCTION                                                                                             |

|-------------------------------|-----------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------|

| Latched Input                 | A4-B5<br>B1-B2<br>B4-A5                             |                         | Direction in port enable latched mode.                                                               |

| Transparent Input             | A4-B5<br>B1-B2<br>B4-A4                             |                         | Direction in Port enable Transparent.                                                                |

| Latched Output                | B5-A5<br>B2-A3<br>or (B2-A2)<br>or (A1-A2)<br>B3-A5 |                         | Direction out Enable on When external device controls enable Strobe for external device Latched Mode |

| Transparent Output            | B5-A5<br>B2-A3<br>A1-A2<br>B3-A3                    |                         | Direction out enable on write strobe for external device transparent mode                            |

| Latched<br>Bi-directional     | Port A                                              | Port B                  |                                                                                                      |

|                               | B5-A5                                               | A4-B5                   | Direction                                                                                            |

| (JB3                          | -B6/JB3-A1)                                         | B1-A2                   | Handshake                                                                                            |

|                               | B2-A2                                               |                         | Out enable                                                                                           |

| (JB1                          | -11/JB1-8)                                          |                         | Handshake                                                                                            |

|                               | (JB1                                                | -10/JB1-6)              | Handshake                                                                                            |

|                               |                                                     | B1-A2                   | In enable                                                                                            |

| Transparent<br>Bi-directional |                                                     | B1-B5<br>B2-A3<br>B1-A2 | Direction<br>Port enable<br>Handshake                                                                |

#### 3.5 5V Only Charge Option (JB5)

When 12 volts is not available to the DSTD-703, install JB5 for proper battery charging operation.

# 3.6 Bytewide Memory Socket Configuration (JB6, JB7, JB8, JB9)

The DSTD-703 incorporates four 28-pin sockets which can be independently configured to accept a variety of pin compatible memory devices. Table 3-8 lists each socket, its corresponding jumper block, and its address space for the standard configuration. Table 3-9 illustrates the necessary jumper connections for configuring a socket to accept a particular memory device.

The DSTD-703 is shipped from the factory with a memory decoding PAL (U22) which supports 2K byte chips. The factory can supply memory decoding PAL's on request for other standard configurations using 4K byte and 8K byte chips. Consult the factory for PAL programming details for non-standard requirements.

The base address of memory is selected by the user. (see Section 3-7)

TABLE 3 - 8

MEMORY SOCKET/JUMPER BLOCK ASSIGNMENT

| SOCKET       | ADDRESS             | JUMPER BLOCK |

|--------------|---------------------|--------------|

| U <b>9</b>   | base + 0000 to 07FF | JB6          |

| U10          | base + 0800 to OFFF | JB7          |

| U11          | base + 1000 to 17FF | JB8          |

| U <b>1</b> 2 | base + 1800 to 1FFF | JB9          |

Table 3 - 9 shows the straps necessary to configure the sockets for the different memory types. All the sockets are wired independently, allowing any mix of chips within the addressing constraints.

TABLE 3 - 9

MEMORY SOCKET CONFIGURATION

| MEMORY       | JUMPER<br>CONNECTIONS |                               |  |

|--------------|-----------------------|-------------------------------|--|

| 2758         | OPEN                  | 1 - 3<br>4 - 6<br>2,7,5       |  |

| 2759         | OPEN                  | 1 - 4<br>4 - 6<br>2,7,3,5     |  |

| 2716         |                       | 1A - 1B<br>3A - 4A<br>5B - 4A |  |

| 2732         |                       | 1A - 1B<br>3A - 2A<br>5B - 4A |  |

| 2764         |                       | 1A - 1B<br>3A - 2A<br>5B - 4A |  |

| 4118<br>4801 |                       | 1B - 2B<br>3A - 3B<br>5B - 4A |  |

| 4802         |                       | 1B - 1A<br>3A - 3B<br>5B - 4A |  |

JUMPER BLOCK LAYOUT FOR J6, J7, J8, J9,

A B o o o o o o o

#### 3.7 On Board Battery Select (JB10)

The DSTD-703 allows the user to select between on-board battery or an external battery. The on-board battery is selected by installing a jumper at JB10. The external battery is selected by connecting the positive side of the battery to external connector J2 pin 8 and the negative side to J2 pin 10.

#### 3.8 Memory Base Address Select (JB11)

The board's position in the processor's memory address space is selected by using hardwired jumpers. The board can be selected to occupy an 8K, 16K or 32K range of address by JB11. JB11 also configures the base address of the card to any 8K, 16K or 32K boundary.

#### **TABLE 3 - 10**

#### **MEMORY RANGE SELECT**

| 32K | install | 2B-2A; | 4B-4C; | 5B-5C; | 3B-3C; | 6B-6C |

|-----|---------|--------|--------|--------|--------|-------|

|     | install |        |        |        |        |       |

| 8K  | install | 2B-2A; | 4B-4A: | 5B-5A  |        |       |

#### **TABLE 3 - 11**

#### MEMORY BASE ADDRESS SELECT

#### 32K Range

| Base at  | 0000H:<br>8000H:                     | install<br>install                       |                                              | 1B - 1A<br>1B - 1C                       |

|----------|--------------------------------------|------------------------------------------|----------------------------------------------|------------------------------------------|

| 16K Rang | ge                                   |                                          |                                              |                                          |

| Base at  | 0000H:<br>4000H:<br>8000H:<br>C000H: | install<br>install<br>install<br>install | 1B - 1A;<br>1B - 1A;<br>1B - 1C;<br>1B - 1C; | 3B - 3A<br>3B - 3C<br>3B - 3A<br>3B - 3C |

#### 8K Range

| Base | at | 0000H: | install | 1B - | 1A; | 3B - 1A; | 6B <del>-</del> | 6A |

|------|----|--------|---------|------|-----|----------|-----------------|----|

|      |    | 2000H: | install | 1B - | 1A; | 3B - 1A; | 6B <b>-</b>     | 6C |

|      |    | 4000H: | install | 1B - | 1A; | 3B - 1C; | 6B <b>–</b>     | 6A |

|      |    | 6000H: | install | 1B - | 1A; | 3B - 1C; | 6B <b>-</b>     | 6C |

|      |    | 8000H: | install | 1B - | 1C; | 3B - 1A; | 6B 🗕            | 6A |

|      |    | AOOOH: | install | 1B - | 1C; | 3B - 1A; | 6B 🗕            | 6C |

|      |    | C000H: | install | 1B - | 1C; | 3B - 1C; | 6B <b>–</b>     | 6A |

|      |    | EOOOH: | install | 1B - | 1C; | 3B - 1C; | 6B <b>-</b>     | 6C |

## 3.9 Memory Option Configuration (JB12)

This Jumper Block is available as a user defined function. It is an input to the memory decoder and may be used to select a non-standard user defined memory map.

#### 3.10 DMA Chain Enable (JB13)

This Jumper Block is used only when a dy-4 SYSTEMS INC. backplane is used. It provides a path through this card for the DMA chain.

#### SECTION 4

#### 4.0 SPECIFICATIONS

#### 4.1 Functional Specifications

#### 4.1.1 Word Size

Data 8 bits I/O Addressing 8 bits

4.1.2 Cycle Time

Min Max DSTD-703 - 2.5 250kHz 2.5MHz DSTD-703 - 4.0 250kHz 4.0MHz

#### 4.1.3 I/O Port Addressing

The DSTD-703 occupies 8 contiguous I/O addresses. The base address is user selectable by JB2 (see Section 3.2). Two I/O addresses are used for the Real Time Clock (RTC) chip and memory enable port; two for the two 8 bit parallel port and four for the CTC.

#### 4.1.4 Real Time Clock

The RTC occupies two I/O addresses on the DSTD-703.

At base + 0 is the data port base + 1 is the address latch that controls the address codes to the RTC chip.

The appendix contains a data sheet for the RTC chip.

Example for reading time. HH/MM/SS

A,2; LD(51H),A; select counter-seconds A,(50H); read seconds from RTC chip (SEC),A; store in location (SEC) OUT ΙN LD LD A,3 (51H), A ; select counter-minutes A,(50H) ; read minutes (MIN), A ; store in location (MIN) OUT IN LDLD A,4 OUT (61H),A ; select counter-hours IN A,(50H) ; read hours (HRS), A ; store in location (HRS) LD

SPECIFICATIONS DSTD-703

#### 4.1.5 Memory Enable Bit

The memory enable bit is located at I/O address base +1 bit 5. Memory is enabled when this bit is set High, and disabled when it is set Low. This bit is set low by reset.

#### Eight Bit Parallel Ports 4.1.6

There are two general purpose 8 bit parallel ports on the DSTD-703. They may be configured to run in several modes (refer to Section 3.3). Port 0 is controlled via I/O address base +2 and Port 1 is controlled via I/O address base +3.

#### 4.1.7 Counter/Timer

The counter/timer controller is located at I/O address base +4 through to base +7. Refer to Section 3.1 for configuration description.

#### 4.1.8 Interrupts

The DSTD-703 supports vectored interrupt generation via the CTC chip. The interrupt vector is programmable upon initialization. Also the DSTD-703 supports full daisy chain interrupt priority.

#### 4.2 Electrical Specifications

#### 4.2.1 STD Bus Interface

one 74LS load max. Bus Inputs:

$I_{OL}$  24 mA min @  $V_{OL}$  0.5 Volts  $I_{OH}$  15 mA min @  $V_{OH}$  2.4 Volts Bus Outputs:

#### 4.2.2 Operating Temperature

O degree Celsius to 60 degrees Celsius

#### 4.2.3 Power Supply Requirements

+5VDC 5% @ 1.0 Amps Max +12VDC 5% @ 0.02 Amps Max

## 4.3 Mechanical Specification

4.3.1 Card Dimensions

4.5 inches (11.43 cm.) wide by 6.50 inches (16.52 cm.) long 0.48 inches (1.22 cm.) maximum height 0.062 inches (0.16 cm.) printed circuit board thickness

4.3.2 STD Bus Edge Connector

56 Pin dual readout: 0.125 inch centers

4.3.2.1 Mating Bus Connector

Viking 3VH28/1CES (PCB)

Viking 3VH28/1CND5 (Wire wrap)

Viking 3VH28/1CN5 (Solder lug)

4.3.3 Counter/Timer Connector

10 Pin Dual 0.100 inch grid

4.3.3.1 Mating Connector

Flat cable Ansley 609-100M or equivalent

4.3.4 Parallel Port Connector

1 - 26 Pin Dual 0.100 inch grid flat cable type male connector (header)

4.3.4.1 Parallel Port Mating Connector

Ansley 609 - 2600M (flat cable) or equivalent

Winchester PGB26A - housing ) For use with Winchester 100-700C0s - contacts ) discrete wires

FACTORY NOTICES DSTD-703

#### SECTION 5

#### 5.0 FACTORY NOTICES

#### 5.1 Factory Repair Service

In the event that difficulty is encountered with this unit, it may be returned directly to dy-4 for repair. This service will be provided free of charge if the unit is returned within the warranty period. However, units which have been modified or abused in any way will not be accepted for service, or will be repaired at the owner's expense.

When returning a circuit board, place it inside the conductive plastic bag in which it was delivered to protect the MOS devices from electrostate discharge. THE CIRCUIT BOARD MUST NEVER BE PLACED IN CONTACT WITH STYROFOAM MATERIAL. Enclose a letter containing the following information with the returned circuit board:

Name, address and phone number of purchaser Date and place of purchase Brief description of the difficulty

Mail a copy of this letter SEPARATELY to:

dy-4 SYSTEMS INC.,

888 Lady Ellen Place,

Ottawa, Ontario

K1Z 5M1, Canada

Securely package and mail the circuit board, prepaid and insured, to the same address.

#### 5.2 Limited Warranty

dy-4 warrants this product against defective materials and workmanship for a period of 90 days. This warranty does not apply to any product that has been subjected to misuse, accident, improper installation, improper application, or improper operation, nor does it apply to any product that has been repaired or altered by other than an authorized factory representative.

There are no warranties which extend beyond those herein specifically given.

#### NOTICE

The antistatic bag is provided for shipment of the dy-4 PC boards to prevent damage to the components due to electrostatic discharge.

Failure to use this bag in shipment will VOID the warranty.

# APPENDIX A OPTION JUMPER SUMMARY

# APPENDIX A

# OPTION JUMPER SUMMARY

| A-1 | The  | following  | is | а | summary | of | the | DSTD-703 | Option |

|-----|------|------------|----|---|---------|----|-----|----------|--------|

|     | Jump | er Blocks. |    |   |         |    |     |          |        |

| JB1       | Counter/Timer Configuration Block. |

|-----------|------------------------------------|

| JB2       | I/O Base Address Select.           |

| JB3,4     | Parallel Ports.                    |

| JB5       | 5V Only Charge Option.             |

| JB6,7,8,9 | Memory Socket Configuration.       |

| JB10      | On Board Battery Select.           |

| JB11      | Memory Base Address Select.        |

| JB12      | Memory Option Configuration.       |

JB13 DMA Chain Enable.

# A-2 Counter Timer Configuration (JB1)

| JB1 |               |

|-----|---------------|

| 0   | RTC Interrupt |

| 0   | J2-1          |

| 0   | J2-2          |

| 0   | J2-3          |

| o   | J2-4          |

| 0   | J2-5          |

| 0   | J2-6          |

| 0   | J2-7          |

| 0   | J2-8          |

| 0   | CLK PO        |

| 0   | CLK P1        |

| 0   | P1 Interrupt  |

# A-3 I/O Base Address (JB2)

B o o o o o o o A o o o o o o o o o o

| B1  | to | В6 |         | G              | round |

|-----|----|----|---------|----------------|-------|

| A 1 |    |    | Address | Bit            | 7     |

| A2  |    |    | Address | Bit            | 6     |

| A3  |    |    | Address | Bit            | 5     |

| A4  |    |    | Address | Bit            | 4     |

| A5  |    |    | Address | $\mathtt{Bit}$ | 3     |

| A 6 |    |    | /TORO   |                |       |

A-4 Parallel Ports (JB3,4) 1 2 3 4 5 6 B o o o o o A o o o o o A 1 WRP 0/1 B 1 RDP 0/1 A2 P(O/1) INTR B2 G EN (74LS64X) A3 GND В3 SEL A/B (74LS64X) SEL B/A (74LS64X) A 4 В4 GND DIR (74LS64X) A5 +5V B5 CLP 0/1 A6 +5**V** B6 A-5 +5V Battery Charge Option (JB5) o Battery Feed o +5V A-6 Memory Socket Configuration (JB6.7.8.9) В Α Address Bit 10 1 o o Socket pin 21 (A10) Address Bit 11 2 o o GND Socket pin 23 (A11/WE/VPP) 3 o o Write Strobe +5V 4 0 0 +5V VBATT 5 o o Socket pin 26 (VCC)

On Board Battery Select (JB10)

A-7

JB10

Battery o o Battery Feed

#### A-8Memory Base Address Select (JB11) 5 6 1 2 3 C 0 0 0 0 0 0 JB11 В O 0 0 0 0 0 Α 0 0 0 0 0 GND A1,3,6 Address Bit 15 A2 Α4 Address Bit 14 Address Bit 13 A5 B1 Comparator Bit B3 Comparator Bit A3 Comparator Bit B2 B2 В3 B4 Comparator Bit A2 B5 Comparator Bit A1 Comparator Bit B1 В6

# A-9 Memory Option Configuration

C1-C6

JB12

+5V logic '1'

opt input o o GND

#### A-10 DMA Chain Enable (JB13)

JB13

Pin 41 o o Pin 40

#### A-11 Programming The CTC

#### A-11.1 Channel Selection

DSTD products using the Z80 CTC decode the CTC to occupy 4 contiguous port addresses. Writing to the appropriate port address will automatically select the correct register in the CTC.

#### A-11.2 Interrupt Vectors

If any one of the CTC channels is going to be used with its interrupt enabled, an Interrupt Vector must be written to the CTC. The use need only supply the 5 high bits of one vector as the CTC assumes the vector points to 4 contiguous byte pairs corresponding to the 4 channels. Note that DO must equal 0 to indicate that the word being written to the CTC is an interrupt vector; this also requires vectored addresses to start at an even memory locations.

| D7 | D6                                                                                                                               | D5       | D4      | D3 | D2                                                    | D1      | DO   |

|----|----------------------------------------------------------------------------------------------------------------------------------|----------|---------|----|-------------------------------------------------------|---------|------|

| V7 | V 6                                                                                                                              | V5       | V 4     | ٧3 | X                                                     | X       | 0    |

|    | <user< th=""><th>SUPPLIED</th><th>VECTOR&gt;</th><th></th><th><supp< th=""><th>LIED BY</th><th>CTC&gt;</th></supp<></th></user<> | SUPPLIED | VECTOR> |    | <supp< th=""><th>LIED BY</th><th>CTC&gt;</th></supp<> | LIED BY | CTC> |

#### A-11.3 Channel Control Register

The control register bit functions are as illustrated below.

| D <b>7</b> | D6   | D5    | D4    | D3   | D2   | D1    | D0 |

|------------|------|-------|-------|------|------|-------|----|

| INT        |      |       |       |      | LOAD |       |    |

| ENA        | MODE | RANGE | SLOPE | TRIG | TC   | RESET | 1  |

DO = O indicates the byte is an INTERRUPT VECTOR.

DO = 1 indicates the byte is a CONTROL WORD.

D1 = 0 the channel continues current operation.

D1 = 1 the channel is immediately RESET to control word values.

D2 = 0 indicates NO TIME CONSTANT to follow.

D2 = 1 the next I/O byte will be a TIME CONSTANT. (1 to 256)

D3 = 0 timer will FREE-RUN starting on next processor cycle.

D3 = 1 indicates timer will start on EXTERNAL TRIGGER.

D4 = 0 indicates external trigger on NEGATIVE-GOING edge.

D4 = 1 indicates external trigger on POSITIVE-GOING edge.

D5 = 0 indicates prescaler factor of 16. (timer mode only)

D5 = 1 indicates prescaler factor of 256. (timer mode only)

D6 = 0 indicates TIMER mode. (prescaler is enabled)

D6 = 1 indicates COUNTER mode. (prescaler disabled)

D7 = O INTERRUPT DISABLED for that channel.

D7 = 1 INTERRUPT on zero count ENABLED for the channel.

APPENDIX B

STD-Z80 BUS SIGNALS

STD-Z80 BUS PIN OUT AND DESCRIPTION

APPENDIX B

| BUS                       | MNEMONIC                   | DESCRIPTION                                                                                                                                                          |

|---------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           |                            |                                                                                                                                                                      |

| 1                         | 5 V                        | 5Vdc system power                                                                                                                                                    |

| 2                         | 5 V                        | 5Vdc system power                                                                                                                                                    |

| 3                         | GND                        | Ground - System signal ground and DC return                                                                                                                          |

| 4                         | GND                        | Ground - System signal ground and DC return                                                                                                                          |

| 5                         | -5V                        | -5Vdc system power                                                                                                                                                   |

| 6                         | -5V                        | -5Vdc system power                                                                                                                                                   |

| 7                         | D3                         |                                                                                                                                                                      |

| 8                         | D7                         |                                                                                                                                                                      |

| 9<br>10<br>11<br>12<br>13 | D2<br>D6<br>D1<br>D5<br>D0 | Data Bus (Tri-state, input/output active high). D0-D7 constitute an 8-bit bidirectional data bus. The data bus is used for data exchange with memory and I/O devices |

| 14                        | D4                         |                                                                                                                                                                      |

| 15                        | A7                         |                                                                                                                                                                      |