## FEATURES

- Wide Supply Voltage Range 6V to 20V

- Input range 500mV beyond the rails

- Rail-to-Rail Output Swing

- Large DC Voltage Gain 90dB (Typical)

- High slew rate 40V/ $\mu$ s

- Protection Function

- Over Temperature Protection (OTP)

- Over Current Protection (OCP)

- -3dB Bandwidth (unit gain) 30MHz

- $\pm 350$ mA Output Short Circuit Current

- Unity-gain stable

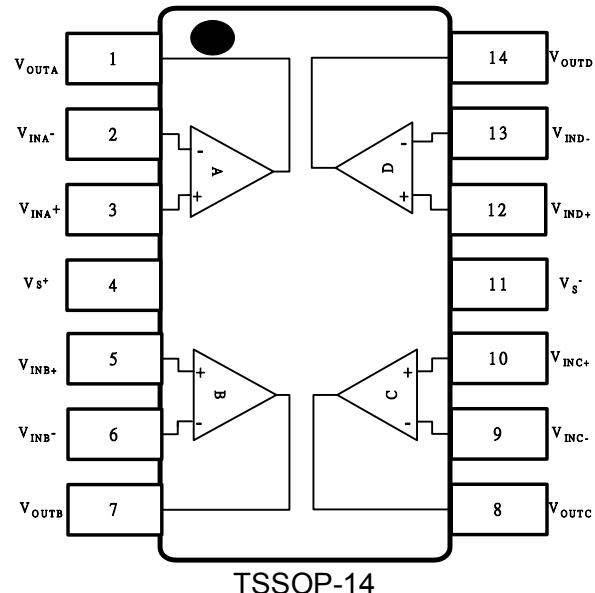

- Ultra-small Package TSSOP-14

## APPLICATIONS

- TFT-LCD Reference Driver

- Touch-Screen Display

- Wireless LANs

- Personal Communication Devices

- Direct Access Arrangement

- Personal Digital Assistant (PDA)

- Active Filter

- Sampling ADC Amplifier

- ADC/DAC Buffer

- Electronic Notebook

- Office Automation

With features of 40V/ $\mu$ s high slew rate and 500ns of fast settling time, as well as 100mA (sink and source) of high output driving capability, the EC5604 is ideal for the requirements of flat panel Thin Film Transistor Liquid Crystal Displays (TFT-LCD) panel reference buffers application. Due to insensitive to power supply variation, EC5604 offers flexibility of use in multitude of applications such as battery power, portable devices and anywhere low power consumption is concerned. With standard operational amplifier pin assignment, the EC5604 is offered in space saving 14-Pin TSSOP package and specified over the -40°C to +85°C temperature range.

## PIN ASSIGNMENT

## GENERAL DESCRIPTION

The EC5604 is a 100mA output current rail-to-rail quad channels operational amplifier with wide supply range from 6V to 18V while consumes only 2.0mA per channel. It provides 0.5V beyond the supply rails of common mode input range and capability of rail-to-rail output swing as well. This enables the amplifier to offer maximum dynamic range at any supply voltage among many applications. A 20MHz gain bandwidth product allows EC5604 to perform more stable than other devices in Internet applications.

**ABSOLUTE MAXIMUM RATINGS (TA = 25 °C)**

Values beyond absolute maximum ratings may cause permanent damage to the device. These are stress ratings only; functional device operation is not implied. Exposure to AMR conditions for extended periods may affect device reliability.

|                                              |                                   |                       |                 |

|----------------------------------------------|-----------------------------------|-----------------------|-----------------|

| Supply Voltage between $V_{S+}$ and $V_{S-}$ | +20V                              | Storage Temperature   | -65°C to +150°C |

| Input Voltage                                | $V_{S-} - 0.5V$ , $V_{S+} + 0.5V$ | Operating Temperature | -40°C to +85°C  |

| Maximum Continuous Output Current            | 100mA                             | Lead Temperature      | 260°C           |

| Maximum Die Temperature                      | +125°C                            | ESD Voltage           | 2kV             |

**Important Note:**

All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

**ELECTRICAL CHARACTERISTICS**

$V_{S+} = +5V$ ,  $V_{S-} = -5V$ ,  $R_L = 10k\Omega$  and  $C_L = 10pF$  to 0V,  $T_A = 25^\circ C$  unless otherwise specified.

| Parameter                                                                                            | Description                           | Condition                                             | Min                                           | Typ       | Max   | Units           |

|------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------------------|-----------------------------------------------|-----------|-------|-----------------|

| <b>Input Characteristics</b>                                                                         |                                       |                                                       |                                               |           |       |                 |

| $V_{OS}$                                                                                             | Input Offset Voltage                  | $V_{CM} = 0V$                                         |                                               | 2         | 12    | mV              |

| $TCV_{OS}$                                                                                           | Average Offset Voltage Drift          | [1]                                                   |                                               | 5         |       | $\mu V^\circ C$ |

| $I_B$                                                                                                | Input Bias Current                    | $V_{CM} = 0V$                                         |                                               | 2         | 50    | nA              |

| $R_{IN}$                                                                                             | Input Impedance                       |                                                       |                                               | 1         |       | G               |

| $C_{IN}$                                                                                             | Input Capacitance                     |                                                       |                                               | 1.35      |       | pF              |

| CMIR                                                                                                 | Common-Mode Input Range               |                                                       | -0.5                                          |           | +5.5  | V               |

| CMRR                                                                                                 | Common-Mode Rejection Ratio           | for $V_{IN}$ from -0.5V to 5.5V                       | 50                                            | 70        |       | dB              |

| $A_{VOL}$                                                                                            | Open-Loop Gain                        | $-4.5V \leq V_{OUT} \leq 4.5V$                        | 75                                            | 90        |       | dB              |

| <b>Output Characteristics</b>                                                                        |                                       |                                                       |                                               |           |       |                 |

| $V_{OL}$                                                                                             | Output Swing Low                      | $I_L = -5mA$                                          |                                               | -4.92     | -4.85 | mV              |

| $V_{OH}$                                                                                             | Output Swing High                     | $I_L = 5mA$                                           | 4.85                                          | 4.92      |       | V               |

| $I_{SC}$                                                                                             | Short Circuit Current                 |                                                       |                                               | $\pm 350$ |       | mA              |

| $I_{OUT}$                                                                                            | Output Current                        |                                                       |                                               | $\pm 100$ |       | mA              |

| $I_{PK}$                                                                                             | Peak Output Current                   | $V_{S+} = 18V$ , $V_{IN} = V_{S+}/2$<br>$V_{S-} = 0V$ | Source Current: I load<br>$V_{OUT}$ to GND    | 550       |       | mA              |

|                                                                                                      |                                       |                                                       | Sink Current: I load<br>$V_{OUT}$ to $V_{S+}$ |           |       |                 |

| <b>Power Supply Performance</b>                                                                      |                                       |                                                       |                                               |           |       |                 |

| PSRR                                                                                                 | Power Supply Rejection Ratio          | $V_S$ is moved from $\pm 2.25V$ to $\pm 7.75V$        | 60                                            | 80        |       | dB              |

| $I_S$                                                                                                | Supply Current (Per Amplifier)        | No Load,                                              |                                               | 2         |       | mA              |

| <b>Dynamic Performance</b>                                                                           |                                       |                                                       |                                               |           |       |                 |

| SR                                                                                                   | Slew Rate [2]                         | $-4.0V \leq V_{OUT} \leq 4.0V$ , 20% to 80%           |                                               | 40        |       | V/ $\mu$ s      |

| $t_s$                                                                                                | Settling to $\pm 0.1\%$ ( $AV = +1$ ) | ( $AV = +1$ ), $V_O = 2V$ Step                        |                                               | 500       |       | ns              |

| BW                                                                                                   | -3dB Bandwidth                        | $R_L = 10k\Omega$ , $C_L = 10pF$                      |                                               | 30        |       | MHz             |

| GBWP                                                                                                 | Gain-Bandwidth Product                | $R_L = 10k\Omega$ , $C_L = 10pF$                      |                                               | 20        |       | MHz             |

| PM                                                                                                   | Phase Margin                          | $R_L = 10k\Omega$ , $C_L = 10 pF$                     |                                               | 50        |       | Degrees         |

| CS                                                                                                   | Channel Separation                    | $f = 1$ MHz                                           |                                               | 75        |       | dB              |

| TSD                                                                                                  | Thermal Shutdown                      |                                                       |                                               | 150       |       | °C              |

| 1. Measured over operating temperature range<br>2. Slew rate is measured on rising and falling edges |                                       |                                                       |                                               |           |       |                 |

**TYPICAL PERFORMANCE CURVES**

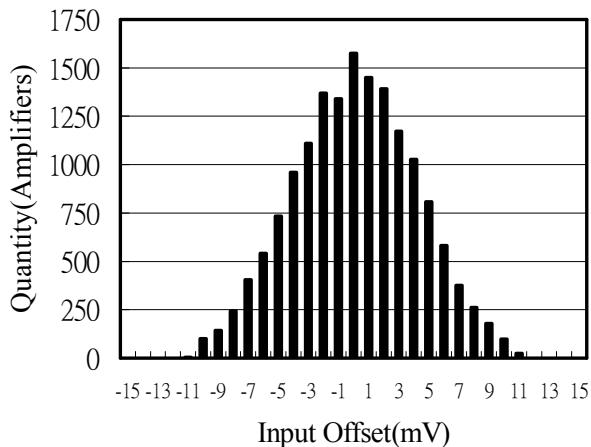

Figure (a) Input Offset Voltage Distribution

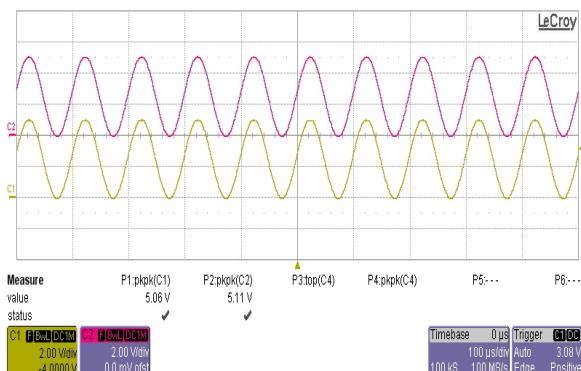

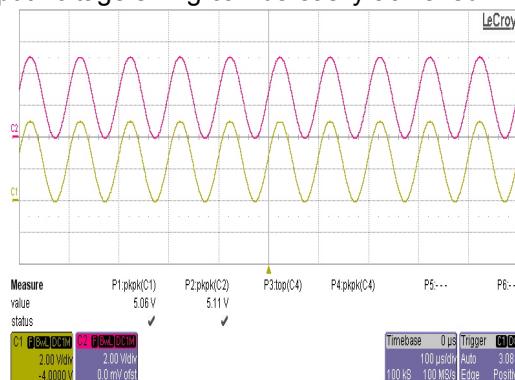

Figure (b) Rail to Rail Capability

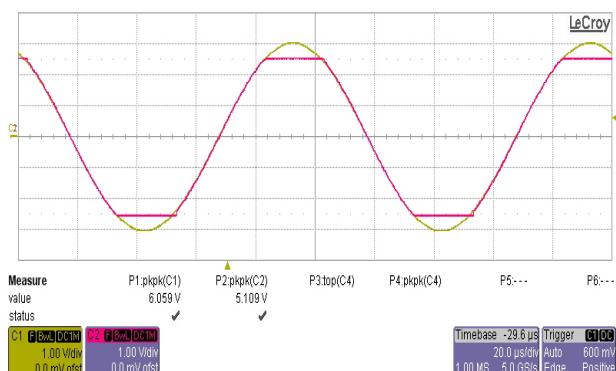

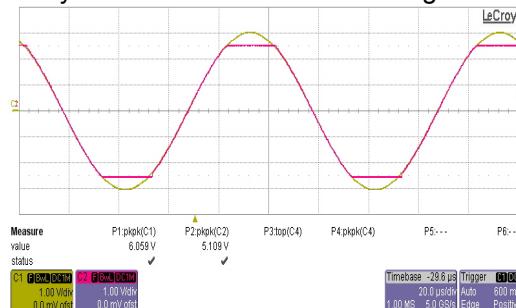

Figure (c) Input beyond the rails

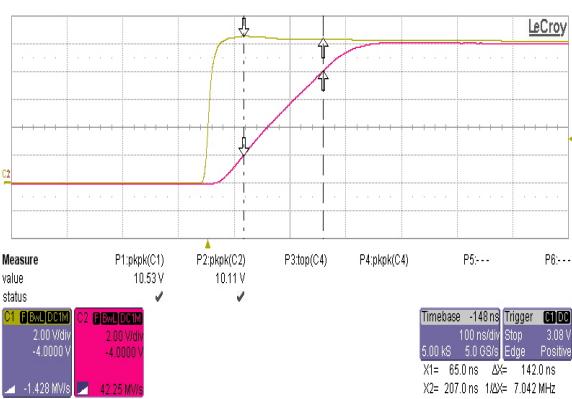

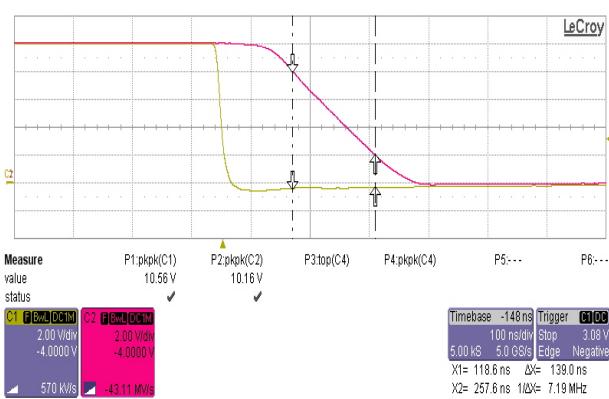

Figure (d) Large Signal Transient Response

Figure (e) Large Signal Transient Response

## APPLICATIONS INFORMATION

## Product Description

The EC5604 rail-to-rail quad channels amplifier is built on an advanced high voltage CMOS process. It's beyond rails input capability and full swing of output range made itself an ideal amplifier for use in a wide range of general-purpose applications. The features of 40V/ $\mu$ S high slew rate, fast settling time, 20MHz of GBWP as well as high output driving capability have proven the EC5604 a good voltage reference buffer for TFT-LCD for applications. High phase margin make the EC5604 ideal for Connected in voltage follower mode for high drive applications

## Supply Voltage, Input Range and Output Swing

The EC5604 can be operated with a single nominal wide supply voltage ranging from 6V to 18V with stable performance over operating temperatures of -40 °C to +85 °C.

With 500mV greater than rail-to-rail input common mode voltage range and 80dB of Common Mode Rejection Ratio, the EC5604 allows a wide range sensing among many applications without having any concerns over exceeding the range and no compromise in accuracy. The output swings of the EC5604 typically extend to within 80mV of positive and negative supply rails with load currents of 5mA. The output voltage swing can be even closer to the supply rails by merely decreasing the load current. Figure 1 shows the input and output waveforms for the device in the unity-gain configuration. The amplifier is operated under  $\pm$ 5V supply with a 10k load connected to GND. The input is a 10Vp-p sinusoid. An approximately 9.985 Vp-p of output voltage swing can be easily achieved.

Figure 1. Operation with Rail-to-Rail Input and Output.

## Output Short Circuit Current Limit

A +/-350mA short circuit current will be limited by the EC5604 if the output is directly shorted to the positive or the negative supply. For an indefinitely output short circuit, the power dissipation could easily increase such that the device may be damaged. The internal metal interconnections are

well designed to prevent the output continuous current from exceeding +/-100mA such that the maximum reliability can be well maintained.

## Output Phase Reversal

The EC5604 is designed to prevent its output from being phase reversal as long as the input voltage is limited from  $V_S - 0.5V$  to  $V_S + 0.5V$ . Figure 2 shows a photo of the device output with its input voltage driven beyond the supply rails. Although the phase of the device's output will not be reversed, the input's over-voltage should be avoided. An improper input voltage exceeds supply range by more than 0.6V may result in an over stress damage.

Figure 2. Operation with Beyond-the Rails Input

## Power Dissipation

The EC5604 is designed for maximum output current capability. Even though momentary output shorted to ground causes little damage to the device.

For the high drive amplifier EC5604, it is possible to exceed the 'absolute-maximum junction temperature' under certain load current conditions. Therefore, it is important to calculate the maximum junction temperature for the application to determine if load conditions need to be modified for the amplifier to remain in the safe operating area. The maximum power dissipation allowed in a package is determined according to:

$$P_{D\max} = \frac{T_{J\max} - T_{A\max}}{\Theta_{JA}}$$

Where:

$T_{J\max}$  = Maximum Junction Temperature

$T_{A\max}$  = Maximum Ambient Temperature

$\Theta_{JA}$  = Thermal Resistance of the Package

$P_{D\max}$  = Maximum Power Dissipation in the Package.

The maximum power dissipation actually produced by an IC is the total quiescent supply current times the total power supply voltage, plus the power in the IC due to the loads, or:

$$P_{D\max} = \sum_i [V_S \times I_{Smax} + (V_{S+} - V_O) \times I_L]$$

When sourcing, and

$$P_{Dmax} = \sum_i [V_s \times I_{smax} + (V_o - V_{s-}) \times I_L]$$

When sinking.

Where:

$i = 1$  to  $4$

$V_s$  = Total Supply Voltage

$I_{smax}$  = Maximum Supply Current Per Amplifier

$V_o$  = Maximum Output Voltage of the Application

$I_L$  = Load current

$$R_L = \text{Load Resistance} = (V_{s+} - V_o) / I_L = (V_o - V_{s-}) / I_L$$

| Package           | $\theta_{ja}$<br>( $^{\circ}\text{C}/\text{W}$ ) |

|-------------------|--------------------------------------------------|

| TSSOP14           | 165                                              |

| TSSOP14 1.98x2.23 | 75                                               |

| TSSOP14 3x3       | 59                                               |

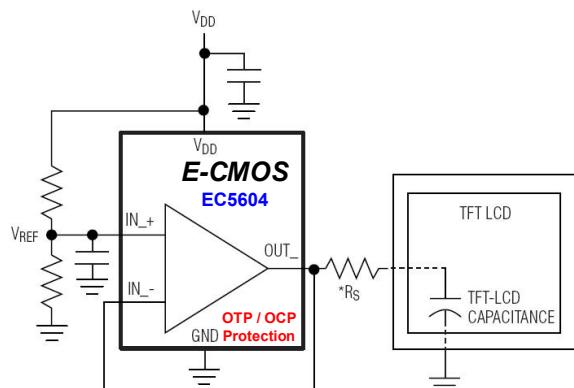

### Driving Capacitive Loads

The EC5604 is designed to drive a wide range of capacitive loads. In addition, the output current handling capability of the device allows for good slewing characteristics even with large capacitive loads. The combination of these features make the EC5604 ideally for applications such as TFT LCD panel buffers, ADC input amplifiers, etc.

As load capacitance increases on the device output, resulting in additional pole in the op amp's feedback loop. Depending on the application, a small value of series resistance must be placed in series with the output (usually between  $5 \Omega$  and  $50 \Omega$ ). However, the op amp remains stable because the load capacitance and the series resistance create a zero that cancels the effect of this pole. It improves the performance of the device to ensure stability and fast settling with very large capacitive loads. Figure 3 shows the typical application configuration.

\*Rs BE NEEDED FOR SOME APPLICATIONS.

Figure 3. Typical Application Configuration.

### Power Supply Bypassing and Printed Circuit Board Layout

With high phase margin, the EC5604 performs stable gain at high frequency. Like any high-frequency device, good layout of the printed circuit board usually comes with optimum performance. Ground plane construction is highly recommended, lead lengths should be as short as possible and the power supply pins must be well bypassed to reduce the risk of oscillation. For normal single supply operation, where the  $V_{s-}$  pin is connected to ground, a  $0.1\mu\text{F}$  ceramic capacitor should be placed from  $V_{s+}$  pin to  $V_{s-}$  pin as a bypassing capacitor. A  $4.7\mu\text{F}$  tantalum capacitor should then be connected in parallel, placed in the region of the amplifier. One  $4.7\mu\text{F}$  capacitor may be used for multiple devices. This same capacitor combination should be placed at each supply pin to ground if split supplies are to be used.

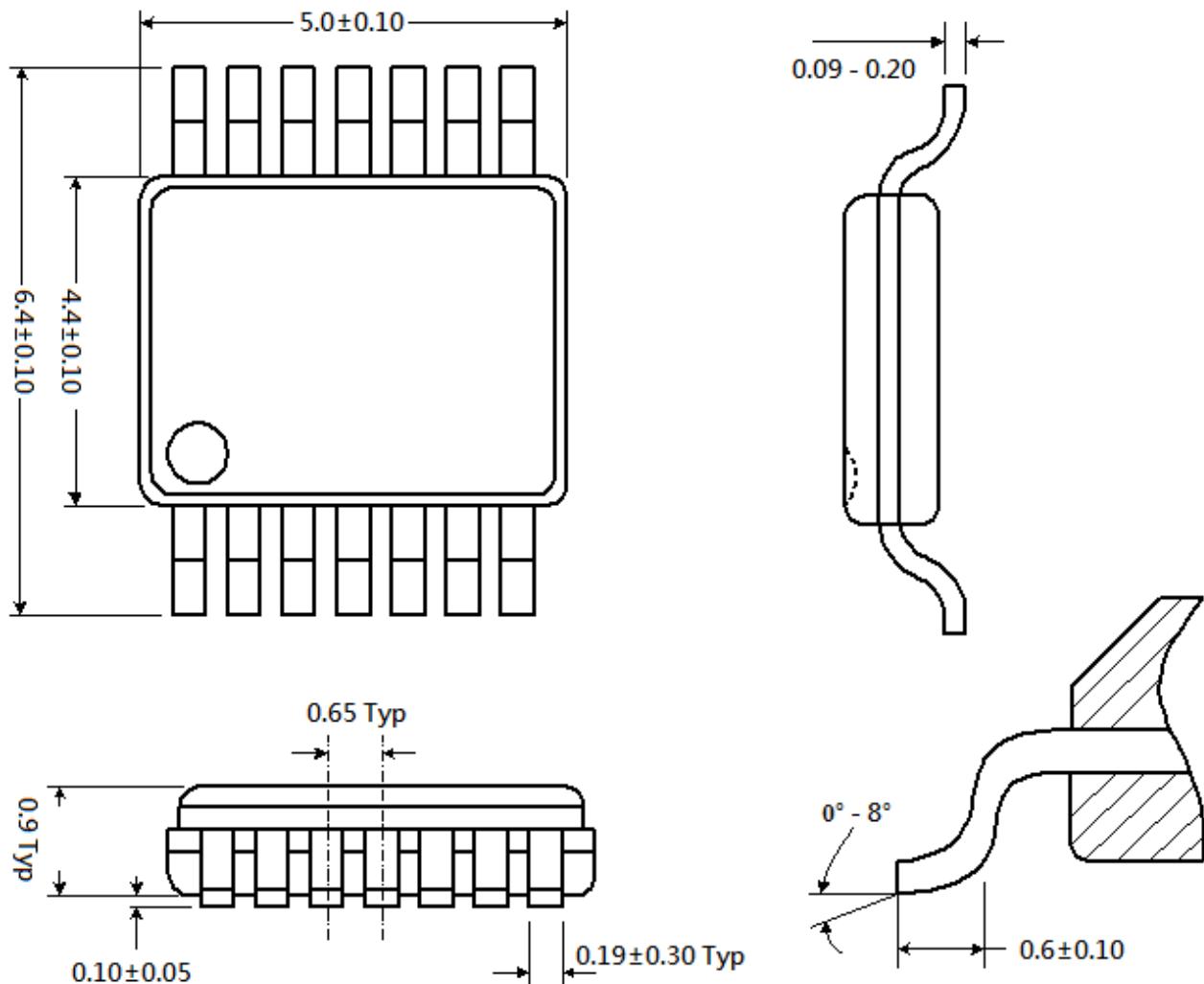

**OUTLINE DIMENSIONS** (Dimensions shown in millimeters)

TSSOP (Thin-Shrink Small Outline Package)

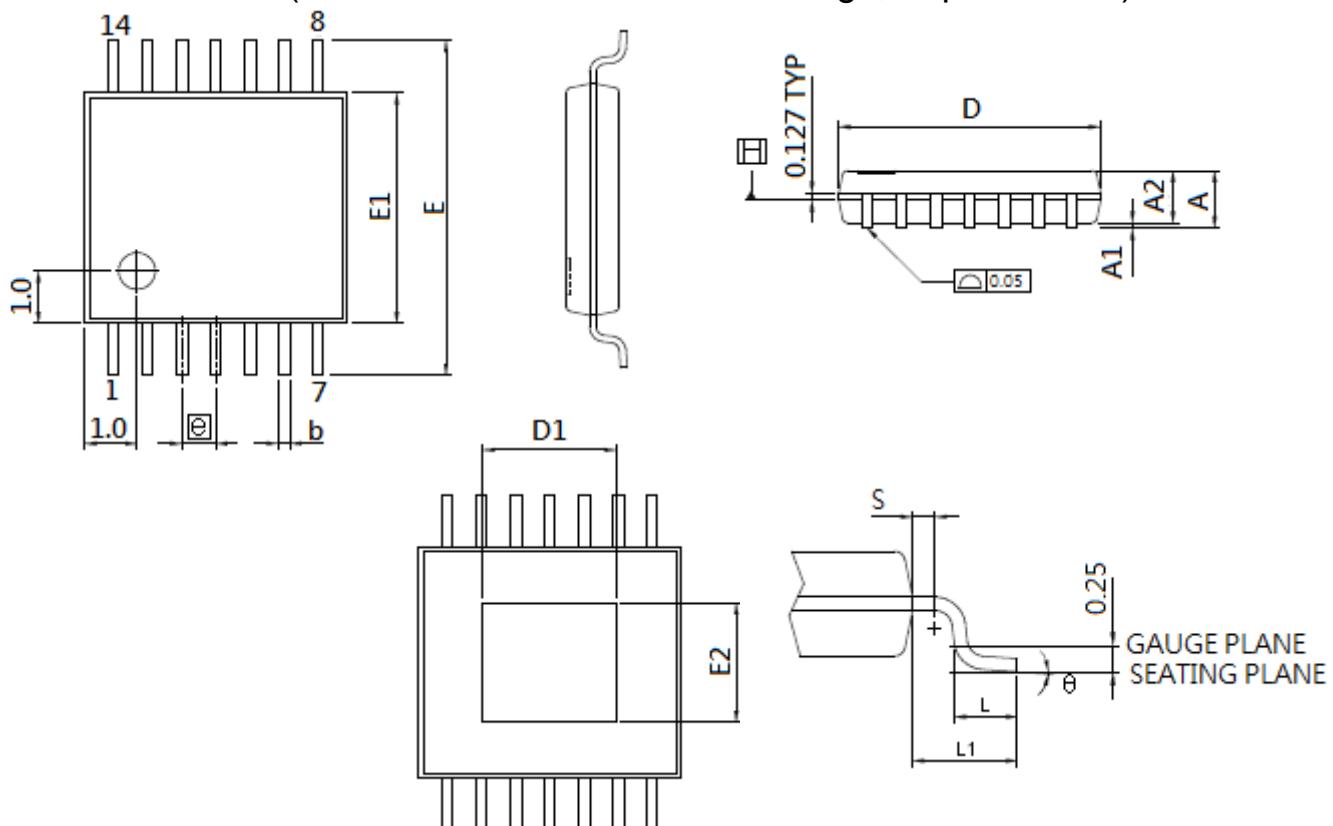

## TSSOP (Thin-Shrink Small Outline Package, Exposed Pad)

## VARIATIONS (ALL DIMENSIONS SHOWN IN MM)

| SYMBOLS                   | MIN.     | NOM. | MAX. |

|---------------------------|----------|------|------|

| <b>A</b>                  | -        | -    | 1.20 |

| <b>A1</b>                 | 0.05     | -    | 0.15 |

| <b>THERMALLY ENHANCED</b> | 0.00     | -    | 0.15 |

| <b>A2</b>                 | 0.80     | 1.00 | 1.05 |

| <b>b</b>                  | 0.19     | -    | 0.30 |

| <b>D</b>                  | 4.90     | 5.00 | 5.10 |

| <b>D1</b>                 | 1.92     | 2.23 | 2.54 |

| <b>E2</b>                 | 1.67     | 1.98 | 2.29 |

| <b>E1</b>                 | 4.30     | 4.40 | 4.50 |

| <b>E</b>                  | 6.40 BSC |      |      |

| <b>e</b>                  | 0.65 BSC |      |      |

| <b>L1</b>                 | 1.00 BSC |      |      |

| <b>L</b>                  | 0.50     | 0.60 | 0.75 |

| <b>S</b>                  | 0.20     | -    | -    |

| <b>θ</b>                  | 0°       | -    | 8°   |

## NOTES:

1. JEDEC OUTLINE

STANDARD: MO-153 AB-1

THERMALLY ENHANCED: MO-153 ABT-1

2. DIMENSION 'D' DOES NOT INCLUDE MOLD FLASH. PROTRUSION OR GATE BURRS. MOLD FLASH. PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.15 PER SIDE.

3. DIMENSION 'E1' DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 PER SIDE.

4. DIMENSION 'B' DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08MM TOTAL IN EXCESS OF THE 'B' DIMENSION AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OF THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD IS 0.07 MM.

5. DIMENSIONS 'D' AND 'E1' TO BE DETERMINED AT DATUM PLANE  $\square$

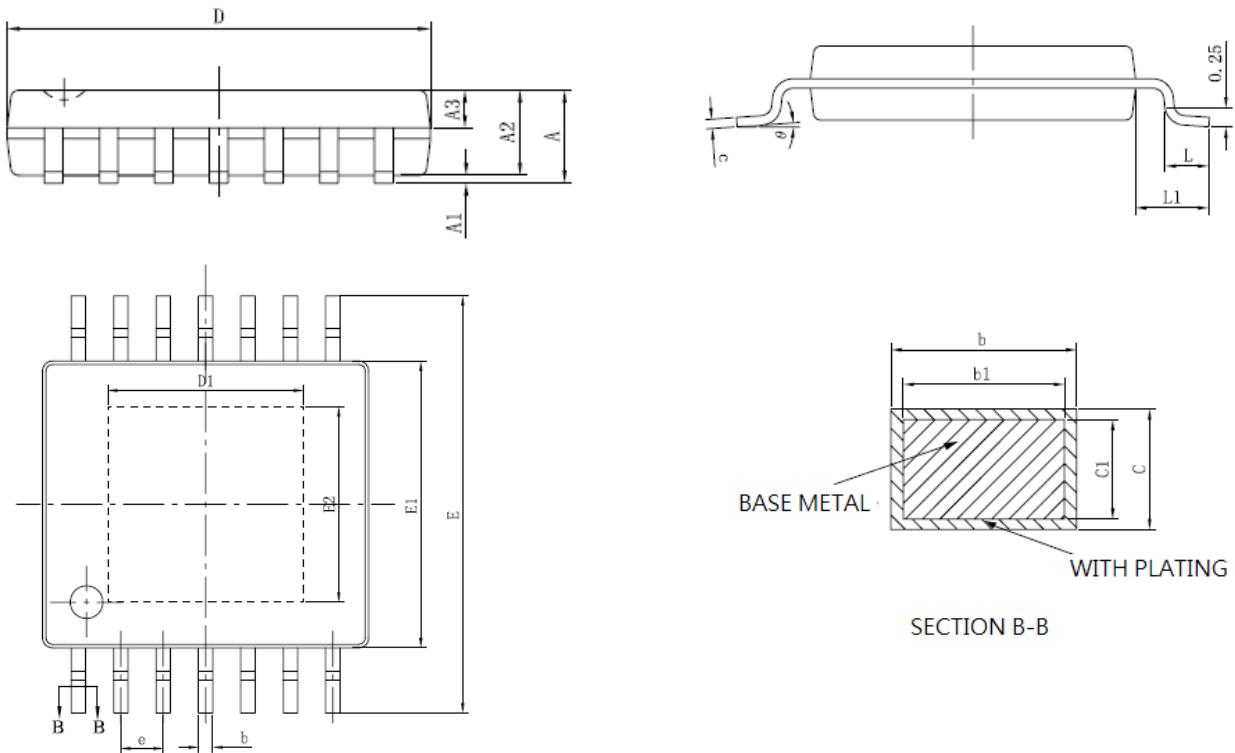

## TSSOP (Thin-Shrink Small Outline Package, Exposed Pad)

| SYMBOL | MILLIMETER |      |      |

|--------|------------|------|------|

|        | MIN        | NOM  | MAX  |

| A      | -          | -    | 1.20 |

| A1     | 0.05       | -    | 0.15 |

| A2     | 0.90       | 1.00 | 1.05 |

| A3     | 0.39       | 0.44 | 0.49 |

| b      | 0.20       | -    | 0.30 |

| b1     | 0.19       | 0.22 | 0.25 |

| c      | 0.13       | -    | 0.19 |

| c1     | 0.12       | 0.13 | 0.14 |

| D      | 4.86       | 4.96 | 5.06 |

| D1     | 2.90       | 3.00 | 3.10 |

| E2     | 2.90       | 3.00 | 3.10 |

| E1     | 4.30       | 4.40 | 4.50 |

| E      | 6.25       | 6.40 | 6.55 |

| e      | 0.65BSC    |      |      |

| L      | 0.45       | -    | 0.75 |

| L1     | 1.00BSC    |      |      |

| θ      | 0          | -    | 8°   |

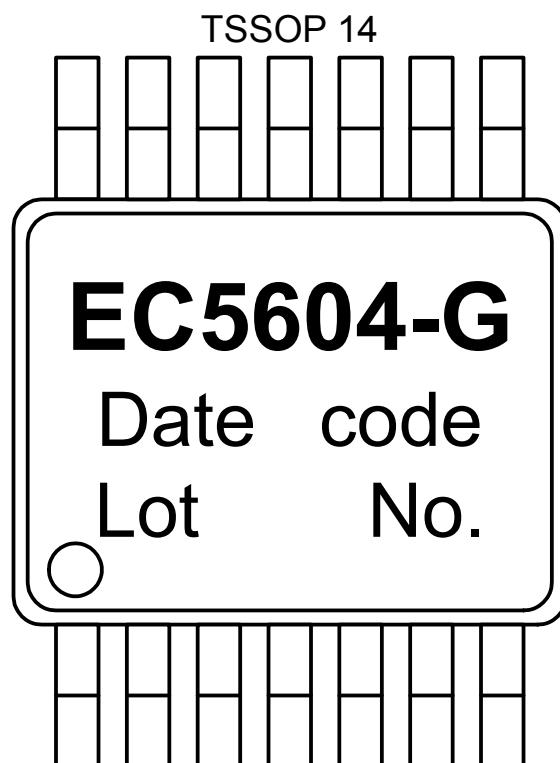

## PACKAGE MARKING INDICATION

## ORDERING INFORMATION

| PART NUMBER | TOP MARK | PACKAGE                                       |

|-------------|----------|-----------------------------------------------|

| EC5604I-G   | EC5604-G | Green mode TSSOP-14                           |

| EC5604I-HG  | EC5604HG | Green mode TSSOP-14(EP Size: 1.98mm x 2.23mm) |

| EC5604I-H1G | EC5604H1 | Green mode TSSOP-14(EP Size: 3mm x 3mm)       |

**General Disclaimer:**

1. Product information and specifications furnished by E-CMOS in this data sheets are in effect as of the publication date shown and are believed to be accurate and reliable. However, no responsibility is assumed by E-CMOS for the use of any information shown herein, nor for any patent or other rights infringement.

2. No license is granted by implication or otherwise under any patent or industrial properties owned by E-CMOS or any third party through this document.

3. The information herein is subject to change at any time without notice.

4. Neither reproduction nor duplication of this document, in any form, the whole or part is allowed without the prior written approval from E-CMOS.

5. Products of E-CMOS Corp., unless otherwise specified, are not authorized for use as critical components of any device or equipment in applications that demand extremely high reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aircraft, vehicles, nuclear power, radiation resistant system, transportation, disaster prevention equipment, gas related equipment, physical exercise equipment, safety equipment and medical equipment for life support, etc.

6. Although E-CMOS makes every attempt to ensure that its products are of high quality and reliability, thorough consideration of safety design and operating within the ranges guaranteed are strongly recommended to prevent any accident and damage that may ensue. E-CMOS bares no responsibility for failure or damage when abused or used beyond the guaranteed ranges.

7. Products applied to life support devices and systems are strongly requested to contact E-CMOS Corporation headquarter for the written approval to establish suitable terms & conditions. E-CMOS' warranty is limited to replacement of defective components. Any personal injury or death or any other consequential damages of property are not covered.

Copyright © 2002 by E-CMOS Corporation.

**E-CMOS CORPORATION IC DATASHEET**

**ADDRESS: NO.1, CREATION RD. 2<sup>ND</sup>, SCIENCE-BASED INDUSTRIAL PARK,

HSIN-CHU 300, TAIWAN, R.O.C.**

**WEBSITE: <http://www.ecmos.com.tw>**

**E-MAIL: <mailto:sales@ecmos.com.tw>**

**TEL: 886-3-5785888**

**FAX: 886-3-5783630**