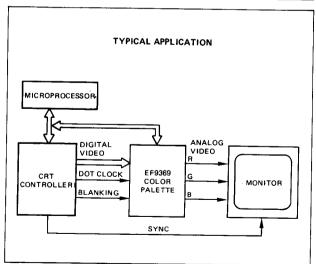

The EF9369 single chip palette provides a low cost, yet remarkable enhancement for any low to mid-range color graphics application. It allows displaying up to 16 different colors, each of these colors being freely selected out of 4096 preset values. EF9369 contains a 16 register color look-up table, three 4-bit D/A converters and a microprocessor interface for color loading.

- On chip color look-up table

- 4096 color palette (16 colors selected from 4096)

- On-chip three 4-bit resolution video DACs with γ law correction

- Dot rate up to 30 Megadots per second

- Marking bit for inlay purpose

- Versatile microprocessor interface :

- directly compatible with address/data multiplexed 8-bit microprocessor bus such as 6801, EF6805CT, 8051...

- directly compatible with non-multiplexed 8 or 16-bit microprocessor bus (6809, 6502, 68008...).

- Single 5 V supply

- HMOS 2 technology.

# HMOS2

SINGLE CHIP COLOR PALETTE

#### MAXIMUM RATINGS

| Rating                      | Symbol            | Value        | Unit |  |

|-----------------------------|-------------------|--------------|------|--|

| Supply voltage              | vcc*              | - 0.3 to 7.0 | ٧    |  |

| Inout voltage               | v <sub>in</sub> • | - 0.3 to 7.0 | ٧    |  |

| Operating temperature range | TA                | 0 to 70      | °c   |  |

| Storage temperature range   | Tstg              | - 55 to 150  | °c   |  |

| Max power dissipation       | PDm               | 0.45         | W    |  |

Stresses above those hereby listed may cause permanent damage to the device. The ratings are stress ones only and functional operation of the device at these or any conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. Standard MOS circuits handling procedure should be used to evoid possible damage to the device.

# **ELECTRICAL OPERATING CHARACTERISTICS**

$(VCC = 5.0 V \pm 5 \%, VSS = 0, TA = 0 to 70°C))$

| Characteristic                              | Symbol           | Min   | Тур | Max  | Unit      |

|---------------------------------------------|------------------|-------|-----|------|-----------|

|                                             | Vcc              | 4.75  | 5   | 5.25 | V         |

| Supply voltage                              | VDDC             | -     | Vcc | TBD  | V         |

| Analog supply voltage Analog supply current | IDDC             |       | 20  | -    | mA        |

| Input low voltage                           | VIL              | - 0.3 | -   | 0.8  | V         |

| Input ligh voltage RESET                    | VIH              | 3     | _   | Vcc  | \ \       |

| All other inputs                            |                  | 2     |     | Vcc  | <b></b> _ |

| Input leakage current                       | lin              |       |     | 20   | μА        |

| Output high voltags (I load = - 500 µA)     | Voн              | 2.4   |     |      | V         |

| Output low voltage (Iload = 1.6 mA)         | VOL              | -     |     | 0.4  | V         |

| Power dissipation                           | PD               | -     | 250 |      | mW        |

| Input capacitance                           | Cin              |       | -   | 15   | ρF        |

| Three state (off state) input current       | <sup>I</sup> TSI | -     | -   | 10   | μА        |

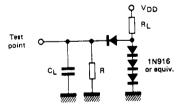

#### Test load for digital output

## Test load for analog output

| AD(0:7) | м              |

|---------|----------------|

| 100 pF  | 50 pF          |

| 1 ΚΩ    | 3.3 KΩ         |

| 4.7 ΚΩ  | 4.7 ΚΩ         |

|         | 100 pF<br>1 KΩ |

<sup>\*</sup>With respect to VSS

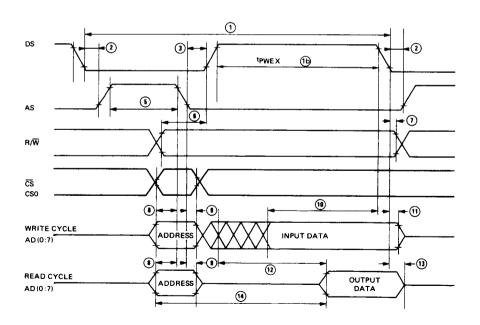

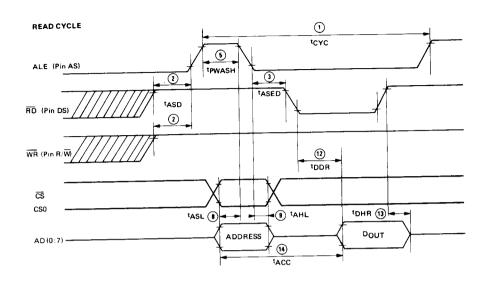

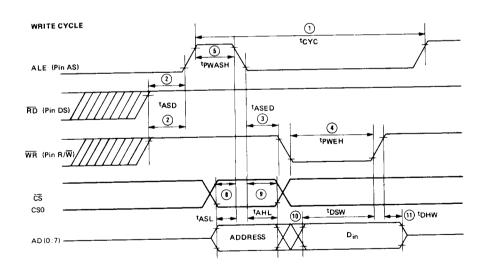

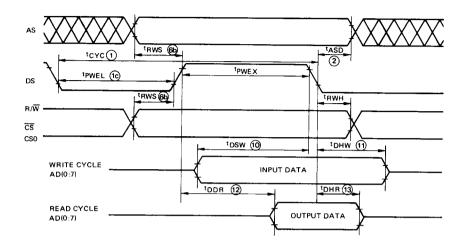

MICROPROCESSOR INTERFACE TIMING AD(0:7), AS, DS, R/W, CS, CS0

V<sub>CC</sub> =  $5.0 \pm 5$  %, T<sub>A</sub> =  $0^{\circ}$  to +  $70^{\circ}$ C, C<sub>L</sub> = 100 pF on AD(0:7) Reference levels : V<sub>IL</sub> = 0.8 V and V<sub>IH</sub> = 2 V on all inputs ; V<sub>OL</sub> = 0.4 V and V<sub>OH</sub> = 2.4 V on all outputs.

| ldent.<br>number | Characteristic                                        | Symbol             | Min | Тур | Max   | Unit |  |

|------------------|-------------------------------------------------------|--------------------|-----|-----|-------|------|--|

| 1                | Cycle time                                            | tCYC               | 400 | _   | _     | ns   |  |

| 1b               | DS pulse width high time                              | <sup>t</sup> PWE X | 200 | _   | -     | ns   |  |

| 1c               | DS pulse width low time (Timing 3)                    | <sup>t</sup> PWEL  | 100 | -   | 10000 | ns   |  |

| 2                | DS low to AS high (timing 1)                          | tASD               | 30  |     |       | ns.  |  |

|                  | DS high or R/W high to AS high (timing 2)             | - 1                |     | ]   |       | 1    |  |

| 3                | AS low to DS high (timing 1)                          | †ASED              | 30  |     |       | ns   |  |

|                  | AS low to DS low or R/W low (timing 2)                |                    |     | ĺ   | 1     |      |  |

| 4                | Write pulse width                                     | <sup>t</sup> PWEH  | 200 | _   |       | ns   |  |

| 5                | AS pulse width                                        | †PWASH             | 100 | _   | -     | ns   |  |

| 6                | R/W to DS setup time (timing 1)                       | tRWS               | 100 | _   | _     | ns   |  |

| 6b               | R/W, AS, CS, CS0 to DS setup time (timing 3)          |                    | 100 | _   | -     |      |  |

| 7                | R/W to DS hold time (timing 1)                        | tRWH               | 10  | _   | _     | ns   |  |

| 8                | Address and CS, CS0 setup time                        | †ASL               | 20  | -   | _     | ns   |  |

| 9                | Address and CS, CSO hold time                         | tAHL               | 20  | _   | _     | nŝ   |  |

| 10               | Data setup time (write cycle)                         | †DSW               | 100 | -   | _     | ns   |  |

| 11               | Data hold time (write cycle)                          | tDĤW               | 10  | _   | _     | ns   |  |

| 12               | Data access time from DS (read cycle)                 | <sup>t</sup> DDR   | -   | _   | 150   | ns   |  |

| 13               | DS inactive to high impedance state time (read cycle) | tDHR               | 10  |     | 80    | ns   |  |

| 14               | Address to data valid access time                     | TACC               | _   |     | 300   | ns   |  |

TIMING DIAGRAM 1 - MULTIPLEXED MODE - MOTOROLA TYPE (SMI = VSS)

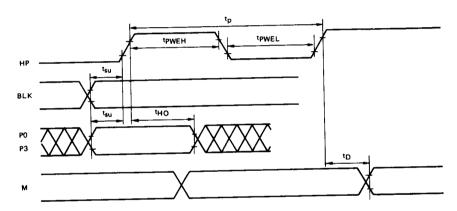

# DIGITAL VIDEO SIGNALS - HP, P(0:3), BLK, M, RESET

$\begin{array}{l} \text{VCC} = 5.0 \pm 5 \text{ \%, TA} = 0^{\circ}\text{C to + }70^{\circ}\text{C, C}_{L} = 50 \text{ pF on M.} \\ \text{Reference levels : VIL} = 0.8 \text{ V and VIH} = 2 \text{ V on all inputs ;} \\ \text{VOL} = 0.4 \text{ V and VOH} = 2.4 \text{ V on all outputs.} \end{array}$

|                                  |                | EF9 |      | EF9369-30 |      | Unit |

|----------------------------------|----------------|-----|------|-----------|------|------|

| Characteristic                   | Symbol         | Min | Max  | Min       | Max  |      |

| HP clock period                  | tp             | 58  | 1000 | 33        | 1000 | ns   |

| HP high pulse width              | †PWEH          | 25  | _    | 13        |      | ns   |

| HP low pulse width               | tPWEL          | 25  |      | 13        |      | ns   |

| BLK and P(0:3) set up time to HP | tsu            | 5   |      | 5         | -    | ns   |

| BLK and P(0:3) hold time from HP | tHO            | 10  |      | 10        |      | ns   |

| M output delay from HP           | t <sub>D</sub> |     | 45   |           | 30   | ns   |

| RESET high pulse width           | tpwrl          | 400 | . –  | 400       |      | ns   |

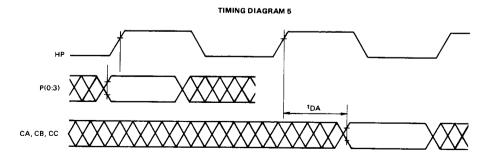

#### TIMING DIAGRAM 4

TABLE 1

| Rinar      | Binary input |   | Analog output | (V) |

|------------|--------------|---|---------------|-----|

|            |              |   | Тур           | Max |

| Low level  | 0000         | _ | 0.8           | _   |

|            | 0001         | - | 1.18          | _   |

|            | 0010         | _ | 1.28          | _   |

|            | 0011         | - | 1.36          | _   |

|            | 0100         | - | 1.42          | _   |

|            | 0101         | _ | 1.47          | _   |

|            | 0110         | _ | 1.52          | _   |

|            | 0111         | _ | 1.56          | _   |

|            | 1000         | - | 1.60          | _   |

|            | 1001         | - | 1.63          | _   |

|            | 1010         | _ | 1.66          | _   |

|            | 1011         | - | 1.69          | _   |

|            | 1100         | _ | 1.72          | _   |

|            | 1101         | - | 1.75          | -   |

|            | 1110         | _ | 1.78          | _   |

| High level | 1111         | _ | 1.80          | _   |

#### Note:

The internal A/D converters deliver on CA, CB and CC outputs 16 levels with  $\gamma$  law correction ( $\gamma=2.8$ ). The typical transfer characteristic is given by :

$$V = (\frac{N}{15})^{\frac{1}{2.8}} \cdot \frac{V_{DDC}}{5} + 0.16 V_{DCC}$$

Where N is the binary input value.

The typical analog video output impedance is 300  $\Omega$  for EF9369-30 and 400  $\Omega$  for EF9369.

| Ch arac teristic           |                 | Min | Тур | Max | Unit |

|----------------------------|-----------------|-----|-----|-----|------|

| CA, CB, CC outputs from HP | t <sub>DA</sub> | -   | 80  | -   | ns   |

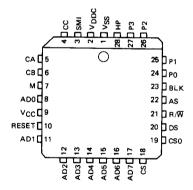

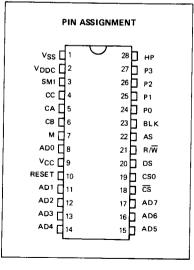

# PIN DESCRIPTION

#### MICROPROCESSOR INTERFACE

All the input/output pins are TTL compatible.

| NAME            | PIN<br>TYPE | N°                 | FUNCTION                     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------|-------------|--------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD(0:7)         | 1/0         | 8-11-14<br>15 - 17 | Multiplexed address/data bus | These 8 bidirectional pins are to be connected to the micro-processor system bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SMI             | I           | 3                  | Interface<br>mode<br>select  | When this input is connected to VCC, the EF9369 is in the non multiplexed mode.  When this input is connected to VSS (ground), the EF9369 is in a multiplexed mode to provide a direct interface with either Motorola or Intel type microprocessor.                                                                                                                                                                                                                                                                                    |

| AS              | 1           | 22                 | Address<br>strobe            | In non-multiplexed mode, this input selects either the address register (AS = 1) or the data register (AS = 0) to be accessed. In multiplexed mode, the falling edge of this control signal latches the address on the AD(0:7) lines, the state of the Data Strobe (DS) and Chip Select lines ( $\overline{\text{CS}}$ , CS0). When using Intel type microprocessor, this input must be connected to the ALE control line.                                                                                                             |

| DS              | l           | 20                 | Data<br>strobe               | In non-multiplexed mode, this active high control signal enables the AD(0:7) input/output buffers and strobes data to/from the EF9369. This signal is usually derived from the processor E ( $\phi$ 2) clock.  In multiplexed mode, the input is strobed by the falling edge of AS. The strobe value selects either Motorola or Intel type. When using an Intel type microprocessor, DS must be connected to the $\overline{\text{RD}}$ control line. With a Motorola type microprocessor, DS must be connected to E( $\phi$ 2) clock. |

| R/ <del>W</del> | I           | 21                 | Read/Write                   | This control signal determines whether the EF9369 is read $(R/\overline{W}=1)$ or written $(R/\overline{W}=0)$ . When using Intel type microprocessor, this input must be connected to the $\overline{WR}$ control line.                                                                                                                                                                                                                                                                                                               |

| CS<br>CS0       | I           | 18<br>19           | Chip Select                  | CS must be low and CS0 must be high to select the EF9369. In non-multiplexed mode, the EF9369 remains selected as long as the selection condition is met.  In multiplexed mode, the selection condition is latched when AS is low.                                                                                                                                                                                                                                                                                                     |

#### VIDEO INTERFACE

| NAME           | PIN<br>Type | N°          | FUNCTION         | DESCRIPTION                                                                                                                                                                                                                                 |

|----------------|-------------|-------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P(0:3)         | 1           | 24 - 27     | Pixel inputs     | These four TTL compatible inputs are strobed by HP into the color index register to address the color look-up table.                                                                                                                        |

| НР             | ı           | 28          | Dot clock        | The rising edge of this input latches the P(0:3) and BLK inputs into the EF9369 and the data out of the color look-up table into the output registers.                                                                                      |

| М              | 0           | 7           | Marking          | This output is synchronised by HP and delivers the marking bit value from the color look-up table.                                                                                                                                          |

| CA<br>CB<br>CC | 0           | 5<br>6<br>4 | Color<br>outputs | These three analog high impedance outputs deliver the color signal levels from the internal D/A converters (DAC). The delay between CA, CB, CC outputs and the latched value P(0:3) is one HP clock period plus tDA (see Timing Diagram 5). |

| BLK            | ı           | 23          | Blanking         | A high level on this input forces the CA, CB, CC and M outputs to low level.                                                                                                                                                                |

| RESET          | ı           | 10          | Reset            | This active high input forces the CA, CB, CC, outputs to low level until the next microprocessor access to the device.                                                                                                                      |

# OTHER PINS

| Vcc  | s | 9 | Power supply        | + 5 V.                                                                  |

|------|---|---|---------------------|-------------------------------------------------------------------------|

| VDDC | S | 2 | Analog power supply | Power supply for the internal DACs. This input can be connected to VCC. |

| VSS  | s | 1 | Power supply        | Ground.                                                                 |

#### **FUNCTIONAL DESCRIPTION**

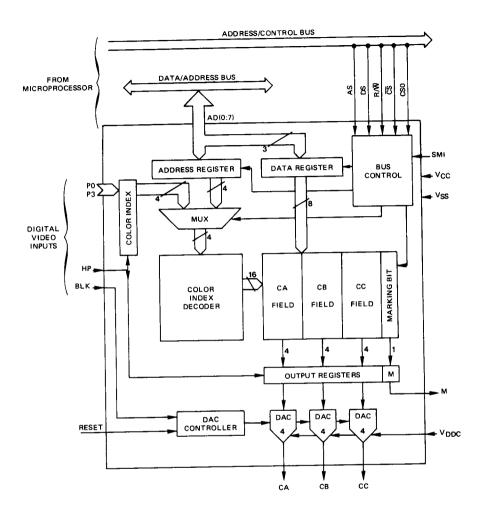

EF9369 contains a 16 register Color-Look Up Table (CLUT). Each of these 13-bit register holds three 4-bit color fields CA (0:3), CB (0:3) and CC (0:3) and a marking bit M.

These registers can be accessed (read or write) by the microprocessor through the microprocessor interface. These registers are also read by the video process: a 4-bit pixel value and a clock must be provided at pixel rate to the P(0:3) and HP input pins. These signals may be delivered either by 4 video shift registers and the shifting clock of a bit map CRT controller or by an alphanumeric or semigraphic CRT controller. The pixel value, after clock resynchronisation, is used as a color index: it selects one out of the 16 CLUT registers. Each color field of the selected register is converted to an analog signal and delivered to one of the CA, CB or CC output. The marking bit is directly routed to the M output. When the CA, CB and CC outputs are used as RGB analog signals, one cofor out of 4096 is associated to each pixel value. In short this process freely maps a 16 color index set into a 4096 color set.

#### MICROPROCESSOR INTERFACE

The 8-bit microprocessor interface gives access (read or write) to the CLUT which is addressed as a 32 byte table. The 13-bit color register # N (N = 0 to 15) is accessed at address 2N and 2N + 1. Even address holds CA (0:3) and CB (0:3), odd address holds CC (0:3) and M (see fig. 1).

EF9369 provides two bus modes through the SMI programming pin:

- Multiplexed mode for address/data multiplexed 8-bit microprocessor bus.

- Non-multiplexed mode for non-multiplexed 8 or 16bit microprocessor bus.

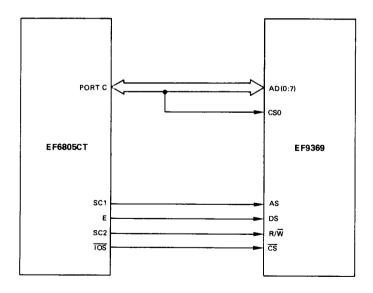

#### MULTIPLEXED MODE (SMI connected to Veg)

In this mode, EF9369 can be directly connected to popular address/data multiplexed microprocessor, either Motorola type (6801, EF6805CT...) or Intel type (8048, 8051, 8088..). In this last case the EF9369 AS, DS and  $R/\overline{W}$  inputs must be connected respectively to the ALE,  $\overline{RD}$  and  $\overline{WR}$  microprocessor control lines.

Color Look-Up Table (CLUT) **CLUT Byte Address** Register Index # 7 6 5 3 2 0 7 6 5 2 4 3 1 0 CB3 CB2 CB1 CRO CA3 CA2 CA1 CAO ¥ x x 0 ٥ 0 0 0 n x ССЗ X х м CC2 CC1 CCO x х х 0 0 0 0 1 CR3 CB<sub>2</sub> CB1 CB0 CA3 CA2 CA<sub>1</sub> CAO x x 0 o n 1 n х ¥ ¥ м CC3 CC2 CC1 CCO ¥ × х 0 0 0 1 1 CR3 CB2 CB1 СВО CA3 CA2 CA1 CAO х х 1 1 1 1 0 15 х x x м CC3 CC2 CC1 CCO x ¥ ¥ 1 1 1

FIGURE 1 - CLUT ADDRESSING

X = don't care.

In this mode, EF9369 maps into the microprocessor addressing space as 32 CLUT byte address. Random access to one byte takes one cycle: on the falling edge of the AS input, EF9369 latches AD (0:7) into the on-chip address register, the DS and chip select lines into dedicated flip-flops. The strobed value of DS allows recognition of Intel or Motorola type for further processing. (See pin description section and microprocessor timing diagrams for details). When the EF9369 chip select lines enable selection, the addressed byte is accessed during the data phase of the cycle.

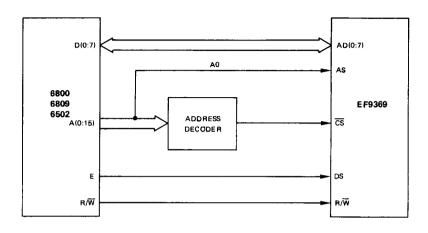

#### NON MULTIPLEXED MODE (SMI connected to VCC)

In this mode EF9369 can be directly connected to any 8 or 16-bit, non multiplexed, microprocessor bus (6800, 6809, 6502, 68008...).

This mode provides an indirect, auto-incremented addressing scheme. EF9369 maps into the microprocessor addressing space as 2 byte address only. AS is used to select one out of 2 registers:

- the write only address register (5 bits) addressed when AS = 1.

- $\bullet$  the read/write data register (8 bits) addressed when AS=0.

Random access to a CLUT byte takes two bus cycles: 1/Load the CLUT address into the address register. 2/Access (read or write) the value in the data register.

After each access to the data register, the address register is automatically incremented modulo 32. This scheme allows sequential addressing to the CLUT without address reloading, the complete CLUT can so be reloaded in 33 bus cycles.

#### VIDEO PROCESS

The CRT controller sends to EF9369 a pixel value on pins P (0:3), a pixel rate clock on HP input and a blanking signal on pin BLK. The pixel value is latched into the color index register by the rising edge of HP. The color index register selects one register in the CLUT. The color fields of the selected register are routed to 3 DACs and M is directly routed to the M digital output.

After impedance matching, the CA, CB, and CC outputs can be used to drive a RGB analog color monitor. Alternatively one of these outputs can be used to drive a monochrome monitor thus providing up to 16 gray levels. The marking digital output can be used to drive analog video switches, thus providing video overlay facility on a color per color basis.

The blanking input forces the analog outputs and the M output to low level thus allowing the beam to be switched off during retrace intervals.

#### NOTES

- Each 4 bit-D/A converter is γ corrected in order to linearize the luminance driven on the screen versus the digital value. The typical digital to voltage conversion law is given table 1. The output voltages are proportionnal to the analog supply voltage VDDC. When required, setting VDCC allows a gain adjustment. But in most applications, VDDC and VDD can be derived from thesame supply through independent decoupling.

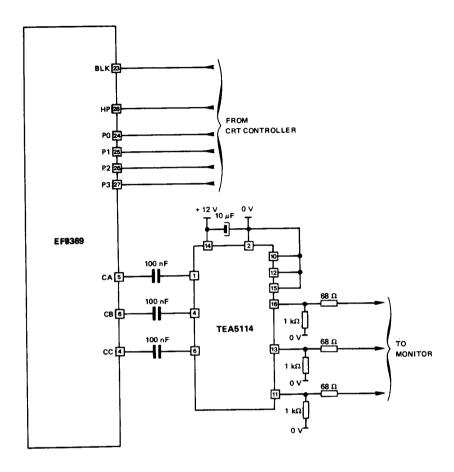

- 2. CA, CB and CC are high impedance outputs (500  $\Omega$  typical) which require proper adaptation in most applications. THOMSON SEMICONDUCTORS TEA 5114 provides such a 1 V 75  $\Omega$  low cost adaptation. (See fig. 2).

- 3. As the CLUT is shared between microprocessor access and video access, a low level is forced on the CA, CB, CC and M outputs during any chip select periods. To avoid to spoil the screen with black strokes it is recommended to access the CLUT from the microprocessor only during the retrace periods.

- 4. RESET This input forces CA, CB, CC and M outputs to a low level until the next microprocessor access. At power on or at the beginning of a session RESET allows to keep a clean black screen until proper initialization.

### INTERFACE WITH EF6805CT

NOTE: Each digital or analog ground must be separately connected to EF9369 pin 1. (See AN-059).

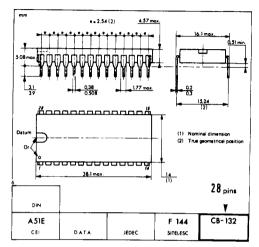

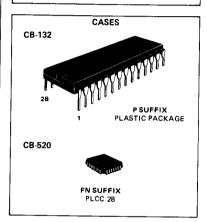

P SUFFIX PLASTIC PACKAGE

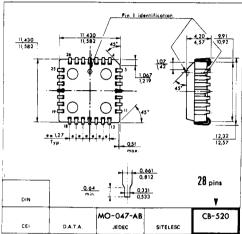

FN SUFFIX PLCC 28