# EG2183 Datasheet

High-power MOS transistor, IGBT transistor gate driver chip

### Version Change record

| Date             | Description                         |

|------------------|-------------------------------------|

| October 22, 2016 | First draft of the EG2183 Datasheet |

|                  |                                     |

|                  |                                     |

|                  |                                     |

|                  |                                     |

|                  |                                     |

|                  |                                     |

|                  |                                     |

|                  |                                     |

|                  |                                     |

|                  |                                     |

|                  |                                     |

|                  |                                     |

|                  |                                     |

|                  |                                     |

|                  |                                     |

|                  |                                     |

### **Contents**

| 1.                            | Fea                | turestures                                                        | 1 |  |  |  |  |

|-------------------------------|--------------------|-------------------------------------------------------------------|---|--|--|--|--|

| 2.                            | Description        |                                                                   |   |  |  |  |  |

| 3.                            | App                | lication areas                                                    | 1 |  |  |  |  |

| 4.                            |                    |                                                                   |   |  |  |  |  |

|                               |                    | Pin definition                                                    |   |  |  |  |  |

|                               |                    | Pin description                                                   |   |  |  |  |  |

| 5.                            |                    | k diagram                                                         |   |  |  |  |  |

| 6.                            |                    |                                                                   |   |  |  |  |  |

| 7. Electrical characteristics |                    |                                                                   |   |  |  |  |  |

|                               | 7.1                | Limit parameters                                                  | 2 |  |  |  |  |

|                               |                    | Typical parameters                                                |   |  |  |  |  |

|                               | 7.3                | Switching time characteristics and dead time waveform diagram     |   |  |  |  |  |

| 8.                            | Application design |                                                                   |   |  |  |  |  |

|                               |                    | VCC terminal supply voltage                                       |   |  |  |  |  |

|                               | 8.2                | Input logic signal requirements and output driver characteristics |   |  |  |  |  |

|                               | 8.3                | Bootstrap circuit                                                 |   |  |  |  |  |

| 9.                            | Pacl               | kage size                                                         |   |  |  |  |  |

|                               |                    | SO8 package size                                                  | c |  |  |  |  |

### EG2183 Datasheet V1.0

#### 1. Features

- High-end suspension bootstrap power supply design, withstand voltage up to 600V

- Adapts to 5V, 3.3 V input voltages

- Maximum frequency support 500KHZ

- Low-side VCC voltage range 3.5 V-20V

- Output current capability IO+/- 2A/2.5 A

- Built-in dead zone control circuit

- Comes with locking function, completely eliminate the upper and lower tube output is turned on at the same time

- HIN input channel is active at high level, controlling high-end HO

- LIN input channel is active at low level, controlling low-end LO output

- Fewer peripheral devices

- Quiescent current less than 20uA, ideal for battery applications

- Package form: SOP-8

### 2. Description

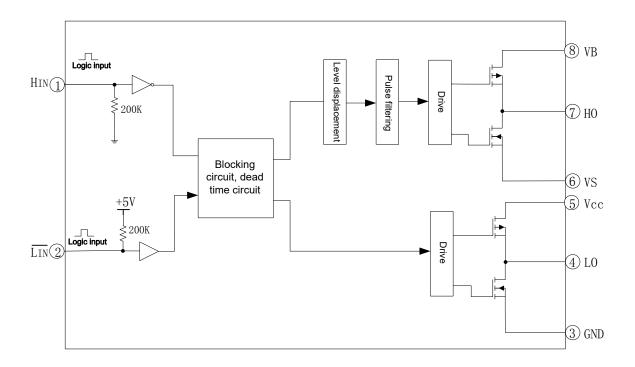

EG2183 is a cost-effective high-power MOS transistor, IGBT transistor Gate Drive dedicated chip, integrated logic signal input processing circuit, dead zone control circuit, latch circuit, level displacement circuit, pulse filter circuit and output drive circuit, dedicated to brushless motor controller drive circuit.

EG2183 high-side operating voltage up to 600V, low-side VCC supply voltage range is wide 3.5 V ~ 20V, static power consumption is less than 20uA. The chip has a latching function to prevent the output power tube is turned on at the same time, the input channel HIN built-in a 200k pull-down resistor, LIN built-in pull-up 5V high potential, when the input floating so that the upper and lower power MOS transistor is turned off, the output current capability IO+/- 2/2. 5 A,using SOP8 package.

#### 3. Application Areas

- Mobile power supply high voltage fast charge switching power supply

- Electric vehicle controller

- Variable frequency pump controller

- 600V step-down switching power supply

- Brushless motor driver

- High voltage Class-D power amplifier

### 4. Pin

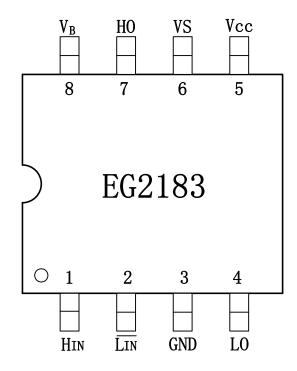

#### 4.1 Pin definition

Figure 4-1. EG2183 pin definition

### 4.2 Pin description

| Pin № | Pin name | I/O   | Description                                                                                                                                                                      |  |

|-------|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1     | HIN      | I     | Logic input control signal active high, control the high-side power MOS transistor is turned on and off "0" is the off power MOS transistor "1" is the open power MOS transistor |  |

| 2     | LIN      | ı     | Logic input control signal active low, control the low-side power MOS transistor is turned on and off "1" is the off power MOS transistor "0" is the open power MOS transistor   |  |

| 3     | GND      | GND   | The ground end of the chip.                                                                                                                                                      |  |

| 4     | LO       | 0     | The output controls the conduction and shutdown of the low-side MOS transistor                                                                                                   |  |

| 5     | Vcc      | Power | Chip power input, voltage range 2.8 V-20V,an external high-frequency 0.1 uF bypass capacitor can reduce the high-frequency noise at the input of the chip                        |  |

| 6     | VS       | 0     | High-end suspended Ground end                                                                                                                                                    |  |

| 7     | НО       | 0     | The output controls the on and off of the high-side MOS transistor                                                                                                               |  |

| 8     | VB       | Power | High-end suspended power supply                                                                                                                                                  |  |

### 5. Block diagram

Figure 5-1. EG2183 internal circuit diagram

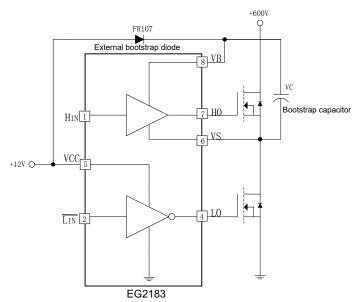

## 6. Typical application circuit

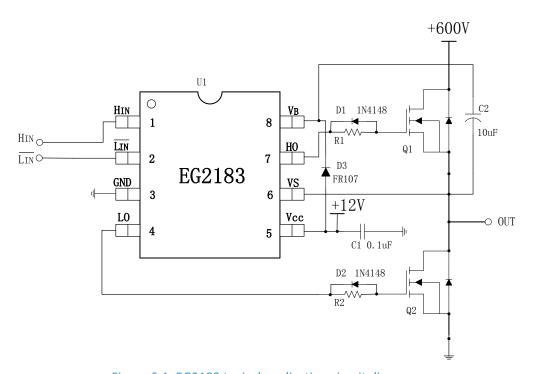

Figure 6-1. EG2183 typical application circuit diagram

### 7. Electrical characteristics

#### 7.1 Limit parameters

Without further explanation, at TA=25 ℃ conditions

| Symbols | Parameter name                           | Test conditions | Min.          | Max.     | Units         |

|---------|------------------------------------------|-----------------|---------------|----------|---------------|

| VB      | High side floating absolute voltage      | -               | -0.3          | 600      | V             |

| VS      | High side floating supply offset voltage | -               | VB-20         | VB+0.3   | V             |

| НО      | High side floating supply offset voltage | _               | VS-0.3 VB+0.3 |          | V             |

| LO      | Low side output voltage                  | _               | -0.3          | VCC+0.3  | V             |

| VCC     | Low side and logic fixed supply voltage  | _               | -0.3 20       |          | V             |

| HIN     | Logic input voltage (HIN)                | _               | -0.3          | VCC+0. 3 | V             |

| LIN     | Logic input voltage (LIN)                | _               | -0.3          | 6        | ٧             |

| TA      | Ambient temperature                      | _               | -45           | 125      | Ç             |

| Tstr    | Storage temperature                      | _               | -55           | 150      | င             |

| TL      | Soldering temperature                    | T=10S           | - 300         |          | ${\mathbb C}$ |

Note: exceeding the listed limit parameters may cause permanent damage to the chip, operating in extreme conditions for a long time will affect the reliability of the chip.

#### 7.2 Typical parameters

Without further explanation, at TA=25  $^{\circ}$ C, Vcc=12V, load capacitance CL=10NF conditions

| Parameter name                                      | Symbols                                           | Test conditions                             | Min. | Typical | Max. | Units |  |

|-----------------------------------------------------|---------------------------------------------------|---------------------------------------------|------|---------|------|-------|--|

| Power supply                                        | Vcc                                               | -                                           | 3.5  | 12      | 20   | V     |  |

| Quiescent current                                   | Icc                                               | Input floating, VCC=12V                     | -    | -       | 30   | uA    |  |

| Input logic signal high potential                   | Vin(H)                                            | All input control signals                   | 2.5  | -       | -    | V     |  |

| Input logic signal low potential                    | Vin(L)                                            | All input control signals                   | -0.3 | 0       | 1.0  | ٧     |  |

| Current at the high level of the input logic signal | Iin(H)                                            | Vin=5V                                      | -    | -       | 20   | uA    |  |

| Input logic signal low current                      | Iin(L)                                            | Vin=OV                                      | -20  | -       | -    | uA    |  |

| Low-side output LO                                  | Low-side output LO switching time characteristics |                                             |      |         |      |       |  |

| On delay                                            | Ton                                               | See Figure 7-1                              | -    | 280     | 400  | ns    |  |

| Off delay                                           | Toff                                              | See Figure 7-1                              | -    | 125     | 300  | ns    |  |

| Rise Time                                           | Tr                                                | See Figure 7-1                              | -    | 120     | 200  | ns    |  |

| Descent time                                        | Tf                                                | See Figure 7-1                              | -    | 80      | 100  | ns    |  |

| High-side output HO                                 | switching tim                                     | e characteristics                           |      |         |      |       |  |

| On delay                                            | Ton                                               | See Figure 7-2                              | -    | 250     | 400  | ns    |  |

| Off delay                                           | Toff                                              | See Figure 7-2                              | -    | 180     | 400  | ns    |  |

| Rise Time                                           | Tr                                                | See Figure 7-2                              | -    | 120     | 200  | ns    |  |

| Descent time                                        | Tf                                                | See Figure 7-2                              | -    | 80      | 100  | ns    |  |

| Dead time characteris                               | stics                                             | ,                                           |      |         |      |       |  |

| Dead time                                           | DT                                                | See Figure 7-3,<br>No load capacitance CL=0 | 50   | 100     | 300  | ns    |  |

| IO output maximum drive capability                  |                                                   |                                             |      |         |      |       |  |

| IO output pull current                              | I0+                                               | Vo=0V,VIN=VIH<br>PW≤10uS                    | 1.8  | 2       | -    | А     |  |

| IO output sink current                              | I0-                                               | Vo=12V,VIN=VIL<br>PW≤10uS                   | 2    | 2.5     | -    | А     |  |

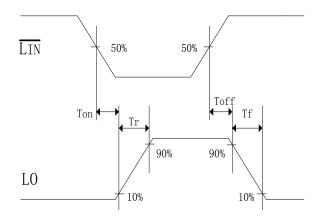

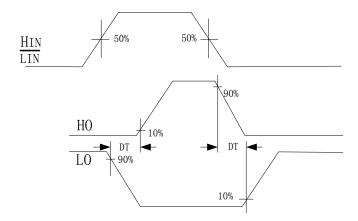

### 7.3 Switching time characteristics and dead time waveform

50% 50% HIN Toff Ton  ${\rm Tr}$ 90% 90% Н0 10% 10%

Figure 7-1. Low-side output LO switching time waveform diagram

Figure 7-2. High-side output HO switching time waveform

Figure 7-3. Dead time waveform

### 8. Application Design

#### 8.1 VCC terminal power supply voltage

For different MOS transistors, choose different drive voltages. The recommended power supply VCC operating voltage for high-voltage turn-on MOS transistors is typically 10V-15V; the recommended power supply VCC operating voltage for low-voltage turn-on MOS transistors is 3.5V-10V.

#### 8.2 Input logic signal requirements and output driver characteristics

The main functions of EG2183 include logic signal input processing, dead time control, level conversion function, floating bootstrap power supply structure and upper and lower bridge totem pole output. The high-level threshold of the logic signal input terminal is 2.5V or more, and the low-level threshold is below 1.0V. The output current of the logic signal is required to be small, so that the MCU output logic signal can be directly connected to the input channel of EG2183.

The maximum input of the high-end high-side and low-side output drivers can reach 2.5A and the maximum output current can reach 2A. The high-side high-side channel can withstand a voltage of 600V, and conduction between the input logic signal and the output control signal The delay is small, the low-end output turn-on conduction delay is 280ns, the turn-off conduction delay is 125ns, the high-end output turn-on conduction delay is 250ns, and the turn-off conduction delay is 180ns. The rise time of low-side output turn-on is 110ns, the fall time of turn-off is 50ns, the rise time of high-end output turn-on is 110ns, and the fall time of turn-off is 50ns.

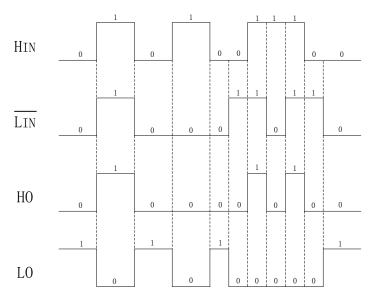

The logic function diagram of input signal and output signal is shown in Figure 8-2:

Figure 8-2. Input signal and output signal logic function diagram

Logical truth table of input signal and output signal:

High-power MOS transistor, IGBT transistor gate driver chip

Input Output Input and output logic HIN (pin 4) LIN (pin 3) HO (pin 7) LO (pin 5) 0 0 1

0 0 0 1 1 0 0 0 0

It can be seen from the truth table that when the input logic signals HIN and LIN are both "0" and non-simultaneously "1", the driver control output HO and LO are both "0" and the upper and lower power tubes are turned off at the same time. When the logic signals HIN and LIN are both "0", the driver control output HO is "0", the upper tube is turned off, and LO is "1", the lower tube is turned on. When the input logic signals HIN and LIN are both "1", the driver controls the output HO is "1", the upper tube is turned on, and the LO is "0", the lower tube is turned off; the internal logic processor prevents the upper and lower power tubes of the controller from being turned on at the same time, and has a mutual locking function.

#### 8.3 Bootstrap circuit

The EG2183 adopts a bootstrap floating drive power structure to greatly simplify the design of the drive power supply. Only one power supply voltage VCC can complete the drive of the high-end N-channel MOS transistor and the low-end N-channel MOS transistor, which brings practical application. It's a great convenience. EG2183 can use an external bootstrap diode as shown in Figure 8-3 and a bootstrap capacitor to automatically complete the bootstrap function. It is assumed that the C bootstrap capacitor has been charged to a sufficient voltage during the period when the lower tube is turned on and the upper tube is turned off (Vc=VCC) ), when the HO output high level, when the upper tube is turned on and the lower tube is turned off, the voltage on the VC bootstrap capacitor will be equivalent to a voltage source as the power supply for the internal drivers VB and VS to complete the drive of the high-side N-channel MOS transistor.

Figure 8-3. EG2183 bootstrap circuit structure

### 9. Package size

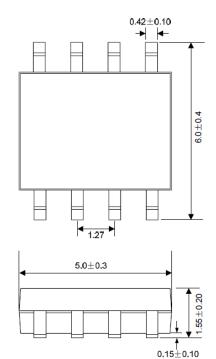

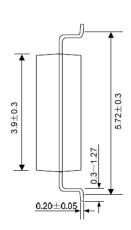

### 9.1 SO8 Package size