### Data Sheet

#### January 31, 2005

### FN7376.2

### 6-Channel Clock Driver

intercil

The EL5001 is a 6-channel level shifting driver designed primarily for use as a clock driver in LTPS LCD displays. The EL5001 buffers and level shifts six logic level input signals. The six channels are grouped in to two sets, one of two channels and one of four channels. Each set can be configured in the inverting or non-inverting modes. Operating from 3.3V input logic, the output swing is set using two reference input pins. These pins can be up to 18V differential and are not buffered, so should therefore be bypassed effectively.

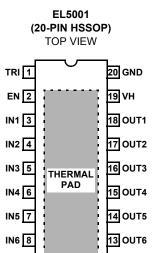

The EL5001 is designed to drive capacitive loads of 500pF with rise and fall times of just 20ns. A three-state pin is provided to set all outputs in to a high impedance mode. The ENABLE pin can be used to put the device in to a power save mode where the power consumption drops to just  $3\mu$ A.

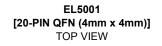

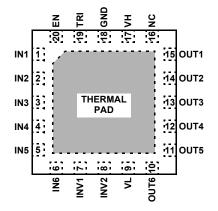

The EL5001 is available in 20-pin QFN (4mm x 4mm) and HTSSOP packages. Both are specified for operation over the -40 $^{\circ}$ C to +85 $^{\circ}$ C temperature range.

#### Features

- SIx inverting/non-inverting channels

- 3.3V input logic

- 18V output

- 250µA typical supply current

- · Drives up to 500pF

- $T_R/T_F = 35$ ns max

- · Disable function

- · 20-pin QFN (4mm x 4mm) and HTSSOP packages

- · Pb-free available (RoHS compliant)

#### Applications

- · LTPS LCD clock drivers

- CCD driving

- Level shifters

|                             | PACKAGE                                | TAPE &<br>REEL | PKG. DWG. # |                              |                               | TAPE & | PKG. DWG. # |  |

|-----------------------------|----------------------------------------|----------------|-------------|------------------------------|-------------------------------|--------|-------------|--|

| PART NUMBER                 |                                        |                |             | PART NUMBER                  | PACKAGE                       | REEL   |             |  |

| EL5001IL                    | 20-Pin QFN<br>(4mm x 4mm)              | -              | MDP0046     | EL5001IRE                    | 20-Pin<br>HTSSOP              | -      | MDP0048     |  |

| EL5001IL-T7                 | 20-Pin QFN<br>(4mm x 4mm)              | 7"             | MDP0046     | EL5001IRE-T7                 | 20-Pin<br>HTSSOP              | 7"     | MDP0048     |  |

| EL5001IL-T13                | 20-Pin QFN<br>(4mm x 4mm)              | 13"            | MDP0046     | EL5001IRE-T13                | 20-Pin<br>HTSSOP              | 13"    | MDP0048     |  |

| EL5001ILZ<br>(See Note)     | 20-Pin QFN<br>(4mm x 4mm)<br>(Pb-Free) | -              | MDP0046     | EL5001IREZ<br>(See Note)     | 20-Pin<br>HTSSOP<br>(Pb-Free) | -      | MDP0048     |  |

| EL5001ILZ-T7<br>(See Note)  | 20-Pin QFN<br>(4mm x 4mm)<br>(Pb-Free) | 7"             | MDP0046     | EL5001IREZ-T7<br>(See Note)  | 20-Pin<br>HTSSOP<br>(Pb-Free) | 7"     | MDP0048     |  |

| EL5001ILZ-T13<br>(See Note) | 20-Pin QFN<br>(4mm x 4mm)<br>(Pb-Free) | 13"            | MDP0046     | EL5001IREZ-T13<br>(See Note) | 20-Pin<br>HTSSOP<br>(Pb-Free) | 13"    | MDP0048     |  |

NOTE: Intersil Pb-free products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020C.

#### CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. 1-888-INTERSIL or 321-724-7143 | Intersil (and design) is a registered trademark of Intersil Americas Inc. Copyright © Intersil Americas Inc. 2004, 2005. All Rights Reserved. All other trademarks mentioned are the property of their respective owners.

### **Ordering Information**

INV1 9 INV2 10 12 VL

11 NC

#### Absolute Maximum Ratings (T<sub>A</sub> = 25°C)

| Supply Voltage between V <sub>SD</sub> and GND | Maximum Die Temperature |

|------------------------------------------------|-------------------------|

| Ambient Operating Temperature40 C to +85 C     | Power Dissipation       |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

## $\label{eq:constraint} \textbf{Electrical Specifications} \quad V_{H} = 10 \text{V}, \ V_{L} = -5 \text{V}, \ \text{EN} = 3 \text{V}, \ \text{unless otherwise specified}.$

| PARAMETER                      | DESCRIPTION                                   | CONDITION                                    | MIN  | TYP   | MAX   | UNIT |

|--------------------------------|-----------------------------------------------|----------------------------------------------|------|-------|-------|------|

| POWER SUPPL                    | Y                                             | ·                                            |      |       |       |      |

| I <sub>S</sub>                 | Supply Current                                | EN = 3V, IN <sub>X</sub> = 0V                |      | 750   | 1200  | μA   |

|                                |                                               | EN = 3V, IN <sub>X</sub> = 3V                |      | 250   | 500   | μA   |

| I <sub>S_DIS</sub>             | Supply Current - Disabled                     | EN = 0V, IN <sub>X</sub> = 0V                |      | 3     |       | μA   |

| V <sub>LR</sub>                | V <sub>L</sub> Range                          |                                              | -13  |       | 0     | V    |

| V <sub>HR</sub>                | V <sub>H</sub> Range                          |                                              | 5    |       | 18    | V    |

| V <sub>H</sub> -V <sub>L</sub> | Maximum V <sub>H</sub> - V <sub>L</sub> Range |                                              | 0    |       | 18    | V    |

| INPUT                          |                                               |                                              |      |       | 1     |      |

| V <sub>IH</sub>                | Logic '1' Input Voltage                       |                                              | 2.0  |       |       | V    |

| I <sub>IH</sub>                | Logic '1' Input Current                       |                                              |      | 0.1   | 10    | μA   |

| V <sub>IL</sub>                | Logic '0' Input Voltage                       |                                              |      |       | 0.8   | V    |

| IIL                            | Logic '0' Input Current                       |                                              |      | 0.1   | 10    | μA   |

| C <sub>IN</sub>                | Input Capacitance                             |                                              |      | 3.5   |       | pF   |

| R <sub>IN</sub>                | Input Resistance                              |                                              |      | 50    |       | MΩ   |

| OUTPUT                         |                                               | I                                            |      |       | 1     |      |

| V <sub>OH</sub>                | V <sub>OUTL</sub> High                        | IN <sub>X</sub> = 10V, I <sub>L</sub> = 10mA | 9.80 | 9.88  |       | V    |

| V <sub>OL</sub>                | V <sub>OUTL</sub> Low                         | IN <sub>X</sub> = 0V, I <sub>L</sub> = -10mA |      | -4.90 | -4.88 | V    |

| R <sub>OH</sub>                | On Resistance V <sub>H</sub> to OUT           | I <sub>L</sub> = 50mA                        |      | 11    | 15    | Ω    |

| R <sub>OL</sub>                | On Resistance $V_L$ to OUT                    | I <sub>L</sub> = 50mA                        |      | 11    | 15    | Ω    |

| I <sub>PEAK</sub>              | Peak Output Current                           |                                              |      | 500   |       | mA   |

| ۱ <sub>L</sub>                 | Out Leakage Current                           |                                              |      | 0.1   | 0.5   | μA   |

| SWITCHING CH                   | IARACTERISTICS                                |                                              |      |       | 1     |      |

| t <sub>R</sub>                 | Rise Time                                     | C <sub>L</sub> = 500pF                       |      | 20    | 35    | ns   |

| t <sub>F</sub>                 | Fall Time                                     | C <sub>L</sub> = 500pF                       |      | 20    | 35    | ns   |

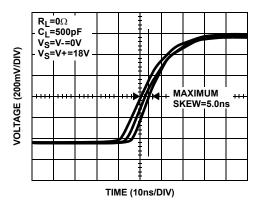

| t <sub>RFD</sub>               | T <sub>R</sub> , T <sub>F</sub> Matching      | C <sub>L</sub> = 500pF                       |      | 5     |       | ns   |

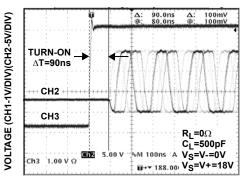

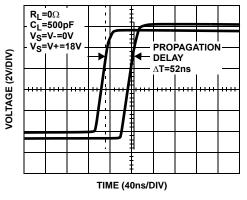

| t <sub>D</sub> +               | Turn On Delay                                 | C <sub>L</sub> = 500pF                       |      | 55    |       | ns   |

| t <sub>D</sub> -               | Turn Off Delay                                | C <sub>L</sub> = 500pF                       |      | 55    |       | ns   |

| t <sub>DD</sub>                | t <sub>D</sub> +, t <sub>D</sub> -, Matching  | C <sub>L</sub> = 500pF                       |      | 5     |       | ns   |

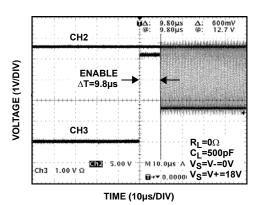

| t <sub>EN</sub>                | Enable Time                                   |                                              | 9.8  |       |       | μs   |

| t <sub>DIS</sub>               | Disable Time                                  |                                              | 2.2  |       |       | μs   |

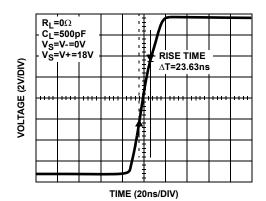

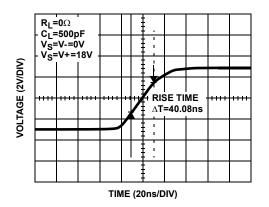

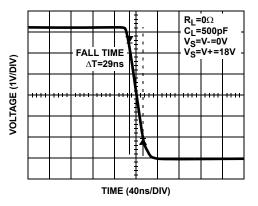

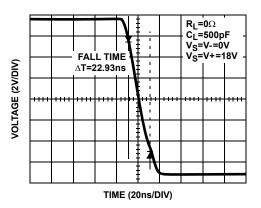

### **Typical Performance Curves**

FIGURE 1. RISE TIME OUTPUT  $6V_{\mbox{P-P}}$

FIGURE 3. RISE TIME OUTPUT 12VP-P

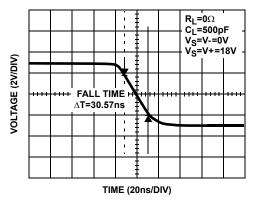

FIGURE 2. FALL TIME OUTPUT 6VP-P

FIGURE 4. FALL TIME OUTPUT 12VP-P

FIGURE 6. FALL TIME OUTPUT 5VP-P

### Typical Performance Curves (Continued)

TIME (100ns/DIV)

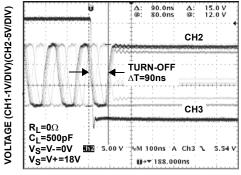

FIGURE 9. TURN-OFF (TRI)

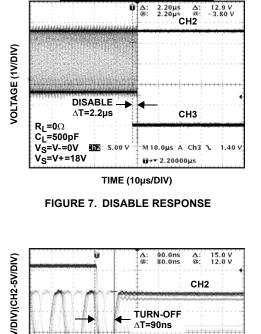

FIGURE 11. ENABLE/DISABLE THRESHOLD

FIGURE 8. ENABLE RESPONSE

TIME (100ns/DIV)

FIGURE 10. TURN-ON (TRI)

FIGURE 12. PROPAGATION DELAY

### Typical Performance Curves (Continued)

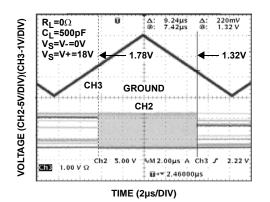

FIGURE 13. SKEW

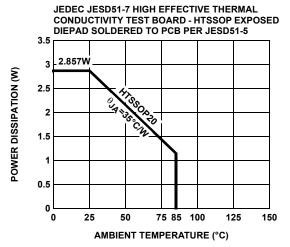

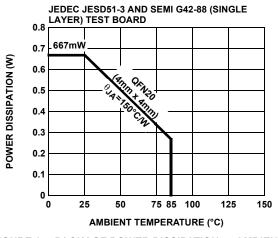

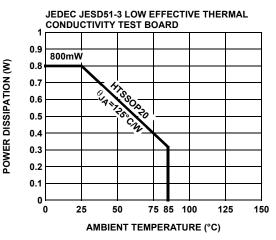

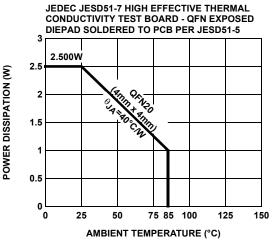

FIGURE 15. PACKAGE POWER DISSIPATION vs AMBIENT TEMPERATURE

FIGURE 17. PACKAGE POWER DISSIPATION vs AMBIENT TEMPERATURE

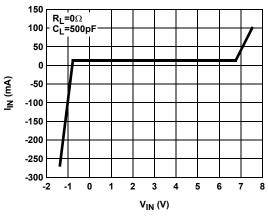

FIGURE 14. INPUT CURRENT vs VOLTAGE

FIGURE 16. PACKAGE POWER DISSIPATION vs AMBIENT TEMPERATURE

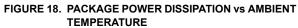

EL5001 Test Board Circuit Layout

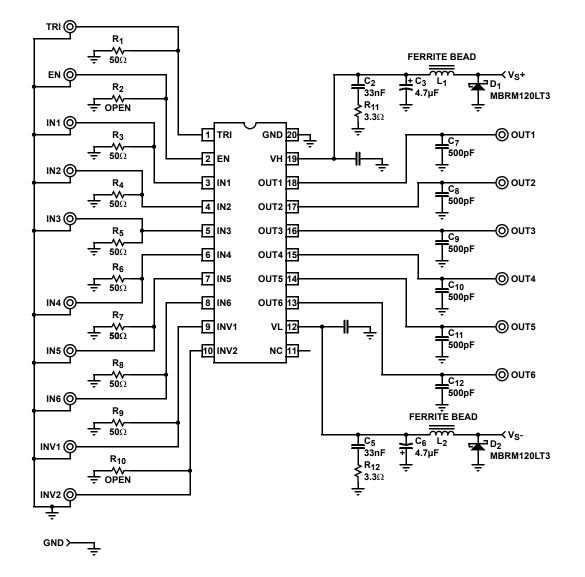

**Block Diagram**

### **Applications Information**

The EL5001, a six channel high performance buffer, is directed primarily as a clock driver to LPTS LCD display applications. The six input channels are grouped into one group of four inputs and one group of two inputs each with a single pin (INV1 or INV2) to toggle the polarity from inverting to non-inverting. Each channel consists of a single N-channel low side driver and single P-channel high side driver. These 11 $\Omega$  devices pull the output to either the high or low voltage on V<sub>H</sub> and V<sub>L</sub> respectively, depending on the logic input signal.

A common 3-state pin is available that when activated will pull all 6-channel outputs to the high impedance state. Enable and disable pins turn shutdown both inputs and outputs. Timing plots for 3-state, enable, and disable functions are included in the characterization documentation.

The EL5001 is available in either a 20-pin HTSSOP or QFN (4mm x 4mm) packages to provide a choice for power dissipation considerations.

#### Supply Voltage and Input Compatibility

The EL5001 is designed to operate at a maximum potential range from 0V to 18V. Because the EL5001 does not contain a true analog switch, the positive supply must always be 4V higher than the negative supply.

All input pins are compatible with both 3V and 5V CMOS signals. With the positive supply set to  $V_S$  = 5V the EL5001 is compatible with TTL inputs.

### Power Supply Bypassing

Due to the high switching currents generated by the EL5001 power supply bypassing is very important on both the positive and negative supplies. A 4.7 $\mu$ F tantalum capacitor can be used in parallel with a 0.1 $\mu$ F low-inductance ceramic MLC capacitor. As with all bypass components, these should be placed as close as possible to the supply pins. We also recommend the V<sub>L</sub> and V<sub>H</sub> pins have some level of bypassing especially when the device is driving highly capacitive loads.

### **Power Dissipation Calculation**

When switching at high speeds, or driving heavy loads, the EL5001 drive capability is limited by the rise in die temperature brought about by internal power dissipation. For reliable operation die temperature must be kept below  $T_{JMAX}$  (125°C). It is necessary to calculate the power dissipation for a given application prior to selecting package type.

Power dissipation may be calculated:

$$PD = (V_{S} \times I_{S}) + \sum (C_{INT} \times V_{S}^{2} \times f) + (C_{L} \times V_{OUT}^{2} \times f)$$

where:

$V_S$  = Total power supply to the EL5001 (from  $V_S$ + to  $V_S$ -)

$V_{OUT}$  = Swing on the output ( $V_{H} - V_{L}$ )

C<sub>L</sub> = Load capacitance

C<sub>INT</sub> = Internal load capacitance (80pF max)

$I_S$  = Quiescent supply current (3mA max)

f = Frequency

Having obtained the application's power dissipation, the maximum junction temperature can be calculated:

$$\mathsf{T}_{\mathsf{JMAX}} = \mathsf{T}_{\mathsf{MAX}} + \Theta_{\mathsf{JA}} \times \mathsf{PD}$$

where:

T<sub>JMAX</sub> = Maximum junction temperature (125°C)

T<sub>MAX</sub> = Maximum ambient operating temperature

PD = Power dissipation calculated above

$\theta_{JA}$  = Thermal resistance, junction to ambient, of the application (package + PCB combination)

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Intersil:

EL5001IREZ EL5001IREZ-T13 EL5001IREZ-T7