# Élan<sup>™</sup>SC520 Microcontroller Register Set Manual

Order #22005B

| DataSheet4U.com            |                           |                      |                       |                        |                        |

|----------------------------|---------------------------|----------------------|-----------------------|------------------------|------------------------|

|                            |                           |                      |                       |                        |                        |

|                            |                           |                      |                       |                        |                        |

|                            |                           |                      |                       |                        |                        |

|                            |                           |                      |                       |                        |                        |

|                            |                           |                      |                       |                        |                        |

|                            |                           |                      |                       |                        |                        |

|                            |                           |                      |                       |                        |                        |

|                            |                           |                      |                       |                        |                        |

|                            |                           |                      |                       |                        |                        |

|                            |                           |                      |                       |                        |                        |

|                            |                           |                      |                       |                        |                        |

|                            |                           |                      |                       |                        |                        |

|                            |                           |                      |                       |                        |                        |

|                            |                           |                      |                       |                        |                        |

|                            |                           |                      |                       |                        |                        |

|                            |                           |                      |                       |                        |                        |

|                            |                           |                      |                       |                        |                        |

|                            | © 2001 Adv                | anced Micro Dev      | vices, Inc. All righ  | its reserved.          |                        |

| The contents of this docum | ent are provided in conne | ection with Advanced | d Micro Devices, Inc. | . ("AMD") products. AM | MD makes no representa |

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

#### **Trademarks**

AMD, the AMD logo, and combinations thereof, AMDebug, E86, and Élan are trademarks, Am486 and Am5<sub>x</sub>86 are registered trademarks, and FusionE86 is a service mark of Advanced Micro Devices, Inc.

Product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

# IF YOU HAVE QUESTIONS, WE'RE HERE TO HELP YOU.

The AMD customer service network includes U.S. offices, international offices, and a customer training center. Expert technical assistance is available from the AMD worldwide staff of field application engineers and factory support staff to answer E86™ family hardware and software development questions.

Frequently accessed numbers are listed below. Additional contact information is listed on the back of this manual. AMD's WWW site lists the latest phone numbers.

# **Technical Support**

Answers to technical questions are available online, through e-mail, and by telephone.

Go to AMD's home page at **www.amd.com** and follow the Support link for the latest AMD technical support phone numbers, software, and Frequently Asked Questions.

For technical support questions on all E86 products, send e-mail to **epd.support@amd.com** (in the US and Canada) or **euro.tech@amd.com** (in Europe and the UK).

You can also call the AMD Corporate Applications Hotline at:

(800) 222-9323 Toll-free for U.S. and Canada 44-(0) 1276-803-299 U.K. and Europe hotline

# **WWW Support**

For specific information on E86 products, access the AMD home page at **www.amd.com** and follow the Embedded Processors link. These pages provide information on upcoming product releases, overviews of existing products, information on product support and tools, and a list of technical documentation. Support tools include online benchmarking tools and CodeKit software—tested source code example applications. Many of the technical documents are available online in PDF form.

Questions, requests, and input concerning AMD's WWW pages can be sent via e-mail to web.feedback@amd.com.

# **Documentation and Literature Support**

Data books, user's manuals, data sheets, application notes, and product CDs are free with a simple phone call. Internationally, contact your local AMD sales office for product literature.

To order literature, go to **www.amd.com/support/literature.html** or, in the U.S. and Canada, call (800) 222-9323.

# **Third-Party Support**

AMD FusionE86<sup>SM</sup> partners provide an array of products designed to meet critical time-to-market needs. Products and solutions available include emulators, hardware and software debuggers, board-level products, and software development tools, among others. The WWW site and the  $E86^{TM}$  Family Products Development Tools CD, order #21058, describe these solutions. In addition, mature development tools and applications for the x86 platform are widely available in the general marketplace.

# AMDA

# **TABLE OF CONTENTS**

| PREFACE          | INTRODUCTION                                            | XV   |

|------------------|---------------------------------------------------------|------|

|                  | Élan™SC520 Microcontroller                              |      |

|                  | Purpose of this Manual                                  |      |

|                  | Intended Audience                                       |      |

|                  | Overview of this Manual                                 |      |

|                  | Related Documents                                       |      |

|                  | Additional Information                                  |      |

|                  | Documentation Conventions                               |      |

| CHAPTER 1        | CONFIGURATION REGISTER OVERVIEW                         | 1-1  |

|                  | 1.1 Memory-Mapped Configuration Region (MMCR) Registers | 1-1  |

|                  | 1.2 Direct-Mapped I/O Registers                         |      |

|                  | 1.3 PCI Host Bridge Indexed Configuration Registers     | 1-10 |

|                  | 1.4 RTC and CMOS RAM Indexed Registers                  | 1-11 |

| CHAPTER 2        | SYSTEM ADDRESS MAPPING REGISTERS                        | 2-1  |

|                  | 2.1 Overview                                            |      |

|                  | 2.2 Registers                                           |      |

|                  | Address Decode Control (ADDDECCTL)                      |      |

|                  | Write-Protect Violation Status (WPVSTA)                 |      |

|                  | Programmable Address Region 0 (PAR0)                    |      |

|                  | Programmable Address Region 2 (PAR2)                    |      |

|                  | Programmable Address Region 3 (PAR3)                    |      |

|                  | Programmable Address Region 4 (PAR4)                    |      |

|                  | Programmable Address Region 5 (PAR5)                    |      |

|                  | Programmable Address Region 6 (PAR6)                    |      |

|                  | Programmable Address Region 7 (PAR7)                    |      |

|                  | Programmable Address Region 8 (PAR8)                    |      |

|                  | Programmable Address Region 9 (PAR9)                    |      |

|                  | Programmable Address Region 10 (PAR10)                  |      |

|                  | Programmable Address Region 11 (PAR11)                  |      |

|                  | Programmable Address Region 12 (PAR12)                  |      |

|                  | Programmable Address Region 13 (PAR13)                  |      |

|                  | Programmable Address Region 14 (PAR14)                  |      |

|                  | Programmable Address Region 15 (PAR15)                  |      |

|                  | Configuration Base Address (CBAR)                       | 2-9  |

| <b>CHAPTER 3</b> | RESET GENERATION REGISTERS                              | 3-1  |

|                  | 3.1 Overview                                            |      |

|                  | 3.2 Registers                                           |      |

|                  | System Board Information (SYSINFO)                      |      |

|                  | Reset Configuration (RESCFG)                            |      |

|                  | Reset Status (RESSTA)                                   |      |

|                  | SCP Data Port (SCPDATA)                                 |      |

|                  | SCP Command Port (SCPCMD)                               |      |

|                  | System Control Port A (SYSCTLA)                         | 3-9  |

| CHAPTER 4 | Am5 <sub>X</sub> 86 <sup>®</sup> CPU REGISTERS                   | 4-1        |

|-----------|------------------------------------------------------------------|------------|

|           | 4.1 Overview.         4.2 Registers                              |            |

|           | Élan™SC520 Microcontroller Revision ID (REVID)                   | 4-2        |

| CHAPTER 5 | SYSTEM ARBITRATION REGISTERS                                     | 5-1        |

| CHAPTER 3 | 5.1 Overview                                                     | _          |

|           | 5.2 Registers                                                    |            |

|           | System Arbiter Control (SYSARBCTL)                               | 5-2        |

|           | PCI Bus Arbiter Status (PCIARBSTA)                               |            |

|           | System Arbiter Master Enable (SYSARBMENB)                        |            |

|           |                                                                  |            |

| CHAPTER 6 | PCI BUS HOST BRIDGE REGISTERS 6.1 Overview                       | 6-1        |

|           | 6.2 Registers                                                    |            |

|           | Host Bridge Control (HBCTL)                                      |            |

|           | Host Bridge Target Interrupt Control (HBTGTIRQCTL)               | 6-5        |

|           | Host Bridge Target Interrupt Status (HBTGTIRQSTA)                |            |

|           | Host Bridge Master Interrupt Control (HBMSTIRQCTL)               |            |

|           | Host Bridge Master Interrupt Status (HBMSTIRQSTA)                |            |

|           | PCI Configuration Address (PCICFGADR)                            |            |

|           | PCI Configuration Data (PCICFGDATA)                              | 6-17       |

|           | Device/Vendor ID (PCIDEVID)                                      |            |

|           | Status/Command (PCISTACMD)                                       |            |

|           | Class Code/Revision ID (PCICCREVID)                              |            |

|           | Master Retry Time-Out (PCIMRETRYTO)                              | 6-24       |

| CHAPTER 7 | SDRAM CONTROLLER REGISTERS                                       | 7-1        |

|           | 7.1 Overview                                                     |            |

|           | 7.2 Registers                                                    |            |

|           | SDRAM Timing Control (DRCTL)                                     | 7-2        |

|           | SDRAM Timing Control (DRCTMCTL)SDRAM Bank Configuration (DRCCFG) | 7-5        |

|           | SDRAM Bank 0–3 Ending Address (DRCBENDADR)                       |            |

|           | ECC Control (ECCCTL)                                             | 7-9        |

|           | ECC Status (ECCSTA)                                              | 7-10       |

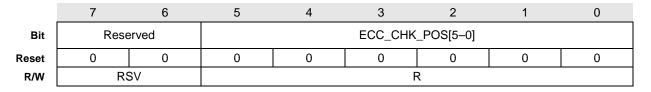

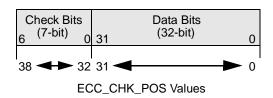

|           | ECC Check Bit Position (ECCCKBPOS)                               |            |

|           | ECC Single-Bit Error Address (ECCSBADD)                          |            |

|           | ECC Multi-Bit Error Address (ECCMBADD)                           | 7-15       |

| CHAPTER 8 | WRITE BUFFER AND READ BUFFER REGISTER                            | 8-1        |

|           | 8.1 Overview                                                     | 8-1        |

|           | 8.2 Register                                                     |            |

|           | SDRAM Buffer Control (DBCTL)                                     | 8-2        |

| CHAPTER 9 | ROM/FLASH CONTROLLER REGISTERS                                   | 9-1        |

|           | 9.1 Overview                                                     |            |

|           | 9.2 Registers                                                    |            |

|           | ROMCS1 Control (ROMCS1CTL)                                       | 9-2<br>9-4 |

|           | ROMCS2 Control (ROMCS2CTL)                                       |            |

| CHAPTER 10        | GENERAL-PURPOSE BUS CONTROLLER REGISTERS                                                                          | 10-1  |

|-------------------|-------------------------------------------------------------------------------------------------------------------|-------|

|                   | 10.1 Overview                                                                                                     |       |

|                   | 10.2 Registers                                                                                                    |       |

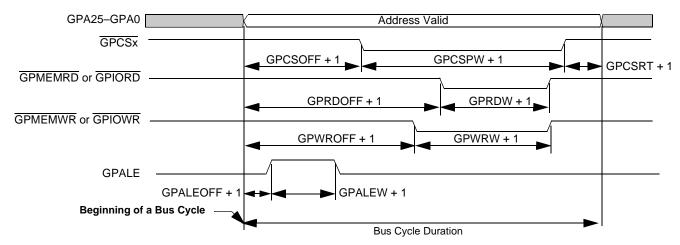

|                   | GP Echo Mode (GPECHO)                                                                                             | 10-2  |

|                   | GP Chip Select Data Width (GPCSDW)                                                                                |       |

|                   | GP Chip Select Qualification (GPCSQUAL)                                                                           |       |

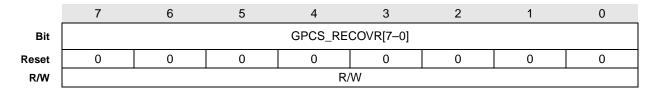

|                   | GP Chip Select Recovery Time (GPCSRT)                                                                             |       |

|                   | GP Chip Select Pulse Width (GPCSPW)                                                                               |       |

|                   | GP Read Pulse Width (GPRDW)                                                                                       |       |

|                   | GP Read Offset (GPRDOFF)                                                                                          |       |

|                   | GP Write Pulse Width (GPWRW)                                                                                      |       |

|                   | GP Write Offset (GPWROFF)                                                                                         |       |

|                   | GPALE Pulse Width (GPALEW)                                                                                        |       |

|                   | GPALE Offset (GPALEOFF)                                                                                           |       |

| <b>CHAPTER 11</b> | GP DMA CONTROLLER REGISTERS                                                                                       | 11-1  |

|                   | 11.1 Overview                                                                                                     |       |

|                   | 11.2 Registers                                                                                                    |       |

|                   | GP-DMA Control (GPDMACTL)                                                                                         |       |

|                   | GP-DMA Memory-Mapped I/O (GPDMAMMIO)                                                                              |       |

|                   | GP-DMA Resource Channel Map A (GPDMAEXTCHMAPA)                                                                    |       |

|                   | GP-DMA Resource Channel Map B (GPDMAEXTCHMAPB) GP-DMA Channel 0 Extended Page (GPDMAEXTPG0)                       |       |

|                   | GP-DMA Channel 1 Extended Page (GPDMAEXTPG0)                                                                      |       |

|                   | GP-DMA Channel 2 Extended Page (GPDMAEXTPG2)                                                                      |       |

|                   | GP-DMA Channel 3 Extended Page (GPDMAEXTPG3)                                                                      |       |

|                   | GP-DMA Channel 5 Extended Page (GPDMAEXTPG5)                                                                      |       |

|                   | GP-DMA Channel 6 Extended Page (GPDMAEXTPG6)                                                                      |       |

|                   | GP-DMA Channel 7 Extended Page (GPDMAEXTPG7)                                                                      |       |

|                   | GP-DMA Channel 3 Extended Transfer Count (GPDMAEXTTC3)                                                            |       |

|                   | GP-DMA Channel 5 Extended Transfer Count (GPDMAEXTTC5)                                                            |       |

|                   | GP-DMA Channel 6 Extended Transfer Count (GPDMAEXTTC6)                                                            |       |

|                   | GP-DMA Channel 7 Extended Transfer Count (GPDMAEXTTC7).                                                           |       |

|                   | Buffer Chaining Control (GPDMABCCTL)                                                                              |       |

|                   | Buffer Chaining Status (GPDMABCSTA)                                                                               |       |

|                   | Buffer Chaining Valid (GPDMABCVAL)                                                                                |       |

|                   | GP-DMA Channel 3 Next Address Low (GPDMANXTADDL3)                                                                 |       |

|                   | GP-DMA Channel 3 Next Address High (GPDMANXTADDH3)                                                                | 11-27 |

|                   | GP-DMA Channel 5 Next Address Low (GPDMANXTADDL5)                                                                 |       |

|                   | GP-DMA Channel 5 Next Address High (GPDMANXTADDH5)                                                                |       |

|                   | GP-DMA Channel 6 Next Address Low (GPDMANXTADDL6)                                                                 |       |

|                   | GP-DMA Channel 6 Next Address High (GPDMANXTADDH6)                                                                |       |

|                   | GP-DMA Channel 7 Next Address Low (GPDMANXTADDL7)                                                                 |       |

|                   | GP-DMA Channel 7 Next Address High (GPDMANXTADDH7)                                                                |       |

|                   | GP-DMA Channel 3 Next Transfer Count Low (GPDMANXTTCL3).                                                          |       |

|                   | GP-DMA Channel 3 Next Transfer Count High (GPDMANXTTCH3)                                                          |       |

|                   | GP-DMA Channel 5 Next Transfer Count Low (GPDMANXTTCL5).                                                          |       |

|                   | GP-DMA Channel 5 Next Transfer Count High (GPDMANXTTCH5) GP-DMA Channel 6 Next Transfer Count Low (GPDMANXTTCL6). |       |

|                   | GP-DMA Channel 6 Next Transfer Count Low (GPDMANXTTCL6).                                                          |       |

|                   | GP-DMA Channel 7 Next Transfer Count Fight (GP DMANXTTCH).                                                        |       |

|                   | GP-DMA Channel 7 Next Transfer Count High (GPDMANXTTCH7)                                                          |       |

|                   | Slave DMA Channel 0 Memory Address (GPDMA0MAR)                                                                    |       |

|                   | Slave DMA Channel 0 Transfer Count (GPDMA0TC)                                                                     | 11-43 |

|                   | Slave DMA Channel 1 Memory Address (GPDMA1MAR)                                                                    |       |

|                   | Slave DMA Channel 1 Transfer Count (GPDMA1TC)                                                                     |       |

|                   | Slave DMA Channel 2 Memory Address (GPDMA2MAR)                                                                    |       |

|                   | Slave DMA Channel 2 Transfer Count (GPDMA2TC)                                                                     | 11-47 |

|            | Slave DMA Channel 3 Memory Address (GPDMA3MAR)    | 11-48 |

|------------|---------------------------------------------------|-------|

|            | Slave DMA Channel 3 Transfer Count (GPDMA3TC)     |       |

|            | Slave DMA Channel 0-3 Status (SLDMASTA)           |       |

|            | Slave DMA Channel 0-3 Control (SLDMACTL)          |       |

|            | Slave Software DRQ(n) Request (SLDMASWREQ)        |       |

|            | Slave DMA Channel 0-3 Mask (SLDMAMSK)             |       |

|            | Slave DMA Channel 0-3 Mode (SLDMAMODE)            | 11-55 |

|            | Slave DMA Clear Byte Pointer (SLDMACBP)           |       |

|            | Slave DMA Controller Reset (SLDMARST)             |       |

|            | Slave DMA Controller Temporary (SLDMATMP)         |       |

|            | Slave DMA Mask Reset (SLDMAMSKRST)                |       |

|            | Slave DMA General Mask (SLDMAGENMSK)              |       |

|            | General 0 (GPDMAGR0)                              |       |

|            | Slave DMA Channel 2 Page (GPDMA2PG)               | 11-63 |

|            | Slave DMA Channel 3 Page (GPDMA3PG)               |       |

|            | Slave DMA Channel 1 Page (GPDMA1PG)               |       |

|            | General 1 (GPDMAGR1)                              |       |

|            | General 2 (GPDMAGR2)                              |       |

|            | General 3 (GPDMAGR3)                              |       |

|            | Slave DMA Channel 0 Page (GPDMA0PG)               |       |

|            | General 4 (GPDMAGR4)                              |       |

|            | Master DMA Channel 6 Page (GPDMA6PG)              |       |

|            | Master DMA Channel 7 Page (GPDMA7PG)              |       |

|            | Master DMA Channel 5 Page (GPDMA5PG)              |       |

|            | General 5 (GPDMAGR5)                              |       |

|            | General 6 (GPDMAGR6)                              |       |

|            | General 7 (GPDMAGR7)                              |       |

|            | General 8 (GPDMAGR8)                              |       |

|            | Master DMA Channel 4 Memory Address (GPDMA4MAR)   |       |

|            | Master DMA Channel 4 Transfer Count (GPDMA4TC)    |       |

|            | Master DMA Channel 5 Memory Address (GPDMA5MAR)   |       |

|            | Master DMA Channel 5 Transfer Count (GPDMA5TC)    |       |

|            | Master DMA Channel 6 Memory Address (GPDMA6MAR)   |       |

|            | Master DMA Channel 6 Transfer Count (GPDMA6TC)    |       |

|            | Master DMA Channel 7 Memory Address (GPDMA7MAR)   |       |

|            | Master DMA Channel 7 Transfer Count (GPDMA7TC)    |       |

|            | Master DMA Channel 4–7 Status (MSTDMASTA)         |       |

|            | Master DMA Channel 4–7 Control (MSTDMACTL)        |       |

|            | Master Software DRQ(n) Request (MSTDMASWREQ)      |       |

|            | Master DMA Channel 4–7 Mask (MSTDMAMSK)           |       |

|            | Master DMA Channel 4–7 Mode (MSTDMAMODE)          |       |

|            | Master DMA Clear Byte Pointer (MSTDMACBP)         |       |

|            | Master DMA Controller Reset (MSTDMARST)           |       |

|            | Master DMA Controller Temporary (MSTDMATMP)       |       |

|            | Master DMA Mask Reset (MSTDMAMSKRST)              |       |

|            | Master DMA General Mask (MSTDMAGENMSK)            |       |

|            |                                                   |       |

| CHAPTER 12 | PROGRAMMABLE INTERRUPT CONTROLLER REGISTERS       | 12-1  |

|            | 12.1 Overview                                     |       |

|            | 12.2 Registers                                    | 12-1  |

|            | Interrupt Control (PICICR)                        |       |

|            | Master PIC Interrupt Mode (MPICMODE)              |       |

|            | Slave 1 PIC Interrupt Mode (SL1PICMODE)           |       |

|            | Slave 2 PIC Interrupt Mode (SL2PICMODE)           |       |

|            | Software Interrupt 16–1 Control (SWINT16_1)       |       |

|            | Software Interrupt 22–17/NMI Control (SWINT22_17) |       |

|            | Interrupt Pin Polarity (INTPINPOL)                |       |

|            | PCI Host Bridge Interrupt Mapping (PCIHOSTMAP)    |       |

|            | ECC Interrupt Mapping (ECCMAP)                    | 12-19 |

|            |                                                   |       |

| GP Timer 0 Interrupt Mapping (GPTMR0MAP)              |       |

|-------------------------------------------------------|-------|

| GP Timer 1 Interrupt Mapping (GPTMR1MAP)              |       |

| GP Timer 2 Interrupt Mapping (GPTMR2MAP)              |       |

| PIT 0 Interrupt Mapping (PIT0MAP)                     |       |

| PIT 1 Interrupt Mapping (PIT1MAP)                     |       |

| PIT 2 Interrupt Mapping (PIT2MAP)                     |       |

| UART 1 Interrupt Mapping (UART1MAP)                   |       |

| UART 2 Interrupt Mapping (UART2MAP)                   |       |

| PCI Interrupt A Mapping (PCIINTAMAP)                  |       |

| PCI Interrupt B Mapping (PCIINTBMAP)                  |       |

| PCI Interrupt C Mapping (PCIINTCMAP)                  |       |

| PCI Interrupt D Mapping (PCIINTDMAP)                  |       |

| DMA Buffer Chaining Interrupt Mapping (DMABCINTMAP)   |       |

| SSI Interrupt Mapping (SSIMAP)                        |       |

| Watchdog Timer Interrupt Mapping (WDTMAP)             |       |

| RTC Interrupt Mapping (RTCMAP)                        |       |

| Write-Protect Violation Interrupt Mapping (WPVMAP)    |       |

| AMDebug™ Technology RX/TX Interrupt Mapping (ICEMAP)  |       |

| Floating Point Error Interrupt Mapping (FERRMAP)      |       |

| GPIRQ0 Interrupt Mapping (GP0IMAP)                    |       |

| GPIRQ1 Interrupt Mapping (GP1IMAP)                    |       |

| GPIRQ2 Interrupt Mapping (GP2IMAP)                    |       |

| GPIRQ3 Interrupt Mapping (GP3IMAP)                    |       |

| GPIRQ4 Interrupt Mapping (GP4IMAP)                    |       |

| GPIRQ5 Interrupt Mapping (GP5IMAP)                    |       |

| GPIRQ6 Interrupt Mapping (GP6IMAP)                    |       |

| GPIRQ7 Interrupt Mapping (GP7IMAP)                    |       |

| GPIRQ8 Interrupt Mapping (GP8IMAP)                    |       |

| GPIRQ9 Interrupt Mapping (GP9IMAP)                    |       |

| GPIRQ10 Interrupt Mapping (GP10IMAP)                  |       |

| Master PIC Interrupt Request (MPICIR)                 |       |

| Master PIC Initialization Control Word 1 (MPICICW1)   |       |

| Master PIC Operation Control Word 2 (MPICOCW2)        |       |

| Master PIC Operation Control Word 3 (MPICOCW3)        | 12-30 |

| Master PIC Initialization Control Word 2 (MPICICW2)   |       |

| Master PIC Initialization Control Word 3 (MPICICW3)   | 12-33 |

| Master PIC Initialization Control Word 4 (MPICICW4)   | 12-35 |

| Master PIC Interrupt Mask (MPICINTMSK)                | 12-36 |

| Slave 2 PIC Interrupt Request (S2PICIR)               | 12-37 |

| Slave 2 PIC In-Service (S2PICISR)                     | 12-38 |

| Slave 2 PIC Initialization Control Word 1 (S2PICICW1) |       |

| Slave 2 PIC Operation Control Word 2 (S2PICOCW2)      |       |

| Slave 2 PIC Operation Control Word 3 (S2PICOCW3)      |       |

| Slave 2 PIC Initialization Control Word 2 (S2PICICW2) |       |

| Slave 2 PIC Initialization Control Word 3 (S2PICICW3) |       |

| Slave 2 PIC Interrupt Mask (S2PICINTMSK)              |       |

| Slave 1 PIC Interrupt Request (S1PICIR)               |       |

| Slave 1 PIC In-Service (S1PICISR)                     | 12-50 |

| Slave 1 PIC Initialization Control Word 1 (S1PICICW1) | 12-51 |

| Slave 1 PIC Operation Control Word 2 (S1PICOCW2)      | 12-53 |

| Slave 1 PIC Operation Control Word 3 (S1PICOCW3)      | 12-55 |

| Slave 1 PIC Initialization Control Word 2 (S1PICICW2) | 12-57 |

| Slave 1 PIC Initialization Control Word 3 (S1PICICW3) | 12-58 |

| Slave 1 PIC Initialization Control Word 4 (S1PICICW4) |       |

| Slave 1 PIC Interrupt Mask (S1PICINTMSK)              | 12-60 |

| Floating Point Error Interrupt Clear (FPUERRCLR)      | 12-61 |

| CHAPTER 13        | PROGRAMMABLE INTERVAL TIMER REGISTERS                                                       | 13-1  |

|-------------------|---------------------------------------------------------------------------------------------|-------|

|                   | 13.1 Overview                                                                               | 13-1  |

|                   | 13.2 Registers                                                                              | 13-1  |

|                   | PIT Channel 0 Count (PIT0CNT)                                                               | 13-2  |

|                   | PIT Channel 1 Count (PIT1CNT)                                                               |       |

|                   | PIT Channel 2 Count (PIT2CNT)                                                               |       |

|                   | PIT 0 Status (PIT0STA)                                                                      |       |

|                   | PIT 1 Status (PIT1STA)                                                                      |       |

|                   | PIT 2 Status (PIT2STA)                                                                      |       |

|                   | PIT Mode Control (PITMODECTL)                                                               |       |

|                   | PIT Counter Latch Command (PITCNTLAT)                                                       |       |

|                   | PIT Read-Back Command (PITRDBACK)                                                           |       |

|                   | System Control Port B (SYSCTLB)                                                             | 13-13 |

| <b>CHAPTER 14</b> | GENERAL-PURPOSE TIMER REGISTERS                                                             | 14-1  |

|                   | 14.1 Overview                                                                               |       |

|                   | 14.2 Registers                                                                              |       |

|                   | GP Timers Status (GPTMRSTA)                                                                 |       |

|                   | GP Timer 0 Mode/Control (GPTMR0CTL)                                                         |       |

|                   | GP Timer 0 Count (GPTMR0CNT)                                                                |       |

|                   | GP Timer 0 Maxcount Compare A (GPTMR0MAXCMPA)                                               |       |

|                   | GP Timer 0 Maxcount Compare B (GPTMR0MAXCMPB)                                               |       |

|                   | GP Timer 1 Mode/Control (GPTMR1CTL)                                                         |       |

|                   | GP Timer 1 Count (GPTMR1CNT)                                                                |       |

|                   | GP Timer 1 Maxcount Compare A (GPTMR1MAXCMPA) GP Timer 1 Maxcount Compare B (GPTMR1MAXCMPB) |       |

|                   | GP Timer 1 Maxcount Compare B (GPTMR TMAXCMPB)                                              |       |

|                   | GP Timer 2 Mode/Control (GP TMR2CT2)                                                        |       |

|                   | GP Timer 2 Maxcount Compare A (GPTMR2MAXCMPA)                                               | 14-18 |

|                   | · · · ·                                                                                     |       |

| CHAPTER 15        | SOFTWARE TIMER REGISTERS                                                                    | 15-1  |

|                   | 15.1 Overview                                                                               |       |

|                   | 15.2 Registers                                                                              |       |

|                   | Software Timer Millisecond Count (SWTMRMILLI)                                               |       |

|                   | Software Timer Microsecond Count (SWTMRMICRO)                                               |       |

|                   | Software Timer Configuration (SWTMRCFG)                                                     | 15-4  |

| CHAPTER 16        | WATCHDOG TIMER REGISTERS                                                                    | 16-1  |

|                   | 16.1 Overview                                                                               |       |

|                   | 16.2 Registers                                                                              | 16-1  |

|                   | Watchdog Timer Control (WDTMRCTL)                                                           |       |

|                   | Watchdog Timer Count Low (WDTMRCNTL)                                                        |       |

|                   | Watchdog Timer Count High (WDTMRCNTH)                                                       | 16-5  |

| <b>CHAPTER 17</b> | REAL-TIME CLOCK REGISTERS                       | 17-1  |

|-------------------|-------------------------------------------------|-------|

|                   | 17.1 Overview                                   | 17-1  |

|                   | 17.2 Registers                                  | 17-1  |

|                   | RTC/CMOS RAM Index (RTCIDX)                     |       |

|                   | RTC/CMOS RAM Data Port (RTCDATA)                |       |

|                   | RTC Current Second (RTCCURSEC)                  | 17-4  |

|                   | RTC Alarm Second (RTCALMSEC)                    | 17-5  |

|                   | RTC Current Minute (RTCCURMIN)                  |       |

|                   | RTC Alarm Minute (RTCALMMIN)                    |       |

|                   | RTC Current Hour (RTCCURHR)                     |       |

|                   | RTC Alarm Hour (RTCALMHR)                       | 17-9  |

|                   | RTC Current Day of the Week (RTCCURDOW)         |       |

|                   | RTC Current Day of the Month (RTCCURDOM)        |       |

|                   | RTC Current Month (RTCCURMON)                   |       |

|                   | RTC Current Year (RTCCURYR)                     |       |

|                   | RTC Control A (RTCCTLA)                         |       |

|                   | RTC Status C (RTCSTAC)                          |       |

|                   | RTC Status D (RTCSTAD)                          |       |

|                   | General-Purpose CMOS RAM (114 bytes) (RTCCMOS)  |       |

|                   |                                                 |       |

| CHAPTER 18        | UART SERIAL PORT REGISTERS                      | 18-1  |

|                   | 18.1 Overview                                   |       |

|                   | 18.2 Registers                                  |       |

|                   | UART 1 General Control (UART1CTL)               |       |

|                   | UART 2 General Control (UART2CTL)               |       |

|                   | UART 1 General Status (UART1STA)                |       |

|                   | UART 2 General Status (UART2STA)                |       |

|                   | UART 1 FIFO Control Shadow (UART1FCRSHAD)       |       |

|                   | UART 2 FIFO Control Shadow (UART2FCRSHAD)       |       |

|                   | UART 2 Transmit Holding (UART2THR)              |       |

|                   | UART 1 Transmit Holding (UART1THR)              |       |

|                   | UART 2 Receive Buffer (UART2RBR)                |       |

|                   | UART 1 Receive Buffer (UART1RBR)                |       |

|                   | UART 2 Baud Clock Divisor Latch LSB (UART2BCDL) |       |

|                   | UART 1 Baud Clock Divisor Latch LSB (UART1BCDL) |       |

|                   | UART 2 Baud Clock Divisor Latch MSB (UART2BCDH) |       |

|                   | UART 1 Baud Clock Divisor Latch MSB (UART1BCDH) |       |

|                   | UART 2 Interrupt Enable (UART2INTENB)           |       |

|                   | UART 1 Interrupt Enable (UART1INTENB)           |       |

|                   | UART 2 Interrupt ID (UART2INTID)                |       |

|                   | UART 1 Interrupt ID (UART1INTID)                |       |

|                   | UART 2 FIFO Control (UART2FCR)                  |       |

|                   | UART 1 FIFO Control (UART1FCR)                  |       |

|                   | UART 2 Line Control (UART2LCR)                  |       |

|                   | UART 1 Line Control (UART1LCR)                  |       |

|                   | UART 2 Modern Control (UART2MCR)                |       |

|                   | UART 1 Modem Control (UART1MCR)                 |       |

|                   | UART 2 Line Status (UART2LSR)                   |       |

|                   | UART 1 Line Status (UART1LSR)                   |       |

|                   | UART 2 Modern Status (UART2MSR)                 |       |

|                   | UART 1 Modem Status (UART1MSR)                  |       |

|                   | UART 2 Scratch Pad (UART2SCRATCH)               |       |

|                   | LIART 1 Scratch Pad (LIART1SCRATCH)             | 18-75 |

| CHAPTER 19 | SYNCHRONOUS SERIAL INTERFACE REGISTERS  19.1 Overview.  19.2 Registers  SSI Control (SSICTL)  SSI Transmit (SSIXMIT)  SSI Command (SSICMD)  SSI Status (SSISTA)  SSI Receive (SSIRCV) |             |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| CHAPTER 20 | PROGRAMMABLE INPUT/OUTPUT REGISTERS 20.1 Overview                                                                                                                                     | <b>20-1</b> |

|            | 20.1 Overview                                                                                                                                                                         |             |

|            | PIO15–PIO0 Pin Function Select (PIOPFS15_0)                                                                                                                                           |             |

|            | PIO31–PIO16 Pin Function Select (PIOPFS31_16)                                                                                                                                         |             |

|            | Chip Select Pin Function Select (CSPFS)                                                                                                                                               |             |

|            | Clock Select (CLKSEL)                                                                                                                                                                 |             |

|            | Drive Strength Control (DSCTL)                                                                                                                                                        | 20-10       |

|            | PIO15–PIO0 Direction (PIODIR15_0)                                                                                                                                                     |             |

|            | PIO31–PIO16 Direction (PIODIR31_16)                                                                                                                                                   |             |

|            | PIO15-PIO0 Data (PIODATA15_0)                                                                                                                                                         |             |

|            | PIO31–PIO16 Data (PIODATA31_16)                                                                                                                                                       |             |

|            | PIO15-PIO0 Set (PIOSET15_0)                                                                                                                                                           |             |

|            | PIO31–PIO16 Set (PIOSET31_16)                                                                                                                                                         |             |

|            | PIO15-PIO0 Clear (PIOCLR15_0)                                                                                                                                                         | 20-24       |

|            | PIO31-PIO16 Clear (PIOCLR31_16)                                                                                                                                                       | 20-26       |

| INDEX      |                                                                                                                                                                                       | Index-1     |

# **LIST OF FIGURES**

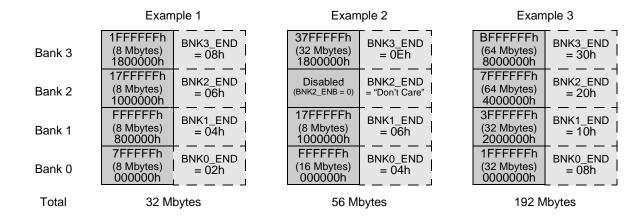

|             | Examples of Bank Ending Address Configuration                   |      |

|-------------|-----------------------------------------------------------------|------|

| •           | ECC Check Bit and Data Bit Positions                            |      |

| Figure 10-1 | GP Bus Signal Timing Adjustment                                 | 10-7 |

|             |                                                                 |      |

| LIST OF TA  | ABLES                                                           |      |

| Table 0-1   | Documentation Notation                                          | xvii |

| Table 1-1   | Memory-Mapped Configuration Region (MMCR) Registers (By Offset) | 1-2  |

| Table 1-2   | Direct-Mapped I/O Registers                                     | 1-7  |

| Table 1-3   | PCI Indexed Registers                                           | 1-11 |

| Table 1-4   | Real-Time Clock Indexed Registers                               | 1-11 |

| Table 2-1   | System Address Mapping MMCR Registers                           | 2-1  |

| Table 2-2   | System Address Mapping Direct-Mapped Register                   | 2-1  |

| Table 3-1   | Reset Generation MMCR Registers                                 |      |

| Table 3-2   | Reset Generation Direct-Mapped Registers                        |      |

| Table 3-3   | Microcontroller Reset Sources                                   |      |

| Table 4-1   | Am5 <sub>x</sub> 86® CPU MMCR Registers                         |      |

| Table 5-1   | System Arbiter MMCR Registers                                   |      |

| Table 6-1   | PCI Bus Host Bridge MMCR Registers                              |      |

| Table 6-2   | PCI Bus Host Bridge Direct-Mapped Registers                     |      |

| Table 6-3   | PCI Bus Host Bridge Indexed Registers                           |      |

| Table 7-1   | SDRAM Controller MMCR Registers                                 |      |

| Table 7-2   | Example ECC Check Codes and Associated Data                     |      |

| Table 8-1   | Write Buffer and Read Buffer MMCR Register                      |      |

| Table 9-1   | ROM Controller MMCR Registers                                   |      |

| Table 10-1  | GP Bus MMCR Registers                                           | 10-1 |

|             | GP Bus Echo Mode Minimum Timing                                 |      |

|             | GP-DMA MMCR Registers                                           |      |

|             | GP-DMA Direct-Mapped Registers                                  |      |

|             | Programmable Interrupt Controller MMCR Registers                |      |

|             | Programmable Interrupt Controller Direct-Mapped Registers       |      |

|             | Master PIC I/O Port 0020h Access Summary                        |      |

|             | Master PIC I/O Port 0020h Access Summary (Same as Table 12-3)   |      |

|             | Master PIC I/O Port 0020h Access Summary (Same as Table 12-3)   |      |

|             | Slave 2 PIC I/O Port 0024h Access Summary (Same as Table 12-6)  |      |

|             | Slave 2 PIC I/O Port 0024h Access Summary (Same as Table 12-6)  |      |

|             | Slave 1 PIC I/O Port 00A0h Access Summary                       |      |

|             | Slave 1 PIC I/O Port 00A0h Access Summary (Same as Table 12-9)  |      |

|             | Slave 1 PIC I/O Port 00A0h Access Summary (Same as Table 12-9)  |      |

|             | Programmable Interval Timer Direct-Mapped Registers             |      |

|             | PIT Counter Mode Settings                                       |      |

|             | General-Purpose Timer MMCR Registers                            |      |

|             | Software Timer MMCR Registers                                   |      |

|             | Watchdog Timer MMCR Registers                                   |      |

|             | Watchdog Timer Exponent Selections                              |      |

|             | Real-Time Clock Direct-Mapped Registers                         |      |

|             | Real-Time Clock Indexed Registers                               |      |

|             | UART MMCR Registers                                             |      |

|             | UART Direct-Mapped Registers                                    |      |

|             | Baud Rates, Divisors, and Clock Source                          |      |

|             | UART Interrupt Identification and Priority                      |      |

|             | UART Interrupt Programming Summary                              |      |

|             | SSI MMCR Registers                                              |      |

|             | SSI Clock Speed Selections                                      |      |

|             | Programmable I/O MMCR Registers                                 |      |

|             | PIO Register Programming Summary                                |      |

| Table 20-2  | PIO Register Programming Summary                                |      |

# INTRODUCTION

# ÉLAN™SC520 MICROCONTROLLER

The Élan™SC520 microcontroller is a full-featured microcontroller developed for the general embedded market. The ÉlanSC520 microcontroller combines a 32-bit, low-voltage Am5<sub>x</sub>86® CPU with a complete set of integrated peripherals suitable for both real-time and PC/AT-compatible embedded applications.

## **PURPOSE OF THIS MANUAL**

This manual includes in reference format the complete set of registers required to configure the ElanSC520 microcontroller and control its peripherals. This manual does not document the  $Am5_x86$  processor registers.

## **Intended Audience**

This reference manual is intended primarily for programmers who are developing code for the ÉlanSC520 microcontroller. Computer software and hardware architects and system engineers who are designing or are considering designing systems based on this microcontroller may also be interested in the information contained in this document. For more information on programming this microcontroller, see the *Élan™SC520 Microcontroller User's Manual*, order #22004.

#### Overview of this Manual

The manual is organized into the following chapters:

- Chapter 1 contains an overview of all the microcontroller's configuration registers.

- Chapter 2 describes the system address mapping registers.

- Chapter 3 describes the reset generation registers.

- Chapter 4 describes the Am5,86 CPU registers.

- Chapter 5 describes the **system arbitration registers**.

- Chapter 6 describes the **PCI host bridge registers**.

- Chapter 7 describes the **synchronous DRAM (SDRAM) controller registers**.

- Chapter 8 describes the write buffer and read buffer register.

- Chapter 9 describes the **ROM/Flash memory controller registers**.

- Chapter 10 describes the **general-purpose (GP) bus controller registers**.

- Chapter 11 describes the **GP bus DMA controller registers**.

- Chapter 12 describes the programmable interrupt controller (PIC) registers.

- Chapter 13 describes the programmable interval timer (PIT) registers.

- Chapter 14 describes the **general-purpose (GP) timer registers**.

- Chapter 15 describes the **software timer registers**.

- Chapter 16 describes the watchdog timer (WDT) registers.

- Chapter 17 describes the real-time clock (RTC) registers.

- Chapter 18 describes the **UART registers**.

- Chapter 19 describes the **synchronous serial interface (SSI) registers**.

- Chapter 20 describes the **programmable I/O (PIO) registers**.

- The Index lists all registers and bits alphabetically by name and mnemonic.

Each chapter describes the function's memory-mapped configuration region (MMCR) registers first, followed by direct-mapped and then indexed register descriptions, if any. Within each chapter, the registers of each type are listed in ascending hexadecimal order unless descriptions for identical registers (for example, direct-mapped UART registers) are combined.

## **RELATED DOCUMENTS**

The following documents contain additional information that will be useful in designing an embedded application based on the ÉlanSC520 microcontroller.

# **AMD Documentation**

In addition to this manual, the documentation set for the ÉlanSC520 microcontroller includes the following documents:

- Élan™SC520 Microcontroller User's Manual, order #22004, provides a functional description of the microcontroller for both hardware and software designers.

- Élan™SC520 Microcontroller Data Sheet, order #22003, includes complete pin lists, pin state tables, timing and thermal characteristics, and package dimensions for the ÉlanSC520 microcontroller.

Other information of interest:

- The Am486® Microprocessor Software User's Manual, order #18497, includes the complete instruction set for the integrated Am5<sub>x</sub>86 CPU.

- Am5x86® Microprocessor Family Data Sheet, order #19751

- Am486®DX/DX2 Microprocessor Hardware Reference Manual, order #17965

- E86<sup>™</sup> Family Products and Development Tools CD, order #21058, provides a single-source multimedia tool for customer evaluation of AMD products, as well as FusionE86 partner tools and technologies that support the E86 family. Technical documentation is included on the CD in PDF format.

To order literature, contact the nearest AMD sales office or call the literature center at one of the numbers listed on the back cover of this manual. In addition, all these documents are available in PDF form on the AMD web site. To access the AMD home page, go to **www.amd.com**. Then follow the Embedded Processor link for information about AMD's E86 family of microcontrollers.

Introduction

#### **Additional Information**

www.DataSheet4LL

The following non-AMD documents and sources provide additional information that may be of interest to ÉlanSC520 microcontroller users:

- *PCI Local Bus Specification,* Revision 2.2, December 18, 1998, PCI Special Interest Group, 800-433-5177 (US), 503-693-6360 (International), www.pcisig.com.

- IEEE Std 1149.1-1990 Standard Test Access Port and Boundary-Scan Architecture, (order #SH16626-NYF), Institute of Electrical and Electronic Engineers, Inc., 800-678-4333, www.ieee.org.

- PCI System Architecture, Mindshare, Inc., Reading, MA: Addison-Wesley, 1995, ISBN 0-201-40993-3.

- *ISA System Architecture*, Mindshare, Inc., Reading, MA: Addison-Wesley, 1995, ISBN 0-201-40996-8.

- 80486 System Architecture, Mindshare, Inc., Reading, MA: Addison-Wesley, 1995, ISBN 0-201-40994-1

- *The Indispensable PC Hardware Book*, Hans-Peter Messmer, Wokingham, England: Addison-Wesley, 1995, ISBN 0-201-87697-3.

# **DOCUMENTATION CONVENTIONS**

Table 0-1 lists the documentation conventions used throughout this manual.

## **Table 0-1 Documentation Notation**

| Notation              | Meaning                                                                                                                                                                                                                                                                                                                                  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset Default Values  |                                                                                                                                                                                                                                                                                                                                          |

| Default               | Value after a system reset                                                                                                                                                                                                                                                                                                               |

| 0                     | Low                                                                                                                                                                                                                                                                                                                                      |

| 1                     | Active or High                                                                                                                                                                                                                                                                                                                           |

| х                     | No value is guaranteed                                                                                                                                                                                                                                                                                                                   |

| ?                     | Determined by sources external to the ÉlanSC520 microcontroller                                                                                                                                                                                                                                                                          |

| Read/Write Attributes | •                                                                                                                                                                                                                                                                                                                                        |

| R                     | The bit field is read-only. A write to the register at this bit field has no effect. The contents may or may not be changed by hardware.                                                                                                                                                                                                 |

| W                     | The bit field is write-only. Reading this register at this bit field does not return a meaningful value and has no side effects.                                                                                                                                                                                                         |

| R/W                   | The bit field is read/write. Reading the register at this bit field always returns the last value written. Reads have no side effects.                                                                                                                                                                                                   |

| R/W!                  | The bit field is read/write with conditions. The "!" indicates that there are side effects to using this bit. For example, reading a bit or register might not always return the last value written. Note that both reads and writes can have side effects. If you see a "!", be sure to read the bit description and programming notes. |

| RSV                   | The bit field is reserved for internal test/debug or future expansion. This bit field should be written to 0 for normal system operation. This bit field always returns 0 when read.                                                                                                                                                     |

| RSV!                  | The bit field is reserved for compatibility purposes. For example, the bit field might be ignored during writes to maintain software compatibility. If you see a "!", be sure to read the bit description and programming notes.                                                                                                         |

| Reference Notation    | •                                                                                                                                                                                                                                                                                                                                        |

| MMCR offset 00h       | ÉlanSC520 microcontroller Memory-Mapped Configuration Region (MMCR) offset register 00h                                                                                                                                                                                                                                                  |

| PCI index 00h         | PCI indexed register 00h                                                                                                                                                                                                                                                                                                                 |

| Port 00h              | Direct-mapped I/O register 00h                                                                                                                                                                                                                                                                                                           |

| RTC index 00h         | RTC and configuration RAM indexed register 00h                                                                                                                                                                                                                                                                                           |

# Table 0-1 Documentation Notation (Continued)

| Notation              | Meaning                                                                                                                                                                                                            |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Naming            |                                                                                                                                                                                                                    |

| {}                    | Pin function during hardware reset                                                                                                                                                                                 |

| []                    | Alternative pin function selected by software configuration                                                                                                                                                        |

| ROMCS1                | An overbar indicates that the signal assumes the logic Low state when asserted.                                                                                                                                    |

| GPRESET               | The absence of an overbar indicates that the signal assumes the logic High state when asserted.                                                                                                                    |

| ads, hold             | A signal name in all lowercase indicates an internal signal.                                                                                                                                                       |

| ROMCS2-ROMCS1         | Two ROM chip select signals                                                                                                                                                                                        |

| ROMCSx                | Any of the two ROM chip select signals                                                                                                                                                                             |

| Numbers               |                                                                                                                                                                                                                    |

| b                     | Binary number                                                                                                                                                                                                      |

| d                     | Decimal number Decimal is the default radix                                                                                                                                                                        |

| h                     | Hexadecimal number                                                                                                                                                                                                 |

| x in register address | Any of several legal values; e.g., using 0xF8h for the UART Transmit Holding register is either 02F8h or 03F8h, depending on the UART                                                                              |

| [X-Y]                 | The bit field that consists of bits X through Y. Example: The SB_ADDR[23–16] bit field.                                                                                                                            |

| 33 MHz                | Refers to the system clock frequency being used. This can be either 33.000 MHz or 33.333 MHz. See the <i>Élan™SC520 Microcontroller User's Manual</i> , order #22004, for more information about clock generation. |

| General               |                                                                                                                                                                                                                    |

| field                 | Bit field in a register (one or more consecutive and related bits)                                                                                                                                                 |

| can                   | It is possible to perform an action if properly configured                                                                                                                                                         |

| will                  | A certain action is going to occur                                                                                                                                                                                 |

| Set the ENB bit.      | Write the ENB bit to 1.  Note: The bit referred to is either in the register being described, or the register is referred to explicitly in the surrounding text.                                                   |

| Clear the ENB bit.    | Change the ENB bit to 0. Usually a bit is cleared by writing a 0 to it; however, some bits are cleared by writing a 1.                                                                                             |

| Reset the ENB bit.    | Context-sensitive. Can refer either to resetting the bit to its default value or to clearing the bit.                                                                                                              |

# CONFIGURATION REGISTER OVERVIEW

The Élan™SC520 microcontroller has four different types of configuration registers:

- Memory-Mapped Configuration Region (MMCR) Registers—These are memory-mapped peripherals and configuration registers that are specific to the ÉlanSC520 microcontroller's control and status functions, such as the SDRAM and GP bus controllers. These registers are 8-bits, 16-bits, or 32-bits wide and reside in memory space.

- **Direct-Mapped Registers**—These include the Configuration Base Address (CBAR) register, the PCI Configuration Address and Data (PCICFGADR and PCICFGDATA) registers, and PC/AT-compatible peripherals. All direct-mapped I/O registers reside in fixed I/O space. The CBAR, PCICFGADR, and PCICFGDATA registers are 32 bits wide. All other direct-mapped peripheral configuration registers are 8 bits wide.

- PCI Host Bridge Indexed Configuration Registers—These registers are located in the PCI bus configuration space, which is defined in the PCI Local Bus Specification, Revision 2.2, to be accessed through two 32-bit I/O locations at 0CF8h (index) and 0CFCh (data).

- RTC Indexed Registers—These registers are located in the PC/AT-compatible realtime clock (RTC) configuration space, which is accessed using I/O ports 0070h (index) and 0071h (data).

Register descriptions are organized within this manual by function, e.g., GP bus, SDRAM, or UART. Each function's chapter describes the MMCR registers first, followed by direct-mapped, and then indexed register descriptions, if any. In each chapter, registers of each type are listed in ascending hexadecimal order unless descriptions for identical registers (for example, direct-mapped UART registers) are combined.

The remainder of this chapter presents an overview of the registers by type.

# 1.1 MEMORY-MAPPED CONFIGURATION REGION (MMCR) REGISTERS

The ÉlanSC520 microcontroller's memory-mapped configuration region (MMCR) contains all internal peripheral control and configuration registers that are not defined as direct-mapped I/O, PCI indexed, or RTC indexed registers.

After reset, the MMCR registers are located in the 4-Kbyte region in memory address space from FFFEF000–FFFEFFFh. The MMCR registers can be aliased to any 4-Kbyte region in the lower 1-Gbyte address space (00000000h–1FFFFFFh) via the I/O-mapped CBAR register (see page 2-9). The MMCR is available at its original location in high memory even if it is aliased via the CBAR register. See the memory and I/O space chapter in the  $\acute{E}lan^{TM}SC520$  Microcontroller User's Manual, order #22004, for more detail.

Table 1-1 on page 1-2 lists all the MMCR registers included in the ÉlanSC520 microcontroller.

Table 1-1 Memory-Mapped Configuration Region (MMCR) Registers (By Offset)

| Register Name                         | Mnemonic    | MMCR Offset | Page Number |

|---------------------------------------|-------------|-------------|-------------|

| CPU                                   |             | 00–02h      |             |

| ÉlanSC520 Microcontroller Revision ID | REVID       | 00h         | page 4-2    |

| Am5 <sub>x</sub> 86® CPU Control      | CPUCTL      | 02h         | page 4-3    |

| SDRAM Controller                      |             | 10–28h      |             |

| SDRAM Control                         | DRCCTL      | 10h         | page 7-4    |

| SDRAM Timing Control                  | DRCTMCTL    | 12h         | page 7-4    |

| SDRAM Bank Configuration              | DRCCFG      | 14h         | page 7-5    |

| SDRAM Bank 0–3 Ending Address         | DRCBENDADR  | 18h         | page 7-7    |

| ECC Control                           | ECCCTL      | 20h         | page 7-9    |

| ECC Status                            | ECCSTA      | 21h         | page 7-10   |

| ECC Check Bit Position                | ECCCKBPOS   | 22h         | page 7-11   |

| ECC Check Code Test                   | ECCCKTEST   | 23h         | page 7-12   |

| ECC Single-Bit Error Address          | ECCSBADD    | 24h         | page 7-14   |

| ECC Multi-Bit Error Address           | ECCMBADD    | 28h         | page 7-15   |

| SDRAM Buffer                          |             | 40h         |             |

| SDRAM Buffer Control                  | DBCTL       | 40h         | page 8-2    |

| ROM/Flash Controller                  |             | 50–56h      |             |

| BOOTCS Control                        | BOOTCSCTL   | 50h         | page 9-2    |

| ROMCS1 Control                        | ROMCS1CTL   | 54h         | page 9-4    |

| ROMCS2 Control                        | ROMCS2CTL   | 56h         | page 9-6    |

| PCI Bus Host Bridge                   |             | 60-6Ch      |             |

| Host Bridge Control                   | HBCTL       | 60h         | page 6-3    |

| Host Bridge Target Interrupt Control  | HBTGTIRQCTL | 62h         | page 6-5    |

| Host Bridge Target Interrupt Status   | HBTGTIRQSTA | 64h         | page 6-7    |

| Host Bridge Master Interrupt Control  | HBMSTIRQCTL | 66h         | page 6-9    |

| Host Bridge Master Interrupt Status   | HBMSTIRQSTA | 68h         | page 6-12   |

| Host Bridge Master Interrupt Address  | MSTINTADD   | 6Ch         | page 6-14   |

| System Arbitration                    |             | 70–74h      |             |

| System Arbiter Control                | SYSARBCTL   | 70h         | page 5-2    |

| PCI Bus Arbiter Status                | PCIARBSTA   | 71h         | page 5-3    |

| System Arbiter Master Enable          | SYSARBMENB  | 72h         | page 5-4    |

| Arbiter Priority Control              | ARBPRICTL   | 74h         | page 5-6    |

www.DataSheet4U.com\_

Table 1-1 Memory-Mapped Configuration Region (MMCR) Registers (By Offset) (Continued)

| Register Name                  | Mnemonic  | MMCR Offset | Page Number |

|--------------------------------|-----------|-------------|-------------|

| System Address Mapping         | -         | 80-C4h      |             |

| Address Decode Control         | ADDDECCTL | 80h         | page 2-2    |

| Write-Protect Violation Status | WPVSTA    | 82h         | page 2-4    |

| Programmable Address Region 0  | PAR0      | 88h         | page 2-5    |

| Programmable Address Region 1  | PAR1      | 8Ch         | page 2-5    |

| Programmable Address Region 2  | PAR2      | 90h         | page 2-5    |

| Programmable Address Region 3  | PAR3      | 94h         | page 2-5    |

| Programmable Address Region 4  | PAR4      | 98h         | page 2-5    |

| Programmable Address Region 5  | PAR5      | 9Ch         | page 2-5    |

| Programmable Address Region 6  | PAR6      | A0h         | page 2-5    |

| Programmable Address Region 7  | PAR7      | A4h         | page 2-5    |

| Programmable Address Region 8  | PAR8      | A8h         | page 2-5    |

| Programmable Address Region 9  | PAR9      | ACh         | page 2-5    |

| Programmable Address Region 10 | PAR10     | B0h         | page 2-5    |

| Programmable Address Region 11 | PAR11     | B4h         | page 2-5    |

| Programmable Address Region 12 | PAR12     | B8h         | page 2-5    |

| Programmable Address Region 13 | PAR13     | BCh         | page 2-5    |

| Programmable Address Region 14 | PAR14     | C0h         | page 2-5    |