Spec. No.: C554QP Issued Date: 2010.11.17 Revised Date:

Page No. : 1/12

### 3A Low Dropout LDO

## EM5103

### **General Description**

EM5103 is a 3A low dropout linear regulator designed for low dropout and high current applications. This device works with dual supplies, a control input for the control circuitry and a power input as low as 1.2V for providing current to output.

It features 3A output current and ultra-low-drop output voltage as well as full protection functions. Vout can be as low as 0.8V.

#### **Features**

- ●VIN Range 1.2V to 5.5V

- Vout is Adjustable (0.8V Min)

- •Excellent Line Regulation

- •Excellent Load Regulation

- •3A Guaranteed Output Current\*

\*Check thermal design information.

- •300mV @ 3A Dropout Voltage

- •OTP and OCP Functions

- •Very Low On-Resistance

- •Enable & Power good Signal

### **Applications**

- •Notebook & Netbook

- •Graphic Cards & MB

- •Low Voltage Logic Supplies

- •Chipset Supplies

- •Server System

- •SMPS Post Regulators

### **Ordering Information**

| Part Number | Package                        |

|-------------|--------------------------------|

| EM5103QP    | PSOP-8                         |

|             | (Pb-free lead plating package) |

| EM5103NA    | DFN3×3-10L                     |

|             | (Pb-free lead plating package) |

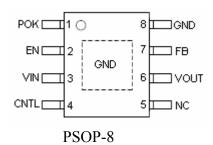

### **Pin Configuration**

Spec. No. : C554QP Issued Date : 2010.11.17 Revised Date :

Revised Date : Page No. : 2/12

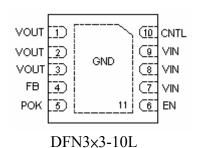

## **Typical Application Circuit**

PSOP-8 DFN3×3-10L

## **Pin Assignment**

| D' M                                                                                        | ]      | Pin No.    |                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|---------------------------------------------------------------------------------------------|--------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Name                                                                                    | PSOP-8 | DFN3×3-10L | Pin Function                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| POK                                                                                         | 1      | 5          | <b>Power OK Indication.</b> POK is an open-drain output. An external pull high resistor connected to this pin is required.                                                                                                                                                                                                                       |  |  |  |  |

| EN                                                                                          | 2      | 6          | <b>Enable Input.</b> Pulling the pin below 0.4V turns the regulator off.                                                                                                                                                                                                                                                                         |  |  |  |  |

| VIN                                                                                         | 3      | 7,8,9      | Input Voltage. This is the drain input to the power device that supplies current to the output pin. VIN cannot be forced higher than VCNTL.                                                                                                                                                                                                      |  |  |  |  |

| CNTL                                                                                        | 4      | 10         | <b>Supply Input for Control Circuit.</b> CNTL provides supply voltage to the control circuitry and driver for the pass transistor. The driving capability of output current is proportioned to the Vcntl. For the device to regulate, the voltage on this pin must be at least 2.0V greater than the output voltage, and no less than Vcntl_min. |  |  |  |  |

| NC                                                                                          | 5      | -          | No Connection inside chip.                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| VOUT                                                                                        | 6      | 1,2,3      | Output Voltage. Vout is power output pin. An internal pull low resistance exists when the device is disabled. Minimum 22µF low ESR ceramic holding capacitor is required at this pin for stabilizing Vout voltage.                                                                                                                               |  |  |  |  |

| FB 7 4 resistor divider from the output to 0 as $V_{OUT} = (1 + R_1/R_2) \times 0.8V (V)$ . |        | 4          | <b>Feedback Voltage.</b> FB is the inverting input to the error amplifier. A resistor divider from the output to GND is used to set the regulation voltage as $V_{OUT} = (1 + R_1/R_2) \times 0.8V$ (V). This pin has high impedance and should be kept from noisy source to guarantee stable operation.                                         |  |  |  |  |

| GND                                                                                         | 8      | 11         | Ground.                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

Spec. No. : C554QP Issued Date : 2010.11.17

Revised Date : Page No. : 3/12

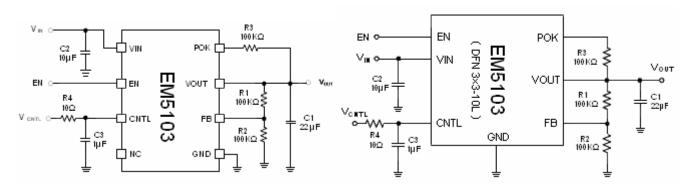

## **Function Block Diagram**

### Absolute Maximum Ratings (Note 1)

| •V <sub>IN</sub> 0.3V to +6.0V                                         | <i>V</i>      |

|------------------------------------------------------------------------|---------------|

| •VCNTL (Note 1)                                                        | Į             |

| •Other Pins0.3V to (VCNTL+0.3V                                         | <b>'</b> )    |

| • Package Thermal Resistance, θJA, PSOP-8 (Note 2) 75°C/W              | V             |

| DFN3×3-10L 60°C/V                                                      | V             |

| • Package Thermal Resistance, θ <sub>JC</sub> , PSOP-8 (Note 2) 15°C/W | V             |

| • Power Dissipation, PD @ TA = 25°C, PSOP-8 (Note 3) 1.9W              | V             |

| DFN3×3-10L 1.67V                                                       | V             |

| • Junction Temperature 150°C                                           | $\mathcal{I}$ |

| •Lead Temperature (Soldering, 10 sec.) 260°C                           | _             |

| •Storage Temperature65°C to 150°C                                      | C             |

| •ESD susceptibility (Note4)                                            |               |

| HBM (Human Body Mode) 2KV<br>MM (Machine Mode) 200V                    |               |

| 171171 (171acmine 1710de)                                              | •             |

### **Recommended Operating Conditions (Note5)**

| Supply Input Voltage, VIN | 1.0V to VCNTL         |

|---------------------------|-----------------------|

| Control Voltage, VCNTL    | 3.0V to 5.5V          |

| Junction Temperature      | <b>−40°C to 125°C</b> |

| Ambient Temperature       | 40°C to 85°C          |

Spec. No.: C554QP Issued Date: 2010.11.17

Revised Date: Page No.: 4/12

## **Electrical Characteristics** @ $V_{CNTL}$ =5V, $T_A$ =25 $^{\circ}C$ , unless otherwise specified

| Parameter                        | Symbol          | Test Conditions                                                                                                                                      | Min      | Тур  | Max     | Units         |

|----------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|---------|---------------|

| Supply Input Section             | Syllibol        | Test Collations                                                                                                                                      | IVIIII   | Тур  | IVIAX   | Ullits        |

| Control Input Voltage            | VCNTL           | Vout= Vref                                                                                                                                           | 3.0      |      | 5.5     | V             |

| POR Threshold                    | VCNTLRTH        | VOUI— VREF                                                                                                                                           | 3.0      | 2.7  | 3.3     | $\frac{v}{V}$ |

| POR Hysteresis                   | VCNTLHYS        |                                                                                                                                                      | _        | 0.2  | _       | V             |

| Power Input Voltage              | VENTERYS        | Vout=Vref                                                                                                                                            | 1.0      | -    | VCNTL   | V             |

| Control Input Current in         | ICNTL_SD        | VIN=VCNTL=5V, IOUT=0A, VEN=0V                                                                                                                        | 1.0      | 10   | 30      | μA            |

| Quiescent Current                | IQ              | VIN=VCNTL=VEN=5V, IOUT=0A, VOUT=VREF                                                                                                                 | -        | 0.9  | 1.5     | mA            |

| Feedback                         |                 | I                                                                                                                                                    |          |      |         |               |

| Reference Voltage                | Vref            | VIN=VCNTL=VEN=5V, IOUT=0A,<br>VOUT=VREF                                                                                                              | 0.788    | 0.8  | 0.812   | V             |

| Feedback Input Current           | Ifb             | 7 007 7 100                                                                                                                                          | -        | 5    | -       | nA            |

| VIN Line Regulation              | VREF(LINE)      | 1.2V <vin<5v, iout="0A," vcntl="VEN=5V," vout="VREF&lt;/td"><td>-</td><td>0.01</td><td>0.1</td><td>%/V</td></vin<5v,>                                | -        | 0.01 | 0.1     | %/V           |

| Load Regulation (Note 6)         | VREF(LOAD)      | 10mA <iout<3a, vin="Vcntl=Ven=5V," vout="Vref&lt;/td"><td>-</td><td>0.8</td><td>1.5</td><td>%/A</td></iout<3a,>                                      | -        | 0.8  | 1.5     | %/A           |

| Load Regulation over Temperature | Vref(total)     | 10mA <iout<3a, -40°="" by="" c="" c<tj<125°="" design<="" td="" vin="VcntL=Ven=5V," vout="Vref,"><td>-</td><td>-</td><td>3</td><td>%</td></iout<3a,> | -        | -    | 3       | %             |

|                                  | **              | IOUT=2A, VCNTL=VEN=5V, VOUT=VREF                                                                                                                     | -        | 200  | 240     | mV            |

| Dropout Voltage (Note 7)         | VDROP           | IOUT=3A, VCNTL=VEN=5V, VOUT=VREF                                                                                                                     | -        | 300  | 360     | mV            |

| Output Voltage                   | Vout            |                                                                                                                                                      | 0.8      |      | Vcntl-2 | V             |

| Vour Pull Low Resistance         |                 | VIN=VCNTL=5V, VEN=0V                                                                                                                                 | _        | 70   | _       | Ω             |

| Enable                           |                 |                                                                                                                                                      | <u> </u> |      |         |               |

| Enable High Level                | V <sub>EN</sub> |                                                                                                                                                      | 1.4      | -    | -       | V             |

| Disable Low Level                | V <sub>SD</sub> |                                                                                                                                                      | -        | -    | 0.4     | V             |

| Enable Source Current            | Ien             | V <sub>CNTL</sub> =5V, V <sub>EN</sub> =0V                                                                                                           | -        | 7    | 18      | μΑ            |

| Enable Input Impedance           | Zen             |                                                                                                                                                      | -        | 700  | -       | ΚΩ            |

| Output Voltage Ramp Up<br>Time   |                 |                                                                                                                                                      | 1.5      | 2.5  | 4.5     | ms            |

| PWROK                            |                 |                                                                                                                                                      |          |      |         |               |

| FB Power OK Threshold            | VPOKTH          | VIN=VCNTL=VEN=5V, IOUT=0A,<br>VOUT=VREF                                                                                                              | -        | 90   | -       | %             |

| Power OK Hysteresis              | VPOKHYS         | VIN=VCNTL=VEN=5V, IOUT=0A,<br>VOUT=VREF                                                                                                              | -        | 8    | -       | %             |

| POK Delay Time                   |                 | From Vour>90% to POK rising                                                                                                                          | 0.5      | 1.0  | 2.0     | ms            |

| Over Current Protection          |                 |                                                                                                                                                      | I        |      | 1       |               |

| OCP Threshold Level              | Іоср            | VIN=VCNTL=VEN=5V, VOUT=VREF                                                                                                                          | 3.2      | 4.0  | -       | А             |

| Output Short Circuit Current     | Isc             | VIN=VCNTL=VEN=5V, VOUT=0V                                                                                                                            | 1.5      | 2.5  | -       | А             |

Spec. No.: C554QP Issued Date: 2010.11.17

Revised Date : Page No. : 5/12

| Parameter                      | Symbol | Test Conditions                         | Min | Тур | Max | Units |

|--------------------------------|--------|-----------------------------------------|-----|-----|-----|-------|

| Thermal Protection             |        |                                         |     |     |     |       |

| Thermal Shutdown Temperature   | Tsd    | VIN=VCNTL=VEN=5V, IOUT=0A,<br>VOUT=VREF | -   | 160 | -   | °C    |

| Thermal Shutdown<br>Hysteresis | Tsdhys | VIN=VCNTL=VEN=5V, IOUT=0A,<br>VOUT=VREF | -   | 30  | -   | °C    |

- Note 1. Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

- Note 2.  $\theta_{JA}$  is measured in the natural convection at TA=25°C on a 4-layers high effective thermal conductivity test board with minimum copper area of JEDEC 51-7 thermal measurement standard. The case point of  $\theta_{JC}$  is on the expose pad for PSOP-8 package.

- Note 3. 0JA is 52°C/W for PSOP-8 packages on JEDEC 51-7 (4 layers,2S2P) thermal test board with 50mm 2 copper area.

- Note 4. Devices are ESD sensitive. Handling precaution is recommended.

- Note 5. The device is not guaranteed to function outside its operating conditions.

- Note 6. Load regulation is measured by a current pulse with 50Hz frequency and 10% duty cycle.

- Note 7. The dropout voltage is defined as (VIN-VOUT), which is measured when VOUT equal to (VOUT,(NORMAL)-100mV).

Spec. No. : C554QP Issued Date : 2010.11.17 Revised Date :

Page No.: 6/12

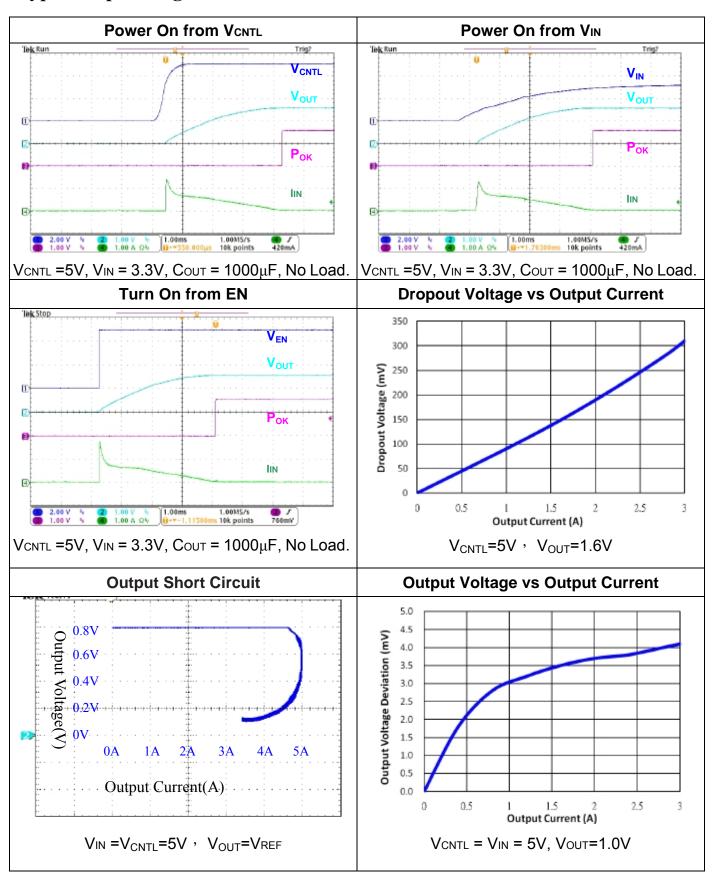

### **Typical Operating Characteristics**

Spec. No.: C554QP Issued Date: 2010.11.17

Revised Date : Page No. : 7/12

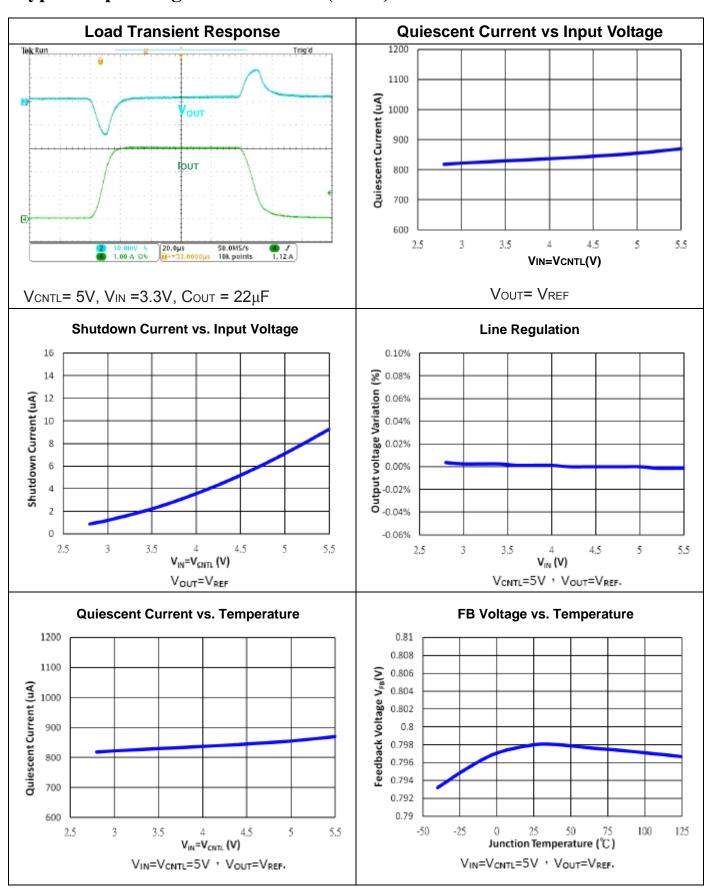

## **Typical Operating Characteristics(Cont.)**

Spec. No.: C554QP Issued Date: 2010.11.17 Revised Date:

Page No.: 8/12

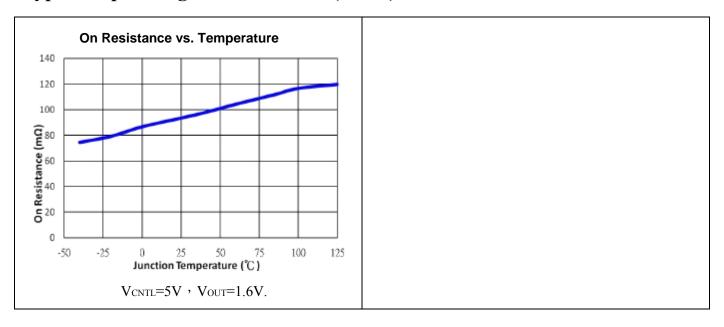

### **Typical Operating Characteristics(Cont.)**

### **Functional Description**

#### **Enable Function**

EM5103 is enabled if the voltage of the EN pin is greater than 1.4V. If the voltage of the EN pin is less than 0.4V, the IC will be disabled. The quiescent current can be decreased to be less than  $10\mu$ A typically.

#### **POR – Power ON Reset**

To let EM5103 start to operation, CNTL voltage must be higher than its POR voltage even when EN voltage is pulled higher than enable high voltage. Typical POR voltage is 2.7V.

#### **VOUT Voltage Adjustment**

The Vout voltage of EM5103 can be adjusted by external voltage divider. Refer to typical application circuit, Vout voltage is calculated by the following equation:

$$V_{OUT} = (1 + \frac{R_1}{R_2}) \times 0.8V$$

Spec. No. : C554QP Issued Date : 2010.11.17 Revised Date :

Page No.: 9/12

#### **Over Current Limit Function**

EM5103 features over current limiting function as well as output short circuit current fold back function. Typically, before the thermal protection is triggered, EM5103 can limit its output current to 4.0A. When output voltage is decreased, the limiting current level also decreases. When Vout is short to GND, or Vout voltage is zero, the output current level is limited to 2.5A, typically.

### **Input and Output Capacitor Selection**

For CNTL pin, a  $1\mu F$  ceramic capacitor is enough for bypassing the supply of CNTL to GND. For VIN pin,  $10\mu F$  or larger ceramic capacitor is required to provide bypass path in transient current demand. Vout pin is also recommended to have  $22\mu F$  or larger ceramic capacitor to be stable and reduce the Vout voltage dip when fast loading transient is happened. A feed-forward capacitor can be placed between Vout and FB pin to speed up the transient response, optionally.

#### **Power Dissipation**

The max power depends on some conditions, including thermal impedance, PCB layout, airflow, and so on. The max power dissipation can be calculated by the formula as below:

$P_{D(max)} = (T_{J(max)} - T_A) / \theta_{JA}$

$T_{J(max)}$  is the max junction temperature;  $\theta_{JA}$  is the thermal impedance from junction to ambient. The thermal impedance  $\theta_{JA}$  of exposed SOP-8 is package design and PCB design dependent.

The thermal impedance can be reduced by increasing the copper area under the exposed pad of the SOP-8 package. So, to let the copper area as large as possible is helpful for the thermal performance of the exposed SOP-8 package.

For recommended specification of EM5103, the max junction temperature is 125 degree C. The  $\theta_{JA}$  of exposed SOP-8 is 75°C/W on the standard JEDEC 51-7(4 layers, 2S2P, copper 2 oz) thermal test board. The max power dissipation (at 25°C ambient, on the min exposed pad layout) can be calculated as below:

$P_{D \text{ (max at 25°C)}} = (125^{\circ}\text{C} - 25^{\circ}\text{C}) / (75^{\circ}\text{C/W}) = 1.33\text{W}$

Spec. No.: C554QP Issued Date: 2010.11.17

Revised Date : Page No. : 10/12

Recommended wave soldering condition

| Product         | Peak Temperature | Soldering Time  |  |  |

|-----------------|------------------|-----------------|--|--|

| Pb-free devices | 260 +0/-5 °C     | 5 +1/-1 seconds |  |  |

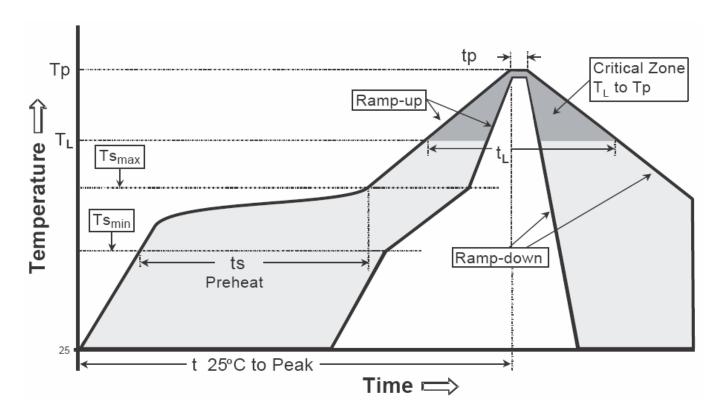

### Recommended temperature profile for IR reflow

| Profile feature                                | Sn-Pb eutectic Assembly | Pb-free Assembly |

|------------------------------------------------|-------------------------|------------------|

| Average ramp-up rate<br>(Tsmax to Tp)          | 3°C/second max.         | 3°C/second max.  |

| Preheat                                        |                         |                  |

| -Temperature Min(Ts min)                       | 100°C                   | 150°C            |

| -Temperature Max(Ts max)                       | 150°C                   | 200°C            |

| -Time(ts min to ts max)                        | 60-120 seconds          | 60-180 seconds   |

| Time maintained above:                         |                         |                  |

| −Temperature (T∟)                              | 183°C                   | 217°C            |

| – Time (t∟)                                    | 60-150 seconds          | 60-150 seconds   |

| Peak Temperature(T <sub>P</sub> )              | 240 +0/-5 °C            | 260 +0/-5 °C     |

| Time within 5°C of actual peak temperature(tp) | 10-30 seconds           | 20-40 seconds    |

| Ramp down rate                                 | 6°C/second max.         | 6°C/second max.  |

| Time 25 °C to peak temperature                 | 6 minutes max.          | 8 minutes max.   |

Note: All temperatures refer to topside of the package, measured on the package body surface.

Spec. No. : C554QP Issued Date : 2010.11.17 Revised Date :

Page No.: 11/12

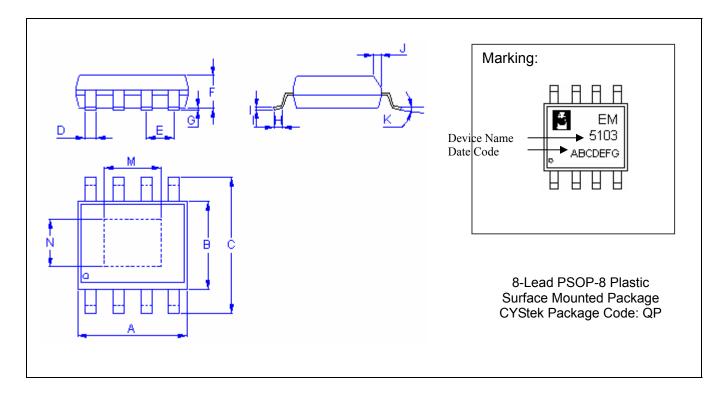

#### **PSOP-8 Dimension**

\*:Typical

| · · · · · · · · · · · · · · · · · · · |        |        |             |      |       |        |        |             |      |

|---------------------------------------|--------|--------|-------------|------|-------|--------|--------|-------------|------|

| DIM                                   | Inches |        | Millimeters |      | DIM   | Inches |        | Millimeters |      |

|                                       | Min.   | Max.   | Min.        | Max. | ווועו | Min.   | Max.   | Min.        | Max. |

| Α                                     | 0.1850 | 0.2008 | 4.70        | 5.10 | Н     | 0.0157 | 0.0327 | 0.40        | 0.83 |

| В                                     | 0.1457 | 0.1614 | 3.70        | 4.10 |       | 0.0075 | 0.0102 | 0.19        | 0.26 |

| С                                     | 0.2283 | 0.2441 | 5.80        | 6.20 | J     | 0.0098 | 0.0197 | 0.25        | 0.50 |

| D                                     | 0.0130 | 0.0200 | 0.33        | 0.51 | K     | 0°     | 8°     | <b>0</b> °  | 8°   |

| Е                                     | 0.05*  |        | 1.27 *      |      | М     | 0.0764 | 0.0980 | 1.94        | 2.49 |

| F                                     | 0.0472 | 0.0638 | 1.20        | 1.62 | N     | 0.0764 | 0.0980 | 1.94        | 2.49 |

| G                                     | 0.0032 | 0.0110 | 0.08        | 0.28 |       |        |        |             |      |

Notes: 1. Controlling dimension: millimeters.

2. Maximum lead thickness includes lead finish thickness, and minimum lead thickness is the minimum thickness of base material.

3.If there is any question with packing specification or packing method, please contact your local CYStek sales office.

#### Material:

• Mold Compound : Epoxy resin family, flammability solid burning class:UL94V-0

Spec. No.: C554QP Issued Date: 2010.11.17 Revised Date:

Revised Date : Page No. : 12/12

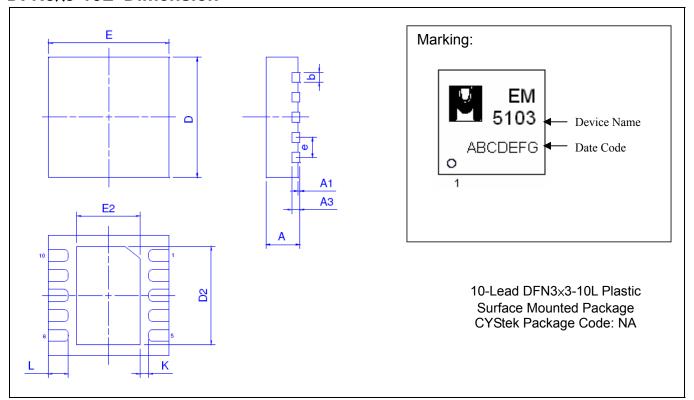

#### DFN3×3-10L Dimension

\*:Typical

| DIM | Inches |       | Millimeters |       | DIM | Inches |       | Millimeters |      |

|-----|--------|-------|-------------|-------|-----|--------|-------|-------------|------|

|     | Min.   | Max.  | Min.        | Max.  | DIM | Min.   | Max.  | Min.        | Max. |

| Α   | 0.028  | 0.031 | 0.70        | 0.80  | D2  | 0.087  | 0.106 | 2.20        | 2.70 |

| A1  | 0.000  | 0.020 | 0.00        | 0.50  | E2  | 0.055  | 0.069 | 1.40        | 1.75 |

| A3  | 0.008* |       | 0.2         | 0.20* |     | 0.0    | 20*   | 0.5         | 50*  |

| b   | 0.007  | 0.012 | 0.18        | 0.30  | L   | 0.012  | 0.020 | 0.30        | 0.50 |

| D   | 0.1    | 18*   | 3.0*        |       | K   | 0.008  | -     | 0.20        | -    |

| Е   | 0.118* |       | 3.0*        |       |     |        |       |             |      |

Notes: 1.Controlling dimension: millimeters.

2.Maximum lead thickness includes lead finish thickness, and minimum lead thickness is the minimum thickness of base material. 3.If there is any question with packing specification or packing method, please contact your local CYStek sales office.

#### Material

• Mold Compound : Epoxy resin family, flammability solid burning class:UL94V-0

#### Important Notice:

- All rights are reserved. Reproduction in whole or in part is prohibited without the prior written approval of CYStek.

- CYStek reserves the right to make changes to its products without notice.

- CYStek semiconductor products are not warranted to be suitable for use in Life-Support Applications, or systems.

- CYStek assumes no liability for any consequence of customer product design, infringement of patents, or application assistance.