# 1.3MHz 1.2A, Synchronous Step-Down Regulator

## **General Description**

EML3412 is designed with high efficiency step down DC/DC converter for portable devices applications. It features with extreme low quiescent current with no load which is the best fit for extending battery life during the standby mode. The device operates from 2.5V to 5.5V input voltage and up to 1.2A output current capability. High 1.3MHz internal frequency makes small surface mount inductors and capacitors possible and reduces overall PCB board space. Further, build-in synchronous switch makes external Schottky diode is no longer needed and efficiency is improved. EML3412 is designed base on pulse width modulation (PWM) for low output voltage ripple and fixed frequency noise, low dropout mode provides 100% duty cycle operation. Low reference voltage is designed for achieving regulated output down to 0.6V.

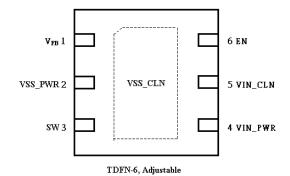

The device is available in an adjustable version. The EML3412 is available in TDFN-6 package.

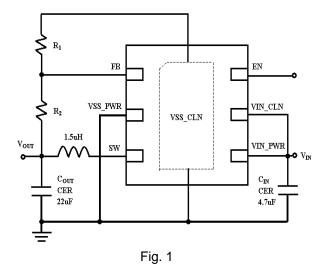

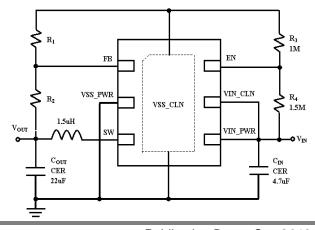

## Typical Application (adjustable)

#### **Features**

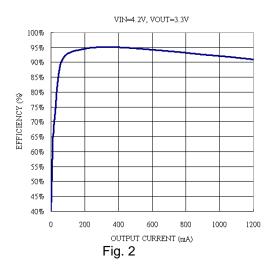

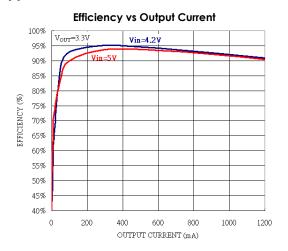

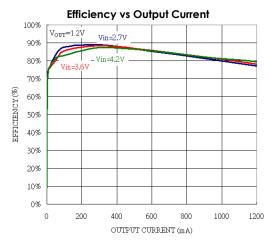

- Achieve 95% efficiency

- Input Voltage: 2.5V to 5.5V

- Output Current up to 1.2A

- Reference voltage 0.6V

- Quiescent Current 240µ A with No Switching

- Internal switching frequency 1.3MHz

- No Schottky Diode needed

- Low Dropout Operation: 100% Duty Cycle

- Shutdown current < 1µ A

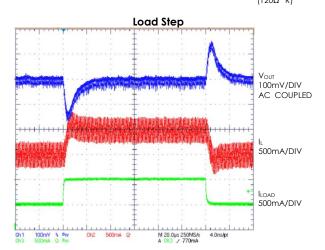

- Excellent Line and Load Transient Response

- Over-current and Over-temperature Protection

#### **Applications**

- Blue-Tooth devices

- Cellular and Smart Phones

- Personal multi-media Player (PMP)

- Wireless networking

- Digital Still Cameras

- Portable applications

#### Order, Mark & Packing Information

| Package | Vout               | Product ID        | Marking                                    | Packing              |

|---------|--------------------|-------------------|--------------------------------------------|----------------------|

| TDFN-6  | 00<br>(Adjustable) | EML3412-00FF06NRR | 6 5 4  ESMT  EML3412  Tracking Code  1 2 3 | 5K units Tape & Reel |

## Package configuration

#### EML3412-00FF06NRR

00 Adjustable

FF06 TDFN-6 Package

NRR RoHS & Halogen free

Rating: -40 to 85°C

Package in Tape & Reel

## Pin Functions

| Pin #                                               | Pin Name | Function                                                                                                                                                                         |

|-----------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 V <sub>FB</sub> (Adjustable) Vout (Fixed voltage) |          | Feedback Pin. Receives the feedback voltage from an external resistive divider across the output.                                                                                |

|                                                     |          | Output Voltage Pin. An internal resistive divider divides the output voltage down for comparison to the internal reference voltage.                                              |

| 2                                                   | VSS_PWR  | Power Ground Pin.                                                                                                                                                                |

| 3                                                   | SW       | Switch Pin. Must be connected to Inductor. This pin connects to the drains of the internal main and synchronous power MOSFET switches.                                           |

| 4 VIN_PWR                                           |          | Power Input Pin. Must be closely decoupled to GND pin with a 4.7µF or greater ceramic capacitor.                                                                                 |

| 5 VIN_CLN                                           |          | Analog Input Pin. Must be closely decoupled to GND pin with a 4.7µF or greater ceramic capacitor.                                                                                |

| 6 EN                                                |          | Enable Pin. Minimum 1.2V to enable the device. Maximum 0.4V to shut down the device. Do not leave this pin floating and enable the chip after Vin is in the input voltage range. |

| Exposed pad                                         | VSS_CLN  | Analog Ground Pin.                                                                                                                                                               |

## **Absolute Maximum Ratings**

Devices are subjected to failure if they stay above absolute maximum ratings.

| Input Voltage                            | Operating Temperature Range                |

|------------------------------------------|--------------------------------------------|

| EN, $V_{FB}$ Voltages 0.3V to $V_{IN}$   | Junction Temperature (Notes 1, 3) 125°C    |

| SW Voltage 0.3V to $(V_{IN} + 0.3V)$     | Storage Temperature Range 65°C to 150°C    |

| PMOS Switch Source Current (DC) 2A       | Lead Temperature (Soldering, 10 sec) 240°C |

| NMOS Switch Sink Current (DC) 2A         | ESD Susceptibility HBM 2KV                 |

| Peak Switch Sink and Source Current 3.5A | MM 200V                                    |

#### Thermal data

| Thermal resistance | Parameter                 | Value  |

|--------------------|---------------------------|--------|

| θ JA               | Junction-ambient (Note.4) | 55°C/W |

| θ JC               | Junction-case (Note.5)    | 10°C/W |

## **Electrical Characteristics**

The ● denotes specifications which apply over the full operating temperature range, otherwise specifications are T<sub>A</sub> = 25°C.  $V_{IN}$  = 5V unless otherwise specified.

| Symbol             | Parameter                         | Conditions                                          |   | Min   | Тур  | Max   | Units |

|--------------------|-----------------------------------|-----------------------------------------------------|---|-------|------|-------|-------|

| I <sub>VFB</sub>   | Feedback Current                  |                                                     |   |       |      | ±100  | nA    |

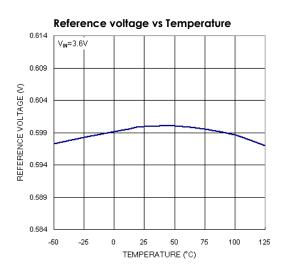

| .,                 | Regulated Feedback Voltage        | T <sub>A</sub> = 25°C                               |   | 0.588 | 0.6  | 0.612 |       |

| $V_{FB}$           |                                   | -40°C ≤ T <sub>A</sub> ≤ 85°C                       | • | 0.585 | 0.6  | 0.615 | V     |

| V <sub>OUT</sub> % | Output Voltage Accuracy           |                                                     | • | -3    |      | 3     | %     |

| $\Delta$ $V_{FB}$  | Reference Voltage Line Regulation | V <sub>IN</sub> = 2.5V to 5.5V                      | • |       |      | 0.4   | %/V   |

| $\Delta$ $V_{OVL}$ | Output Over-voltage Lockout       | $\Delta V_{OVL} = V_{OVL} - V_{FB}$                 |   | 20    | 50   | 80    | mV    |

| Δ V <sub>OUT</sub> | Output Voltage Line Regulation    | V <sub>IN</sub> = 2.5V to 5.5V                      | • |       |      | 0.4   | %/V   |

| I <sub>PK</sub>    | Peak Inductor Current             | $V_{IN} = 3V$ , $V_{FB} = 0.5V$ or $V_{OUT} = 90\%$ |   |       | 2.4  |       | Α     |

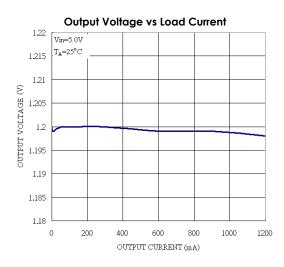

| $V_{LOADREG}$      | Output Voltage Load Regulation    | lout=10mA to 1.2A                                   |   |       | 0.2  |       | %/A   |

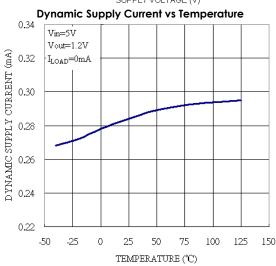

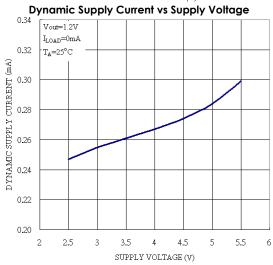

|                    | Quiescent Current (Note 2)        | $V_{FB} = 0.5V \text{ or } V_{OUT} = 90\%$          |   |       | 240  | 340   | μΑ    |

| Is                 | Shutdown                          | $V_{EN} = 0V$ , $V_{IN} = 4.2V$                     |   |       | 0.1  | 1     | μΑ    |

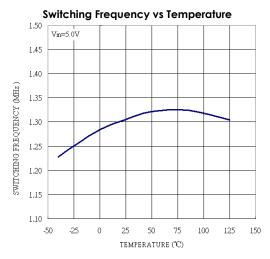

| fosc               | Oscillator Frequency              | V <sub>FB</sub> = 0.6V or V <sub>OUT</sub> = 100%   | • | 1.04  | 1.30 | 1.56  | MHz   |

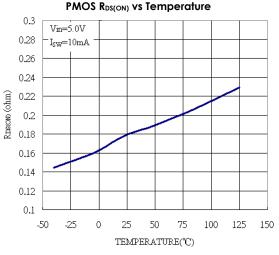

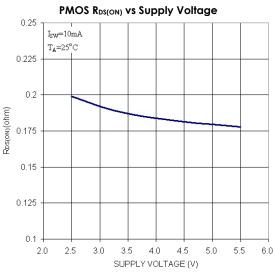

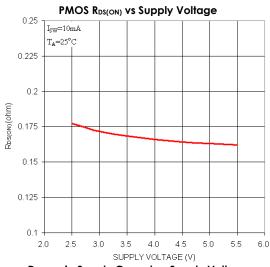

| R <sub>PFET</sub>  | R DS(ON) of PMOS                  | I <sub>sw</sub> = 750mA                             |   |       | 0.18 |       | Ω     |

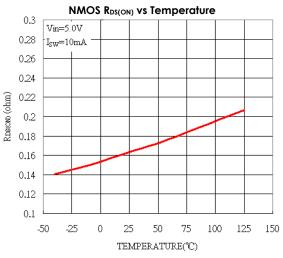

| R <sub>NFET</sub>  | R DS(ON) OF NMOS                  | $I_{SW} = -750$ mA                                  |   |       | 0.16 |       | Ω     |

| I <sub>LSW</sub>   | SW Leakage                        | $V_{EN} = 0V$ , $V_{SW} = 0V$ or 5V, $V_{IN} = 5V$  |   |       |      | ±1    | μА    |

|                    | Enable Threshold                  |                                                     | • | 1.2   |      |       | V     |

| V <sub>EN</sub>    | Shutdown Threshold                |                                                     | • |       |      | 0.4   | V     |

| I <sub>EN</sub>    | EN Leakage Current                |                                                     | • |       |      | ±1    | μА    |

**Note 1:**  $T_A$  is a function of the ambient temperature  $T_A$  and power dissipation  $P_D$  (  $T_A = T_A + (P_D)(55^{\circ}C/W)$  )

Note 2: Dynamic quiescent current is higher due to the gate charge being delivered at the switching frequency.

Note 3: This IC is build-in over-temperature protection to avoid damage from overload conditions.

Note 4:  $\theta$  JA is measured in the natural convection at TA=25°C on a highly effective thermal conductivity test board (4 layers, 2S2P) according to the JEDEC 51-5 thermal measurement standard.

**Note 5:**  $\theta$  <sub>JC</sub> represents the heat resistance between the chip and the package top case.

Publication Date: Oct. 2013 Revision: 2.5 3/15

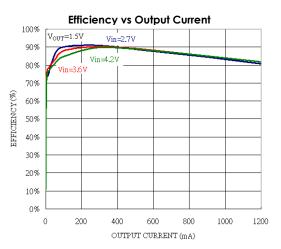

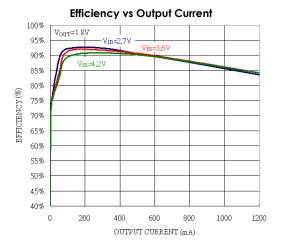

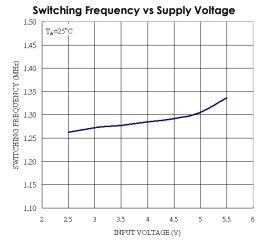

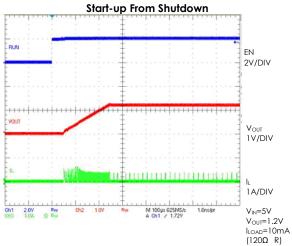

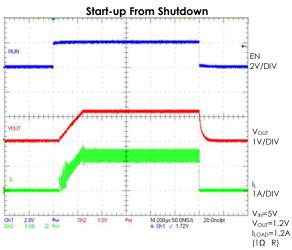

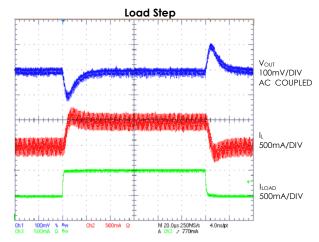

## **Typical Performance Characteristics**

$V_{\text{IN}}\!\!=\!5.0\text{V},\,V_{\text{OUT}}\!\!=\!2.5\text{V},\,I_{\text{LOAD}}\!\!=\!\!500\text{mA}$  to 1A

$V_{\text{IN}}\!\!=\!3.3V,\,V_{\text{OUT}}\!\!=\!1.5V,\,I_{\text{LOAD}}\!\!=\!500\text{mA}$  to 1 A

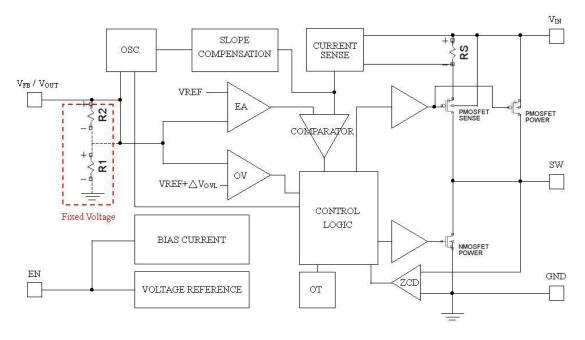

# **Functional Block Diagram**

## **Applications**

#### **Inductor Selection**

Basically, inductor ripple current and core saturation current are two factors considered to decide the Inductor value.

$$\Delta I_{L} = \frac{1}{f \cdot L} V_{OUT} \left( 1 - \frac{V_{OUT}}{V_{IN}} \right)$$

Eq. 1

The Eq. 1 shows the inductor ripple current is a function of frequency, inductance, Vin and Vout. It is recommended to set ripple current to 40% of max. load current. A low ESR inductor is preferred.

#### C<sub>IN</sub> and C<sub>OUT</sub> Selection

A low ESR input capacitor can prevent large voltage transients at  $V_{\text{IN}}$ . The RMS current of input capacitor is required larger than  $I_{\text{RMS}}$  calculated by:

$$I_{\text{RMS}} \stackrel{\cong}{=} I_{\text{OMAX}} \frac{\sqrt{V_{\text{OUT}} (V_{\text{IN}} - V_{\text{OUT}})}}{V_{\text{IN}}} \qquad \text{Eq. 2}$$

ESR is an important parameter to select  $C_{\text{OUT}}$ . The output ripple  $V_{\text{OUT}}$  is determined by:

$$\Delta V_{OUT} \cong \Delta I_{L} \left( ESR + \frac{1}{8 \cdot f \cdot C_{OUT}} \right)$$

Eq. 3

Higher values, lower cost ceramic capacitors are now available in smaller sizes. These ceramic capacitors have high ripple currents, high voltage ratings and low ESR that make them ideal for switching regulator applications. Optimize very low output ripple and small circuit size is doable from Cout selection since Cout does not affect the internal control loop stability. It is recommended to use the X5R or X7R which have the best temperature and voltage characteristics of all the ceramics for a given value and size.

#### **Output Voltage**

In the adjustable version, the output voltage can be determined by:

$$V_{OUT} = 0.6 V \left( 1 + \frac{R_2}{R_1} \right)$$

Eq. 4

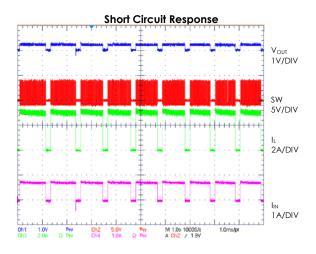

#### **Short Circuit Behavior**

EML3412 has over-current and over-temperature protection. Over-current protection cycle by cycle limits P-driver FET current to prevent inductor current from losing control. Over-temperature protection function turns off driver FETs when junction temperature is high and recovers to normal operation after it is cool enough. When EML3412 is used to transfer Vin=5V to Vout=1.2V, shorting Vout to ground makes over-current and over- temperature protection active. The waveform is shown as the following diagram.

#### **Thermal Considerations**

Although thermal shutdown is build-in in EML3412 that protect the device from thermal damage, the total power dissipation that EML3412 can sustain should be base on the package thermal capability. The formula to ensure the safe operation is shown in Note 1.

To avoid the EML3412 from exceeding the maximum junction temperature, the user will need to do some thermal analysis.

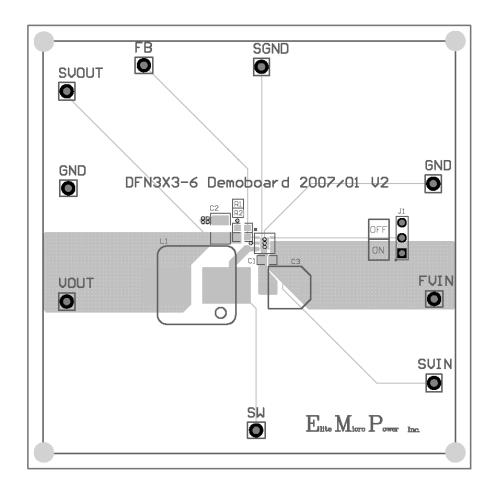

#### **Guidelines for PCB Layout**

To ensure proper operation of the EML3412, please note the following PCB layout guidelines:

- 1. The GND trace, the SW trace and the  $V_{\text{IN}}$  trace should be kept short, direct and wide.

- 2.  $V_{FB}$  pin must be connected directly to the feedback resistors. Resistive divider  $R_1/R_2$  must be connected and parallel to the output capacitor  $C_{OUT}$ .

- 3. The Input capacitor  $C_{\text{IN}}$  must be connected to pin  $V_{\text{IN}}$  as closely as possible.

- 4. Keep SW node away from the sensitive  $V_{\text{FB}}$  node since this node is with high frequency and voltage swing.

- 5. Keep the (-) plates of C<sub>IN</sub> and C<sub>OUT</sub> as close as possible.

- 6. Connect all analog grounds to a common node and connect the common node to power ground through an independent path.

#### **Self-Enable Application**

A self-enable function could be used when EML3412 is connected as the following diagram:

Publication Date: Oct. 2013 Revision: 2.5 8/15

The resistor ratio R3:R4=1:1.5 is recommended.

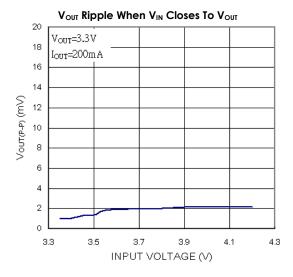

#### Output Voltage Ripple When $V_{\text{IN}}$ Closes To $V_{\text{OUT}}$

EML3412 goes into LDO mode when input voltage closes to output voltage. The transition from PWM mode to LDO mode is smooth. Bottom diagram shows the relationship of output voltage ripple versus input voltage when output voltage is 3.3V and EML3412 provides 200mA load current.

Assume the EML3412 is used in a single lithium-ion battery-powered application. The  $V_{\text{IN}}$  range will be about 2.7V to 4.2V. Output voltage is 1.8V.

With this information we can calculate L using equation:

$$L = \frac{1}{f \cdot \Delta I_{L}} V_{OUT} \left( 1 - \frac{V_{OUT}}{V_{IN}} \right)$$

Substituting  $V_{\text{OUT}}$  = 1.8V,  $V_{\text{IN}}$  = 4.2V,  $\Delta I_{\text{L}}$  = 480mA and f = 1.3MHz in eq. 1 gives:

$$L = \frac{1.8V}{1.3MHz \cdot 480mA} \left(1 - \frac{1.8V}{4.2V}\right) = 1.65uH$$

A 1.5 $\mu$ H inductor could be chose with this application. A greater inductor with less equivalent series resistance makes best efficiency.  $C_{\rm IN}$  will require an RMS current rating of at least  $l_{\rm LOAD(MAX)}/2$  and low ESR. In most cases, a ceramic capacitor will satisfy this requirement.

**Design Example**

## **Recommended Components**

| Ī | Supplier  | Inductance (uH) | I <sub>sat</sub> (A) | $DCR_{max}$ (m $\Omega$ ) | Dimensions (mm) | Part Number    |

|---|-----------|-----------------|----------------------|---------------------------|-----------------|----------------|

|   | Coilcraft | 1.5             | 14                   | 13                        | 12.3 x 12.3 x 6 | MSS1260-152NLB |

| Supplier    | Capacitance (uF) | Package | Part Number       |

|-------------|------------------|---------|-------------------|

| YAGEO       | 4.7              | 0805    | CC0805KKX5R6BB475 |

| TAIYO YUDEN | 22               | 1812    | EMK432BJ226KM-T   |

Publication Date: Oct. 2013 Revision: 2.5 9/15

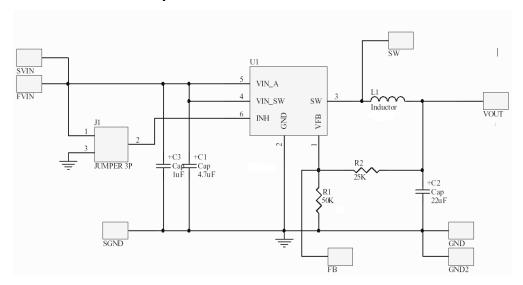

## **Application (Continued)**

## Typical schematic for PCB layout

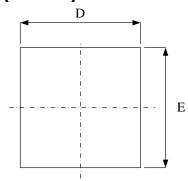

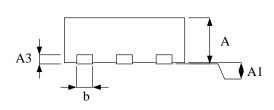

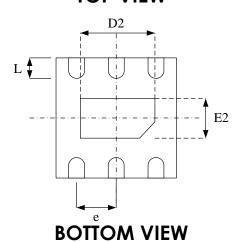

# Package Outline Drawing TDFN-6L (3x3 mm)

## **TOP VIEW**

**SIDE VIEW**

| C1 1   | Dimension in mm |      |  |

|--------|-----------------|------|--|

| Symbol | Min             | Max  |  |

| А      | 0.70            | 0.85 |  |

| A1     | 0.00            | 0.05 |  |

| A3     | 0.18            | 0.25 |  |

| ь      | 0.25            | 0.45 |  |

| D      | 2.95            | 3.05 |  |

| Е      | 2.95            | 3.05 |  |

| е      | 0.95 BSC        |      |  |

| L      | 0.20            | 0.50 |  |

Exposed pad

|    | Dimension in mm |      |  |

|----|-----------------|------|--|

|    | Min             | Max  |  |

| D2 | 2.20            | 2.60 |  |

| E2 | 1.40            | 1.75 |  |

## Old Order, Marking & Packing Information

| Package | Vout               | Product ID        | Marking                          | Packing              |

|---------|--------------------|-------------------|----------------------------------|----------------------|

| TDFN-6  | 00<br>(Adjustable) | EML3412-00FF06NRR | 6 5 4  EMP EML3412 Tracking Code | 5K units Tape & Reel |

|         |                    |                   | PIN1 DOT 1 2 3                   |                      |

## **Revision History**

| Revision | Date       | Description                                                                                        |

|----------|------------|----------------------------------------------------------------------------------------------------|

| 2.0      | 2009.06.05 | EMP transferred from version 1.2                                                                   |

| 2.1      | 2010.06.02 | To revise circuitry                                                                                |

| 2.2      | 2010.09.30 | Package dimension update                                                                           |

| 2.3      | 2011.01.28 | Revise electrical characteristics(VEN)                                                             |

| 2.4      | 2013.02.18 | Added the note4 and note5 in the electrical characteristics     Update the TDFN-6L package outline |

| 2.5      | 2013.10.24 | Modify marking                                                                                     |

## Important Notice

All rights reserved.

No part of this document may be reproduced or duplicated in any form or by any means without the prior permission of ESMT.

The contents contained in this document are believed to be accurate at the time of publication. ESMT assumes no responsibility for any error in this document, and reserves the right to change the products or specification in this document without notice.

The information contained herein is presented only as a guide or examples for the application of our products. No responsibility is assumed by ESMT for any infringement of patents, copyrights, or other intellectual property rights of third parties which may result from its use. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of ESMT or others.

Any semiconductor devices may have inherently a certain rate of failure. To minimize risks associated with customer's application, adequate design and operating safeguards against injury, damage, or loss from such failure, should be provided by the customer when making application designs.

ESMT's products are not authorized for use in critical applications such as, but not limited to, life support devices or system, where failure or abnormal operation may directly affect human lives or cause physical injury or property damage. If products described here are to be used for such kinds of application, purchaser must do its own quality assurance testing appropriate to such applications.

Publication Date: Oct. 2013 Revision: 2.5 15/15