# DVI/HDMI Compliant Splitter with HDCP EP9122

User Guide V0.4

Revised: May. 02, 2006

Original Release Date: Sep. 09, 2005

**Explore**

Explore reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Explore does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Explore products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Explore product could create a situation where personal injury or death may occur. Should Buyer purchase or use Explore products for any such unintended or unauthorized application, Buyer shall indemnify and hold Explore and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Explore was negligent regarding the design or manufacture of the part.

# **Revision History**

| Version<br>Number | Revision<br>Date | Author     | Description of Changes                       |

|-------------------|------------------|------------|----------------------------------------------|

| 0.0               | Sep/09/2005      | Jerry Chen | Initial Version                              |

| 0.1               | Oct/18/2005      | Ether Lai  | Change Pin Sequence; Add Package Description |

| 0.2               | Jan/14/2006      | Ether Lai  | Change Package Type                          |

| 0.3               | Feb/25/2006      | Ether Lai  | Review for 1st Engineering Lot               |

| 0.4               | May/02/2006      | Haowen Lu  | Add power consumption information            |

#### **Section 1 Introduction**

#### 1.1 Overview

The EP9122 is an DVI/HDMI splitter with integrated HDCP decryption/encryption engines which is compliant with HDMI Rev 1.1 and HDCP Rev 1.1 specifications. The EP9122 receives DVI/HDMI inputs, process HDCP decryption and encryption and transmits the data to 2 DVI/HDMI ports. The chip uses an external EE to store the encrypted HDCP receiver/transmitter keys.

#### 1.2 Features

- DVI Specification 1.0 Compliant

- HDMI Specification 1.1 Compliant

- Integrated HDCP decryption/encryption engines which are compliant with HDCP Rev 1.1 specification

- Encrypted HDCP keys store in external serial EE

- Wide Frequency Range: 25MHz 165MHz

- Supports 1 DVI/HDMI input port and 2 DVI/HDMI output ports

- Supports conversion of HDMI signaling to DVI signaling

- Supports video muting for transmitter ports

- Cascadable to make more than 2 output ports

- Single 3.3V CMOS Design

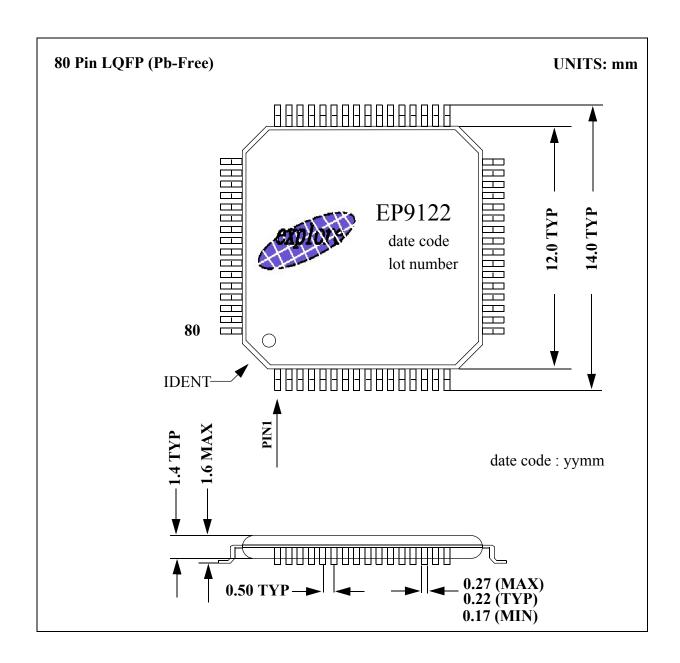

- 80-Pin LQFP (Pb-Free)

## **Section 2 Overview**

## 2.1 Block Diagram

SDA3 SCL3 **IIC Slave** Registers EXT\_RSTb & EXT\_SWING Logics DVI/HDMI SDA1 **HDCP** Keys **IIC Slave** Receiver SCL1 SDA2 **IIC Master** SCL2 DVI/HDMI DVI/HDMI **HDCP** Keys **HDCP Keys** Transmitter Transmitter TX00+/-TX10+/-TX20+/-TXC0+/-

Figure 2-1 Block Diagram

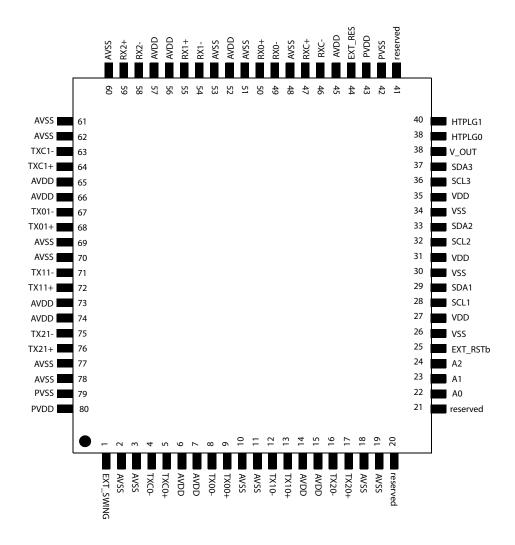

## 2.2 Pin Diagram

Figure 2-2 Pin Diagram

## 2.3 Pin Description

Unless otherwise stated, unused input pins must be tied to ground, and unused output pins left open.

**Table 2-1 IIC Pins**

| NAME       | IN /<br>OUT | DESCRIPTION                                                               |

|------------|-------------|---------------------------------------------------------------------------|

| SCL1       | IN          | IIC SCL signal for receiver port DDC                                      |

| SDA1       | Ю           | IIC SDA signal for receiver port DDC (open drain)                         |

| SCL2       | OUT         | IIC SCL signal for EE interface (open drain)                              |

| SDA2       | Ю           | IIC SDA signal for EE interface (open drain)                              |

| SCL3       | IN          | IIC SCL signal for internal registers access                              |

| SDA3       | Ю           | IIC SDA signal for internal registers access (open drain)                 |

| A2, A1, A0 | IN          | Determine the lowest 3-bit of the IIC addrress for IIC Port 3 (SCL3/SDA3) |

Table 2-2 Misc. Pins

| NAME     | IN /<br>OUT | DESCRIPTION                                                                                                                        |

|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------|

| EXT_RSTb | IN          | External Reset (Active LOW). A HIGH level indicates normal operation and a LOW level causes all the logic on the chip to be reset. |

| V_OUT    | OUT         | Polarity corrected vertical sync pulse (active high) derived from receiver input                                                   |

| reserved | IN          | Must be tied LOW for normal operation.                                                                                             |

**Table 2-3 Receiver Pins**

| NAME                                         | IN /<br>OUT | DESCRIPTION                                      |

|----------------------------------------------|-------------|--------------------------------------------------|

| RX0-<br>RX0+<br>RX1-<br>RX1+<br>RX2-<br>RX2+ | Analog      | Differential Data Input Pairs for receiver port  |

| RXC-<br>RXC+                                 |             | Differential Clock Input Pairs for receiver port |

| EXT_RES                                      | Analog      | DVI/HDMI External Termination Resistor           |

**Table 2-4 Transmitter Pins**

| NAME                                               | IN /<br>OUT | DESCRIPTION                                                                                                                                                           |  |  |  |

|----------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| TX00-<br>TX00+<br>TX10-<br>TX10+<br>TX20-<br>TX20+ | Analog      | Differential Data Output Pairs for transmitter port 0                                                                                                                 |  |  |  |

| TXC0-<br>TXC0+                                     |             | Differential Clock Output Pairs for transmitter port 0                                                                                                                |  |  |  |

| HTPLG0                                             | IN          | Hot Plug Input This pin is used to monitor the "HOT PLUG" signal for tansmitter port 0. Note: This input is only 3.3V tolerant and has no internal debouncer circuit. |  |  |  |

| TX01-<br>TX01+<br>TX11-<br>TX11+<br>TX21-<br>TX21+ | Analog      | Differential Data Output Pairs for transmitter port 1                                                                                                                 |  |  |  |

| TXC1-<br>TXC1+                                     |             | Differential Clock Output Pairs for transmitter port 1                                                                                                                |  |  |  |

| HTPLG1                                             | IN          | Hot Plug Input This pin is used to monitor the "HOT PLUG" signal for tansmitter port 1. Note: This input is only 3.3V tolerant and has no internal debouncer circuit. |  |  |  |

| EXT_SWING                                          | Analog      | Voltage Swing Adjust. A resistor should tie this pin to AVCC. This resistance determines the amplitude of the voltage swing. $560\Omega$ is recommended.              |  |  |  |

**Table 2-5 Power and Ground Pins**

| NAME | IN /<br>OUT | DESCRIPTION                |

|------|-------------|----------------------------|

| VDD  | PWR         | Digital Power, 3.3V        |

| VSS  | GND         | Digital Ground             |

| AVDD | PWR         | Analog Power, 3.3V         |

| AVSS | GND         | Analog Ground              |

| PVDD | PWR         | Analog Power for PLL, 3.3V |

| PVSS | GND         | Analog Ground for PLL      |

### 2.4 Electrical Characteristics

#### **Absolute Maximum Conditions**

| Symbol           | Parameter                                | Min  | Тур | Max                   | Units |

|------------------|------------------------------------------|------|-----|-----------------------|-------|

| Vcc              | Supply Voltage                           | -0.3 |     | 4.0                   | V     |

| V <sub>I</sub>   | Input Voltage                            | -0.3 |     | V <sub>cc</sub> + 0.3 | V     |

| V <sub>O</sub>   | Output Voltage                           | -0.3 |     | V <sub>cc</sub> + 0.3 | V     |

| T <sub>A</sub>   | Ambient Temperature (with power applied) | -25  |     | 105                   | °C    |

| T <sub>STG</sub> | Storage Temperature                      | -40  |     | 125                   | °C    |

| P <sub>PD</sub>  | Package Power Dissipation                |      |     | 1                     | W     |

<sup>1</sup> Permanent device damage may occur if absolute maximum conditions are exceeded.

#### **Normal Operating Conditions**

| Symbol           | Parameter                                | Min  | Тур | Max | Units             |

|------------------|------------------------------------------|------|-----|-----|-------------------|

| Vcc              | Supply Voltage                           | 3.0  | 3.3 | 3.6 | V                 |

| V <sub>CCN</sub> | Supply Voltage Noise <sup>1</sup>        | -0.3 |     | 100 | mV <sub>p-p</sub> |

| T <sub>A</sub>   | Ambient Temperature (with power applied) | 0    | 25  | 70  | °C                |

<sup>1</sup> Guaranteed by design.

#### DC Digital I/O Specifications (under normal operating conditions unless otherwise specified)

| Symbol          | Parameter                                             | Conditions     | Min | Тур | Max  | Units |

|-----------------|-------------------------------------------------------|----------------|-----|-----|------|-------|

| V <sub>IH</sub> | High-level Input Voltage                              |                | 2.0 |     |      | ٧     |

| V <sub>IL</sub> | Low-level Input Voltage                               |                |     |     | 0.8  | ٧     |

| V <sub>OH</sub> | High-level Output Voltage                             |                | 2.4 |     |      | ٧     |

| V <sub>OL</sub> | Low-level Output Voltage                              |                |     |     | 0.4  | ٧     |

| I <sub>OL</sub> | Output Leakage Current                                | High Impedance | -10 |     | 10   | uA    |

| V <sub>ID</sub> | Differential Input Voltage, Single<br>Ended Amplitude |                | 150 |     | 1000 | mV    |

<sup>2</sup> Functional operation should be restricted to the conditions described under Normal Operating Conditions.

#### User Guide — EP9122\_UG V0.4

|                 |                  | 720p, 60Hz<br>Typical Case<br>Pattern <sup>1</sup>  | 195 | 255 | mA |

|-----------------|------------------|-----------------------------------------------------|-----|-----|----|

|                 |                  | 720p, 60Hz<br>Worst Case<br>Pattern <sup>2</sup>    | 205 | 270 | mA |

|                 | , Supply Current | 1080p, 60Hz<br>Typical Case<br>Pattern <sup>1</sup> | 270 | 360 | mA |

| I <sub>CC</sub> | (25°C Ambient)   | 1080p, 60Hz<br>Worst Case<br>Pattern <sup>2</sup>   | 300 | 400 | mA |

|                 |                  | UXGA, 60Hz<br>Typical Case<br>Pattern <sup>1</sup>  | 285 | 380 | mA |

|                 |                  | UXGA, 60Hz<br>Worst Case<br>Pattern <sup>2</sup>    | 310 | 415 | mA |

<sup>1</sup> Quantum Data 882 VTG -- pattern master.

<sup>2</sup> Quantum Data 882 VTG -- pattern check\_11.

## **Section 3 Detail Functional Descriptions**

#### 3.1 General

The chip provides an IIC (SCL3/SDA3) serial bus interface to communicate with the host. The IIC address for this slave IIC interface is "0111\_A2\_A1\_A1\_x" (where x=1 for read and x=0 for write). A2, A1 and A0 are programmable by pins

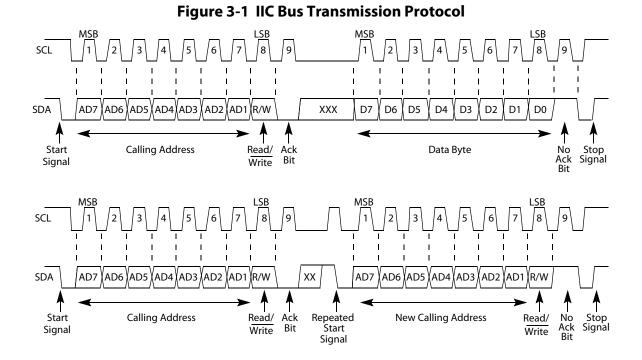

#### 3.2 IIC Interface

The IIC bus interface uses a Serial Data line (SDA at pin SDA3) and a Serial Clock Line (SCL at pin SCL3) for data transfer. The chip acts as a slave for receiving and transmitting data over the serial interface. All devices connected to the IIC bus must have open drain or open collector outputs. Logic AND function is exercised on both lines with external pull-up resistors, the value of these resistors is system dependent. When the serial interface is not active, the logic levels on SCL and SDA are pulled HIGH by external pull-up resistors.

Data received or transmitted on the SDA line must be stable at the positive edge of SCL. If the SDA changes state while SCL is HIGH, the IIC interface interprets that action as a START or STOP sequence. Data on SDA must change only when SCL is LOW.

The standard IIC traffic protocol is illustrated in the following Figure:

#### 3.2.1 Basic Protocol

For EP9122, there are six components to serial bus operation:

- START Signal

- Slave Address Byte

- Base Register Address Byte

- Data Byte for Read/Write

- STOP Signal

When the serial interface is inactive (SCL and SDA are HIGH), communication are initiated by a START signal which is a HIGH-to-LOW transition on SDA while SCL is HIGH. The first eight bits of data transferred after a START signal comprising a seven bit slave address (the seven MSB bits) and a single R/W bit (the LSB bit). The R/W bit indicates the direction of data transfer, "1" means read from device and "0" means write to device. If the transmitted slave address matches the address of the device, the EP9122 sends the acknowledge by asserting SDA Low on the ninth SCL pulse. Else, the EP9122 does not assert the acknowledge.

Writing data to specific control registers of the chip requires that the 8-bits address of the control register is written after the slave address has been acknowledged. This control register address is the base address for the subsequent write operations. The base address auto-increments by one for each byte of data written after the data byte intended for the base address. The acknowledge bit will be sent on the ninth SCL pulse after every 8-bits data received.

Data are read from the control registers of the chip in a similar manner. Reading requires two data transfer operations:

The base address must be written with the R/W bit of the slave address byte LOW to set up a sequential read operation.

Reading (the R/W bit of the slave address byte HIGH) begins at the previously established base address. The address of the read register auto-increments after each byte is transferred.

To terminate a read/write sequence to the chip, a STOP signal must be sent. A STOP signal comprises a LOW-to-HIGH transition of SDA while SCL is HIGH.

A repeated start signal occurs when the master device driving the serial interface generates a START signal without first generating a STOP signal to terminate the current read/write sequence. This can be used to change the mode of communication (read, write) between the slave and master without releasing the bus.

#### 3.2.2 Examples of the read/write sequence

Write to One Control Register

- START Signal

- Slave Address Byte (R/W bit = LOW)

- Base Address Byte

- Data Byte to Base Address

- STOP Signal

#### Write to Multiple Control Registers

- START Signal

- Slave Address Byte (R/W bit = LOW)

- Base Address Byte

- Data Byte to Base Address

- Data Byte to (Base Address + 1)

- Data Byte to (Base Address + 2)

- .....

- Data Byte to (Base Address + N)

- STOP Signal

#### Read from One Control Register

- START Signal

- Slave Address Byte (R/W bit = LOW)

- Base Address Byte

- STOP Signal (Optional)

- START Signal

- Slave Address Byte (R/W = HIGH)

- Data Byte from Base Address

- STOP Signal

#### Read from Multiple Control Registers

- START Signal

- Slave Address Byte (R/W bit = LOW)

- Base Address Byte

- STOP Signal (Optional)

- START Signal

- Slave Address Byte (R/W = HIGH)

- Data Byte from Base Address

- Data Byte from (Base Address + 1)

- Data Byte from (Base Address + 2)

- •

- Data Byte from (Base Address + N)

- STOP Signal

## 3.3 Description of the Control Registers

The following table shows all the control registers of the DVI/HDMI Transmitter EP9122:

**Table 3-1 IIC Control Registers**

| Addr | Mode | Bit7        | Bit6      | Bit5    | Bit4      | Bit3  | Bit2    | Bit1      | Bit0      | RESET |

|------|------|-------------|-----------|---------|-----------|-------|---------|-----------|-----------|-------|

| \$07 | R/W  | RX_LINK_ON  | RX_DE_ON  | RX_HDMI | RX_ENC_ON | -     | -       | RX_PU     | TX_SEL    | 02h   |

| \$08 | R/W  | TX_MUTE     | RX_VSYNC  | -       | -         | -     | -       | -         | TX_PU     | 01h   |

| \$09 | R    | -           | -         | -       | -         | -     | TX_RSEN | TX_HTPLG  | -         | 00h   |

| \$0A | R/W  |             | RESERV    | ED[3:0] |           | -     | -       | -         | -         | 80h   |

| \$0E | R/W  | -           | -         | -       | -         | -     | -       | TX_EESS   | TX_HDMI   | 01h   |

| \$0F | R/W  | TX_AKSV_RDY | TX_ENC_ON | -       | TX_RPTR   | -     | -       | TX_RI_RDY | TX_ENC_EN | 00h   |

| \$10 | R/W  |             |           |         | TX_B      | KSV_1 |         |           |           | XXh   |

| \$11 | R/W  |             |           |         | TX_B      | (SV_2 |         |           |           | XXh   |

| \$12 | R/W  |             |           |         | TX_B      | (SV_3 |         |           |           | XXh   |

| \$13 | R/W  |             | TX_BKSV_4 |         |           |       |         |           |           | XXh   |

| \$14 | R/W  | TX_BKSV_5   |           |         |           |       |         |           | XXh       |       |

| \$15 | R/W  | TX_AN_1     |           |         |           |       |         |           | XXh       |       |

| \$16 | R/W  |             | TX_AN_2   |         |           |       |         |           |           | XXh   |

| \$17 | R/W  |             | TX_AN_3   |         |           |       |         |           |           | XXh   |

| \$18 | R/W  |             | TX_AN_4   |         |           |       |         |           |           | XXh   |

| \$19 | R/W  |             | TX_AN_5   |         |           |       |         |           |           | XXh   |

| \$1A | R/W  |             |           |         | TX_A      | AN_6  |         |           |           | XXh   |

| \$1B | R/W  |             | TX_AN_7   |         |           |       |         |           |           | XXh   |

| \$1C | R/W  | TX_AN_8     |           |         |           |       |         |           | XXh       |       |

| \$1D | R    | TX_AKSV_1   |           |         |           |       |         |           | XXh       |       |

| \$1E | R    | TX_AKSV_2   |           |         |           |       |         |           | XXh       |       |

| \$1F | R    | TX_AKSV_3   |           |         |           |       |         |           | XXh       |       |

| \$20 | R    |             | TX_AKSV_4 |         |           |       |         |           |           | XXh   |

| \$21 | R    |             |           |         | TX_A      | KSV_5 |         |           |           | XXh   |

| \$22 | R | TX_RI_1 | XXh |

|------|---|---------|-----|

| \$23 | R | TX_RI_2 | XXh |

#### 3.3.1 Register Descriptions

Detailed usage of these IIC registers is described in the following section.

#### 3.3.1.1 Control Register 0

Table 3-2 Control Register 0

|        | <b>\$</b> 07 |          |         |           |   |   |          |        |

|--------|--------------|----------|---------|-----------|---|---|----------|--------|

|        |              | 6        | 5       | 4         | 3 | 2 | 1        | 0      |

| R      | RX_LINK_ON   | RX_DE_ON | RX_HDMI | RX_ENC_ON | _ | _ | RX_PU    | TX_SEL |

| W      |              | ì        | -       | -         |   |   | 11.7_1 0 | IX_SEE |

| Reset: | -            | -        | -       | -         | - | - | 1        | 0      |

#### RX\_LINK\_ON — Receiver Link On

This bit indicates whether a valid signal appears at the clock input of the receiver port. This bit is valid even when the receiver is powered off.

- 1 = Clock presents at the input of the receiver port

- 0 = No clock is detected at the input of the receiver port

#### RX\_DE\_ON — Receiver DE On

This bit indicates whether DE signal is toggling at the receiver port. This bit is valid only when the receiver is powered on.

- 1 = DE signal is toggling at the receiver port

- 0 = DE signal is not toggling at the receiver port

#### RX\_HDMI — Receiver HDMI signal

This bit indicates whether the receiver port is receiving DVI or HDMI signal

- 1 = HDMI

- 0 = DVI

#### RX\_ENC\_ON — Receiver Decryption On

This bit indicates whether the HDCP decryption is active at the receiver port.

- 1 = HDCP decryption at the receiver port is active

- 0 = HDCP decryption at the receiver port is not active

#### RX\_PU — Receiver Power Down Control Bit

This bit controls the power of the receiver port

1 = Normal operation.

0 = Power down Mode.

#### TX\_SEL — Transmitter Port Select for IIC Access

The 2 transmitter ports share the same IIC register address. This bit is used to select which transmitter port is addressed for IIC access.

- 1 = Port 1 is selected

- 0 = Port 0 is selected

#### 3.3.1.2 Control Register 1

**Table 3-3 Control Register 1**

|        | <b>300</b> |          |   |   |   |   |   |       |

|--------|------------|----------|---|---|---|---|---|-------|

|        |            | 6        | 5 | 4 | 3 | 2 | 1 | 0     |

| R      | I IX MUIF  | RX_VSYNC | - | - | - | - | - | TX_PU |

| W      |            | -        |   |   |   |   |   |       |

| Reset: | 0          | -        | - | 0 | - | - | - | 1     |

#### TX\_MUTE — Video Mute Transmitter

The bit is used to mute the video for the selected transmitter port.

- 1 = Selected transmitter port is video muted

- 0 = Normal

#### VSYNC — Vertical Sync Status Bit

The VSYNC bit gives the current status of the vertical sync signal received by the receiver.

#### TX\_PU — Transmitter Power Down Control Bit

This bit controls the power of the selected transmitter port

- 1 = Normal operation.

- 0 = Put the selected transmitter port in power down mode.

#### 3.3.1.3 Control Register 2

\$09

Table 3-4 Control Register 2

|        | • |   |   |   |   |         |          |   |  |

|--------|---|---|---|---|---|---------|----------|---|--|

|        |   | 6 | 5 | 4 | 3 | 2       | 1        | 0 |  |

| R      | _ | _ | _ | _ | _ | TX_RSEN | TX_HTPLG | _ |  |

| W      |   |   | _ |   | _ | -       | 1        |   |  |

| Reset. | = | _ | = | = | - | -       | -        | - |  |

#### TX\_RSEN — Transmitter Analog Output Status Bit

The TX\_RSEN bit indicates the analog output status at the selected transmitter port.

- 1 = The selected transmitter analog outputs are connected to the receiver

- 0 = The selected transmitter analog outputs are disconnected

#### TX\_HTPLG — Transmitter Hot Plug Status Bit

The TX\_HTPLG bit indicates the hot plug status at the selected transmitter port.

- 1 = Hot Plug detected at the selected transmitter port.

- 0 = Hot Plug not detected at the selected transmitter port.

#### 3.3.1.4 Control Register 3

Table 3-5 Control Register 3

\$0A

6 5 4 3 2 1 0

RESERVED[3:0] - - - -

Reset: 1 0 0 0 0 - - - - -

#### RESERVED[3:0] — RESERVED Control Bits

Set the reserved registers to 0x80 as the default value.

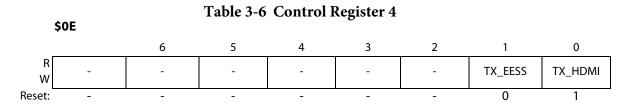

#### 3.3.1.5 Control Register 4

TX\_EESS — Enable Enhanced Encryption Signalling for the selected transmitter port

- 1 = Using Enhanced Encryption Signalling for the selected transmitter port.

- 0 = Using Original Encryption Signalling for the selected transmitter port. This is only valid if the selected transmitter is working in DVI mode (TX\_HDMI = 0).

#### TX\_HDMI — Set HDMI mode for the selected transmitter port

- 1 = Put the selected transmitter port working in HDMI mode. This is valid only if the receiver is receiving HDMI signal.

- 0 = Put the selected transmitter port working in DVI mode.

#### 3.3.1.6 Control Register 5

Table 3-7 Control Register 5

\$0F

6 5 4 3 2 1 0

R TX\_AKSV\_RDY TX\_ENC\_ON - TX\_RPTR - TX\_RI\_RDY TX\_ENC\_EN

- - - 0 - - 0

#### TX\_AKSV\_RDY — Transmitter AKSV Ready

The TX\_AKSV\_RDY bit indicates whether the HDCP keys and AKSV has been successfully downloaded from external EE or not for the selected transmitter port. This bit is read only.

- 1 = HDCP keys and AKSV has been successfully downloaded from external EE. AKSV is ready for read.

- 0 = HDCP keys and AKSV downloading has not been completed. AKSV is not ready for read.

#### TX\_ENC\_ON — Transmitter HDCP Encryption On

The TX\_ENC\_ON bit indicates whether the HDCP encryption for the selected transmitter port is active or not. This bit is read only.

- 1 = HDCP encryption is active.

- 0 = HDCP encryption is not active.

#### TX\_RPTR — Transmit to Repeater

The TX\_RPTR bit should be set if the receiver side which is connected to the selected transmitter port is a repeater. It should be cleared otherwise.

- 1 = The selected transmitter port is connecting to a repeater.

- 0 = The selected transmitter port is not connecting to a repeater.

#### TX\_RI\_RDY — Transmitter RI Ready

This bit indicates that the first Ri value is available for the selected transmitter port. This bit is read only.

- 1 = First Ri value is available for the selected transmitter port.

- 0 = First Ri value is not available for the selected transmitter port.

#### TX\_ENC\_EN — Transmitter ENC Enable

- 1 = Enable HDCP encryption for the selected transmitter port.

- 0 = Disable HDCP encryption the selected transmitter port.

#### **3.3.1.7 TX\_BKSV Registers** - TX\_BKSV\_1 ~ TX\_BKSV\_5

These 5 registers for the selected transmitter port should be programmed with receiver's Key Selection Vector. TX\_BKSV\_1 is the LSB and TX\_BKSV\_5 is the MSB. TX\_BKSV\_5 should be written last, as it triggers the authentication process.

#### **3.3.1.8 TX\_AN Registers** - $TX_AN_1 \sim TX_AN_8$

These 8 registers for the selected transmitter port should be programmed with a 64-bit pseudo-random value before triggering the authentication process. TX\_AN\_1 is the LSB and TX\_AN\_8 is the MSB.

#### **3.3.1.9 TX\_AKSV Registers** - TX\_AKSV\_1 ~ TX\_AKSV\_5

These 5 registers are read only which hold transmitter's Key Selection Vector for the selected transmitter port. TX\_AKSV\_1 is the LSB and TX\_AKSV\_5 is the MSB. All five bytes should be read from here and then written to the receiver. Byte 5 should be written last to the receiver, as it will trigger authentication there. These 5 registers should not be read until TX\_AKSV\_RDY bit is 1.

#### 3.3.1.10 TX\_RI Registers - $TX_RI_1 \sim TX_RI_2$

These 2 registers hold transmitter's Ri value for the selected transmitter port. They should be read and compared against the Ri value of the receiver to ensure that the encryption process on the transmitter and receiver is synchronized.

User Guide — EP9122\_UG V0.4

## **Section 4 Package**

User Guide — EP9122\_UG V0.4

## **User Guide End Sheet**

## FINAL PAGE OF 24 PAGES