# HDMI 1.3 Repeater with Audio Output EP91A1

# User Guide V0.1

Original Release Date: Mar. 11, 2009 Revised Date: Mar. 11, 2009

# Explore

Explore reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Explore does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Explore products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Explore product could create a situation where personal injury or death may occur. Should Buyer purchase or use Explore products for any such unintended or unauthorized application, Buyer shall indemnify and hold Explore and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Explore was negligent regarding the design or manufacture of the part.

# **Revision History**

| Version<br>Number | Revision<br>Date | Author    | Description of Changes |

|-------------------|------------------|-----------|------------------------|

| 0.1               | Mar/11/2009      | Ether Lai | Initial Version        |

# **Section 1 Introduction**

# 1.1 Overview

EP91A1 is an HDMI Repeater with Audio Output which is suitable for low cost Audio Amplifier application. The chip supports 1 HDMI input port, 1 HDMI output port and Audio Outputs in IIS and SPDIF. The chip also supports on-chip EDID RAM. This will save system cost quite a bit. The chip is compliant with HDMI 1.3b and supports SD/HD Audio and Video in 12-bit Deep Color up to 1080p (225 Mhz TMDS clock).

# 1.2 Features

- On-chip 1-IN 1-OUT HDMI Repeater with Equalizer

- Support wide Frequency Range: 25MHz 225MHz TMDS clock

- On-chip HDMI Receiver and Transmitter core which are compliant with HDMI 1.3b specification

- On-chip HDCP Engine which supports Repeater and is compliant with HDCP 2.0 specification

- Supports on-chip EDID RAM for HDMI RX port.

- On-chip Audio Decoder which support 2-channel IIS/DSD and SPDIF audio outputs

- Support audio soft mute

- Support SPDIF Channel Status extraction

- Register-programmable via slave IIC interface

- Flexible interrupt registers with interrupt pin

- Link On and Valid DE Detection

- Controllable tri-state for Audio output pins

- Low stand-by current (< 2mA) at power down mode

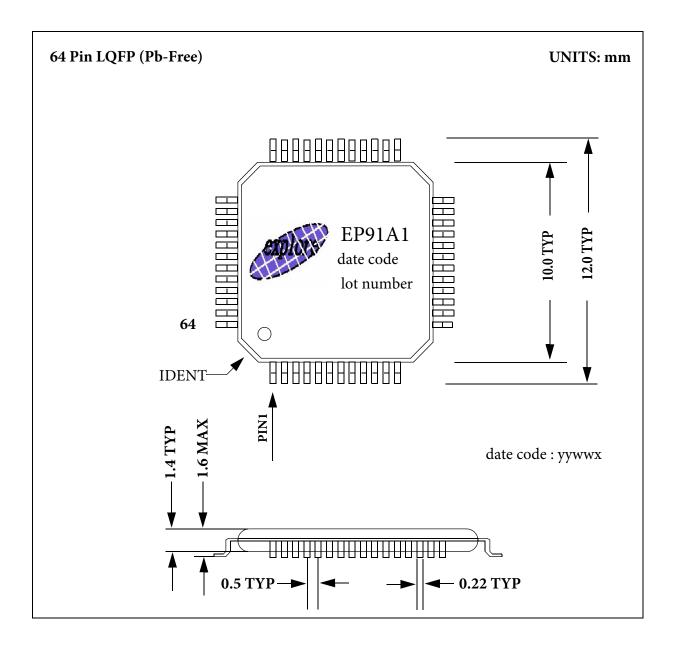

- 64-pin LQFP package

User Guide — EP91A1\_UG V0.1

# **Section 2 Overview**

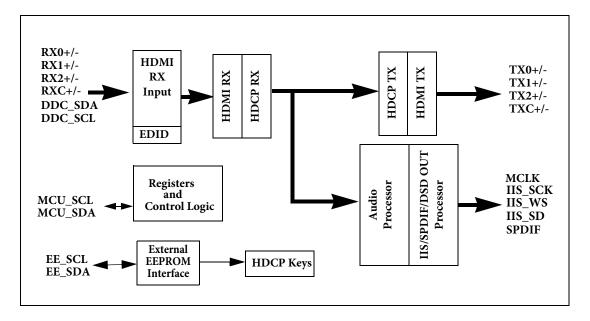

# 2.1 Chip Block Diagram

Figure 2-1 Chip Block Diagram

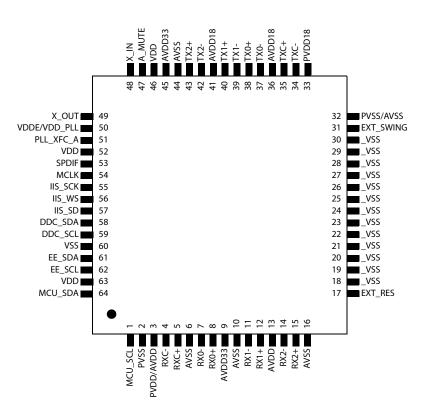

## 2.2 Pin Diagram

# 2.3 Pin Description

Unless otherwise stated, unused input pins must be tied to ground, and unused output pins left open.

| Name    | In/Out | Description                                                                                                                    |  |  |

|---------|--------|--------------------------------------------------------------------------------------------------------------------------------|--|--|

| RXC-    | IN     | Differential Clock Input Pair for HDMI Input                                                                                   |  |  |

| RXC+    | IN     | Differential Clock Input Pair for HDMI Input                                                                                   |  |  |

| RX0-    | IN     | Differential Data Input Pair0 for HDMI Input                                                                                   |  |  |

| RX0+    | IN     | Differential Data Input Pair0 for HDMI Input                                                                                   |  |  |

| RX1-    | IN     | Differential Data Input Pair1 for HDMI Input                                                                                   |  |  |

| RX1+    | IN     | Differential Data Input Pair1 for HDMI Input                                                                                   |  |  |

| RX2-    | IN     | Differential Data Input Pair2 for HDMI Input                                                                                   |  |  |

| RX2+    | IN     | Differential Data Input Pair2 for HDMI Input                                                                                   |  |  |

| EXT_RES | IN     | External Termination Resistor for all HDMI Input Ports. A resistor should tie this pin to AVDD33. 470 $\Omega$ is recommended. |  |  |

#### Table 2-1 HDMI Input Ports

#### Table 2-2 HDMI Output Ports

| Name      | In/Out | Description                                                                                                                                                                |

|-----------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXC-      | OUT    | Differential Clock Output Pair for HDMI Output                                                                                                                             |

| TXC+      | OUT    | Differential Clock Output Pair for HDMI Output                                                                                                                             |

| TX0-      | OUT    | Differential Data Output Pair0 for HDMI Output                                                                                                                             |

| TX0+      | OUT    | Differential Data Output Pair0 for HDMI Output                                                                                                                             |

| TX1-      | OUT    | Differential Data Output Pair1 for HDMI Output                                                                                                                             |

| TX1+      | OUT    | Differential Data Output Pair1 for HDMI Output                                                                                                                             |

| TX2-      | OUT    | Differential Data Output Pair2 for HDMI Output                                                                                                                             |

| TX2+      | OUT    | Differential Data Output Pair2 for HDMI Output                                                                                                                             |

| EXT_SWING | Analog | Voltage Swing Adjust for HDMI Output. A resistor should tie this pin to AVDD18. This resistance determines the amplitude of the voltage swing. $270\Omega$ is recommended. |

#### **Table 2-3 Audio Outputs**

| Name                                                                                                                            | In/Out | Description                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCLK                                                                                                                            | OUT    | System Clock output for audio DAC (128/256/384/512 * F <sub>Sampling_Clock</sub> .<br>Connecting a pull-up (logic 1) or pull-down (logic 0) resistor at this pin<br>defines bit 4 of the slave IIC Address |

| IIS_SCK OUT IIS SCK output for IIS audio port                                                                                   |        | IIS SCK output for IIS audio port. Sampling clock output for DSD.                                                                                                                                          |

| IIS_WS                                                                                                                          | OUT    | IIS WS output for all IIS audio ports.<br>DSD audio output port (Right Channel).                                                                                                                           |

| IIS_SD     OUT     IIS SD output for audio port.<br>DSD audio output port (Left Channel).       SPDIF     OUT     SPDIF output. |        |                                                                                                                                                                                                            |

|                                                                                                                                 |        | SPDIF output.                                                                                                                                                                                              |

| Table 2-3 | Audio | Outputs |

|-----------|-------|---------|

|-----------|-------|---------|

| Name   | In/Out | Description       |

|--------|--------|-------------------|

| A_MUTE | OUT    | Audio Mute Output |

#### Table 2-4 DDC/IIC/MCU/EEPROM

| Name    | In/Out | Description                               |

|---------|--------|-------------------------------------------|

| MCU_SCL | IN     | SCL signal for slave IIC port             |

| MCU_SDA | IO     | SDA signal for slave IIC port             |

| DDC_SCL | IN     | IIC SCL signal for HDMI Receiver DDC Port |

| DDC_SDA | 10     | IIC SDA signal for HDMI Receiver DDC Port |

| EE_SCL  | OUT    | SCL signal for EE IIC port                |

| EE_SDA  | Ю      | SDA signal for EE IIC port                |

#### Table 2-5 Misc. Pins

| Name      | In/Out | Description                                          |  |

|-----------|--------|------------------------------------------------------|--|

| X_IN      | Analog | External Crystal Input, 18.432 Mhz                   |  |

| X_OUT     | Analog | External Crystal Output, 18.432 Mhz                  |  |

| PLL_XFC_A | Analog | For connecting a capacitor to ground for on-chip PLL |  |

#### **Table 2-6 Power Pins**

| Name         | In/Out | Description                           |

|--------------|--------|---------------------------------------|

| AVDD         | PWR    | HDMI Receiver Analog Power (1.8V)     |

| PVDD         | PWR    | HDMI Receiver PLL Analog Power (1.8V) |

| AVDD33       | PWR    | HDMI Termination Power (3.3V)         |

| AVDD18       | PWR    | HDMI Transmitter Analog Power (1.8V)  |

| PVDD18       | PWR    | HDMI Transmitter PLL Analog Power     |

| AVSS, PVSS   | GND    | Analog Ground                         |

| VDDE/VDD_PLL | PWR    | I/O Power (3.3V)                      |

| VDD          | PWR    | Internal Logic Power (1.8V)           |

| VSS          | GND    | I/O & Logic Ground                    |

| _VSS         | GND    | Common Ground                         |

# 2.4 Electrical Characteristics

| Symbol           | Parameter                                | Min  | Тур | Max                     | Units |

|------------------|------------------------------------------|------|-----|-------------------------|-------|

| Vcc33            | 3.3V Supply Voltage                      | -0.3 |     | 4.0                     | V     |

| Vcc18            | 1.8V Supply Voltage                      | -0.3 |     | 2.5                     | V     |

| VI               | Input Voltage                            | -0.3 |     | V <sub>cc33</sub> + 0.3 | V     |

| V <sub>O</sub>   | Output Voltage                           | -0.3 |     | V <sub>cc33</sub> + 0.3 | V     |

| Тյ               | Junction Temperature                     |      |     | 125                     | °C    |

| T <sub>STG</sub> | Storage Temperature                      | -40  |     | 125                     | °C    |

| $\theta_{JA}$    | Thermal Resistance (Junction to Ambient) |      | 44  |                         | °C/W  |

## **Absolute Maximum Conditions**

### **Normal Operating Conditions**

| Symbol           | Parameter                                | Min  | Тур | Max  | Units             |

|------------------|------------------------------------------|------|-----|------|-------------------|

| Vcc33            | 3.3V Supply Voltage                      | 3.14 | 3.3 | 3.6  | V                 |

| Vcc18            | 1.8V Supply Voltage                      | 1.71 | 1.8 | 1.98 | V                 |

| V <sub>CCN</sub> | Supply Voltage Noise <sup>1</sup>        | -0.3 |     | 100  | mV <sub>p-p</sub> |

| T <sub>A</sub>   | Ambient Temperature (with power applied) | 0    | 25  | 70   | °C                |

### DC Digital I/O Specifications (under normal operating conditions unless otherwise specified)

| Symbol          | Parameter                 | Conditions     | Min | Тур | Max | Units |

|-----------------|---------------------------|----------------|-----|-----|-----|-------|

| V <sub>IH</sub> | High-level Input Voltage  |                | 2.0 |     |     | V     |

| V <sub>IL</sub> | Low-level Input Voltage   |                |     |     | 0.8 | V     |

| V <sub>OH</sub> | High-level Output Voltage |                | 2.4 |     |     | V     |

| V <sub>OL</sub> | Low-level Output Voltage  |                |     |     | 0.4 | V     |

| I <sub>OL</sub> | Output Leakage Current    | High Impedance | -10 |     | 10  | uA    |

#### User Guide — EP91A1\_UG V0.1

| Symbol           | Parameter                                                                             | Conditions                                                     |      | Min | Тур  | Max | Units |

|------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------|------|-----|------|-----|-------|

| V <sub>OD</sub>  | Differential Voltage<br>Single ended peak to peak amplitude                           | R <sub>LOAD</sub> = 50 ohm<br>R <sub>EXT_SWING</sub> = 270 ohn | 510  | 550 | 590  | mV  |       |

| V <sub>DOH</sub> | Differential High-level Output Voltage <sup>1</sup>                                   |                                                                |      |     | AVCC |     | V     |

| I <sub>DOS</sub> | Differential Output Short Circuit Current                                             | V <sub>OUT</sub> = 0V; TX_TERM bit                             | is 0 |     |      | 5   | uA    |

|                  | Power-Down Current <sup>2</sup>                                                       | 25°C Ambient                                                   | 3V3  |     | 1    |     | mA    |

| I <sub>PD</sub>  | Power-Down Current                                                                    | 25 C Amblent                                                   | 1V8  |     | 2    |     | mA    |

|                  |                                                                                       | 1000 perclution (0 hit)                                        | 3V3  |     | TBD  |     | mA    |

|                  | Supply Current<br>(25°C Ambient, RX/TX are Active                                     | 1080p Resolution (8-bit)                                       | 1V8  |     | TBD  |     | mA    |

| I <sub>CCD</sub> | $R_{EXT\_RES} = 470 \text{ ohm}, R_{EXT\_SWING} = 270 \text{ ohm}, TX TERM bit is 1)$ | 1090p Poselution (12 bit)                                      | 3V3  |     | TBD  |     | mA    |

|                  | ··· · <u>Drait on 10</u> · )                                                          | 1080p Resolution (12-bit)                                      | 1V8  |     | TBD  |     | mA    |

DC Analogue Specifications (under normal operating conditions unless otherwise specified)

1 Guaranteed by design.

2 Assumes all HDMI/DVI I/O ports are not connected and all digital inputs are silent.

#### Receiver AC Specifications (under normal operating conditions unless otherwise specified)

| Symbol            | Parameter                                                | Conditions | Min | Тур | Max | Units              |

|-------------------|----------------------------------------------------------|------------|-----|-----|-----|--------------------|

| T <sub>DPS</sub>  | Intra-Pair (+ to -) Differential Input Skew <sup>1</sup> |            |     |     | 0.4 | T <sub>bit</sub>   |

| T <sub>CCS</sub>  | Channel to Channel Differential Input Skew <sup>1</sup>  |            |     |     | 1.0 | T <sub>pixel</sub> |

| T <sub>IJIT</sub> | Differential Input Clock Jitter Tolerance <sup>2,3</sup> |            |     |     | 0.3 | T <sub>bit</sub>   |

| F <sub>CIP</sub>  | TMDS CLK Frequency                                       |            | 25  |     | 225 | MHz                |

NOTES:

1. Guaranteed by design.

2. Jitter defines as per DVI 1.0 Specification, Section 4.6 Jitter Specification.

3. Jitter measured with Clock Recovery Unit as per DVI 1.0 Specification, Section 4.7 Electronic Measurement Procedures

#### Transmitter AC Specifications (under normal operating conditions unless otherwise specified)

| Symbol           | Parameter                                      | Conditions                                                                                  | Min | Тур | Max | Units |

|------------------|------------------------------------------------|---------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| S <sub>LHT</sub> | Differential Swing Low-to-High Transition Time | C <sub>LOAD</sub> = 5pF,<br>R <sub>LOAD</sub> = 50 ohm,<br>R <sub>EXT_SWING</sub> = 270 ohm | 170 | 200 | 230 | ps    |

| S <sub>HLT</sub> | Differential Swing High-to-Low Transition Time | C <sub>LOAD</sub> = 5pF,<br>R <sub>LOAD</sub> = 50 ohm,<br>R <sub>EXT_SWING</sub> = 270 ohm | 170 | 200 | 230 | ps    |

| Symbol             | Parameter                     | Conditions            | Min | Тур | Max | Units            |

|--------------------|-------------------------------|-----------------------|-----|-----|-----|------------------|

| T <sub>sck</sub>   | SCK Clock Period              | C <sub>L</sub> = 10pF |     | 1   |     | T <sub>sck</sub> |

| T <sub>sck_d</sub> | SCK Clock Duty Cycle          | C <sub>L</sub> = 10pF | 40% |     | 60% | T <sub>sck</sub> |

| T <sub>sck_h</sub> | SCK Clock High Time           | C <sub>L</sub> = 10pF | 40% |     | 60% | T <sub>sck</sub> |

| T <sub>sck_I</sub> | SCK Clock LOW Time            | C <sub>L</sub> = 10pF | 40% |     | 60% | T <sub>sck</sub> |

| T <sub>iis_s</sub> | SCK to SD and WS (Setup Time) | C <sub>L</sub> = 10pF | 40% |     | -   | T <sub>sck</sub> |

| T <sub>iis_h</sub> | SCK to SD and WS (Hold Time)  | C <sub>L</sub> = 10pF | 40% |     | -   | T <sub>sck</sub> |

I2S Audio AC Specifications (under normal operating conditions unless otherwise specified)

## SPDIF Audio AC Specifications (under normal operating conditions unless otherwise specified)

| Symbol               | Parameter        | Conditions            | Min | Тур | Max  | Units |

|----------------------|------------------|-----------------------|-----|-----|------|-------|

| T <sub>spdif</sub>   | SPDIF Cycle Time | C <sub>L</sub> = 10pF |     | 1   |      | UI    |

| T <sub>spdif_d</sub> | SPDIF Duty Cycle | C <sub>L</sub> = 10pF | 90% |     | 110% | UI    |

User Guide — EP91A1\_UG V0.1

# **Section 3 Functional Description**

## 3.1 1-In 1-Out HDMI Repeater

The chip supports 1 HDMI Input Port, 1 HDMI Output Port and audio outputs. The incoming A/V source is HDCP decoded in HDMI RX and HDCP encoded again for HDMI Transmitter Port output.

# 3.2 Audio Output

Audio data is extracted and decoded from the HDMI RX. The conventional SD/HD Audio and 2 channel One Bit Audio are supported. The decoded audio data is buffered in an on-chip FIFO. An on-chip PLL is used to regenerate audio clock from the HDMI TMDS clock under the control of HDMI source. Digital audio signals in IIS, SPDIF or DSD format are generated based on this regenerated audio clock.

# 3.3 HDCP Engine & HDCP Keys

There are 2 HDCP engines on-chip. One is for HDMI RX port and the other is for HDMI TX Port. The on-chip HDCP (High-bandwidth Digital Content Protection) engines are compliant with HDCP 2.0 specification. The 2 HDCP key sets and BKSVs are downloaded from external EE at power up. The HDCP keys stored in external EE are scrambled for security purpose. The chip will descramble the keys after download.

# 3.4 InfoFrame Data

All types of Packet/InfoFrame data can be extracted, decoded from HDMI data stream and stored in the internal registers. The Audio InfoFrames is always extracted and put in dedicated buffers. Other Packet/InfoFrame type can be selectively extracted and stored in 2 shared packet buffers. Whenever an InfoFrame is received, an interrupt flag is set in an internal register. The MCU can poll the interrupt flags and extract the InfoFrame content through IIC bus.

User Guide — EP91A1\_UG V0.1

# **Section 4 Detail Functional Descriptions**

## 4.1 IIC Interface

The chip provides an IIC serial bus interface (SCL/SDA pins) for MCU to access the HDMI control/status registers and Repeater control/status registers. The IIC address for HDMI control/status registers is "110\_IICA\_100x" and the IIC address for Repeater control/status registers is "110\_IICA\_101x" (where x=1 for read and x=0 for write). IICA is programmable by connecting a pull-up (logic 1) or pull-down (logic 0) resistor at MCLK pin.

|           | HDMI               | Nodule | REPEATER Module |          |  |

|-----------|--------------------|--------|-----------------|----------|--|

| MCLK Pin  | IIC write IIC read |        | IIC write       | IIC read |  |

| Pull-Down | C8                 | С9     | CA              | СВ       |  |

| Pull-Up   | D8                 | D9     | DA              | DB       |  |

Table 4-1 IIC Address of HDMI and Repeater

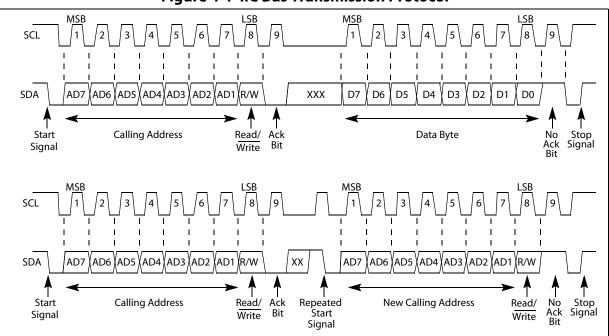

The IIC bus is a slave which uses a Serial Data line (SDA) at MCU\_SDA pin and a Serial Clock Line (SCL) at MCU\_SCL pin for receiving and transmitting data. All devices connected to the IIC bus must have open drain or open collector outputs. Logic AND function is exercised on both lines with external pull-up resistors, the value of these resistors is system dependent. When the serial interface is not active, the logic levels on SCL and SDA are pulled HIGH by external pull-up resistors.

Data received or transmitted on the SDA line must be stable at the positive edge of SCL. If the SDA changes state while SCL is HIGH, the IIC interface interprets that action as a START or STOP sequence. Data on SDA must change only when SCL is LOW.

When the serial interface is inactive (SCL and SDA are HIGH), communication are initiated by a START signal which is a HIGH-to-LOW transition on SDA while SCL is HIGH. The first eight bits of data transferred after a START signal comprising a seven bit slave address (the seven MSB bits) and a single R/W bit (the LSB bit). The R/W bit indicates the direction of data transfer, "1" means read from device and "0" means write to device. If the transmitted slave address matches the address of the device, the chip sends the acknowledge by asserting SDA Low on the ninth SCL pulse. Else, the chip does not acknowledge.

To terminate a read/write sequence, a STOP signal must be sent. A STOP signal comprises a LOW-to-HIGH transition of SDA while SCL is HIGH.

A Repeated START signal occurs when the master device driving the serial interface generates a START signal without first generating a STOP signal to terminate the current read/write sequence. This can be used to change the mode of communication (read, write) between the slave and master without releasing the bus.

The standard IIC traffic protocol is illustrated in the following Figure:

Figure 4-1 IIC Bus Transmission Protocol

# 4.2 IIC Protocol for HDMI and Repeater Control/Status Register

## 4.2.1 HDMI Control/Status Register Access

HDMI control/status registers are organized by Register Sets. Each Register Set is comprised of one or more than one bytes of register. To address a register byte, a Word Address along with a Byte Address should be given. Word Address is used to address the register set and Byte Address is used to address the designated register byte within the addressed register set. There are 5 components in this IIC protocol:

- START Signal

- Slave Address Byte

- Word Address Byte for the Register Set

- Data Bytes for Read/Write from/to the Register Set

- STOP Signal

In Write Operation, data write starts from byte 0 of the register set and continue write to the next byte of the register set if data presents. The acknowledge bit will be sent on the ninth SCL pulse after every 8-bits data received.

In Read Operation, data are read from byte 0 of the register set in a similar manner. Reading requires two IIC transfer operations:

The Word Address must be written with the R/W bit of the slave address byte being LOW to set up the Word Address for the following read operations.

Start reading data with the R/W bit of the slave address byte being HIGH from the Word Address previously established. Data is read from byte 0 of the address register set and continue the next byte read if acknowledge presents.

Write to a Register Set:

- START Signal

- Slave Address Byte (R/W bit = LOW)

- Word Address Byte

- Data Byte/Bytes to the register set starting from byte 0

- STOP Signal

Read from a Register Set:

- START Signal

- Slave Address Byte (R/W bit = LOW)

- Word Address Byte

- Repeated START Signal

- Slave Address Byte (R/W = HIGH)

- Data Byte/Bytes from addressed register set starting from byte 0

- STOP Signal

## 4.2.2 Repeater Control/Status Register Access

Repeater control/status registers are organized by individual registers. To address a register byte, a Base Address should be given. Once the Base Address is established, single byte or multiple bytes data can be written or read from the registers starting from the Base Address. There are 5 components in this IIC protocol:

- START Signal

- Slave Address Byte

- Base Register Address Byte

- Data Byte for Read/Write

- STOP Signal

In Write Operation, data write starts from the Base Address and continue write to the next address register if data presents. The acknowledge bit will be sent on the ninth SCL pulse after every 8-bits data received.

In Read Operation, data are read from the Base Address in a similar manner. Reading requires two IIC transfer operations:

The Base Address must be written with the R/W bit of the slave address byte being LOW to set up the Base Address for the following read operations.

Start reading data with the R/W bit of the slave address byte being HIGH from the Base Address previously established. Data is read from Base Address and continue the next address read if acknowledge presents.

Write to One Control Register:

- START Signal

- Slave Address Byte (R/W bit = LOW)

- Base Address Byte

- Data Byte to Base Address

- STOP Signal

Write to Multiple Control Registers:

- START Signal

- Slave Address Byte (R/W bit = LOW)

- Base Address Byte

- Data Byte to Base Address

- Data Byte to (Base Address + 1)

- Data Byte to (Base Address + 2)

- .....

- Data Byte to (Base Address + N)

- STOP Signal

Read from One Control Register:

- START Signal

- Slave Address Byte (R/W bit = LOW)

- Base Address Byte

- Repeated START Signal

- Slave Address Byte (R/W = HIGH)

- Data Byte from Base Address

- STOP Signal

Read from Multiple Control Registers:

- START Signal

- Slave Address Byte (R/W bit = LOW)

- Base Address Byte

- Repeated START Signal

- Slave Address Byte (R/W = HIGH)

- Data Byte from Base Address

- Data Byte from (Base Address + 1)

- Data Byte from (Base Address + 2)

- .....

- Data Byte from (Base Address + N)

- STOP Signal

## 4.3 HDMI Control/Status Registers

## 4.3.1 Register Descriptions

## 4.3.1.1 Interrupt Control and Flags (Word Address = \$29)

| 1          | Word Address = \$29, Byte 0 |        |        |        |        |   |       |   |  |  |  |  |  |

|------------|-----------------------------|--------|--------|--------|--------|---|-------|---|--|--|--|--|--|

| bit        | 7                           | 6      | 5      | 4      | 3      | 2 | 1     | 0 |  |  |  |  |  |

| R          | -                           | AVMC_F | AVMS_F | SEL2_F | SEL1_F | - | ADO_F | - |  |  |  |  |  |

| W          | -                           | -      | -      | -      | -      | - | -     | - |  |  |  |  |  |

| Pin Reset: | 0                           | 0      | 0      | 0      | 0      | 0 | 0     | 0 |  |  |  |  |  |

Table 4-2

Interrupt Register 0

If this register is read, it gives Interrupt Flag information. Whenever a designated packet is received, the corresponding interrupt flag bit will be set. After MCU read this register, all the flag bits will be cleared automatically. Special care is taken by the design to prevent accidentally loss of any flag bit.

ADO\_F — Audio InfoFrame Interrupt Flag

This bit is set when an Audio InfoFrame is received and is auto cleared when the register is read.

SEL1\_F — 1st Selected Packet Interrupt Flag

This bit is set when the selected packet 1 is received and is auto cleared when the register is read.

### SEL2\_F — 2nd Selected Packet Interrupt Flag

This bit is set when the selected packet 2 is received and is auto cleared when the register is read.

### AVMS\_F — AVMUTE Set Interrupt Flag

This bit is set when AVMUTE is set by General Control Packet and is auto cleared when the register is read.

AVMC\_F — AVMUTE Clear Interrupt Flag

This bit is set when AVMUTE is cleared by General Control Packet and is auto cleared when the register is read.

## Table 4-3 Interrupt Register 1

| Word Address = \$29, Byte 1 |  |

|-----------------------------|--|

|-----------------------------|--|

| bit        | 7      | 6       | 5       | 4       | 3       | 2 | 1 | 0       |

|------------|--------|---------|---------|---------|---------|---|---|---------|

| R          | AAMS_F | EXCP_F6 | EXCP_F5 | EXCP_F4 | EXCP_F3 | - | - | EXCP_F0 |

| W          | -      | -       | -       | -       | -       | - | - | -       |

| Pin Reset: | 0      | 0       | 0       | 0       | 0       | 0 | 0 | 0       |

If this register is read, it gives Interrupt Flag information. Whenever an exception occurs, the corresponding interrupt flag bit will be set. After MCU read this register, all the flag bits will be cleared automatically. Special care is taken by the design to prevent accidentally loss of any flag bit.

EXCP\_F0 — Exception 0 Interrupt Flag

This bit is set when a BCH error is detected.

EXCP\_F3 — Exception 3 Interrupt Flag

This bit is set when audio mode change is detected from ADO packet.

EXCP\_F4 — Exception 4 Interrupt Flag

This bit is set when audio sampling frequency change is detected.

EXCP\_F5 — Exception 4 Interrupt Flag

This bit is set when audio FIFO overflow/underflow is detected.

### EXCP\_F6 — Exception 6 Interrupt Flag

This bit is set when HDMI signal changes from valid to invalid or from invalid to valid.

AAMS\_F — Automatic Audio Mute Set Flag

This bit is set when A\_MUTE bit is automatically set by AAM (Automatic Audio Mute) logic on detection of designated exception.

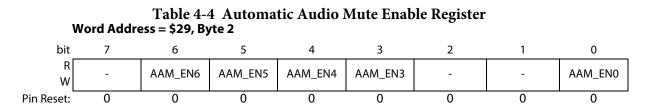

This register controls the Automatic Audio Mute (AAM) function. Each bit controls whether the A\_MUTE bit will be automatically set or not when the designated exception occurs. When A\_MUTE bit is set, audio is mute.

AAM\_EN0 — Automatic Audio Mute Enable 0

1 = A\_MUTE bit will be automatically set when EXCP\_F0 is set.

$0 = A_MUTE$  bit is not affected by EXCP\_F0.

AAM\_EN3 — Automatic Audio Mute Enable 3

1 = A\_MUTE bit will be automatically set when EXCP\_F3 is set.

$0 = A_MUTE$  bit is not affected by EXCP\_F3.

AAM\_EN4 — Automatic Audio Mute Enable 4

1 = A\_MUTE bit will be automatically set when EXCP\_F4 is set.

$0 = A_MUTE$  bit is not affected by EXCP\_F4.

AAM\_EN5 — Automatic Audio Mute Enable 5

$1 = A_MUTE$  bit will be automatically set when EXCP\_F5 is set.

$0 = A_MUTE$  bit is not affected by EXCP\_F5.

AAM\_EN6 — Automatic Audio Mute Enable 6

1 = A\_MUTE bit will be automatically set when EXCP\_F6 is set.

$0 = A_MUTE$  bit is not affected by EXCP\_F6.

#### 4.3.1.2 Audio InfoFrame (Word Address = \$2B)

The 7-byte Audio InfoFrame content is stored in the register set with Word Address \$2C with Byte-0 being the version number, Byte-1 being the packet check sum, Byte-2 corresponding to the 1st byte of the InfoFrame and Byte-6 corresponding to the last byte of the InfoFrame.

| Word<br>Address | By | te # | bit7   | bit6           | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |  |  |  |

|-----------------|----|------|--------|----------------|------|------|------|------|------|------|--|--|--|

|                 | 0  |      |        | Version Number |      |      |      |      |      |      |  |  |  |

|                 | 1  |      |        | Checksum       |      |      |      |      |      |      |  |  |  |

|                 | 2  |      | CT3    | CT2            | CT1  | CT0  | 0    | CC2  | CC1  | CC0  |  |  |  |

| 0x2B            | 3  | R    | 0      | 0              | 0    | SF2  | SF1  | SF0  | SS1  | SS0  |  |  |  |

|                 | 4  |      | 0      | 0              | 0    | 0    | 0    | 0    | 0    | 0    |  |  |  |

|                 | 5  |      | CA7    | CA6            | CA5  | CA4  | CA3  | CA2  | CA1  | CA0  |  |  |  |

|                 | 6  |      | DM_INH | LSV3           | LSV2 | LSV1 | LSV0 | 0    | 0    | 0    |  |  |  |

## Table 4-5 ADO InfoFrame Registers

### 4.3.1.3 Selected Packet 1 (Word Address = \$2D)

Any other packet with specified packet type can be extracted and stored in this register set. The specified packet type needs to be written into Byte-0. If 0 value is written, no packet will be extracted. If a packet with matched packet type is received, the 3-byte Packet Header and the 28-byte Packet Content are stored in the register set in sequence starting from Byte-0 and end at Byte-30.

### 4.3.1.4 Selected Packet 2 (Word Address = \$2E)

Any other packet with specified packet type can be extracted and stored in this register set. The specified packet type needs to be written into Byte-0. If 0 value is written, no packet will be extracted. If a packet with

matched packet type is received, the 3-byte Packet Header and the 28-byte Packet Content are stored in the register set in sequence starting from Byte-0 and end at Byte-30.

| Word<br>Address | Ву | te # | bit7                                                   | bit6                      | bit5      | bit4        | bit3         | bit2       | bit1 | bit0 |  |  |

|-----------------|----|------|--------------------------------------------------------|---------------------------|-----------|-------------|--------------|------------|------|------|--|--|

|                 | 0  | R/W  |                                                        | P                         | acket Hea | der 0 (HB0  | , Selected I | Packet Typ | e)   | .1   |  |  |

|                 | 1  |      |                                                        |                           |           | Packet Hea  | ader 1 (HB1  | )          |      |      |  |  |

|                 | 2  |      | Packet Header 2 (HB2)                                  |                           |           |             |              |            |      |      |  |  |

|                 | 3  |      |                                                        |                           | [         | Data Byte 0 | (PB0 / SB0   | D)         |      |      |  |  |

|                 | 4  |      |                                                        |                           |           |             | (PB1 / SB    | ,          |      |      |  |  |

|                 |    |      |                                                        |                           |           |             | (PB2 / SB2   |            |      |      |  |  |

|                 | 6  |      |                                                        |                           | [         | Data Byte 3 | (PB3 / SB3   | 3)         |      |      |  |  |

|                 | 7  |      |                                                        |                           | [         | Data Byte 4 | (PB4 / SB4   | 4)         |      |      |  |  |

|                 | 8  |      |                                                        |                           |           |             | (PB5 / SB    |            |      |      |  |  |

|                 | 9  |      |                                                        |                           |           |             | 6 (PB6 /SB6  | ,          |      |      |  |  |

|                 | 10 |      |                                                        |                           |           |             | (PB7 / SB0   | ,          |      |      |  |  |

|                 | 11 |      |                                                        | Data Byte 8 (PB8 / SB1)   |           |             |              |            |      |      |  |  |

|                 | 12 | -    |                                                        |                           |           |             | (PB9 / SB2   |            |      |      |  |  |

|                 | 13 | -    |                                                        |                           |           |             | (PB10 / SE   | ,          |      |      |  |  |

| 0x2D            | 14 |      |                                                        |                           |           |             | (PB11 / SE   |            |      |      |  |  |

| &               | 15 | R    |                                                        | Data Byte 12 (PB12 / SB5) |           |             |              |            |      |      |  |  |

| 0x2E            | 16 |      | Data Byte 13 (PB13 / SB6)                              |                           |           |             |              |            |      |      |  |  |

|                 | 17 |      |                                                        | Data Byte 14 (PB14 / SB0) |           |             |              |            |      |      |  |  |

|                 | 18 |      |                                                        |                           |           |             | (PB15 / SE   |            |      |      |  |  |

|                 | 19 |      | Data Byte 16 (PB16 / SB2)                              |                           |           |             |              |            |      |      |  |  |

|                 | 20 |      |                                                        |                           |           |             | (PB17 / SE   |            |      |      |  |  |

|                 | 21 |      |                                                        |                           |           |             | (PB18 / SE   | ,          |      |      |  |  |

| 1               | 22 |      |                                                        |                           |           |             | (PB19 / SE   | ,          |      |      |  |  |

|                 | 23 |      |                                                        |                           |           |             | (PB20 / SE   | ,          |      |      |  |  |

|                 | 24 |      |                                                        |                           |           |             | (PB21 / SE   | ,          |      |      |  |  |

|                 | 25 |      |                                                        |                           |           |             | (PB22 / SE   |            |      |      |  |  |

|                 | 26 |      |                                                        |                           |           |             | (PB23 / SE   |            |      |      |  |  |

|                 | 27 |      |                                                        |                           |           |             | (PB24 / SE   | ,          |      |      |  |  |

|                 | 28 |      | Data Byte 25 (PB25 / SB4)<br>Data Byte 26 (PB26 / SB5) |                           |           |             |              |            |      |      |  |  |

|                 | 29 |      |                                                        |                           |           |             |              |            |      |      |  |  |

|                 | 30 |      |                                                        |                           | Da        | ata Byte 27 | (PB27 / SE   | 36)        |      |      |  |  |

Table 4-6 Selected Packet Type 1/2 Registers

#### 4.3.1.5 Status Register 0 (Word Address = \$3C, Byte 0)

| ,   | Table 4-7 Status Register 0<br>Word Address = \$3C, Byte 0 |   |          |      |   |   |            |        |  |  |  |  |  |

|-----|------------------------------------------------------------|---|----------|------|---|---|------------|--------|--|--|--|--|--|

| bit | 7                                                          | 6 | 5        | 4    | 3 | 2 | 1          | 0      |  |  |  |  |  |

| R   | -                                                          | - | AVMUTE   | HDMI | - | - | DST_double | LAYOUT |  |  |  |  |  |

| W   |                                                            |   | AVMUTE_R |      |   |   |            |        |  |  |  |  |  |

|     | -                                                          | - | 0        | -    | - | - | -          | -      |  |  |  |  |  |

#### Explore Confidential Proprietary NON-DISCLOSURE AGREEMENT REQUIRED

AVMUTE — (Read Only) AVMUTE signal decoded from HDMI General Control Packet.

1 = AVMUTE is in set state.

0 = AVMUTE is in clear state.

- AVMUTE \_R (Write Only) AVMUTE reset.

- 1 = Clear AVMUTE.

- 0 = No operation.

HDMI — (Read Only) Primary RX HDMI/DVI signalling indicator

- 1 = HDMI signalling detected.

- 0 = DVI signalling detected.

DST\_double — (Read Only) DST audio transfer rate indicator. Only valid if DST audio source is selected.

1 = DST audio is in double transfer rate.

0 = DST audio is in normal transfer rate.

LAYOUT — (Read Only) The LAYOUT bit extracted from HDMI audio packet.

1 = LAYOUT bit is 1 indicating 4 audio streams are being received.

0 = LAYOUT bit is 0 indicating 1 audio stream is being received.

### 4.3.1.6 Status Register 1 (Word Address = \$3D, Byte 0)

#### Table 4-8 Status Register 1

| bit | 7       | 6        | 5 | 4    | 3    | 2 | 1 | 0 |

|-----|---------|----------|---|------|------|---|---|---|

| R   | LINK_ON | DE_VALID | - | A_UF | A_OF | - | - | - |

| W   |         |          |   |      |      |   |   |   |

| -   | -       | -        | - | -    | -    | - | - | - |

- LINK\_ON (Read Only) Link On indicator for Primary RX. Only valid when HDMI is not in power down mode.

- 1 = Valid clock signal detected at Primary RX Port.

- 0 = No clock signal presents at Primary RX Port.

### DE\_VALID — (Read Only) DE Valid indicator for Primary RX.

- 1 = Valid DE signal detected at Primary RX Port.

- 0 = No valid DE signal presents at Primary RX Port.

A\_UF — (Read Only) Audio FIFO underflow flag. Set by audio logic. Cleared by read of Status Register 1.

1 = Audio FIFO underflow detected.

0 = Normal

A\_OF — (Read Only) Audio FIFO overflow flag. Set by audio logic. Cleared by read of Status Register 1.

- 1 = Audio FIFO overflow detected.

- 0 = Normal

### 4.3.1.7 SPDIF Channel Status Register (Word Address = \$3E)

The first 40 bits of the SPDIF Channel Status code (referred to as CS[39:0] with CS[0] being the first bit) are extracted from audio packets and put in this register set. CS[7:0] is stored in Byte-0[7:0], CS[15:8] is stored in Byte-1[7;0], CS[23:16] is stored in Byte-2[7:0], CS[31:24] is stored in Byte-3[7:0] and CS[39:32] is stored in Byte-4[7:0].

Most of the bits in this register set is Read Only except CS[2] and CS[15:8] which are writable. If CS\_OW\_EN bit is set, the written bits will replace the extracted bits and appear in SPDIF output.

Refer to IEC60958 specification for the detailed description of each bit. The following table shows the bit definition for Consumer Use Application.

| Word<br>Address | Byte # |   | bit7               | bit6              | bit5 | bit4 | bit3                 | bit2           | bit1 | bit0    |  |

|-----------------|--------|---|--------------------|-------------------|------|------|----------------------|----------------|------|---------|--|

|                 | 0      |   | MODE               | MODE[1:0] PRE[2:0 |      |      |                      | COPY           | PCM  | PRO = 0 |  |

|                 | 1      |   |                    | CAT_CODE[7:0]     |      |      |                      |                |      |         |  |

| 0x3E            | 2      | R | CH_NUM[3:0]        |                   |      |      | SRC_NUM[3:0]         |                |      |         |  |

|                 | 3      |   | RS                 | RSVD CLK_ACC[1:0] |      |      |                      | SAMP_FREQ[3:0] |      |         |  |

|                 | 4      |   | ORG_SAMP_FREQ[3:0] |                   |      |      | SAMP_LEN[2:0] MAX_LE |                |      |         |  |

Table 4-9 SPDIF Channel Status Registers (Consumer Use)

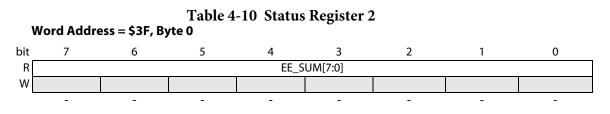

### 4.3.1.8 Status Register 2 (Word Address = \$3F, Byte 0)

EE\_SUM[7:0] — (Read Only) EE Check Sum.

When EE download is completed, the 8-bit EE Check Sum is put in this register by download logic.

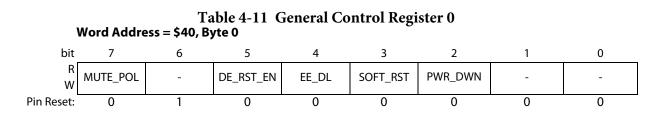

#### 4.3.1.9 General Control Register 0 (Word Address = \$40, Byte 0)

MUTE\_POL — A\_MUTE output polarity control

- 1 = A\_MUTE pin output is active low. A low level indicate mute.

- $0 = A_MUTE$  pin output is active high. A high level indicate mute.

DE\_RST\_EN — Enable invalid DE to reset HDCP

1 = Allow HDCP logic to be reset when invalid DE is detected. HDCP will start from non-authed and non-encrypted state after this reset.

0 = Normal.

EE\_DL — Write 1 followed by write 0 will trigger HDCP key downloading from EE.

The HDCP engine has to be reset by asserting the RX\_HDCP\_RST and RX\_RI\_RST control bits in REPEATER section before the HDCP Key re-download process is triggered.

SOFT\_RST — Soft Reset

1 = Reset all the HDMI and HDCP logic except IIC registers.

0 = Normal.

PWR\_DWN — Power Down

1 = HDMI is in Power Down mode. HDMI and HDCP logic are reset except IIC registers

0 = Normal.

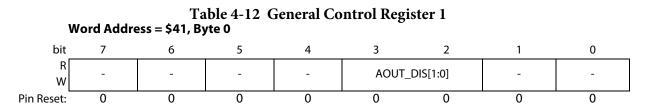

### 4.3.1.10 General Control Register 1 (Word Address = \$41, Byte 0)

AOUT\_DIS[1:0] — Audio Output Disable mode

- 00 = MCLK, IIS\_SCK, IIS\_SD0, IIS\_WS and SPDIF pins are normal outputs.

- 01 = IIS\_SCK, IIS\_SD0, IIS\_WS pins are put in tri-state. MCLK and SPDIF pins are normal output.

- 10 = SPDIF pin is put in tri-state with weak pull-down. MCLK, IIS\_SCK, IIS\_SD0, IIS\_SD1,

- IIS\_SD2, IIS\_SD3, IIS\_WS pins are normal output.

- 11 = MCLK, IIS\_SCK, IIS\_SD0, IIS\_SD1, IIS\_SD2, IIS\_SD3, IIS\_WS and SPDIF pins are all put in tri-state with weak pull-down.

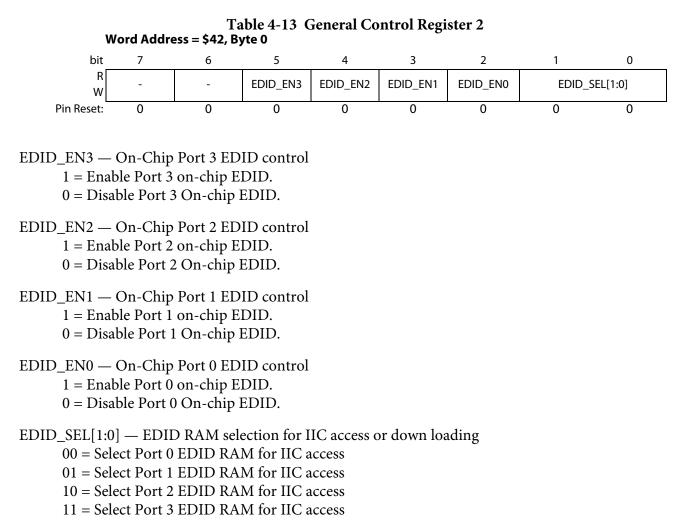

#### 4.3.1.11 General Control Register 2 (Word Address = \$42, Byte 0)

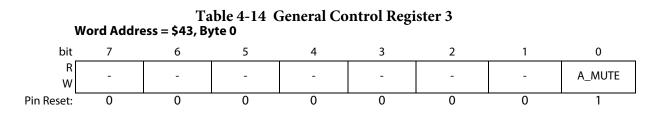

#### 4.3.1.12 General Control Register 3 (Word Address = \$43, Byte 0)

#### A\_MUTE — Audio Mute Control

1 = Audio is mute

0 = Normal

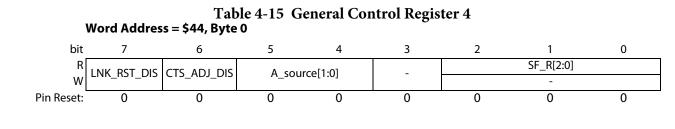

### 4.3.1.13 General Control Register 4 (Word Address = \$44, Byte 0)

$LINK\_RST\_DIS - Disable \ HDCP \ reset \ by \ link-off \ condition$

1 = HDCP is not reset by link-off condition

0 = HDCP is reset by link-off condition

CTS\_ADJ\_DIS — Disable CTS auto adjustment

1 = CTS is not adjusted

0 = CTS is auto adjusted to prevent FIFO overflow or underflow

A\_source — Audio Source Selection

00 = Select audio source from Standard Audio Sample Packets

01 = Select audio source from One Bit Audio Sample Packets

10 = Select audio source from High Bit Rate Audio Sample Packets

11 = Reserved

SF\_R[2:0] — (Read Only) Audio Sampling Frequency information derived from Audio Clock Regeneration Packet while the X\_IN frequency is 18.432MHz

000 = 32 KHz 001 = 44.1 KHz 010 = 48 KHz 011 = 88.2 KHz 100 = 96 KHz 101 = 176.4 KHz 110 = 192 KHz 111 = 768 KHz

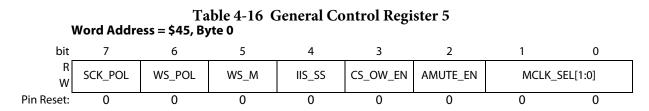

### 4.3.1.14 General Control Register 5 (Word Address = \$45, Byte 0)

### SCK\_POL — IIS\_SCK output polarity

1 = Inverse from IIS standard.

0 = IIS standard.

WS\_POL — IIS\_WS output polarity

- 1 = Inverse from IIS standard.

- 0 = IIS standard.

WS\_M — IIS\_WS output timing mode

- 1 = IIS\_WS is one clock delayed compared with standard IIS timing.

- 0 = IIS standard.

- IIS\_SS IIS sample size

1 = IIS outputs 32 bits sample size.

0 = IIS outputs 16 bits sample size.

CS\_OW\_EN — Channel Status Over Write Enable

1 = Enable SPDIF Channel Status Over Write.

0 = Disable SPDIF Channel Status Over Write.

AMUTE\_EN — Audio mute enable

1 = Enable on-chip audio mute logic.

0 = Disable on-chip audio mute logic. Audio mute shall be performed in external Audio DAC.

MCLK\_SEL[1:0] — MCLK Selection

These 2 bits select audio system clock (MCLK) frequency.

00 = MCLK frequency is 128 times of audio sampling frequency

01 = MCLK frequency is 256 times of audio sampling frequency. Not valid for HBR Audio.

10 = MCLK frequency is 384 times of audio sampling frequency. Not valid for HBR Audio.

11 = MCLK frequency is 512 times of audio sampling frequency. Not valid for HBR Audio.

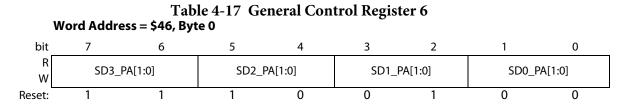

#### 4.3.1.15 General Control Register 6 (Word Address = \$46, Byte 0)

SD3\_PA[1:0] — Audio Stream assignment for IIS\_SD3 output or DSD3(R/L) output

00 =Output Audio Stream 0

- 01 = Output Audio Stream 1

- 10 = Output Audio Stream 2

11 = Output Audio Stream 3

## SD2\_PA[1:0] — Audio Stream assignment for IIS\_SD2 output or DSD2(R/L) output

00 = Output Audio Stream 0

- 01 = Output Audio Stream 1

- 10 = Output Audio Stream 2

- 11 = Output Audio Stream 3

SD1\_PA[1:0] — Audio Stream assignment for IIS\_SD1 output or DSD1(R/L) output

- 00 = Output Audio Stream 0

- 01 = Output Audio Stream 1

- 10 = Output Audio Stream 2

- 11 = Output Audio Stream 3

SD0\_PA[1:0] — Audio Stream assignment for IIS\_SD0 output or DSD0(R/L) output

- 00 = Output Audio Stream 0

- 01 = Output Audio Stream 1

- 10 = Output Audio Stream 2

- 11 = Output Audio Stream 3

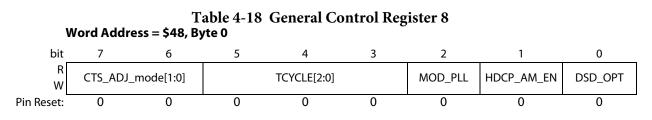

#### 4.3.1.16 General Control Register 8 (Word Address = \$48, Byte 0)

CTA\_ADJ\_mode[1:0] — A parameter to control audio tracking speed when CTS\_ADJ\_DIS is cleared. These bits shall be set to 0 for normal operation.

TCYCLE[2:0] — A parameter to control data judgement of HDMI sampling logic. These bit shall be set to a non-zero values for normal operation.

#### MOD\_PLL — ACR1 Option

- 1 = Configure ACR1 PLL to modulo type and increase reference frequency by 16 times to reduce jitter.

- 0 = ACR1 PLL reference frequency is determined by CTS/N parameter which sent from HDMI TX.

#### HDCP\_AM\_EN — HDCP AVMUTE Option

- 1 = HDCP will be forced not to do descryption when AVMUTE is set.

- 0 = HDCP will do descryption disregard of AVMUTE bit status. This is recommended in normal operation.

DSD\_OPT — DSD Audio Output Option

- 1 = DSD Audio output to DSP.

- 0 = DSD Audio output to DAC.

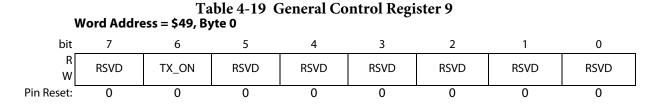

#### 4.3.1.17 General Control Register 9 (Word Address = \$49, Byte 0)

RSVD— This reserved bit shall be set to 0 for normal operation

TX\_ON— HDMI TX Output Port Enable Control

1 = Enable HDMI TX Output Port.

0 = Disable HDMI TX Output Port.

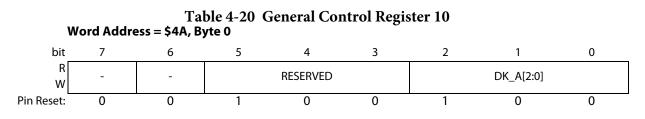

#### 4.3.1.18 General Control Register 10 (Word Address = \$4A, Byte 0)

DK\_A[2:0] — De-skewing Setting Control Bits

DK\_A[2:0] sets the clock to data riming for de-skew purpose for the HDMI transmitter of Output Port A. Eight steps can be selected and the time difference for each step is 200 ps. The default is 0 step.

000 = -4 step 001 = -3 step 010 = -2 step 011 = -1 step 100 = 0 step 101 = +1 step 110 = +2 step 111 = +3 step

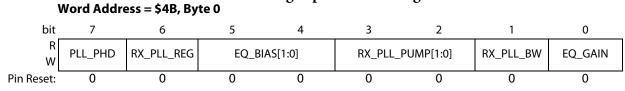

#### 4.3.1.19 Analog Input Control Register (Word Address = \$4B, Byte 0)

### Table 4-21 Analog Input Control Register

PLL\_PHD — Audio PLL Phase Detector Control 1 = fixed0 = variableRX\_PLL\_REG — RX PLL Regulator Control 1 = Enable0 = DisableEQ\_BIAS[1:0] — RX EQ Bias Current Control 00 = 150 uA01 = 125 uA10 = 100 uA11 = 80 uARX\_PLL\_PUMP[1:0] — RX PLL Charge Pump Current Control 00 = 10 uA01 = 20 uA10 = 40 uA11 = 40 uARX\_PLL\_BW — RX PLL Bandwidth Control 1 = 4.1MHz ~ 6.2MHz 0 = 4MHzEQ\_GAIN — RX EQ Gain Control  $1 = 6 \, dB$ 0 = 11 dB

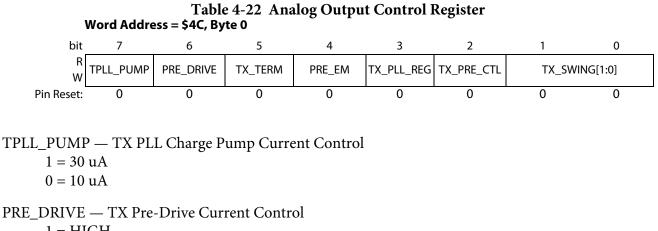

### 4.3.1.20 Analog Output Control Register (Word Address = \$4C, Byte 0)

1 = HIGH0 = LOW

TX\_TERM — TX on-chip 50  $\Omega$  Termination Select

1 = ON0 = OFF

- PRE\_EM TX Pre-Emphasis Strength Control

- 1 = High

- 0 = Low

- TX\_PLL\_REG TX PLL Regulator Control

- 1 = Enable

- 0 = Disable

- TX\_PRE\_CTL TX Output Pre-emphasis On/Off Control

- 1 = TX Output Pre-emphasis is enabled

- 0 = TX Output Pre-emphasis is disabled

TX\_SWING[1:0] — TX Output Swing Control

- 00 = 100%

- 01 = 94%

- 10 = 88%

- 11 = 81%

#### 4.3.1.21 EDID Data Register (Word Address = \$FF, Byte 0~255)

Word Address from \$FF is used for downloading the EDID data to the on-chip EDID RAM selected by EDID\_SEL[1:0]. The 256 data bytes in this register set correspond to the 256 byte EDID data.

# 4.4 Repeater Control/Status Registers

The following table shows all the control/Status registers of the Repeater:

| Addr | R/W | Bit7        | Bit6      | Bit5    | Bit4      | Bit3    | Bit2      | Bit1       | Bit0        | RESET |  |  |  |  |

|------|-----|-------------|-----------|---------|-----------|---------|-----------|------------|-------------|-------|--|--|--|--|

| \$07 | R/W | RX_LINK_ON  | RX_DE_ON  | RX_HDMI | RX_ENC_ON | -       | -         | RSVD       | RSVD        | 02h   |  |  |  |  |

| \$08 | R/W | TX_MUTE     | RX_VSYNC  | -       | -         | -       | -         | TX_ENC_OPT | -           | 01h   |  |  |  |  |

| \$09 | R   | -           | -         | -       | -         | -       | TX_RSEN   | -          | -           | 00h   |  |  |  |  |

| \$0A | W   | -           | -         | -       | -         | -       | RX_RI_RST | RX_DDC_DIS | RX_HDCP_RST | 00h   |  |  |  |  |

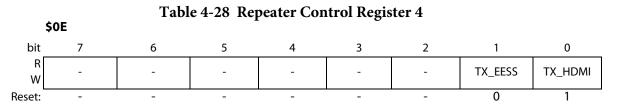

| \$0E | R/W | -           | -         | -       | -         | -       | -         | TX_EESS    | TX_HDMI     | 01h   |  |  |  |  |

| \$0F | R/W | TX_AKSV_RDY | TX_ENC_ON | -       | TX_RPTR   | -       | -         | TX_RI_RDY  | TX_ENC_EN   | 00h   |  |  |  |  |

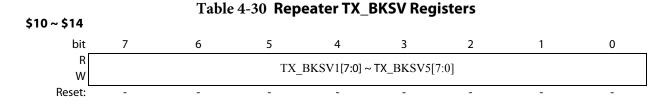

| \$10 | R/W |             | TX_BKSV_1 |         |           |         |           |            |             |       |  |  |  |  |

| \$11 | R/W |             |           |         | ТХ        | _BKSV_2 |           |            |             | XXh   |  |  |  |  |

| \$12 | R/W |             | TX_BKSV_3 |         |           |         |           |            |             |       |  |  |  |  |

| \$13 | R/W |             | TX_BKSV_4 |         |           |         |           |            |             |       |  |  |  |  |

| \$14 | R/W |             | TX_BKSV_5 |         |           |         |           |            |             |       |  |  |  |  |

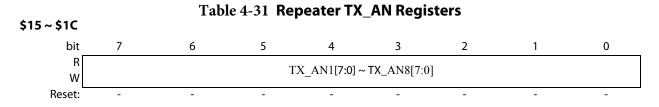

| \$15 | R/W |             | TX_AN_1   |         |           |         |           |            |             |       |  |  |  |  |

| \$16 | R/W |             | TX_AN_2   |         |           |         |           |            |             |       |  |  |  |  |

| \$17 | R/W |             |           |         | T         | X_AN_3  |           |            |             | XXh   |  |  |  |  |

| \$18 | R/W |             |           |         | T         | X_AN_4  |           |            |             | XXh   |  |  |  |  |

| \$19 | R/W |             |           |         | T         | X_AN_5  |           |            |             | XXh   |  |  |  |  |

| \$1A | R/W |             |           |         | T         | X_AN_6  |           |            |             | XXh   |  |  |  |  |

| \$1B | R/W |             |           |         | T         | X_AN_7  |           |            |             | XXh   |  |  |  |  |

| \$1C | R/W |             |           |         | T         | X_AN_8  |           |            |             | XXh   |  |  |  |  |

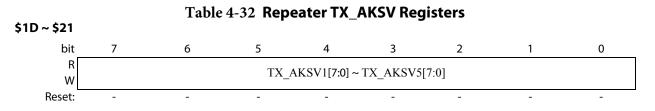

| \$1D | R   |             |           |         | TX        | _AKSV_1 |           |            |             | XXh   |  |  |  |  |

| \$1E | R   |             |           |         | TX        | _AKSV_2 |           |            |             | XXh   |  |  |  |  |

| \$1F | R   |             |           |         | TX        | _AKSV_3 |           |            |             | XXh   |  |  |  |  |

| \$20 | R   |             |           |         | TX        | _AKSV_4 |           |            |             | XXh   |  |  |  |  |

| \$21 | R   |             |           |         | TX        | _AKSV_5 |           |            |             | XXh   |  |  |  |  |

| \$22 | R   |             |           |         | Т         | X_RI_1  |           |            |             | XXh   |  |  |  |  |

| \$23 | R   |             |           |         | Т         | 'X_RI_2 |           |            |             | XXh   |  |  |  |  |

| \$25 | R   |             |           |         | T         | X_M0_1  |           |            |             | XXh   |  |  |  |  |

### Table 4-23 Repeater Control/Status Registers

| \$26 | R | TX_M0_2          | XXh   |  |  |  |  |  |  |  |  |

|------|---|------------------|-------|--|--|--|--|--|--|--|--|

| \$27 | R | TX_M0_3          | XXh   |  |  |  |  |  |  |  |  |

| \$28 | R | TX_M0_4          | XXh   |  |  |  |  |  |  |  |  |

| \$29 | R | TX_M0_5          | XXh   |  |  |  |  |  |  |  |  |

| \$2A | R | TX_M0_6          | XXh   |  |  |  |  |  |  |  |  |

| \$2B | R | TX_M0_7          | XXh   |  |  |  |  |  |  |  |  |

| \$2C | R | TX_M0_8          | XXh   |  |  |  |  |  |  |  |  |

| \$40 | R | RX_M0_RD         | Y XXh |  |  |  |  |  |  |  |  |

| \$41 | R | RX_M0_1          |       |  |  |  |  |  |  |  |  |

| \$42 | R | RX_M0_2          | XXh   |  |  |  |  |  |  |  |  |

| \$43 | R | RX_M0_3          | XXh   |  |  |  |  |  |  |  |  |

| \$44 | R | RX_M0_4          | XXh   |  |  |  |  |  |  |  |  |

| \$45 | R | RX_M0_5          | XXh   |  |  |  |  |  |  |  |  |

| \$46 | R | RX_M0_6          | XXh   |  |  |  |  |  |  |  |  |

| \$47 | R | RX_M0_7          | XXh   |  |  |  |  |  |  |  |  |

| \$48 | R | RX_M0_8          | XXh   |  |  |  |  |  |  |  |  |

| \$50 | W | RX_Bcaps         | 91h   |  |  |  |  |  |  |  |  |

| \$51 | w | RX_Bstatus[7:0]  | 00h   |  |  |  |  |  |  |  |  |

| \$52 | w | RX_Bstatus[11:8] | 00h   |  |  |  |  |  |  |  |  |

| \$60 | W | RX_SHA-1_HASH_0  | XXh   |  |  |  |  |  |  |  |  |

| \$61 | W | RX_SHA-1_HASH_1  | XXh   |  |  |  |  |  |  |  |  |

| \$62 | w | RX_SHA-1_HASH_2  | XXh   |  |  |  |  |  |  |  |  |

| \$63 | W | RX_SHA-1_HASH_3  | XXh   |  |  |  |  |  |  |  |  |

| \$64 | W | RX_SHA-1_HASH_4  | XXh   |  |  |  |  |  |  |  |  |

| \$65 | W | RX_SHA-1_HASH_5  | XXh   |  |  |  |  |  |  |  |  |

| \$66 | W | RX_SHA-1_HASH_6  | XXh   |  |  |  |  |  |  |  |  |

| \$67 | W | RX_SHA-1_HASH_7  | XXh   |  |  |  |  |  |  |  |  |

| \$68 | W | RX_SHA-1_HASH_8  | XXh   |  |  |  |  |  |  |  |  |

| \$69 | W | RX_SHA-1_HASH_9  | XXh   |  |  |  |  |  |  |  |  |

| \$6A | W | RX_SHA-1_HASH_10 | XXh   |  |  |  |  |  |  |  |  |

| \$6B | W | RX_SHA-1_HASH_11 | XXh   |  |  |  |  |  |  |  |  |

| \$6C | W | RX_SHA-1_HASH_12 | XXh   |  |  |  |  |  |  |  |  |

| \$6D | w | RX_SHA-1_HASH_13 | XXh   |  |  |  |  |  |  |  |  |

| \$6E           | W | RX_SHA-1_HASH_14 | XXh |

|----------------|---|------------------|-----|

| \$6F           | w | RX_SHA-1_HASH_15 | XXh |

| \$70           | W | RX_SHA-1_HASH_16 | XXh |

| \$71           | W | RX_SHA-1_HASH_17 | XXh |

| \$72           | W | RX_SHA-1_HASH_18 | XXh |

| \$73           | W | RX_SHA-1_HASH_19 | XXh |

| \$80 ~<br>\$A7 | W | RX_KSV_FIFOs     | XXh |

## 4.4.1 Register Descriptions

**\$07**

Detailed usage of these IIC registers is described in the following section.

#### 4.4.1.1 Repeater Control Register 0

#### Table 4-24 Repeater Control Register 0

| bit    | 7          | 6        | 5       | 4         | 3 | 2 | 1    | 0    |

|--------|------------|----------|---------|-----------|---|---|------|------|

| R      | RX_LINK_ON | RX_DE_ON | RX_HDMI | RX_ENC_ON | - | - | RSVD | RSVD |

| W      | -          | -        | -       | -         |   |   | NSVD | NOVE |

| Reset: | -          | -        | -       | -         | - | - | 0    | 0    |

#### RX\_LINK\_ON — Receiver Link On

This bit indicates whether a valid signal appears at the clock input of the RX. This bit is valid only when the RX is active (powered on and selected as output source).

1 = Clock presents at the input of the receiver port

0 = No clock is detected at the input of the receiver port

#### RX\_DE\_ON — Receiver DE On

This bit indicates whether DE signal is toggling at the RX. This bit is valid only when the RX is active (powered on and selected as output source).

1 = DE signal is toggling at the receiver port

0 = DE signal is not toggling at the receiver port

#### RX\_HDMI — Receiver HDMI signal

This bit indicates whether the RX is receiving DVI or HDMI signal

1 = HDMI

0 = DVI

RX\_ENC\_ON — Receiver Decryption On

This bit indicates whether the HDCP decryption is active at the RX.

1 = HDCP decryption at the receiver port is active

0 = HDCP decryption at the receiver port is not active

RSVD— This reserved bit shall be set to 0 for normal operation

#### 4.4.1.2 Repeater Control Register 1

#### Table 4-25 Repeater Control Register 1

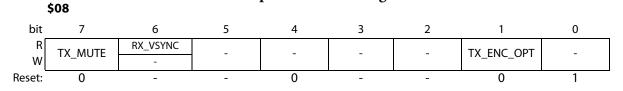

TX\_MUTE — Video Mute Transmitter

The bit is used to mute the video for the transmitter port.

1 = Transmitter port is video muted

0 = Normal

RX\_VSYNC — RX Vertical Sync Status Bit

The RX\_VSYNC bit gives the current status of the vertical sync signal for the RX.

TX\_ENC\_OPT — Transmitter Encryption Option

1 = Not affected by RX encryption status.

0 = Force not to encrypt if RX is not encrypted.

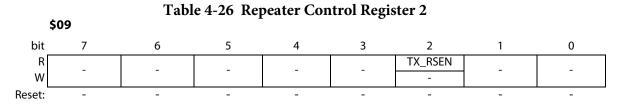

#### 4.4.1.3 Repeater Control Register 2

TX\_RSEN — Transmitter Analog Output Status Bit

The TX\_RSEN bit indicates the analog output status at the transmitter port.

1 = The transmitter analog outputs are connected to the receiver

0 = The transmitter analog outputs are disconnected

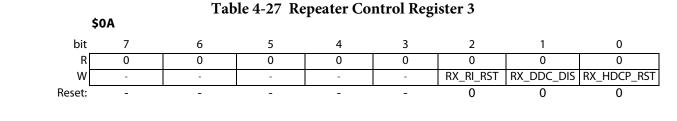

#### 4.4.1.4 Repeater Control Register 3

$RX_RI_RST$  — Reset HDCP Ri value for the RX 1 = Reset HDCP Ri value to 0 for the RX.

0 = Normal.

RX\_DDC\_DIS — Disable DDC ACK for the RX

1 = Disable DDC ACK for the RX.

0 = Normal.

RX\_HDCP\_RST — Reset HDCP for the RX

1 = Reset HDCP for the RX.

0 = Normal.

#### 4.4.1.5 Repeater Control Register 4

TX\_EESS — Enable Enhanced Encryption Signalling for the transmitter port

- 1 = Using Enhanced Encryption Signalling for the transmitter port.

- 0 = Using Original Encryption Signalling for the transmitter port. This is only valid if the transmitter is working in DVI mode (TX\_HDMI = 0).

TX\_HDMI — Set HDMI mode for the transmitter port

- 1 = Put the transmitter port working in HDMI mode. This is valid only if the receiver is receiving HDMI signal.

- 0 = Put the transmitter port working in DVI mode.

#### 4.4.1.6 Repeater Control Register 5

\$0F

| bit      | 7           | 6         | 5   | 4       | 3 | 2 | 1         | 0         |

|----------|-------------|-----------|-----|---------|---|---|-----------|-----------|

| R T<br>W | TX_AKSV_RDY | TX_ENC_ON | . – | TX_RPTR | - | - | TX_RI_RDY | TX_ENC_EN |

|          | -           | -         | -   | 0       | - | - | -         | 0         |

#### Table 4-29 Repeater Control Register 5

TX\_AKSV\_RDY — Transmitter AKSV Ready

The TX\_AKSV\_RDY bit indicates whether the HDCP keys and AKSV has been successfully downloaded from external EE or not for the transmitter port. This bit is read only.

1 = HDCP keys and AKSV has been successfully downloaded from external EE. AKSV is ready for read.

0 = HDCP keys and AKSV downloading has not been completed. AKSV is not ready for read.

#### TX\_ENC\_ON — Transmitter HDCP Encryption On

The TX\_ENC\_ON bit indicates whether the HDCP encryption for the transmitter port is active or not. This bit is read only.

1 = HDCP encryption is active.

0 = HDCP encryption is not active.

TX\_RPTR — Transmit to Repeater

The TX\_RPTR bit should be set if the receiver side which is connected to the transmitter port is a repeater. It should be cleared otherwise.

1 = The transmitter port is connecting to a repeater.

0 = The transmitter port is not connecting to a repeater.

TX\_RI\_RDY — Transmitter RI Ready

This bit indicates that the first Ri value is available for the transmitter port. This bit is read only.

1 = First Ri value is available for the transmitter port.

0 = First Ri value is not available for the transmitter port.

TX\_ENC\_EN — Transmitter ENC Enable

1 = Enable HDCP encryption for the transmitter port.

0 = Disable HDCP encryption the transmitter port.

#### 4.4.1.7 Repeater TX\_BKSV Registers - TX\_BKSV\_1 ~ TX\_BKSV\_5

These 5 registers for the transmitter port should be programmed with receiver's Key Selection Vector. TX\_BKSV\_1 is the LSB and TX\_BKSV\_5 is the MSB. TX\_BKSV\_5 should be written last, as it triggers the authentication process.

#### 4.4.1.8 Repeater TX\_AN Registers - $TX_AN_1 \sim TX_AN_8$

These 8 registers for the transmitter port should be programmed with a 64-bit pseudo-random value before triggering the authentication process. TX\_AN\_1 is the LSB and TX\_AN\_8 is the MSB.

#### 4.4.1.9 Repeater TX\_AKSV Registers - TX\_AKSV\_1 ~ TX\_AKSV\_5

These 5 registers are read only which hold transmitter's Key Selection Vector for the transmitter port. TX\_AKSV\_1 is the LSB and TX\_AKSV\_5 is the MSB. All five bytes should be read from here and then written to the receiver. Byte 5 should be written last to the receiver, as it will trigger authentication there. These 5 registers should not be read until TX\_AKSV\_RDY bit is 1.

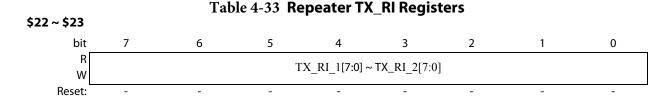

#### 4.4.1.10 Repeater TX\_RI Registers - TX\_RI\_1 ~ TX\_RI\_2

These 2 registers hold transmitter's Ri value for the transmitter port. They should be read and compared against the Ri value of the receiver to ensure that the encryption process on the transmitter and receiver is synchronized.

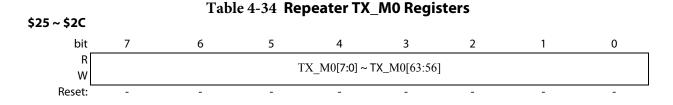

#### 4.4.1.11 Repeater TX\_M0 Registers

This 8 byte registers are used to store the first secret value TX\_M0 which calculated by the HDCP cipher function.

#### 4.4.1.12 Repeater RX\_M0\_RDY Register

\$40

#### Table 4-35 Repeater RX\_M0\_RDY Register

| bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0         |

|--------|---|---|---|---|---|---|---|-----------|

| R      | 0 | 0 | 0 | 0 | 0 | 0 | 0 | RX_M0_RDY |

| Reset: | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0         |

The RX\_M0\_RDY bit will be set to 1 while the last byte of AKSV is written and the HDCP engine completes the M0 calculation.

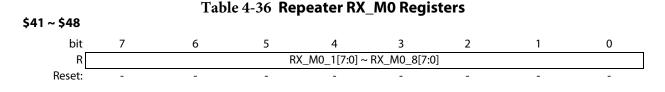

#### 4.4.1.13 Repeater RX\_M0 Registers (\$41 ~ \$48) - RX\_M0\_1 ~ RX\_M0\_8

These 8 registers are read only which hold receiver's M0 values which calculated from HDCP engine. These values can be read while the RX\_M0\_RDY bit is 1 and can be used for SHA calculation.

#### 4.4.1.14 Repeater RX\_Bcaps Register

| \$50 |        | Table 4-37    Repeater RX_Bcaps Register |          |          |      |      |      |             |             |  |  |  |  |

|------|--------|------------------------------------------|----------|----------|------|------|------|-------------|-------------|--|--|--|--|

|      | bit    | 7                                        | 6        | 5        | 4    | 3    | 2    | 1           | 0           |  |  |  |  |

|      | W      | HDMI_CAP                                 | REPEATER | FIFO_RDY | FAST | RSVD | RSVD | 1.1_FEATURE | FAST_REAUTH |  |  |  |  |

|      | Reset: | 1                                        | 0        | 0        | 1    | 0    | 0    | 0           | 1           |  |  |  |  |

This register is write only. The value writes to this register can be read by the upstream source through the DDC link while the HDCP is invoked.

HDMI\_CAP — HDMI Reserved Bit in HDCP Bcaps register

Value written into this bit will reflect to the HDCP Bcaps register, bit 7, HDMI\_RESERVED bit. Use of this bit is reserved. HDCP receivers not capable of supporting HDMI must clear this bit to 0.

#### REPEATER — REPEATER Bit in HDCP Bcaps register

Value written into this bit will reflect to the HDCP Bcaps register, bit 6, REPEATER bit.

FIFO\_RDY — READY Bit in HDCP Bcaps register

Value written into this bit will reflect to the HDCP Bcaps register, bit 5, READY bit.

FAST — FAST Bit in HDCP Bcaps register

Value written into this bit will reflect to the HDCP Bcaps register, bit 4, FAST bit.

1.1\_FEATURE — 1.1\_FEATURE Bit in HDCP Bcaps register

Value written into this bit will reflect to the HDCP Bcaps register, bit 1, 1.1\_FEATURE bit. This bit shall set to 0 always.

FAST\_REAUTH — FAST\_REAUTHENTICATION Bit in HDCP Bcaps register

Value written into this bit will reflect to the HDCP Bcaps register, bit 0, FAST\_REAUTHENTICATION bit.

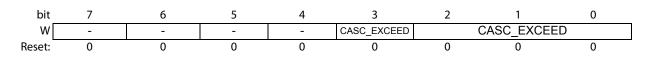

### 4.4.1.15 Repeater RX\_Bstatus Registers (\$51 ~ \$52)

Table 4-39 Repeater RX\_Bstatus (MSB, [15:8]) Register

These 2 bytes registers are write only. The value writes to this register can be read by the upstream source through the DDC link while the HDCP is invoked.

DEV\_EXCEED — MAX\_DEVS\_EXCEEDED Bit in HDCP Bstatus register

Value written into this bit will reflect to the HDCP Bstatus register, bit 7, MAX\_DEVS\_EXCEEDED bit.

DEVICE\_COUNT[6:0] — DEVICE\_COUNT Bits in HDCP Bstatus register

Value written into this bit will reflect to the HDCP Bstatus register, bit 6 ~ bit 0, DEVICE\_COUNT[6:0] bit.

CASC EXCEED --- MAX CASCADE EXCEEDED Bit in HDCP Bstatus register

Value written into this bit will reflect to the HDCP Bstatus register, bit 11, MAX\_CASCADE\_EXCEEDED bit.

DEPTH[2:0] — DEPTH Bits in HDCP Bstatus register

\$52

Value written into this bit will reflect to the HDCP Bstatus register, bit 10 ~ bit 8, DEPTH[2:0] bit.

### 4.4.1.16 Repeater RX\_SHA-1\_HASH Registers (\$60 ~ \$73)

These 20-bytes registers are write only. The value writes to this register can be read by the upstream source through the DDC link while the HDCP is invoked.

| Table 4-40 Re | peater HDCP | SHA-1 Hash | Value Registers |

|---------------|-------------|------------|-----------------|

|---------------|-------------|------------|-----------------|

| Address | bit7 | bit6            | bit5 | bit4    | bit3    | bit2 | bit1 | bit0 | reset |  |  |  |

|---------|------|-----------------|------|---------|---------|------|------|------|-------|--|--|--|

| 0x60    |      | RX_SHA-1_HASH_0 |      |         |         |      |      |      |       |  |  |  |

| 0x61    |      | RX_SHA-1_HASH_1 |      |         |         |      |      |      |       |  |  |  |

| 0x62    |      | RX_SHA-1_HASH_2 |      |         |         |      |      |      |       |  |  |  |

| 0x63    |      |                 | R    | X_SHA-´ | I_HASH_ | _3   |      |      | xxh   |  |  |  |

| 0x64    |      |                 | R    | X_SHA-´ | I_HASH_ | _4   |      |      | xxh   |  |  |  |

| 0x65    |      |                 | R    | X_SHA-´ | I_HASH_ | _5   |      |      | xxh   |  |  |  |

| 0x66    |      |                 | R    | X_SHA-´ | L_HASH_ | _6   |      |      | xxh   |  |  |  |

| 0x67    |      |                 | R    | X_SHA-´ | I_HASH_ | 7    |      |      | xxh   |  |  |  |

| 0x68    |      |                 | R    | X_SHA-´ | I_HASH_ | _8   |      |      | xxh   |  |  |  |

| 0x69    |      |                 | R    | X_SHA-´ | I_HASH_ | 9    |      |      | xxh   |  |  |  |

| 0x6A    |      |                 | RX   | (_SHA-1 | _HASH_  | 10   |      |      | xxh   |  |  |  |

| 0x6B    |      |                 | RX   | (_SHA-1 | _HASH_  | 11   |      |      | xxh   |  |  |  |

| 0x6C    |      |                 | RX   | (_SHA-1 | _HASH_  | 12   |      |      | xxh   |  |  |  |

| Address | bit7             | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | reset |

|---------|------------------|------|------|------|------|------|------|------|-------|

| 0x6D    | RX_SHA-1_HASH_13 |      |      |      |      |      |      |      |       |

| 0x6E    | RX_SHA-1_HASH_14 |      |      |      |      |      |      |      | xxh   |

| 0x6F    | RX_SHA-1_HASH_15 |      |      |      |      |      |      |      | xxh   |

| 0x70    | RX_SHA-1_HASH_16 |      |      |      |      |      |      |      | xxh   |

| 0x71    | RX_SHA-1_HASH_17 |      |      |      |      |      |      |      | xxh   |

| 0x72    | RX_SHA-1_HASH_18 |      |      |      |      |      |      |      | xxh   |

| 0x73    | RX_SHA-1_HASH_19 |      |      |      |      |      |      |      | xxh   |

Table 4-40 Repeater HDCP SHA-1 Hash Value Registers

### 4.4.1.17 Repeater RX\_KSV\_FIFO Registers (\$80 ~ \$A7)

These 40-bytes registers are write only. The value writes to this register can be read by the upstream source through the DDC link while the HDCP is invoked. The MCU shall write 0x00 to these registers to be the default values. Each KSV list contains 5 bytes registers and the register structure is shown below.

Table 4-41 Repeater KSV\_FIFO Registers

| Address          | bit7        | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | reset |

|------------------|-------------|------|------|------|------|------|------|------|-------|

| 0x80 + 5 * (X-1) | KSVx[7:0]   |      |      |      |      |      |      |      |       |

| 0x81 + 5 * (X-1) | KSVx[15:8]  |      |      |      |      |      |      |      |       |

| 0x82 + 5 * (X-1) | KSVx[23:16] |      |      |      |      |      |      |      |       |

| 0x83 + 5 * (X-1) | KSVx[31:24] |      |      |      |      |      |      |      |       |

| 0x84 + 5 * (X-1) | KSVx[39:32] |      |      |      |      |      |      |      | xxh   |

NOTE: X = downstream device count

# Section 5 Package

User Guide — PACKAGE