# HDMI 1.4 Repeater with Audio, VGA and Scaled LVDS Outputs

**EP94Z3(K)**

Data Sheet V0.4

Revised Date: Sep. 27, 2013

Original Release Date: Aug. 29, 2011

# **Explore**

Explore reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Explore does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Explore products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Explore product could create a situation where personal injury or death may occur. Should Buyer purchase or use Explore products for any such unintended or unauthorized application, Buyer shall indemnify and hold Explore and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Explore was negligent regarding the design or manufacture of the part.

# **Revision History**

| Version<br>Number | Revision<br>Date | Author    | Description of Changes                                                         |

|-------------------|------------------|-----------|--------------------------------------------------------------------------------|

| 0.1               | Nov/03/2011      | Ether Lai | Initial Version                                                                |

| 0.2               | Apr/17/2012      | Ether Lai | Revise the Electrical Characteristics;<br>Add the optional part number EP94Z3K |

| 0.3               | May/03/2013      | Ken Chen  | Revised the MHL version to 2.0;                                                |

| 0.4               | Sep/27/2013      | Ken Chen  | Remove the typo, EXT_RES.                                                      |

### **Section 1 Introduction**

#### 1.1 Overview

EP94Z3(K) is an HDMI 1.4 Repeater with Audio, VGA and Scaled LVDS outputs. The chip supports 1 HDMI/MHL RX port and 1 HDMI TX port with repeater function. The chip also supports decoded Audio, VGA and scaled LVDS outputs.

With the Scaled LVDS output, the chip provides a converted video output which can be in a different resolution from that of the HDMI input. The on-chip Scaler is able to scale the input video up or down to any resolution within the range of 0.5X to 2X in both Horizontal and Vertical direction. This is adequate for converting an EIA standard video to fit an LCD panel in different resolution.

The chip is compliant with HDMI 1.4 and supports SD/HD Audio and HD/3D Video up to 1080p. The chip also supports on-chip HDCP RX/TX engines and EDID RAM.

#### 1.2 Features

- On-chip HDMI/MHL Receiver which is compliant with HDMI 1.4b and MHL 2.0 specification

- On-chip HDMI Transmitter core which is compliant with HDMI 1.4b specification

- On-chip HDCP RX/TX Engine which is compliant with HDCP 1.4 specification

- On-chip Video Up/Down Scaler

- On-chip LVDS Transmitter supporting up to 150 Mhz pixel rate

- On-chip DAC supporting up to 150 Mhz pixel rate for VGA output port

- On-chip EDID RAM

- On-Chip HDCP Key (Available for EP94Z3K)

- On-chip Audio Decoder which support 8-channel IIS, S/PDIF and DSD audio outputs

- Support HDMI Repeater function

- Support YCC422 to YCC444 conversion

- Support YCC to RGB conversion in ITU-R BT.601 and 709 color space

- Support Separate Sync and/or SOG (Sync On Green) on VGA output

- Support LPCM, Compressed Surround Audio, HD (HBR) Audio and DSD audio

- Support audio soft mute

- Support SPDIF Channel Status extraction

- Register-programmable via slave IIC interface

- Low stand-by current (< 1mA) at power down mode

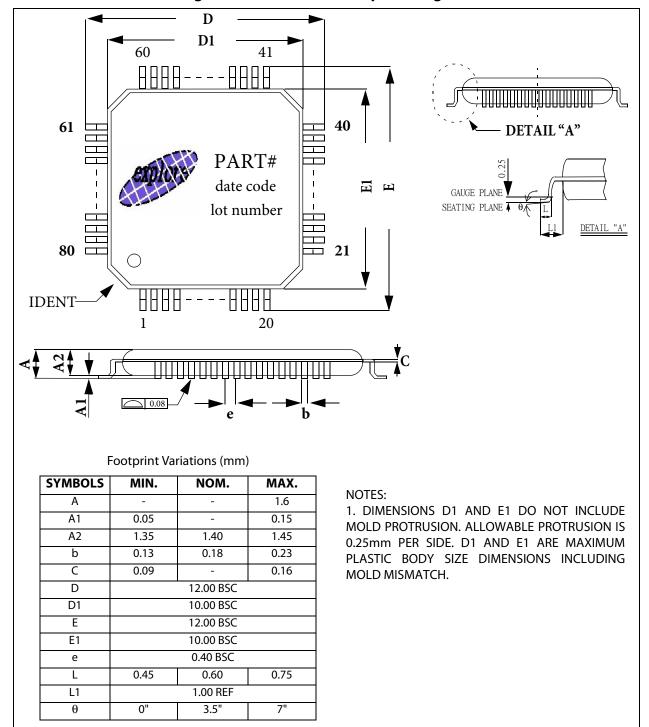

- 80-pin LQFP package

Data Sheet — EP94Z3(K)\_DS V0.4

# **Section 2 Overview**

# 2.1 Block Diagram

LT\_A+/-LT\_B+/-Video MCU\_SCL MCU\_SDA LT\_C+/-LT\_D+/-Scaler LT\_CLK+/-Video VGA\_R VGA\_G Decode Control Registers Video VGA\_B VGA\_HS VGA\_VS DAC RX0+/-HDMI RX1+/-HDMI TX /MHL TX0+/-RX2+/-HDCP RX HDCP TX TX1+/-Input RXC+/-DDC\_SDA DDC\_SCL CBUS Engine Engine TX2+/-Port TXC+/-**EDID** MCLK IIS IIS\_WS IIS\_SD\* **Audio Out** Audio Decode **SPDIF** ➤ SPDIF **Audio Out** PLL

Figure 2-1 Block Diagram

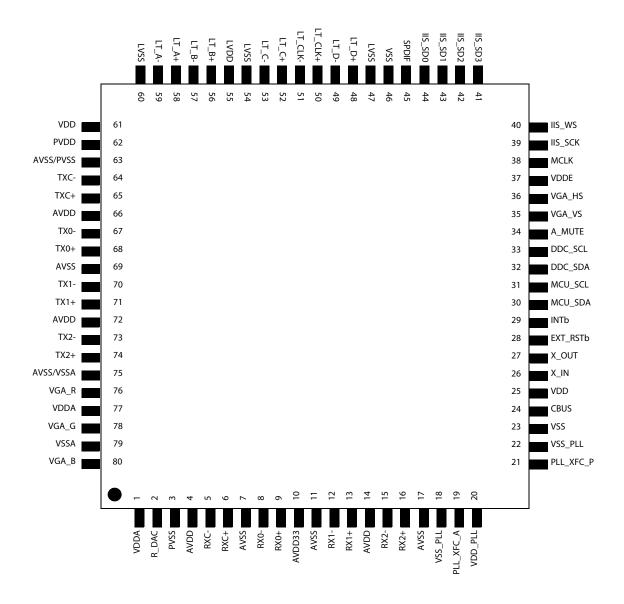

# 2.2 Pin Diagram

Figure 2-2 Pin Diagram

# 2.3 Pin Description

Unless otherwise stated, unused input pins must be tied to ground, and unused output pins left open.

**Table 2-1 HDMI/MHL Input Port**

| Name    | In/Out | Description                                     |

|---------|--------|-------------------------------------------------|

| RXC-    | IN     | HDMI Receiver Differential Clock Input Pair     |

| RXC+    | IN     | HDMI Receiver Differential Clock Input Pair     |

| RX0-    | IN     | HDMI/MHL Receiver Differential Data Input Pair1 |

| RX0+    | IN     | HDMI/MHL Receiver Differential Data Input Pair1 |

| RX1-    | IN     | HDMI Receiver Differential Data Input Pair1     |

| RX1+    | IN     | HDMI Receiver Differential Data Input Pair1     |

| RX2-    | IN     | HDMI Receiver Differential Data Input Pair2     |

| RX2+    | IN     | HDMI Receiver Differential Data Input Pair2     |

| DDC_SCL | IN     | IIC SCL signal for HDMI RX DDC Port             |

| DDC_SDA | Ю      | IIC SDA signal for HDMI RX DDC Port             |

| CBUS    | Ю      | CBUS signal for MHL RX Port                     |

**Table 2-2 LVDS Output Port**

| Name    | In/Out | Description                                    |

|---------|--------|------------------------------------------------|

| LT_CLK- | OUT    | Differential Clock Output Pair for LVDS Output |

| LT_CLK+ | OUT    | Differential Clock Output Pair for LVDS Output |

| LT_A-   | OUT    | Differential Data Output PairA for LVDS Output |

| LT_A+   | OUT    | Differential Data Output PairA for LVDS Output |

| LT_B-   | OUT    | Differential Data Output PairB for LVDS Output |

| LT_B+   | OUT    | Differential Data Output PairB for LVDS Output |

| LT_C-   | OUT    | Differential Data Output PairC for LVDS Output |

| LT_C+   | OUT    | Differential Data Output PairC for LVDS Output |

| LT_D-   | OUT    | Differential Data Output PairD for LVDS Output |

| LT_D+   | OUT    | Differential Data Output PairD for LVDS Output |

**Table 2-3 HDMI Output Port**

| Name | In/Out | Description                                    |

|------|--------|------------------------------------------------|

| TXC- | OUT    | Differential Clock Output Pair for HDMI Output |

| TXC+ | OUT    | Differential Clock Output Pair for HDMI Output |

| TX0- | OUT    | Differential Data Output Pair0 for HDMI Output |

| TX0+ | OUT    | Differential Data Output Pair0 for HDMI Output |

| TX1- | OUT    | Differential Data Output Pair1 for HDMI Output |

| TX1+ | OUT    | Differential Data Output Pair1 for HDMI Output |

| TX2- | OUT    | Differential Data Output Pair2 for HDMI Output |

| TX2+ | OUT    | Differential Data Output Pair2 for HDMI Output |

**Table 2-4 VGA Output Port**

| Name   | In/Out | Description                                                 |

|--------|--------|-------------------------------------------------------------|

| VGA_B  | OUT    | VGA Analogue Blue output                                    |

| VGA_G  | OUT    | VGA Analogue Green output                                   |

| VGA_R  | OUT    | VGA Analogue Red output                                     |

| R_DAC  | Analog | For connecting a resistor to VSSA to set DAC output current |

| VGA_VS | IN/OUT | Vertical Sync Output.                                       |

| VGA_HS | IN/OUT | Horizontal Sync Output.                                     |

## **Table 2-5 Audio Outputs**

| Name          | In/Out | Description                                                                                                                                                                                          |

|---------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCLK          | OUT    | System Clock output for audio DAC (128/256/384/512 * F <sub>Sampling_Clock</sub> . Connecting a pull-up (logic 1) or pull-down (logic 0) resistor at this pin defines bit 4 of the slave IIC Address |

| IIS_SCK       | OUT    | IIS SCK output for IIS audio port. Sampling clock output for DSD.                                                                                                                                    |

| IIS_WS/DSD2R  | OUT    | IIS WS output for all IIS audio ports. DSD audio output port 2 (Right Channel).                                                                                                                      |

| IIS_SD0/DSD0L | OUT    | IIS SD output for audio port 0 or HBR audio output. DSD audio output port 0 (Left Channel).                                                                                                          |

| IIS_SD1/DSD0R | OUT    | IIS SD output for audio port 1 or HBR audio output. DSD audio output port 0 (Right Channel).                                                                                                         |

| IIS_SD2/DSD1L | OUT    | IIS SD output for audio port 2 or HBR audio output. DSD audio output port 1 (Left Channel).                                                                                                          |

| IIS_SD3/DSD1R | OUT    | IIS SD output for audio port 3 or HBR audio output. DSD audio output port 1 (Right Channel).                                                                                                         |

| SPDIF/DSD2L   | OUT    | SPDIF output. DSD audio output port 2 (Left Channel).                                                                                                                                                |

| A_MUTE        | OUT    | Audio Mute Output                                                                                                                                                                                    |

### Table 2-6 Misc. Pins

| Name      | In/Out | Description                                                   |

|-----------|--------|---------------------------------------------------------------|

| MCU_SCL   | IN     | SCL signal for slave IIC port                                 |

| MCU_SDA   | Ю      | SDA signal for slave IIC port                                 |

| INTb      | OUT    | Interrupt output to MCU.                                      |

| EXT_RSTb  | IN     | External Reset input (Active Low) with internal weak pull-up. |

| X_IN      | Analog | External Crystal Input, 24 Mhz                                |

| X_OUT     | Analog | External Crystal Output, 24 Mhz                               |

| PLL_XFC_A | Analog | For connecting the R/C components to ground for on-chip PLL   |

| PLL_XFC_P | Analog | For connecting the R/C components to ground for on-chip PLL   |

#### **Table 2-7 Power Pins**

| Name    | In/Out | Description                        |

|---------|--------|------------------------------------|

| AVDD33  | PWR    | HDMI Termination Power (3.3V)      |

| AVDD    | PWR    | HDMI RX/TX Analog Power (1.8V)     |

| AVSS    | GND    | HDMI RX/TX Analog Ground           |

| PVDD    | PWR    | HDMI RX/TX PLL Analog Power (1.8V) |

| PVSS    | GND    | HDMI RX/TX PLL Analog Ground       |

| LVDD    | PWR    | LVDS Analog Power (3.3V)           |

| LVSS    | GND    | LVDS Analog Ground                 |

| VDDA    | PWR    | ADC Analog Power (1.8V)            |

| VSSA    | GND    | ADC Analog Ground                  |

| VDDE    | PWR    | I/O Logic Power (3.3V)             |

| VDD     | PWR    | Core Logic Power (1.8V)            |

| VSS     | GND    | Digital Ground                     |

| VDD_PLL | GND    | PLL VDD (1.8V)                     |

| VSS_PLL | GND    | PLL Ground                         |

# 2.4 Electrical Characteristics

### **Absolute Maximum Conditions**

| Symbol           | Parameter                                | Min  | Тур | Max              | Units |

|------------------|------------------------------------------|------|-----|------------------|-------|

| Vcc33            | 3.3V Supply Voltage                      | -0.3 |     | 4.0              | V     |

| Vcc18            | 1.8V Supply Voltage                      | -0.3 |     | 2.5              | V     |

| V <sub>I</sub>   | Input Voltage                            | -0.3 |     | $V_{cc33} + 0.3$ | V     |

| V <sub>O</sub>   | Output Voltage                           | -0.3 |     | $V_{cc33} + 0.3$ | V     |

| T <sub>J</sub>   | Junction Temperature                     |      |     | 125              | °C    |

| T <sub>STG</sub> | Storage Temperature                      | -40  |     | 125              | °C    |

| $\theta_{JA}$    | Thermal Resistance (Junction to Ambient) |      | 50  |                  | °C/W  |

| $\theta_{JC}$    | Thermal Resistance (Junction to Case)    |      | 11  |                  | °C/W  |

## **Normal Operating Conditions**

| Symbol           | Parameter                                | Min  | Тур | Max  | Units             |

|------------------|------------------------------------------|------|-----|------|-------------------|

| Vcc33            | 3.3V Supply Voltage                      | 3.14 | 3.3 | 3.6  | V                 |

| Vcc18            | 1.8V Supply Voltage                      | 1.71 | 1.8 | 1.98 | V                 |

| V <sub>CCN</sub> | Supply Voltage Noise <sup>1</sup>        | -0.3 |     | 100  | mV <sub>p-p</sub> |

| T <sub>A</sub>   | Ambient Temperature (with power applied) | 0    | 25  | 70   | °C                |

## DC Digital I/O Specifications (under normal operating conditions unless otherwise specified)

| Symbol          | Parameter                 | Conditions     | Min | Тур | Max | Units |

|-----------------|---------------------------|----------------|-----|-----|-----|-------|

| V <sub>IH</sub> | High-level Input Voltage  |                | 2.0 |     |     | V     |

| V <sub>IL</sub> | Low-level Input Voltage   |                |     |     | 0.8 | V     |

| V <sub>OH</sub> | High-level Output Voltage |                | 2.4 |     |     | V     |

| V <sub>OL</sub> | Low-level Output Voltage  |                |     |     | 0.4 | V     |

| I <sub>OL</sub> | Output Leakage Current    | High Impedance | -10 |     | 10  | uA    |

## CBUS I/O Specifications (under normal operating conditions unless otherwise specified)

| Symbol                                     | Parameter                      | Conditions     | Min | Тур | Max  | Units |

|--------------------------------------------|--------------------------------|----------------|-----|-----|------|-------|

| V <sub>IH_CBUS</sub>                       | CBUS High-level Input Voltage  |                | 1.0 |     |      | V     |

| V <sub>IL_CBUS</sub>                       | CBUS Low-level Input Voltage   |                |     |     | 0.6  | V     |

| V <sub>OH_CBUS</sub>                       | CBUS High-level Output Voltage | VDD = 1.8V     | 1.5 |     | 1.9  | V     |

| V <sub>OL_CBUS</sub>                       | CBUS Low-level Output Voltage  | 1 VDD - 1.6V   |     |     | 0.2  | V     |

| I <sub>IH_CBUS</sub> /I <sub>IL_CBUS</sub> | Input Leakage Current          | High Impedance | -1  |     | 1    | uA    |

| Z <sub>CBUS_SINK_DISCOVER</sub>            | CBUS Pull Down Resistance      | Discovery      | 800 |     | 1200 | Ω     |

| Z <sub>CBUS_SINK_ON</sub>                  | CBUS Pull Down Resistance      | Active         | 90K |     | 110K | Ω     |

## DC Analogue Specifications (under normal operating conditions unless otherwise specified)

| Symbol           | Parameter                                                                                          | Condition                    | าร                         | Min | Тур  | Max | Units |

|------------------|----------------------------------------------------------------------------------------------------|------------------------------|----------------------------|-----|------|-----|-------|

| V <sub>OD</sub>  | Differential Output Voltage<br>Single ended peak to peak amplitude                                 | $R_{LOAD} = 50 c$            | R <sub>LOAD</sub> = 50 ohm |     | 550  | 590 | mV    |

| V <sub>DOH</sub> | Differential High-level Output Voltage <sup>1</sup>                                                |                              |                            |     | AVCC |     | V     |

| I <sub>DOS</sub> | Differential Output Short Circuit Current                                                          | V <sub>OUT</sub> = 0V; TX_TE | RM bit is 0                |     |      | 5   | uA    |

|                  | Power-Down Current <sup>2</sup>                                                                    | 25°C Ambient                 | 3V3                        |     | 10   |     | uA    |

| I <sub>PD</sub>  |                                                                                                    |                              | 1V8                        |     | 30   |     | uA    |

|                  | Supply Current<br>(25°C Ambient, HDMI RX/TX are Active,<br>TX_TERM bit is 1)                       | 1080p 12-bits                | 3V3                        |     | 32   |     | mA    |

|                  |                                                                                                    |                              | 1V8                        |     | 380  |     | mA    |

|                  | Supply Current<br>(25°C Ambient, HDMI RX/TX, VGA and<br>LVDS TX are Active, TX_TERM bit is 1)      | 1080p 8 bits                 | 3V3                        |     | 56   |     | mA    |

|                  |                                                                                                    |                              | 1V8                        |     | 398  |     | mA    |

| I <sub>CCD</sub> |                                                                                                    | 720p 8 bits                  | 3V3                        |     | 56   |     | mA    |

|                  |                                                                                                    |                              | 1V8                        |     | 328  |     | mA    |

|                  | Supply Current<br>(25°C Ambient, MHL RX, HDMI TX, VGA<br>and LVDS TX are Active, TX_TERM bit is 1) | 720p, 60Hz, RGB444           | 3V3                        |     | 47   |     | mA    |

|                  |                                                                                                    |                              | 1V8                        |     | 243  |     | mA    |

<sup>1</sup> Guaranteed by design.

<sup>2</sup> Assumes all HDMI/DVI I/O ports are not connected and all digital inputs are silent.

#### HDMI/MHL Receiver AC Specifications (under normal operating conditions unless otherwise specified)

| Symbol            | Parameter                                                | Conditions | Min | Тур | Max | Units              |

|-------------------|----------------------------------------------------------|------------|-----|-----|-----|--------------------|

| T <sub>DPS</sub>  | Intra-Pair (+ to -) Differential Input Skew <sup>1</sup> |            |     |     | 0.4 | T <sub>bit</sub>   |

| T <sub>CCS</sub>  | Channel to Channel Differential Input Skew <sup>1</sup>  |            |     |     | 1.0 | T <sub>pixel</sub> |

| T <sub>IJIT</sub> | Differential Input Clock Jitter Tolerance <sup>2,3</sup> |            |     |     | 0.3 | T <sub>bit</sub>   |

| F <sub>CIP1</sub> | TMDS CLK Frequency (HDMI mode)                           |            | 25  |     | 225 | MHz                |

| F <sub>CIP2</sub> | Common Mode Input Frequency (MHL mode)                   |            | 25  |     | 75  | MHz                |

#### NOTES:

- 1. Guaranteed by design.

- 2. Jitter defines as per DVI 1.0 Specification, Section 4.6 Jitter Specification.

- 3. Jitter measured with Clock Recovery Unit as per DVI 1.0 Specification, Section 4.7 Electronic Measurement Procedures

#### HDMI Transmitter AC Specifications (under normal operating conditions unless otherwise specified)

| Symbol           | Parameter                                      | Conditions                                                                        | Min | Тур | Max | Units |

|------------------|------------------------------------------------|-----------------------------------------------------------------------------------|-----|-----|-----|-------|

| S <sub>LHT</sub> | Differential Swing Low-to-High Transition Time | $C_{LOAD} = 5pF,$ $R_{LOAD} = 50 \text{ ohm},$ $R_{EXT\_SWING} = 270 \text{ ohm}$ | 170 | 200 | 230 | ps    |

| S <sub>HLT</sub> | Differential Swing High-to-Low Transition Time | $C_{LOAD} = 5pF,$ $R_{LOAD} = 50 \text{ ohm},$ $R_{EXT\_SWING} = 270 \text{ ohm}$ | 170 | 200 | 230 | ps    |

#### I2S Audio AC Specifications (under normal operating conditions unless otherwise specified)

| Symbol             | Parameter                     | Conditions            | Min | Тур | Max | Units            |

|--------------------|-------------------------------|-----------------------|-----|-----|-----|------------------|

| T <sub>sck</sub>   | SCK Clock Period              | C <sub>L</sub> = 10pF |     | 1   |     | T <sub>sck</sub> |

| T <sub>sck_d</sub> | SCK Clock Duty Cycle          | C <sub>L</sub> = 10pF | 40% |     | 60% | T <sub>sck</sub> |

| T <sub>sck_h</sub> | SCK Clock High Time           | C <sub>L</sub> = 10pF | 40% |     | 60% | T <sub>sck</sub> |

| T <sub>sck_l</sub> | SCK Clock LOW Time            | C <sub>L</sub> = 10pF | 40% |     | 60% | T <sub>sck</sub> |

| T <sub>iis_s</sub> | SCK to SD and WS (Setup Time) | C <sub>L</sub> = 10pF | 40% |     | -   | T <sub>sck</sub> |

| T <sub>iis_h</sub> | SCK to SD and WS (Hold Time)  | C <sub>L</sub> = 10pF | 40% |     | -   | T <sub>sck</sub> |

#### SPDIF Audio AC Specifications (under normal operating conditions unless otherwise specified)

| Symbol | Parameter | Conditions | Min | Тур | Max | Units |  |

|--------|-----------|------------|-----|-----|-----|-------|--|

|--------|-----------|------------|-----|-----|-----|-------|--|

| T <sub>spdif</sub>   | SPDIF Cycle Time | C <sub>L</sub> = 10pF |     | 1 |      | UI |

|----------------------|------------------|-----------------------|-----|---|------|----|

| T <sub>spdif_d</sub> | SPDIF Duty Cycle | C <sub>L</sub> = 10pF | 90% |   | 110% | UI |

# LVDS Transmitter DC Specifications (under normal operating conditions unless otherwise specified)

| Symbol           | Parameter                                                     | Conditions                                          | Min   | Тур   | Max    | Units |

|------------------|---------------------------------------------------------------|-----------------------------------------------------|-------|-------|--------|-------|

| V                | Differential Output Voltage                                   | $R_L = 100 \Omega$ , Normal Swing (LVDS_SWING = 1)  | 250   | 350   | 450    | mV    |

| V <sub>OD</sub>  |                                                               | $R_L = 100 \Omega$ , Reduced Swing (LVDS_SWING = 0) | 100   | 200   | 300    |       |

| ΔV <sub>OD</sub> | Change in V <sub>OD</sub> between complimentary output states | $R_L = 100 \Omega$                                  |       |       | 35     | mV    |

| V <sub>OC</sub>  | Common Mode Voltage                                           |                                                     | 1.125 | 1.25  | 1.375  | V     |

| ΔV <sub>OC</sub> | Change in $V_{OC}$ between complimentary output states        |                                                     |       |       | 35     | mV    |

| I <sub>OS</sub>  | Output Short Circuit Current                                  | $V_{OUT} = 0V$ , $R_L = 100 \Omega$                 |       |       | -10    | mA    |

| l <sub>OZ</sub>  | Output Tri-State Current                                      | LVDS_ON = 0;                                        |       | +/- 1 | +/- 10 | uA    |

## 2.5 HBR Audio Output Format

HBR (True HD High Bit Rate) audio is output from IIS pins as shown in the following figure:

IIS\_WS  $(WS_POL = 0)$ IIS\_SD0 1st 16 bits 2nd16 bits 9th16 bits 10th 16 bits IIS\_SD1 3rd 16 bits 4th16 bits 11th 16 bits 12th16 bits IIS\_SD2 5th16 bits 13th 16 bits 6th 16 bits 14th16 bits IIS\_SD3 7th 16 bits 8th 16 bits 15th 16 bits 16th16 bits

Figure 2-3 HBR Audio Output Format

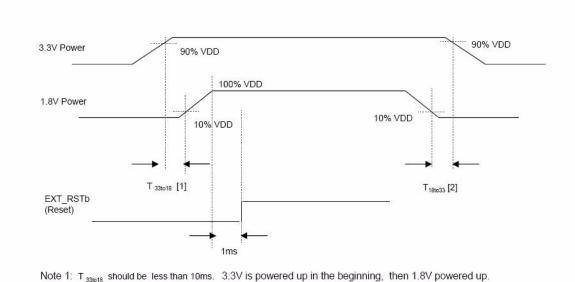

# 2.6 Power Up Sequence

--- Power up Sequence ---

Following figure shows the recommended power on sequence:

Explore Confidential Proprietary NON-DISCLOSURE AGREEMENT REQUIRED

Note 2: T18te33 should be less than 10ms. 1.8V is powered down in the beginning, then 3.3V powered down.

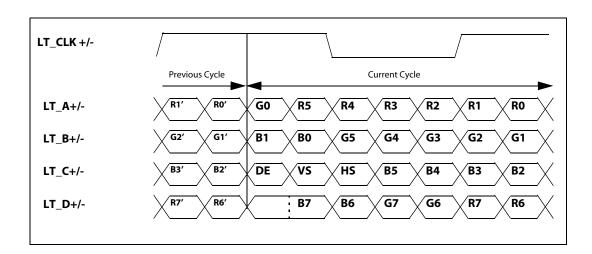

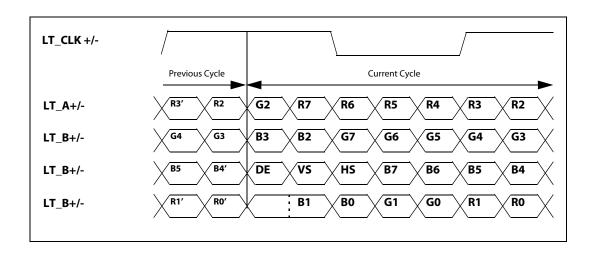

## 2.7 LVDS Output Data Mapping

The LVDS Clock wave form is shown in the following figure. Note that the rising edge of the LVDS clock occurs two LVDS sub symbols before the current cycle of data. The clock is composed of a 4 LVDS sub symbol HIGH time and a 3 LVDS sub symbol LOW time. Two types of RGB data mapping are supported. RGB data mapping is defined by a register bit LVDS\_MAP.

Figure 2-4 LVDS Inputs Data (LVDS\_MAP = 0)

Data Sheet — EP94Z3(K)\_DS V0.4

# **Appendix A Package**

Figure A-1 EP94Z3(K) Footprint Diagram

Data Sheet — PACKAGE