# ESS Technology, Inc.

# ES6461 / ES6460 DMPX Digital Media Processor Datasheet

# OVERVIEW

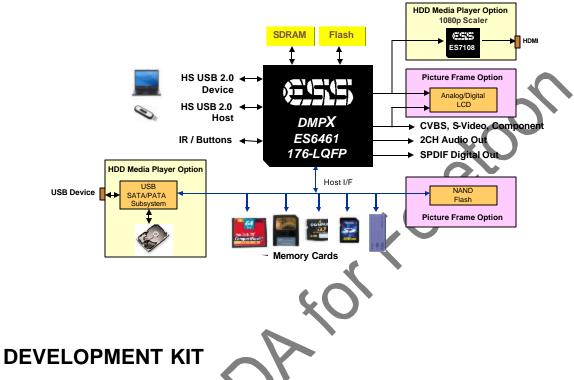

The **DMPX** series is a  $4^{h}$  generation Digital Picture Frame and HDD Media Player solution built upon ESS's highly popular DMP3 (ES6430), DMP2 (ES6425) and DMP1 (ES6420) processors.

| P/N       | Description             | Package  | Core Function                      | HS USB<br>2.0 OTG | Digital TCON /<br>HDMI                     | CF / IDE /<br>MPEG1/2 | AC3          |

|-----------|-------------------------|----------|------------------------------------|-------------------|--------------------------------------------|-----------------------|--------------|

| ES6460SAA | DMPX Premier            | 128-LQFP | Analog TCON                        | 1                 | NA                                         | NA                    | NA           |

| ES6461SAA | DMPX Reference          |          | RTC                                |                   | 24-bit TCON                                | $\sum$                | NA           |

| ES6461SAB | DMPX Reference w/ Dolby | 176-LPFP | MPEG4 / JPEG<br>MP3<br>Card Reader | 2                 | or 1080p upscaler<br>with HDMI<br>(ES7108) | V                     | $\checkmark$ |

The **DMPX** has a versatile card reader interface for direct connection to CF/MicroDrive, SD, MMC, MS/MS Pro, xD, SM, and IDE hard drives. In addition, HS USB 2.0 host/device interfaces are included for connection to PC, thumb drive, USB hard drives and cameras. The built-in A/V decoder supports MPEG 1/2/4, JPEG and MP3 formats with numerous other options including Dolby AC3 and WMA.

The **DMPX** further integrates the TCON, RTC, DC/DC PWM and NAND Flash controllers to make it the most integrated solution for Digital Picture Frame products. In addition, the boot from NAND Flash feature allows additional system cost savings by eliminating the SPI flash.

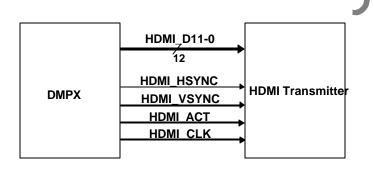

The **DMPX** ES6461 can work with the companion ES7108 Video Scaler/HDMI transmitter to upscale any standard definition (480i/p) video to full 1080p high definition output needed for the emerging HDD Media Player products.

# **KEY FEATURES**

| Feature                                                                                                                            | Benefit                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Audio/Video<br>• 4ch Video DAC<br>• 8/12-bit Digital Video Out<br>• Stereo Audio DAC                                               | <ul> <li>Analog LCD or CVBS / S / Component / VGA / SCART</li> <li>Digital LCD or HDMI (with ES7108) output</li> <li>Eliminate external audio DAC</li> </ul>                                                                                                                                                                                                                                                                        |

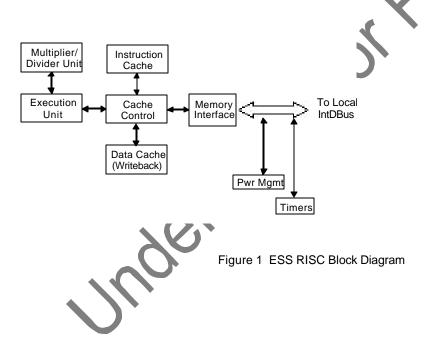

| System & Peripheral<br>32kB RISC cache<br>TCON<br>RTC<br>NAND Flash Boot<br>DC/DC PWM<br>HS USB 2.0 OTG<br>Card Reader<br>IDE port | <ul> <li>Increase JPEG decoding speed</li> <li>Eliminate external TCON for LCD control</li> <li>Eliminate external RTC for clock / calendar</li> <li>Reduce cost by eliminating SPI flash</li> <li>Reduce cost for LCD VGH/VGL and backlight generation</li> <li>Connect USB thumb-drives, cameras or PC</li> <li>Read/write SM, xD, SD, MMC, MS/MS Pro</li> <li>Connect to CF / MD / hard drives or network controllers</li> </ul> |

| Media Playback <ul> <li>MPEG 1/2/4 decoder</li> <li>JPEG/MP3 decoder</li> <li>WMA/AC3 option</li> </ul>                            | <ul> <li>Display MPEG-4 AVI, DVD or VCD video files</li> <li>Display pictures and music slideshows</li> <li>Playback WMA/AC3 audio</li> </ul>                                                                                                                                                                                                                                                                                       |

# **APPLICATIONS**

- Digital Picture Frames

- HDD Media Player

- Digital Signage Media Player

- Embedded TV Media Player

Two development kits are available

- DMPX ES6461 HDD Media Player or Digital Picture Frame reference design

- DMPX ES6460 Digital Picture Frame reference design

Each development kit comes with a complete set of tools:

- Data sheet and schematics

- User Interface software source code

- ROM emulator for code development

Additionally ESS provides FAE support for:

- Customer prototype design

- Firmware customization

# LICENSING REQUIREMENTS

Depending on the features desired, you may be required to apply and obtain a license with the organizations shown below. Per-chip royalties may be required and are to be paid by the purchaser with the respective organizations.

# WMA:

Details on licensing or membership can be obtained at http://www.microsoft.com

# MPEG-2/MPEG-4:

Details on licensing or membership can be obtained at http://www.mpegla.com

### Dolby:

Details on licensing or membership can be obtained at http://www.dolby.com

# AAC MPEG-2/MPEG-4:

Details on licensing or membership can be obtained at http://www.vialicensing.com

### MP3:

Details on licensing or membership can be obtained at http://www.mp3licensing.com

### SD:

Details on licensing or membership can be obtained at http://www.sdcard.org

### **Memory Stick:**

Details on licensing or membership can be obtained at http://www.memorystick.org

### MultiMediaCard:

Details on licensing or membership can be obtained at http://www.mmca.org

# **Compact Flash:**

Details on licensing or membership can be obtained at http://www.compactflash.org

### xD-Picture Card:

Details on licensing or membership can be obtained at http://www.xd-picture.com

# SmartMedia:

Details on licensing or membership can be obtained at http://www.ssfdc.or.jp

# ADDITIONAL LICENSING REQUIREMENTS

# **Dolby Digital Licensing**

Dolby Digital audio enabling software is provided with the DMPX series of DMP processors. Dolby is a trademark of the Dolby Laboratories. Supply of this implementation of Dolby Technology does not convey a license or imply a right under any patent, or any other Industrial or Intellectual Property Right of Dolby Laboratories, to use this implementation in any end-user or ready-to-use final product. Companies planning to use this implementation in products must obtain a license from Dolby Laboratories Licensing Corporation before designing such products. Additional per-chip royalties may be required and are to be paid by the purchaser to Dolby Laboratories, Inc. Details of the OEM Dolby Digital license may be oretoc obtained by writing to:

Dolby Laboratories, Inc. **Dolby Laboratories Licensing Corporation** Attn.: Intellectual Property Manager 100 Potrero Avenue San Francisco, CA 94103-4813 http://www.dolby.com

### MPEG-4 and WMA Notification

System manufacturers need to obtain a license for MPEG-4 decode from MPEG-LA for MPEG-4 parts. Optionally, this device requires system manufacturers to obtain a license for Windows Media Audio from Microsoft in order to support the decoding of WMA content.

4

MPEG-LA 4601 Willard Avenue, Suite 200 Chevy Chase, MD 20815 http://www.mpegla.com

**Microsoft Corporation Digital Media Division** One Microsoft Way Redmond, WA 98052-639 http://www.microsoft

DMPX Datasheet July 23, 2008

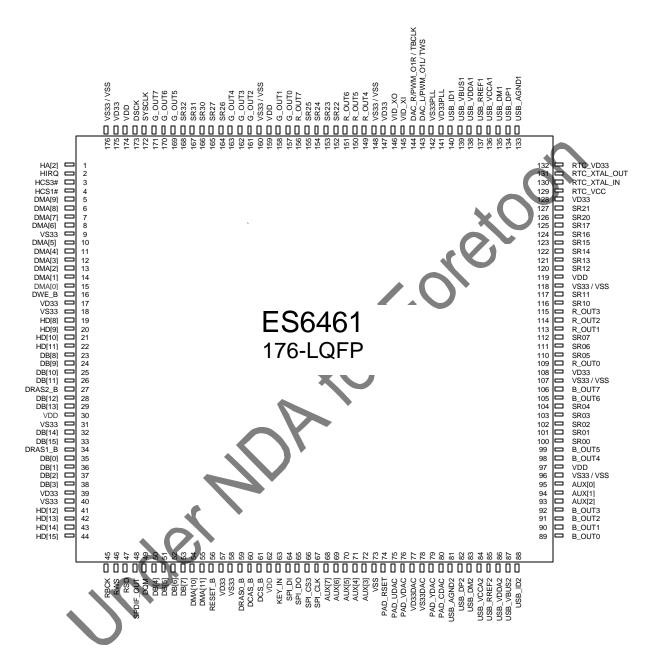

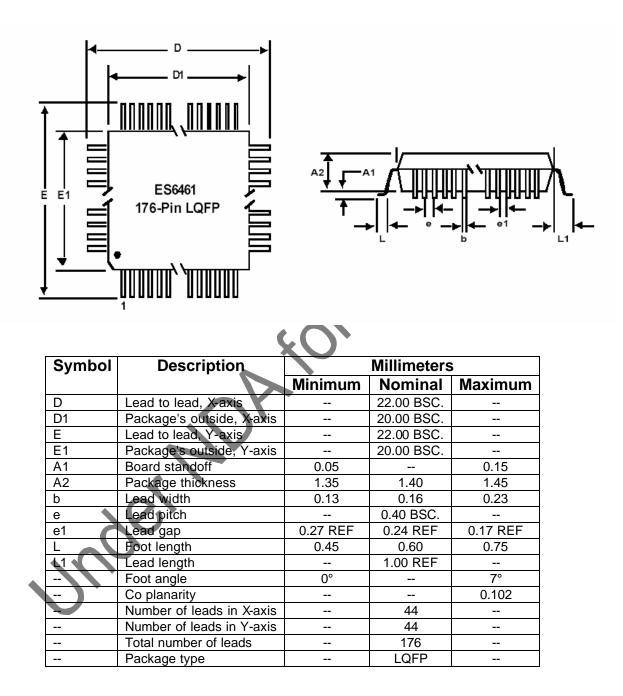

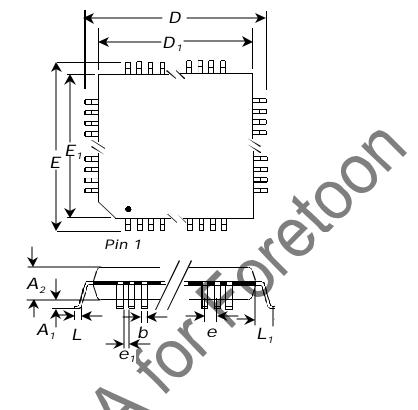

# ES6461 PIN-OUT

# **ES6461 PIN DESCRIPTION**

| ES6461 PIN # | NAME    | Pin Description                           | Туре  |

|--------------|---------|-------------------------------------------|-------|

| 1            | HA[2]   | Host control / GPIO101                    | HOST  |

| 2            | HIRQ    | Host control / GPIO102                    | HOST  |

| 3            | HCS3#   | Host control / GPIO103                    | HOST  |

| 4            | HCS1#   | Host control / GPIO104                    | HOST  |

| 5            | DMA[9]  | DRAM address bus / VDACTEST IN            | DRAM  |

| 6            | DMA[8]  | DRAM address bus / VDACTEST_IN            | DRAM  |

| 7            | DMA[7]  | DRAM address bus / VDACTEST_IN            | DRAM  |

| 8            | DMA[6]  | DRAM address bus / VDACTEST_IN            | DRAM  |

| 9            | VS33    | 3.3V Ground supply                        | G3.3V |

|              | VSS     | 1.2V Ground supply                        | G1.2V |

| 10           | DMA[5]  | DRAM address bus / VDACTEST, IN           | DRAM  |

| 11           | DMA[4]  | DRAM address bus / VDACTEST IN            | DRAM  |

| 12           | DMA[3]  | DRAM address bus / VDACTEST IN            | DRAM  |

| 13           | DMA[2]  | DRAM address bus / VDACTEST IN            | DRAM  |

| 14           | DMA[1]  | DRAM address bus / VDACTEST_IN            | DRAM  |

| 15           | DMA[0]  | DRAM address bus / VDACTEST_IN            | DRAM  |

| 16           | DWE_B   | DRAM Write Enable, For External Bonding / | DRAM  |

|              |         | PLL_SEL[1]                                |       |

| 17           | VD33    | 3.3V power supply                         | P3.3V |

| 18           | VS33    | 3.3V Ground supply                        | G3.3V |

|              | VSS     | 1.2V Ground supply                        | G1.2V |

| 19           | HD[8]   | Host data / GPIO70                        | HOST  |

| 20           | HD[9]   | Host data / GPIO71                        | HOST  |

| 21           | HD[10]  | Host data /GPIO72                         | HOST  |

| 22           | HD[11]  | Host data / GPIO73                        | HOST  |

| 23           | DB[8]   | DRAM data bus                             | DRAM  |

| 24           | DB[9]   | DRAM data bus                             | DRAM  |

| 25           | DB[10]  | DRAM data bus                             | DRAM  |

| 26           | DB[11]  | DRAM data bus                             | DRAM  |

| 27           | DRAS2_B | SDRAM Bank Select 1 / GPIO83 /            | DRAM  |

|              |         | Debug Mode (strap)                        |       |

| 28           | DB[12]  | DRAM data bus                             | DRAM  |

| 29           | DB[13]  | DRAM data bus                             | DRAM  |

| 30           | VDD     | 1.2V power supply                         | P1.2V |

| 31           | VS33    | 3.3V Ground supply                        | G3.3V |

|              | VSS     | 1.2V Ground supply                        | G1.2V |

| 32           | DB[14]  | DRAM data bus                             | DRAM  |

| 33           | DB[15]  | DRAM data bus                             | DRAM  |

| 34           | DRAS1_B | SDRAM Bank Select 0 / GPIO84 /Booting     | DRAM  |

|              | _       | (strap)                                   |       |

| 35           | DB[0]   | DRAM data bus                             | DRAM  |

| 36           | DB[1]   | DRAM data bus                             | DRAM  |

| 37           | DB[2]   | DRAM data bus                             | DRAM  |

| 38           | DB[3]   | DRAM data bus                             | DRAM  |

| 39           | VD33    | 3.3V power supply                         | P3.3V |

| 40           | VS33    | 3.3V Ground supply                        | G3.3V |

|              | VSS     | 1.2V Ground supply                        | G1.2V |

| 41           | HD[12]  | Host data / GPIO74                        | HOST  |

July 23, 2008

| NAME          | Pin Description                                                                                                                                                                                                                                                                                                                                                                         | Туре                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |                                                                                                                                                                                                                                                                                                                                                                                         | HÖST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|               |                                                                                                                                                                                                                                                                                                                                                                                         | HOST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|               |                                                                                                                                                                                                                                                                                                                                                                                         | HOST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|               |                                                                                                                                                                                                                                                                                                                                                                                         | AUDIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|               | · ·                                                                                                                                                                                                                                                                                                                                                                                     | AUDIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|               |                                                                                                                                                                                                                                                                                                                                                                                         | AUDIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|               | · ·                                                                                                                                                                                                                                                                                                                                                                                     | AUDIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|               |                                                                                                                                                                                                                                                                                                                                                                                         | DRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|               |                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|               |                                                                                                                                                                                                                                                                                                                                                                                         | DRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|               |                                                                                                                                                                                                                                                                                                                                                                                         | DRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|               |                                                                                                                                                                                                                                                                                                                                                                                         | SYS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|               |                                                                                                                                                                                                                                                                                                                                                                                         | P3.3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|               |                                                                                                                                                                                                                                                                                                                                                                                         | G3.3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|               |                                                                                                                                                                                                                                                                                                                                                                                         | G1.2V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|               |                                                                                                                                                                                                                                                                                                                                                                                         | DRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|               |                                                                                                                                                                                                                                                                                                                                                                                         | DRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|               |                                                                                                                                                                                                                                                                                                                                                                                         | DRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|               |                                                                                                                                                                                                                                                                                                                                                                                         | P1.2V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| KEY_IN        | Digital key input                                                                                                                                                                                                                                                                                                                                                                       | SYS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SPI_DI        | SPI_DI                                                                                                                                                                                                                                                                                                                                                                                  | SRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SPI_DO        | SPI_DO                                                                                                                                                                                                                                                                                                                                                                                  | SRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SPI_CS3       | SPI_CS3 / Bank3_Sel (strap)                                                                                                                                                                                                                                                                                                                                                             | SRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SPI_CLK       | SPL_CLK7 Bank3_Serial (strap)                                                                                                                                                                                                                                                                                                                                                           | SRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| AUX[7]        | Original AUX[7] / XD_CS# / SM_CS# /<br>GPIO105                                                                                                                                                                                                                                                                                                                                          | AUX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| AUX[6]        | Original AUX[6] / GPIO106 / HRST#                                                                                                                                                                                                                                                                                                                                                       | AUX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| AUX[5]        | Original AUX[5] / SPI_CS2/ MUTE / GPIO37 /<br>NAND_CS#                                                                                                                                                                                                                                                                                                                                  | AUX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| AUX[4]        |                                                                                                                                                                                                                                                                                                                                                                                         | AUX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| AUX[3]        | Original AUX[3] / SM_CD# / SOUT / GPIO34 /                                                                                                                                                                                                                                                                                                                                              | AUX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VSS           | 1.2V Ground supply                                                                                                                                                                                                                                                                                                                                                                      | G1.2V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VS <b>S</b> 3 |                                                                                                                                                                                                                                                                                                                                                                                         | G3.3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PAD_RSET      | VDAC Current Adjustment Resistor Input/                                                                                                                                                                                                                                                                                                                                                 | VDAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PAD UDAC      |                                                                                                                                                                                                                                                                                                                                                                                         | VDAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|               |                                                                                                                                                                                                                                                                                                                                                                                         | VDAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|               |                                                                                                                                                                                                                                                                                                                                                                                         | PA3.3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               |                                                                                                                                                                                                                                                                                                                                                                                         | GA3.3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               |                                                                                                                                                                                                                                                                                                                                                                                         | VDAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|               |                                                                                                                                                                                                                                                                                                                                                                                         | VDAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| _             |                                                                                                                                                                                                                                                                                                                                                                                         | USB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|               |                                                                                                                                                                                                                                                                                                                                                                                         | USB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|               |                                                                                                                                                                                                                                                                                                                                                                                         | USB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| —             |                                                                                                                                                                                                                                                                                                                                                                                         | USB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

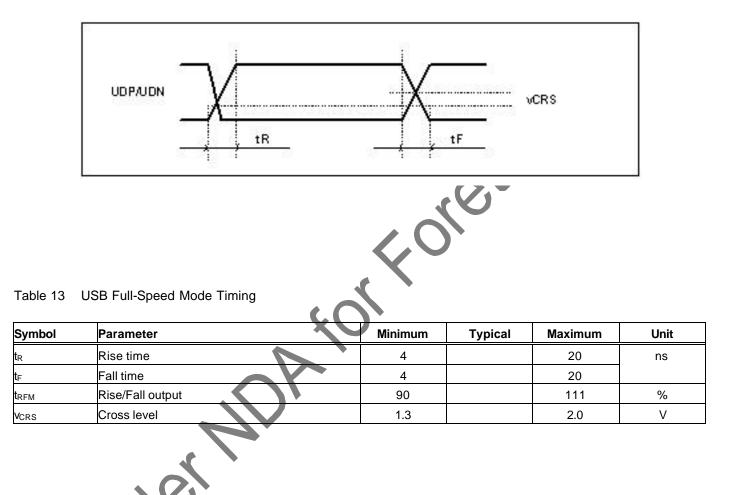

|               |                                                                                                                                                                                                                                                                                                                                                                                         | USB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |