# QUAD BIDIRECTIONAL TRANSIL™ ARRAY FOR ESD PROTECTION

#### **APPLICATION**

ASD™

Where transient overvoltage protection in ESD sensitive equipment is required, such as :

- Computers

- Printers

- Communication systems and cellular phones

- Video equipment

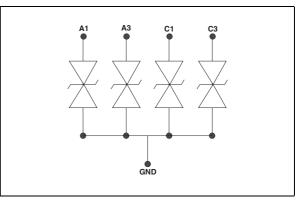

This device is particularly adapted to the protection of symmetrical signals.

#### DESCRIPTION

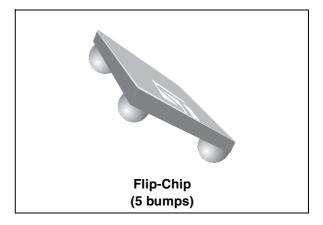

The ESDA14V2-4BF1 is a monolithic array designed to protect up to 4 lines in a bidirectional way against ESD transients.

The device is ideal for situations where board space saving is requested.

#### **FEATURES**

- 4 Bidirectional Transil<sup>™</sup> functions

- ESD Protection: IEC61000-4-2 level 4

- Stand off voltage: 12 V MIN.

- Low leakage current < 1 µA</p>

- 50W Peak pulse power (8/20µs)

#### **BENEFITS**

- High ESD protection level

- High integration

- Suitable for high density boards

#### COMPLIES WITH THE FOLLOWING STANDARDS:

- IEC61000-4-2: 15kV (air discharge)

- 8kV (contact discharge)

- MIL STD 883E- Method 3015-7: class3 25kV (human body model)

#### **Order Codes**

| Part Number   | Marking |

|---------------|---------|

| ESDA14V2-4BF1 | EA      |

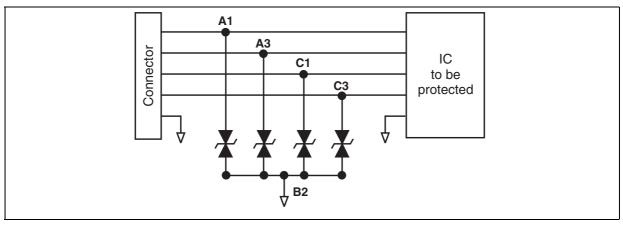

#### **FUNCTIONAL DIAGRAM**

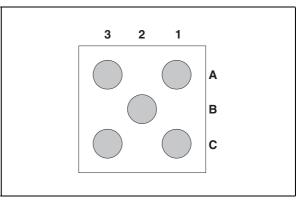

#### **PIN CONFIGURATION (Ball Side)**

| Symbol           | P                             | Value                                                                                        | Unit                |    |

|------------------|-------------------------------|----------------------------------------------------------------------------------------------|---------------------|----|

| V <sub>PP</sub>  | ESD discharge                 | MIL STD 883E - Method 3015-7<br>IEC61000-4-2 air discharge<br>IEC61000-4-2 contact discharge | ± 25<br>± 15<br>± 8 | kV |

| P <sub>PP</sub>  | Peak pulse power (8/20µs)     |                                                                                              | 50                  | W  |

| Тj               | Junction temperature          |                                                                                              | 125                 | °C |

| T <sub>stg</sub> | Storage temperature range     |                                                                                              | -55 to +150         | °C |

| ΤL               | Lead solder temperature (10 s | 260                                                                                          | °C                  |    |

| Т <sub>ор</sub>  | Operating temperature range   | -40 to +125                                                                                  | °C                  |    |

# **ABSOLUTE MAXIMUM RATING** $(T_{amb} = 25^{\circ}C)$

# **ELECTRICAL CHARACTERISTICS** ( $T_{amb} = 25^{\circ}C$ )

| Symbol          | Parameter          |  |  |  |

|-----------------|--------------------|--|--|--|

| V <sub>RM</sub> | Stand-off voltage  |  |  |  |

| V <sub>BR</sub> | Breakdown voltage  |  |  |  |

| V <sub>CL</sub> | Clamping voltage   |  |  |  |

| I <sub>RM</sub> | Leakage current    |  |  |  |

| I <sub>PP</sub> | Peak pulse current |  |  |  |

| С               | Capacitance        |  |  |  |

| Rd              | Dynamic resistance |  |  |  |

|               | V <sub>BR</sub> |      | @ I <sub>R</sub> | I <sub>RM</sub> @ | ₽ V <sub>RM</sub> | R <sub>d</sub> | αΤ                   | С       |

|---------------|-----------------|------|------------------|-------------------|-------------------|----------------|----------------------|---------|

| Part Number   | min.            | max. |                  | max.              |                   | typ.           | max.                 | max.    |

|               |                 |      |                  |                   |                   | note 1         | note 2               | 0V bias |

|               | V               | V    | mA               | μA                | V                 | Ω              | 10 <sup>-4</sup> /°C | pF      |

| ESDA14V2-4BF1 | 14.2 18         | 18   | 1                | 1                 | 12                | 3.2            | 10                   | 15      |

|               | 17.2            |      | I                | 0.1               | 3                 |                |                      |         |

Note 1: Square pulse,  $I_{PP} = 3A$ ,  $tp = 2.5\mu s$ .

Note 2:  $\Delta V_{BR} = \alpha T$  (Tamb -25°C) x V<sub>BR</sub> (25°C)

57.

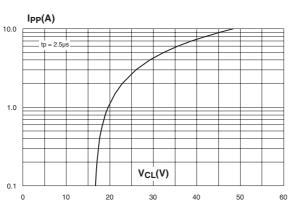

**Fig. 1:** Clamping voltage versus peak pulse current (Tj initial = 25°C) (Rectangular waveform).

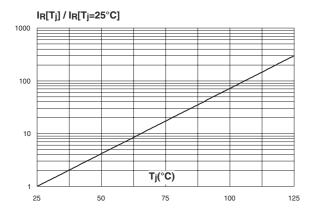

**Fig. 3:** Relative variation of leakage current versus junction temperature (typical values).

#### **APPLICATION EXAMPLE**

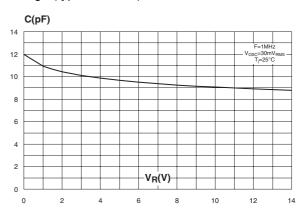

**Fig. 2:** Capacitance versus reverse applied voltage (typical values).

#### **TECHNICAL INFORMATION**

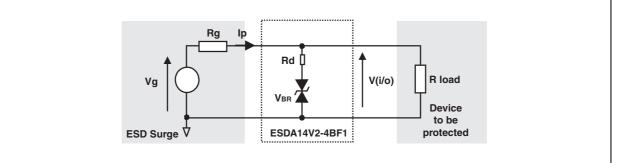

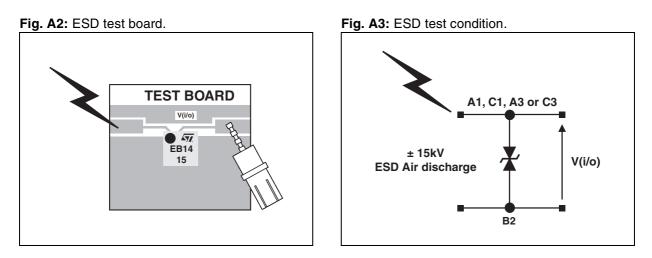

#### 1. ESD protection by ESDA14V2-4BF1

With the focus of lowering the operation levels, the problem of malfunction caused by the environment is critical. Electrostatic discharge (ESD) is a major cause of failure in electronic systems.

As a transient voltage suppressor, ESDA14V2-4BF1 is an ideal choice for ESD protection by suppressing ESD events. It is capable of clamping the incoming transient to a low enough level such that any damage is prevented on the device protected by ESDA14V2-4BF1.

ESDA14V2-4BF1 serves as a parallel protection elements, connected between the signal line and ground. As the transient rises above the operating voltage of the device, the ESDA14V2-4BF1 becomes a low impedance path diverting the transient current to ground.

The clamping voltage is given by the following formula:

$$V_{CL} = V_{BR} + R_d I_{PP}$$

As shown in figure A1, the ESD strikes are clamped by the transient voltage suppressor.

#### Fig. A1: ESD clamping behavior.

To have a good approximation of the remaining voltages at both Vi/o side, we provide the typical dynamical resistance value  $R_d$ . By taking into account the following hypothesis:

$$R_G > R_d$$

""and"" $R_{load} > R_d$

we have:

$$V(i/o) = V_{BR} + R_d \times \frac{V_G}{R_G}$$

The results of the calculation done  $V_G = 8kV$ ,  $R_G = 330\Omega$  (IEC61000-4-2 standard),  $V_{BR} = 14.2V$  (typ.) and  $R_d = 3.2\Omega$  (typ.) give:

$$V(i/o) = 91.8$$

Volts

This confirms the very low remaining voltage across the device to be protected. It is also important to note that in this approximation the parasitic inductance effect was not taken into account. This could be a few tenths of volts during a few ns at the Vi/o side.

<u>ک</u>/

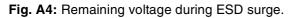

The measurements done here after show very clearly (*figure A4*) the high efficiency of the ESD protection: the clamping voltage V(i/o) becomes very close to  $V_{BR}$  (positive way, *figure A4a*) and  $-V_{BR}$  (negative way, *figure A4b*).

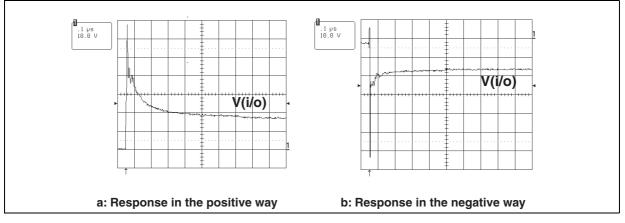

#### 2. Crosstalk behavior

Fig. A5: Crosstalk phenomenon.

The crosstalk phenomena are due to the coupling between 2 lines. Coupling factors ( $\beta$ 12 or  $\beta$ 21) increase when the gap across lines decreases, particularly in silicon dice. In the example above, the expected signal on load R<sub>L2</sub> is  $\alpha_2 V_{G2}$ , in fact the real voltage at this point has got an extra value  $\beta_{21}V_{G2}$ . This part of the V<sub>G1</sub> signal represents the effect of the crosstalk phenomenon of the line 1 on the line 2. This phenomenon has to be taken into account when the drivers impose fast digital data or high frequency analog signals. The perturbed line will be more affected if it works with low voltage signal or high load impedance (few k $\Omega$ ).

**Δ**Υ/.

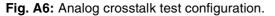

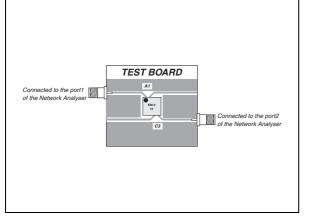

*Figure A6* gives the measurement circuit for the analog crosstalk application. In *figure A7*, the curve shows the effect of the line A1on the line A3. In usual frequency range of analog signals (up to 100 MHz) the effect on disturbed line is less than -30dB.

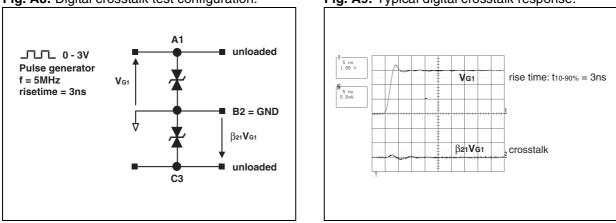

Fig. A8: Digital crosstalk test configuration.

Fig. A9: Typical digital crosstalk response.

*Figure A8* shows the measurement circuit used to quantify the crosstalk effect in a classical digital application.

*Figure A9* shows that in such a condition, the impact on the disturbed line is less than 5 mV peak to peak. No data disturbance was noted on the concerned line. The measurements performed with falling edges give an impact within the same range.

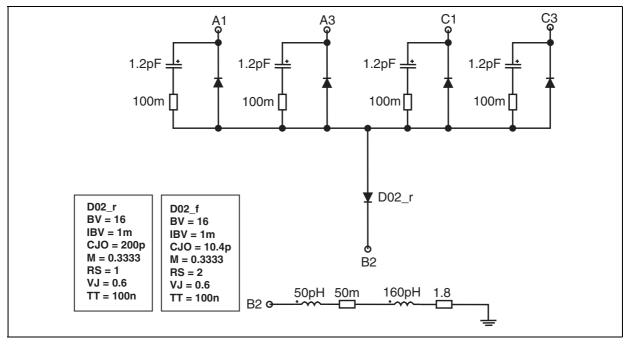

#### Fig. A10: Aplac model.

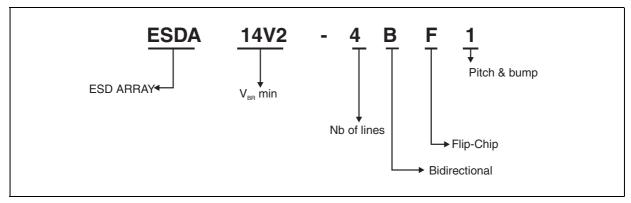

#### **ORDER CODE**

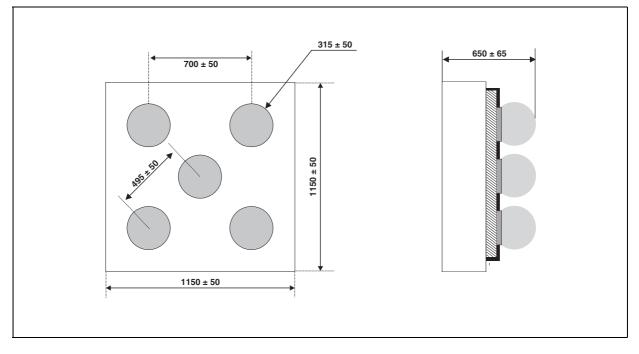

## PACKAGE MECHANICAL DATA

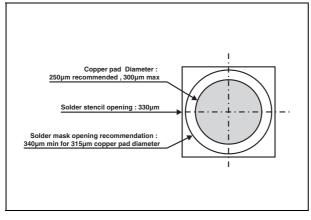

#### FOOT PRINT RECOMMENDATIONS

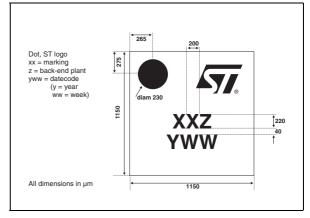

#### MARKING

57.

8/9

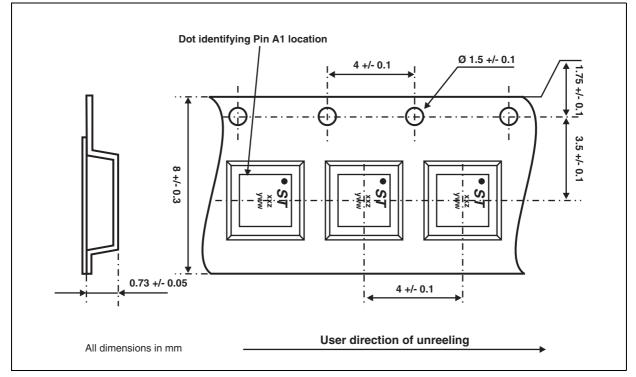

#### FLIP-CHIP TAPE AND REEL SPECIFICATION

#### **ORDERING INFORMATION**

| Part Number   | Marking | Package   | Weight | Base qty | Delivery<br>mode |

|---------------|---------|-----------|--------|----------|------------------|

| ESDA14V2-4VF1 | EA      | Flip Chip | 2.1 mg | 5000     | Tape & reel      |

Note: More packing informations are available in the application notes

- AN1235: "Flip-Chip: Package description and recommandations for use"

- AN1751: "EMI Filters: Recommendations and measurements"

#### **REVISION HISTORY**

#### Table 1: Revision history

| Date        | Revision | Description of Changes     |

|-------------|----------|----------------------------|

| July-2002   | 1        | First issue                |

| 27-May-2004 | 2        | Die clearance optimization |

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners

© 2004 STMicroelectronics - All rights reserved

#### STMicroelectronics GROUP OF COMPANIES

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States www.st.com

57.