# PRODUCT SPECIFICATION FOR LCD MODULE

MODULE NO. : ET-G240160B REVERSION : V1 TYPE : COB

Customer Approval:

| PREPARED BY | DATE |  |

|-------------|------|--|

| CHECKED BY  | DATE |  |

| APPROVED BY | DATE |  |

#### DOCUMENT REVISION HISTORY

| VERSION | DATE          | DESCRIPTION | CHANGED BY |

|---------|---------------|-------------|------------|

| V1      | JAN. 28. 2011 | First issue | OU         |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

|         |               |             |            |

# **1. General Specifications**

JUKAS

C

٢

| Item                      | Standard Value                                           | Unit |

|---------------------------|----------------------------------------------------------|------|

| Number of dots            | 240(W)X160(H)                                            | dots |

| Display Pattern           | ■Dot-Graphic □Character □Digits □with ICON □             |      |

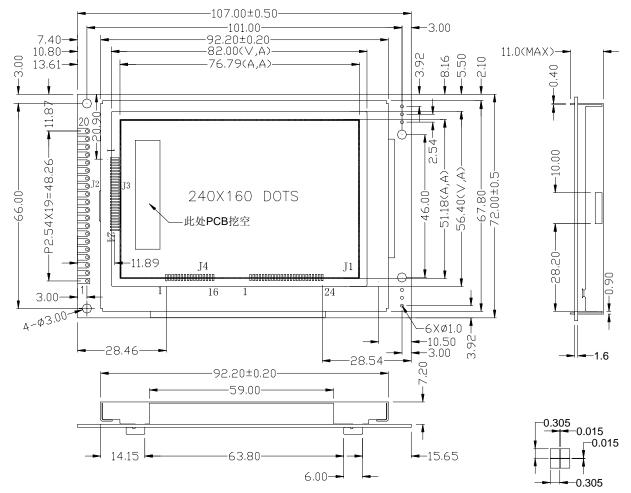

| Module Dimension          | 107(W) X 72.0(H) X 11.0(T)                               | mm   |

| Viewing Area              | 82.0 (W) X 56.4(H)                                       | mm   |

| Active Area               | 76.79(W) x 51.18(H)                                      | mm   |

| DOT Size                  | 0.305(W) x 0.305(H)                                      | mm   |

| DOT Pitch                 | 0.32(W) x 0.32(H)                                        | mm   |

|                           | TN, Positive TN, Negative                                |      |

|                           | 🗆 HTN, Positive 🛛 HTN, Negative                          |      |

| LCD Type                  | □ STN, Yellow-Green □ STN, Gray □ STN, Blue              |      |

|                           | □ FSTN, Positive □ FSTN, Negative                        |      |

|                           | □ Color STN                                              |      |

|                           |                                                          |      |

| Polarizer Type            | □ Transmissive □ Reflective □ Transflective □ Anti-Glare |      |

| View Direction            | □ 6H □ 12H □                                             |      |

| Operation Voltage         | □3.0(3.3) □5.0 □                                         | V    |

| DC-DC Converter           | Build-in External                                        |      |

| LCD Controller IC         | Build-in <u>(RA8806)</u> □ not Build-in                  |      |

| LCD Driver IC             | NT7086PQ                                                 |      |

| LCD Driving Method        | 1/240duty, 1/17bias                                      |      |

| Interface Type            | □6800 □ 8080 □ I2C □ Serial                              |      |

|                           |                                                          |      |

| Backlight Type            | LED CCFL EL Ono Backlight                                |      |

|                           |                                                          |      |

| Backlight Color           | <br>□Yellow-Green □ White □ Amber □ Blue □ Red           |      |

| U U                       |                                                          |      |

| EL/CCFL Driver type       | Build-in External                                        |      |

| Touch Panel IC            | 🗆 Build-in 🛛 not Build-in                                |      |

| Touch Panel               | 🗆 Build-in 🗌 not Build-in                                |      |

| Operation Temperature(oC) | -20~70 (Торі – Торн)                                     | deg  |

| Storage Temperature (oC)  | -30~80 (Tstl Tsth)                                       | deg  |

Note: Label "

"

means the option selected.

LCD MODULE

#

## 2. External Dimensions

# 3. Pin Description

| 3.1 J1(SMD24 , Pitch=1.0mm) |         |       |                                 |  |  |  |  |  |

|-----------------------------|---------|-------|---------------------------------|--|--|--|--|--|

| Pin.No                      | Symbol  | Lever | Description                     |  |  |  |  |  |

| 1                           | VSS     | Р     | GND.                            |  |  |  |  |  |

| 2                           | VDD     | Р     | Power supply for logic and LCD. |  |  |  |  |  |

| 3                           | V0      | Р     | Operating voltage for LCD.      |  |  |  |  |  |

| 4                           | A0      | I     | Data type select                |  |  |  |  |  |

| 5                           | /WR     | I     | Write signal                    |  |  |  |  |  |

| 6                           | /RD     | I     | Read signal                     |  |  |  |  |  |

| 7-14                        | DB0-DB7 | I/O   | Data bus.                       |  |  |  |  |  |

| 15                          | /CS     | I     | Chip select                     |  |  |  |  |  |

| 16                          | /RST    | I     | Reset signal( Low effective ).  |  |  |  |  |  |

| 17                          | 17 VEE  |       | Voltage output to LCD           |  |  |  |  |  |

| 18 LEDA P                   |         | Р     | Backlight anode (+5V).          |  |  |  |  |  |

| 19                          | NC      | /     | No connection                   |  |  |  |  |  |

| 20 | NC  | / | No connection     |

|----|-----|---|-------------------|

| 21 | NC  | / | No connection     |

| 22 | NC  | / | No connection     |

| 23 | INT | 0 | RA8806 Interrupt. |

| 24 | NC  | / | No connection     |

#### 3.2 J2(DIP20, Pitch=2.54mm)

| Pin.No | Symbol  | Lever | Description                     |

|--------|---------|-------|---------------------------------|

| 1      | VSS     | Р     | GND.                            |

| 2      | VDD     | Р     | Power supply for logic and LCD. |

| 3      | V0      | Р     | Operating voltage for LCD.      |

| 4      | /WR     | I     | Write signal                    |

| 5      | /RD     | I     | Read signal                     |

| 6      | /CS     | I     | Chip select                     |

| 7      | A0      | I     | Data type select                |

| 8      | /RST    | I     | Reset signal( Low effective ).  |

| 9-16   | DB0-DB7 | I/O   | Data bus.                       |

| 17     | LEDA    | Р     | Backlight anode (+5V).          |

| 18     | VEE     | Р     | Voltage output to LCD           |

| 19     | LEDA    | Р     | Backlight anode (+5V).          |

| 20     | LEDK    | Р     | Backlight anode ( 0V ).         |

#### 3.3 J3(DIP20, Pitch=2.54mm)

| Pin.No | Symbol     | Lever | Description                                                  |

|--------|------------|-------|--------------------------------------------------------------|

| 1      | FLM(Frame) | Р     | Input / output for chip select or data of the shift register |

| 2      | V1(V2)     | Р     | Power supply for LCD driver                                  |

| 3      | V4(V5)     | Р     | Power supply for LCD driver                                  |

| 4      | VDD        | I     | Power supply for logic and LCD                               |

| 5      | V0         | I     | Power supply for LCD driver                                  |

| 6      | CL1(Load)  | I     | Latch pulse input/shift clock input for the shift register   |

| 7      | CL2(Cp)    | I     | Display data shift clock input for segment mode              |

| 8      | M(Df)      | I     | AC-converting signal input for LCD driver waveform           |

| 9      | /D-OFF     | I/O   | Control input for deselect output level                      |

| 10-13  | D0-D3      | I/O   | Display data input for segment mode                          |

| 14     | VSS        | Р     | GND                                                          |

| 15     | V2(V3)     | Р     | Power supply for LCD driver                                  |

| 16     | V3(V4)     | Р     | Power supply for LCD driver.                                 |

# 4. Electrical Specifications

### 4.1 Absolute Maximum Ratings

| Parameter                     | Symbol     | Conditions | Min.  | Max.      | Units |

|-------------------------------|------------|------------|-------|-----------|-------|

| Supply Voltage(Logic)         | VDD - VSS  |            | - 0.3 | 6.5       | V     |

| Supply Voltage<br>(LCD Drive) | VLCD - VSS |            | 0     | 35.0      | V     |

| Input Voltage                 | VI         |            | -0.3  | VDD + 0.3 | V     |

### 4.2 DC Characteristics

| Parameter                | Symbol                              | Min.                 | Тур.                            | Max.                 | Unit | Condition                                                         |

|--------------------------|-------------------------------------|----------------------|---------------------------------|----------------------|------|-------------------------------------------------------------------|

| Operating Voltage(1)     | V <sub>DDP</sub> / V <sub>DDH</sub> | 4.5                  | 5.0                             | 5.5                  | V    | V <sub>DDP</sub> = V <sub>DDH</sub><br>(Refer to<br>Figure 6-31)  |

| Operating Voltage(2)     | V <sub>DDP</sub> / V <sub>DD</sub>  | 2.4                  | 3.3                             | 3.6                  | V    | $V_{DDP} = V_{DD}$<br>$V_{DDH}$ Open<br>(Refer to<br>Figure 6-30) |

| Oscillator frequency     | Fosc                                | 4                    | 8                               | 12                   | MHz  | $V_{DD} = 5V$                                                     |

| External clock frequency | F <sub>CLK</sub>                    | 4                    | 8                               | 12                   | MHz  | $V_{DD} = 5V$                                                     |

| DC to DC Output Voltage  | V <sub>DD</sub>                     | 2.8V                 | 3.0                             | 3.3                  | V    | Add external<br>1uF Capacitor                                     |

| Input                    |                                     |                      |                                 |                      |      |                                                                   |

| Input High Voltage       | VIH                                 | $0.8 x V_{DD}$       |                                 | V <sub>DD</sub>      | V    | See Note 1, 3                                                     |

| Input Low Voltage        | V <sub>IL</sub>                     | Gnd                  |                                 | $0.2 x V_{DD}$       | V    | See Note 1, 3                                                     |

| Output                   |                                     |                      |                                 |                      |      |                                                                   |

| Output High Voltage      | V <sub>OH</sub>                     | V <sub>DD</sub> -0.4 |                                 | V <sub>DD</sub>      | V    | See Note 2, 3                                                     |

| Output Low Voltage       | V <sub>OL</sub>                     | Gnd                  |                                 | V <sub>DD</sub> +0.4 | V    | See Note 2, 3                                                     |

| Schmitt-trigger          |                                     | -                    |                                 |                      |      |                                                                   |

| Output High Voltage      | V <sub>OH</sub>                     | $0.5 XV_{DD}$        | $0.7 \mathrm{XV}_{\mathrm{DD}}$ | 0.8XV <sub>DD</sub>  | V    | See Note 4                                                        |

| Output Low Voltage       | V <sub>OL</sub>                     | $0.2 X V_{DD}$       | $0.3 XV_{DD}$                   | $0.5 XV_{DD}$        | V    | See Note 4                                                        |

| Input Leakage Current 1  | I <sub>IH</sub>                     |                      |                                 | +1                   | μA   |                                                                   |

| Input Leakage Current 2  | IIL                                 |                      |                                 | -1                   | μA   |                                                                   |

| Operation Current        | I <sub>OPR</sub>                    | 1                    | 5                               | 10                   | mA   |                                                                   |

| Standby Mode Current     |                                     |                      | 1.5                             | 1.8                  | mA   | Case1                                                             |

| (Normal Mode Current)    | I <sub>SB</sub>                     |                      | 1.8                             | 2.1                  | mA   | Case2                                                             |

| Display Off Current      |                                     |                      | 120                             | 140                  | μA   | Case1                                                             |

|                          | DISPLAY                             |                      | 140                             | 160                  | μA   | Case2                                                             |

| Sleep Mode               |                                     |                      | 0.5                             | 1                    | μA   | Case1                                                             |

|                          | SLP                                 |                      | 20                              | 25                   | μA   | Case2                                                             |

### Notes:

1. ZCS1, CS2, ZWR, ZRD, RS, MI, DW, DB, KIN[7:0], TESTMD and TESTI are inputs. KIN[7:0] built-in pull up resistors. The TESTMD and TESTI built-in pull down resistors.

INT, BUSY, CLK\_OUT, PWM\_OUT, KOUT[7:0], LP, FR, YD, ZDOFF, XCK and LD[7:0] are outputs.

3. DATA[7:0] are Bi-direction.

4. The ZRST are Schmitt-trigger with pull-up input. The pulse width on ZRST must be at least 1024\*tc. Note that pulses of more than a few seconds will cause DC voltages to be applied to the LCD panel.

**Case1:**  $V_{DDP} = V_{DD} = A_{VDD} = 3.3V$ ,  $V_{DDH} = NC$ , LCD Driver VDD = 5V, CLK = 4MHz, CLK\_OUT: Off, Segment=160, Common=160, FRM = 78Hz, T<sub>A</sub>=25°C.

**Case2:**  $V_{DDP} = V_{DDH} = 5V$ ,  $V_{DD} = A_{VDD} = 3V$ , LCD Driver VDD = 3.3V, CLK = 4MHz, CLK\_OUT: Off, Segment=160, Common=160, FRM = 78Hz, T<sub>A</sub>=25°C.

٠

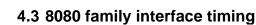

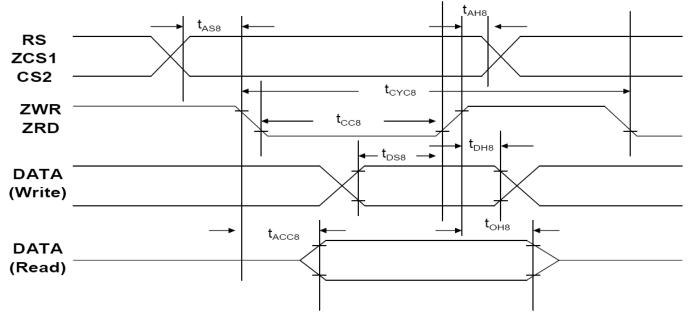

Figure 4-1: 8080 Family Interface Timing

| Symbol            | Description                  | Rating |      | Unit | Condition                    |  |

|-------------------|------------------------------|--------|------|------|------------------------------|--|

| Symbol            | Description                  | Min.   | Max. |      |                              |  |

| t <sub>CYC8</sub> | t <sub>CYC8</sub> Cycle time |        |      | ns   | tc = one system clock period |  |

| t <sub>CC8</sub>  | Strobe Pulse width           | 50     |      | ns   |                              |  |

| t <sub>AS8</sub>  | Address setup time           | 0      |      | ns   |                              |  |

| t <sub>AH8</sub>  | Address hold time            | 20     |      | ns   |                              |  |

| t <sub>DS8</sub>  | Data setup time              | 30     |      | ns   |                              |  |

| t <sub>DH8</sub>  | 8 Data hold time             |        |      | ns   |                              |  |

| t <sub>ACC8</sub> | Data output access time      | 0      | 20   | ns   | 1                            |  |

| t <sub>OH8</sub>  | Data output hold time        | 0      | 10   | ns   | 1                            |  |

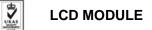

### 4.4 6800 Family Interface Timing

(C)

Ð

#### Figure 4-2: 6800 Family Interface Timing

| Symbol            | Description             | Rating |      | Unit | Condition                      |  |  |

|-------------------|-------------------------|--------|------|------|--------------------------------|--|--|

| Symbol            | Description             | Min.   | Max. |      | Condition                      |  |  |

| t <sub>cyc6</sub> | Cycle time              | 2*tc   |      | ns   | tc is one system clock period: |  |  |

| t <sub>cc6</sub>  | Strobe Pulse width      | 50     |      | ns   | tc = 1/CLK                     |  |  |

| t <sub>AS6</sub>  | Address setup time      | 0      |      | ns   |                                |  |  |

| t <sub>AH6</sub>  | Address hold time       | 20     |      | ns   |                                |  |  |

| t <sub>DS6</sub>  | Data setup time         | 30     |      | ns   |                                |  |  |

| t <sub>DH6</sub>  | Data hold time          | 20     |      | ns   |                                |  |  |

| t <sub>ACC6</sub> | Data output access time | 0      | 20   | ns   | ]                              |  |  |

| t <sub>oH6</sub>  | Data output hold time   | 0      | 10   | ns   |                                |  |  |

ET-G240160BV1

# 5. Register List Table

C

the second

| REG# | Name          | D7             | D6              | D5           | D4      | D3           | D2       | D1       | D0       | Default |

|------|---------------|----------------|-----------------|--------------|---------|--------------|----------|----------|----------|---------|

|      | STATUS        | MBUSY          | SBUSY           | SLEEP        |         |              | WAKE_STS | KS_STS   | TP_STS   |         |

| 00h  | WLCR          | PWR            | LINEAR          | SRST         |         | TEXT_MD      | ZDOFF    | GBLK     | GINV     | 00h     |

| 01h  | MISC          | NO_<br>FLICKER | CLKO_SEL        | BUSY_<br>LEV | INT_LEV | XCK_SEL1     | XCK_SEL0 | SDIR     | CDIR     | 04h     |

| 03h  | ADSR          | SCR_PEND       |                 |              |         | BIT_INV      | SCR_DIR  | SCR_HV   | SCR_EN   | 00h     |

| 0Fh  | INTR          |                | WAKI_EN         | KEYI_EN      | TPI_EN  | TP_ACT       | WAK_STS  | KEY_STS  | TP_STS   | 00h     |

| 10h  | WCCR          | CUR_INC        | FULL_OFS        | BIT_REV      | BOLD    | T90DEG       | CUR_EN   | CUR_BLK  |          | 00h     |

| 11h  | CHWI          | CURH3          | CURH2           | CURH1        | CURH0   | ROWH3        | ROWH 2   | ROWH 1   | ROWH 0   | 00h     |

| 12h  | MAMR          | CUR_HV         | DISPMD2         | DISPMD1      | DISPMD0 | L_MIX1       | L_MIX 0  | MW_MD1   | MW_MD0   | 11h     |

| 20h  | AWRR          |                |                 | AWR5         | AWR4    | AWR3         | AWR2     | AWR1     | AWR0     | 27h     |

| 21h  | DWWR          |                |                 | DWW5         | DWW 4   | DWW 3        | DWW 2    | DWW 1    | DWW 0    | 27h     |

| 30h  | AWBR          | AWB7           | AWB6            | AWB5         | AWB4    | AWB3         | AWB2     | AWB1     | AWB0     | EFh     |

| 31h  | DWHR          | DWH7           | DWH6            | DWH5         | DWH4    | DWH3         | DWH2     | DWH1     | DWH0     | EFh     |

| 40h  | AWLR          |                |                 | AWL5         | AWL4    | AWL3         | AWL2     | AWL1     | AWL0     | 00h     |

| 50h  | AWTR          | AWT7           | AWT6            | AWT5         | AWT4    | AWT3         | AWT2     | AWT1     | AWT0     | 00h     |

| 60h  | CURX          |                |                 | CURX5        | CURX4   | CURX3        | CURX2    | CURX1    | CURX0    | 00h     |

| 61h  | BGSG          |                |                 | BGSG5        | BGSG4   | BGSG3        | BGSG2    | BGSG1    | BGSG0    | 00h     |

| 62h  | ED <b>S</b> G | EDSG7          | EDSG6           | EDSG5        | EDSG4   | EDSG3        | EDSG2    | EDSG1    | EDSG0    | 00h     |

| 70h  | CURY          | CURY7          | CURY6           | CURY5        | CURY4   | CURY3        | CURY2    | CURY1    | CURY0    | 00h     |

| 71h  | BGCM          | BGCM7          | BGCM6           | BGCM5        | BGCM4   | BGCM3        | BGCM2    | BGCM1    | BGCM0    | 00h     |

| 72h  | EDCM          | EDCM7          | EDCM6           | EDCM5        | EDCM4   | EDCM3        | EDCM2    | EDCM1    | EDCM0    | 00h     |

| 80h  | BTMR          | BLKT7          | BLKT6           | BLKT5        | BLKT4   | BLKT3        | BLKT2    | BLKT1    | BLKT0    | 00h     |

| 90h  | ITCR          | ITC7           | ITC6            | ITC5         | ITC4    | ITC3         | ITC2     | ITC1     | ITC0     | 00h     |

| A0h  | KSCR1         | KEY_EN         | KEY4X8          | KSAMP1       | KSAMP0  | LKEY_EN      | KF2      | KF1      | KF0      | 00h     |

| A1h  | KSCR2         | KWAK_EN        |                 |              |         | LKEY_T1      | LKEY_T0  | KEYNO1   | KEYNO0   | 00h     |

| A2h  | KSDR0         | KSD07          | KSD06           | KSD05        | KSD04   | KSD03        | KSD02    | KSD01    | KSD00    | 00h     |

| A3h  | KSDR1         | KSD17          | KSD16           | KSD15        | KSD14   | KSD13        | KSD12    | KSD11    | KSD10    | 00h     |

| A4h  | KSDR2         | KSD27          | KSD26           | KSD25        | KSD24   | KSD23        | KSD22    | KSD21    | KSD20    | 00h     |

| B0h  | MWCR          | MWD7           | MWD6            | MWD5         | MWD4    | MWD3         | MWD2     | MWD1     | MWD0     |         |

| B1h  | MRCR          | MRD7           | MRD6            | MRD5         | MRD4    | MRD3         | MRD2     | MRD1     | MRD0     |         |

| C0h  | TPCR1         | TP_EN          | TP_SMP2         | TP_SMP1      | TP_SMP0 | TPWAK<br>_EN | ACLK2    | ACLK1    | ACLKO    | 00h     |

| C1h  | TPXR          | TPX9           | TPX8            | TPX7         | TPX6    | TPX5         | TPX4     | TPX3     | TPX2     | 00h     |

| C2h  | TPYR          | TPY9           | TPY8            | TPY7         | TPY6    | TPY5         | TPY4     | TPY3     | TPY2     | 00h     |

| C3h  | TPZR          | TPX1           | TPX0            |              |         | TPY1         | TPY0     |          |          | 00h     |

| C4h  | TPCR2         | MTP_MD         |                 |              |         |              |          | MTP_PH1  | MTP_PH2  | 00h     |

| D0h  | PCR           | PWM_EN         | PWM_DIS_<br>LEV |              |         | PCLK_R3      | PCLK_R2  | PCLK_R1  | PCLK_R0  | 00h     |

| D1h  | PDCR          | PDUTY7         | PDUTY6          | PDUTY5       | PDUTY4  | PDUTY3       | PDUTY2   | PDUTY1   | PDUTY0   | 00h     |

| E0h  | PNTR          | PND7           | PND6            | PND5         | PND4    | PND3         | PND2     | PND1     | PND0     | 00h     |

| F0h  | FNCR          | ISO8859_E<br>N |                 |              |         | MCLR         | ASC      | ASC_SEL1 | ASC_SEL0 | 00h     |

| F1h  | FVHT          | FH1            | FH0             | FV1          | FV0     |              |          |          |          | 00h     |

٠

# 6. Register Description

STATUS Register (RS = 1, ZWR = 1)

| Bit | Description                                                                                                                                               | Access |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 7   | <ul> <li>Memory Write Busy Flag</li> <li>0 : Not busy.</li> <li>1 : Busy, when font write or memory clear cycle is running, the busy flag = 1.</li> </ul> | R      |

| 6   | SCAN_BUSY<br>0 : Not busy.<br>1 : When driver scan logic is not idle(i.e. XCK is active), SCAN_BUSY<br>= 1.                                               | R      |

| 5   | SLEEP<br>0 : Normal mode.<br>1 : Sleep mode.                                                                                                              | R      |

| 4-3 | NA                                                                                                                                                        | R      |

| 2   | Wakeup Status bit<br>(The same with REG[0Fh] Bit-2.)                                                                                                      | R      |

| 1   | KS Status bit<br>(The same with REG[0Fh] Bit-1.)                                                                                                          | R      |

| 0   | TP Status bit<br>(The same with REG[0Fh] Bit-0.)                                                                                                          | R      |

### REG [00h] Whole Chip LCD Controller Register (WLCR)

| Bit | Description                                                                                                                                                                                                                                                                                                              | Default | Access |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7   | <ul> <li>Power Mode</li> <li>0 : Normal Mode. All of the functions of RA8806 are available in this mode.</li> <li>1 : Sleep Mode. When RA8806 is in Sleep mode, all of functions enter off mode, except the wake-up trigger block. If wake-up event occurred, RA8806 would wake-up and return to Normal mode.</li> </ul> | 0       | R/W    |

| 6   | Linear Decode mode<br>This bit is used to define the Font ROM address mapping rule. The<br>standard product is set to 0. And 1 for special application that when<br>user a want to create a new Mask Code.<br>0 : BIG5/GB ROM mapping rule.<br>1 : User-defined ROM mapping rule.                                        | 0       | R/W    |

| 5   | <ul> <li>Software Reset</li> <li>0 : Normal Operation.</li> <li>1 : Reset all registers except the contents of Display Data RAM (Only work at Normal mode). When this bit set to "1", the next MPU cycle for RA8806 have to wait 3 clocks at least.</li> </ul>                                                           | 0       | R/W    |

| 4   | Reserved                                                                                                                                                                                                                                                                                                                 | 0       | R      |

| 3   | <ul> <li>Text Mode Selection</li> <li>0 : Graphical Mode. The written data will be treated as a bit-map pattern.</li> <li>1 : Text Mode. The written data will be treated as an ASCII, BIG5 or GB code.</li> </ul>                                                                                                       | 0       | R/W    |

| 2 | Set Display On/Off Selection<br>The bit is used to control LCD Driver Interface signal – "DISP_OFF".<br>0 : DISP_OFF pin output low(Display Off).<br>1 : DISP_OFF pin output high(Display On). | 0 | R/W |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|

| 1 | Blink Mode Selection<br>0 : Normal Display.<br>1 : Blink Full Screen. The blink time is set by register BTMR.                                                                                  | 0 | R/W |

| 0 | Inverse Mode Selection<br>0 : Normal Display.<br>1 : Inverse Full Screen. It will cause the display inversed.                                                                                  | 0 | R/W |

LCD MODULE

#### REG [01h] Misc. Register (MISC)

| Bit | Description                                                                                                                                                                                                                               | Default | Access |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7   | Eliminating Flicker<br>1 : Eliminating flicker mode, scan will auto-pending when busy.<br>0 : Normal mode.                                                                                                                                | 0       | R/W    |

| 6   | <ul> <li>Clock Output (Pin CLK_OUT) Control</li> <li>1 : The pin "CLK_OUT" indicates the SLEEP state of Status Register(0: Normal Mode, 1: Sleep Mode).</li> <li>0 : The pin "CLK_OUT" is the output of Internal system clock.</li> </ul> | 0       | R/W    |

| 5   | Busy Polarity (for "BUSY" pin)<br>1 : Set Active High.<br>0 : Set Active Low.                                                                                                                                                             | 0       | R/W    |

| 4   | Interrupt Polarity (for "INT" pin)<br>1 : Set Active High.<br>0 : Set Active Low.                                                                                                                                                         | 0       | R/W    |

| 3-2 | Driver Clock Selection<br>These two bits are used to select the clock frequency of XCK.<br>0 0 : XCK = CLK/8<br>0 1 : XCK = CLK/4 (Default)<br>1 0 : XCK = CLK/2<br>1 1 : XCK = CLK<br>The "CLK" means system clock.                      | 01      | R/W    |

| 1   | SEG Scan Direction(SDIR)<br>0 : SEG order is 0 ~ 319.<br>1 : SEG order is 319 ~ 0.                                                                                                                                                        | 0       | R/W    |

| 0   | COM Scan Direction(CDIR)<br>0 : COM order 0 ~ 239.<br>1 : COM order 239 ~ 0.                                                                                                                                                              | 0       | R/W    |

#### REG [03h] Advance Display Setup Register (ADSR)

| Bit | Description                                                                               | Default | Access |

|-----|-------------------------------------------------------------------------------------------|---------|--------|

| 7   | Scroll Function Pending<br>1 : Scroll function pending<br>0 : Scroll function keep active | 0       | R/W    |

|     | Note: When SCR_HV(Bit-1) and SCR_EN(Bit-0) are changed, the<br>function does not support. |         |        |

| 6-4 | Reserved                                                                                  | 000     | R      |

SHEN ZHEN ET TECHCHNOLOGY CO., LTD.Tel: 86-755- 8883444561332400Fax: 86-755-88834446E-mail: east@eastet.comHttp://www.eastet.com

| 3 | BIT_ORDER(Set driver data output bit order) <ol> <li>Inverse driver output data order(Bit-7 to Bit-0, Bit-6 to Bit-1 and so on)</li> <li>Normal Mode</li> </ol>                                                                         | 0 | R/W |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|

| 2 | SCR_DIR(Scroll Direction)<br>When SCR_HV = 0(Horizontal Scroll)<br>0 : Left $\rightarrow$ Right.<br>1 : Right $\rightarrow$ Left.<br>When SCR_HV = 1(Vertical Scroll)<br>0 : Top $\rightarrow$ Bottom.<br>1 : Bottom $\rightarrow$ Top. | 0 | R/W |

| 1 | SCR_HV(Scroll Horizontal/Vertical)<br>0 : Segment Scrolling(Horizontal).<br>1 : Common Scrolling(Vertical).                                                                                                                             | 0 | R/W |

| 0 | SCR_EN(Scroll Enable)<br>1 : Scroll function enable.<br>0 : Scroll function disable.                                                                                                                                                    | 0 | R/W |

REG [0Fh] Interrupt Setup and Status Register (INTR)

| Bit | Description                                                                                                                                                                          | Default | Access |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7   | Reserved                                                                                                                                                                             | 0       | R      |

| 6   | Wakeup Interrupt Mask<br>1 : Enable wake-up Interrupt.<br>0 : Disable wake-up Interrupt.                                                                                             | 0       | R/W    |

| 5   | Key-Scan Interrupt Mask         1 : Enable Key-Scan Interrupt.         0 : Disable Key-Scan Interrupt.                                                                               | 0       | R/W    |

| 4   | Touch Panel Interrupt Mask<br>1 : Generate interrupt output if touch panel was detected.<br>0 : Don't generate interrupt output if touch panel was detected.                         | 0       | R/W    |

| 3   | Touch Panel Event(Only activate in TP Manual mode)<br>1 : Touch panel is touched.<br>0 : Touch panel is not touched.                                                                 | 0       | R      |

| 2   | Wakeup Interrupt Status bit<br>1 : Interrupt that indicate wake-up event happen from Sleep mode.<br>0 : No wake-up interrupt happen.<br>User must write "0" to clear the Status bit. | 0       | R/W    |

| 1   | Key-Scan Interrupt Status bit<br>1 : Key-Scan Detects Key Input.<br>0 : Key-Scan doesn't Detect Key Input.<br>User must write "0" to clear the Status bit.                           | 0       | R/W    |

| 0   | Touch Panel Detect Status bit<br>1 : Touch Panel Touched.<br>0 : Touch Panel Untouched.<br>User must write "0" to clear the Status bit.                                              | 0       | R/W    |

#### REG [10h] Whole Chip Cursor Control Register (WCCR)

| Bit | Description                                                                                                                                                                                                         | Default | Access |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7   | CUR_INC (Auto Increase Cursor Position in Reading/Writing DDRAM<br>Operation.)<br>1 : Disable.<br>0 : Enable(Auto Increase).                                                                                        | 0       | R/W    |

| 6   | <ul> <li>FULL_OFS (Full-size and Half-size Character Alignment)</li> <li>1 : Enable, in Full-size and Half-size character mixed mode. Chinese always start at full-size alignment.</li> <li>0 : Disable.</li> </ul> | 0       | R/W    |

| 5   | <ul> <li>Reversed Data Write mode</li> <li>0 : Store Current Data to DDRAM Directly.</li> <li>1 : Store Current Data to DDRAM Inversely.(i.e. 01101101→<br/>10010010)</li> </ul>                                    | 0       | R/W    |

| 4   | Bold Font (Character Mode Only)<br>1 : Bold Font<br>0 : Normal Font                                                                                                                                                 | 0       | R/W    |

| 3   | Font Rotate mode(T90DEG)<br>1 : Font rotates 90 degree. (See Section 6-10-4 for detail)<br>0 : Normal font.                                                                                                         | 0       | R/W    |

| 2   | Cursor Display<br>1 : Set Cursor Display On.<br>0 : Set Cursor Display Off.                                                                                                                                         | 0       | R/W    |

| 1   | Cursor Blinking<br>1 : Blink Cursor. The blink time is determined by register BTMR.<br>0 : Normal.                                                                                                                  | 0       | R/W    |

| 0   | Reserved                                                                                                                                                                                                            | 0       | R      |

### REG [11h] Cursor Height and Word Interval Register (CHWI)

| Bit | Description                                                                                                                                                                                                                                                                                           | Default | Access |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7-4 | Set Cursor Height<br>$0000 \text{ b} \rightarrow \text{Height} = 1 \text{ pixel.}$<br>$0001 \text{ b} \rightarrow \text{Height} = 2 \text{ pixels.}$<br>$0010 \text{ b} \rightarrow \text{Height} = 3 \text{ pixels.}$<br>$\vdots$<br>$1111 \text{ b} \rightarrow \text{Height} = 16 \text{ pixels.}$ | 0000    | R/W    |

|     | <b>Note:</b> In normal font, the cursor width fixed to one byte(8 pixels). And cursor's height is from 1~16pixels that depends on Bit[7:4]. In vertical font, the cursor height fixed to 16 pixels, and width is from 1~8 pixels that depends on Bit[6:4].                                            |         |        |

| 3-0 | Set Line Gap<br>0000 b → Gap = 1 pixel.<br>0001 b → Gap = 2 pixels.<br>0010 b → Gap = 3 pixels.<br>1111 b → Gap = 16 pixels.                                                                                                                                                                          | 0000    | R/W    |

### REG [12h] Memory Access Mode Register (MAMR)

LCD MODULE

| Bit | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Default | Access |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7   | <ul> <li>Cursor Auto Shifting Direction</li> <li>0 : Cursor moves horizontally (left to right) first then vertically (top to down).</li> <li>1 : Cursor moves vertically first then horizontally.</li> <li>Note: In graphic mode, the cursor moving is treated as unit of bytes in horizontal direction. At vertical direction, it's treated as unit of bit. At text mode, the bit is ignored, and the cursor moving is always in horizontal direction.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0       | R/W    |

| 6-4 | Display Layer and Display Mode Selection         0 0 0 : Gray Mode. In this mode, each pixel consists with 2 continuous bits in memory data. With the FRC methodology, 4-level-gray mode is implemented. The bit mapping is list as below.         bit1       bit0       Gray         0       0       Level1 (Lightest)         0       1       Level2         1       0       Level3         1       1       Level4 (Darkest)         Note: Gray mode doesn't support text-mode input.         0       0       1: Show DDRAM1 data on screen.         0       1 : Show DRAM2 data on screen.       0         0       1 : Show Two Layer Mode. The display rule depends on Bit-3 and Bit-2 as following.         1       1 0: Extension Mode (1), the panel will show both DDRAM1 and DDRAM2 data on the screen. The RA8806 is available for 640x240 pixels panel.         1       1 : Extension Mode (2), the panel will show both DDRAM1 and DDRAM2 on the screen. The RA8806 is available for 320x480 pixels panel. | 001     | R/W    |

| 3-2 | Two Layer Mode Selection<br>Combine the data of DDRAM1 and DDRAM2 on the screen when<br>Bit[6:4] is set as "011".<br>0 0 : DDRAM1 "OR" DDRAM2.<br>0 1 : DDRAM1 "XOR" DDRAM2.<br>1 0 : DDRAM1 "NOR" DDRAM2.<br>1 1 : DDRAM1 "AND" DDRAM2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 00      | R/W    |

| 1-0 | MPU Read/Write Layer Selection<br>0 0 : Access CGRAM.(512Byte)<br>0 1 : Access DDRAM1.<br>1 0 : Access DDRAM2.<br>1 1 : Access both DDRAM1 and DDRAM2 concurrently                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 01      | R/W    |

#### REG [20h] Active Window Right Register (AWRR)

| Bit | Description                                                                                                | Default | Access |

|-----|------------------------------------------------------------------------------------------------------------|---------|--------|

| 7-6 | Reserved                                                                                                   | 00      | R      |

| 5-0 | Active Window Right Position → Segment-Right                                                               |         |        |

|     | <b>Note:</b> AWRR must be equal or larger then AWLR, and less or equal then the value 27h (40 in decimal). | 27h     | R/W    |

#### Note:

REG[20h, 30h, 40h, and 50h] are used to dominate an active window for line/row changing when writing data. Users can use these four registers to set the left/right/top/bottom boundary of active window. When data goes beyond the right boundary of it, the cursor will automatically change the next line to write data. It will move to the left boundary of new line in active window. When the data comes to the right-bottom corner, the next write will cause the cursor to move to the left-top corner.

#### **REG [21h]** Display Window Width Register (DWWR)

| Bit | Description                                                       | Default | Access |

|-----|-------------------------------------------------------------------|---------|--------|

| 7-6 | Reserved                                                          | 00      | R      |

|     | Set Display Window Width Position $\rightarrow$ Segment-Width     |         |        |

| 5-0 | Segment-Right = (Segment Number / 8) – 1                          | 27h     | R/W    |

|     | If LCD panel resolution is 320x240, the value of the register is: |         |        |

|     | ( 320 / 8 ) - 1 = 39 = 27h                                        |         |        |

#### Note:

REG[21h, 31h] are used to set Display Window Resolution. Users can set the viewing scope of Display Data RAM. Column width (DWWR) of RA8806 can be set between  $0h \sim 27h$ , and Row height (DWHR) can be set between  $0h \sim EFh$ .

#### REG [30h] Active Window Bottom Register (AWBR)

| Bit | Description                                                                                           | Default | Access |

|-----|-------------------------------------------------------------------------------------------------------|---------|--------|

|     | Active Window Bottom Position → Common-Bottom                                                         |         |        |

| 7-0 | Note: AWBR must be equal or larger then AWTR, and less or equal<br>then the value EFh(239 in decimal) | EFh     | R/W    |

#### REG [31h] Display Window Height Register (DWHR)

| Bit | Description                                                       | Default | Access |

|-----|-------------------------------------------------------------------|---------|--------|

| 7-0 | Display Window Height Position → Common- Height                   | EFh     | R/W    |

|     | Common_ Height = LCD Common Number –1                             |         |        |

|     | If LCD panel resolution is 320x240, the value of the register is: |         |        |

|     | 240 – 1 = 239 = EFh                                               |         |        |

#### REG [40h] Active Window Left Register (AWLR)

| Bit | Description                                                                                   | Default | Access |

|-----|-----------------------------------------------------------------------------------------------|---------|--------|

| 7-6 | Reserved                                                                                      | 00      | R      |

|     | Active Window Left Position → Segment-Left                                                    |         |        |

| 5-0 | <b>Note:</b> AWLR must be equal or less then AWRR, and less then the value 27h(39 in decimal) | 00h     | R/W    |

#### REG [50h] Active Window Top Register (AWTR)

| Bit | Description                                                                                                                            | Default | Access |

|-----|----------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7-0 | Active Window Top Position → Common-Top<br>Note: AWTR must be equal or less then AWBR, and less then the<br>value EFh (239 in decimal) | 00h     | R/W    |

#### REG [60h] Cursor Position X Register (CURX)

| Bit | Description                                                                                                                                                                                                                                                                                                                                                                                          | Default | Access |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7-6 | Reserved                                                                                                                                                                                                                                                                                                                                                                                             | 00      | R      |

| 5-0 | Cursor Position of Segment / RAM0 Address[4:0]<br>Define the cursor address of segment, a value from 0h ~ 27h(0 ~ 40 in<br>decimal)<br>When CGRAM write mode is selected (REG[12h] Bit[1:0] = 00b), the<br>Bit[4:0] is the address for writing bit-map data. When create a full-size<br>font, normally set to 0. When create an odd half-size font, normally set<br>to 0, and set 10h for even font. | 00h     | R/W    |

#### REG [61h] Begin Segment Position Register of Scrolling (BGSG)

| Bit | Description                                                                                                                                                                                                                                                                               | Default | Access |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7-6 | Reserved                                                                                                                                                                                                                                                                                  | 00      | R      |

|     | Segment Start Position of Scrolling Mode                                                                                                                                                                                                                                                  |         |        |

| 5-0 | REG[61h] defines the start position (left boundary) of scroll window, it must be a value that less or equal to the REG[62h], which defines the end position(right boundary) of scroll window. Also it must be less then the value of 27h (40 in decimal), for the Display Data RAM limit. | 00h     | R/W    |

Note:

REG[61h, 62h, 71h, 72h] dominate a named scroll window for scroll function. They must be set before the scroll function is enable.

#### REG [62h] End Segment Position Register of Scrolling (EDSG)

| Bit | Description                                                                                                                                                                                                                                                                                      | Default | Access |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7-6 | Reserved                                                                                                                                                                                                                                                                                         | 00      | R      |

|     | Segment End Position of Scrolling Mode                                                                                                                                                                                                                                                           |         |        |

| 5-0 | REG[62h] defines the end position(right boundary) of scroll window, it must be a value that larger or equal to the REG[61h], which defines the end position(left boundary) of scroll window. Also it must be less or equal then the value of 27h(40 in decimal), for the Display Data RAM limit. | 00h     | R/W    |

#### REG [70h] Cursor Position Y Register (CURY)

| Bit | Description                                                                                                                                                                                                                                                                                    | Default | Access |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7-0 | Cursor Position of Common / RAM0 Address[8:5]<br>Define the cursor address of common, a value from 0h ~ EFh(0 ~ 239<br>in decimal).<br>When CGRAM write mode is selected (REG[12h] Bit[1:0] = 00b), the<br>Bit[3:0] is indicate which font will be created. And Bit[7:4] are not<br>available. | 00h     | R/W    |

#### REG [71h] Scrolling Action Range Begin Common Register (BGCM)

| Bit | Description                                                                                                                                                                                                                                                                                                                                   | Default | Access |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7-0 | Common Start Position of Scrolling Mode<br>REG[71h] defines the begin position(top boundary) of scroll window, it<br>must be a value that less or equal to the REG[72h], which defines the<br>end position(bottom boundary) of scroll window. Also it must be less<br>then the value of EFh (239 in decimal), for the Display Data RAM limit. | 00h     | R/W    |

#### REG [72h] Scrolling Action Range END Common Register (EDCM)

| Bit | Description                                                                                                                                                                                                                                                                                                                                                       | Default | Access |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7-0 | <b>Common Ending Position of Scrolling Mode</b><br>REG[72h] defines the end position(bottom boundary) of scroll window,<br>it must be a value that larger or equal to the REG[71h], which defines<br>the end position(top boundary) of scroll window. Also it must be less<br>or equal then the value of EFh (239 in decimal), for the Display Data<br>RAM limit. | 00h     | R/W    |

#### REG [80h] Blink Time Register (BTMR)

| Bit | Description                                                      | Default | Access |

|-----|------------------------------------------------------------------|---------|--------|

| 7-0 | Cursor Blink Time and Scroll Time                                |         |        |

|     | Blinking Time = Bit[7:0] x (Frame width)                         | 00h     | R/W    |

|     | Frame width = 1/Frame Rate                                       |         |        |

|     | The Frame Rate is depends on the DWWR and DWHR and ITCR setting. |         |        |

#### Notes:

- 1. The Setting also determines the scroll moving speed.

- The Frame width is the time that the controller scan whole panel, it depends on the system clock frequency, setting of display window, driver interface (4-bits/8-bits), Idle time (ITCR), and dual mode or gray scale mode, etc.

#### **REG [90h]** Idle Time Counter Register (ITCR)

| Bit | Description                                                                                                                                                                                     | Default | Access |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

|     | Idle Time Setting, in count of system clock.<br>The value can determine the scan time of each COM of the LCD.                                                                                   |         |        |

|     | COM_PRD = ( COM_SCAN + ITCR) x XCK_PRD                                                                                                                                                          |         |        |

|     | In which,                                                                                                                                                                                       |         |        |

|     | COM_SCAN = (SEG_NO/LD_WIDTH) x (1 + EXT_MD)                                                                                                                                                     |         |        |

|     | XCK_PRD = 1 / XCK                                                                                                                                                                               |         |        |

|     | COM_PRD: The finally scan period for each COM(Unit : ns).                                                                                                                                       |         |        |

| 7-0 | COM_SCAN: The really scan time for each COM.                                                                                                                                                    | 00h     | R/W    |

|     | XCK_PRD: One cycle time of XCK. XCK is depends on the system<br>clock(CLK) and REG[01h] Bit[3:2]. If system clock is<br>8MHz, REG[01h] Bit[3:2] = 10b, then XCK_PRD = 250ns.                    |         |        |

|     | SEG_NO: Segment number, i.e. 240x160 panel, SEG_NO = 240.                                                                                                                                       |         |        |

|     | EXT_MD: In extension mode1 or 2(REG[12h] Bit[6:4] = 111b or 110b),<br>the EXT_MD = 1, otherwise EXT_MD = 0.                                                                                     |         |        |

|     | LD_WIDTH: Driver data width. If LCD driver data bus is 4-bits then<br>LD_WIDTH = 4. If LCD driver data bus is 8-bits then<br>LD_WIDTH = 8. Please refer pin "DW" description of<br>Section 4-3. |         |        |

REG [A0h] Key-Scan Control Register 1 (KSCR1)

| Bit | Description                                                                                                                                | Default | Access |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7   | Key-Scan Enable Bit<br>1 : Enable.<br>0 : Disable.                                                                                         | 0       | R/W    |

| 6   | Key-Scan Matrix Selection<br>1 : 4x8 Matrix(KOUT[3:0] is used, KOUT[7:4] please keep floating)<br>0 : 8x8 Matrix(KOUT[7:0] is used)        | 0       | R/W    |

| 5-4 | Key-Scan Data Sampling Times<br>De-bounce times of scan frequency.<br>0 0 : 4<br>0 1 : 8<br>1 0 : 16<br>1 1 : 32                           | 00      | R/W    |

| 3   | LNGKEY_EN : Long Time Key Function Enable<br>LNGKEY_EN = 0 → Long key function is disable.<br>LNGKEY_EN = 1 → Long key function is enable. | 0       | R/W    |

| 1   |   | tem | cloc |     | equency.<br>10MHz, then the              | related Key-S           | Scan timing are         | e as |     |     |

|-----|---|-----|------|-----|------------------------------------------|-------------------------|-------------------------|------|-----|-----|

|     | ۲ | (F2 | KF1  | KF0 | Key-Scan<br>Pulse Width<br>(KOUT period) | Key-Scan<br>Cycle (4x8) | Key-Scan<br>Cycle (8x8) |      |     |     |

|     |   | 0   | 0    | 0   | 16µs                                     | 64µs                    | 128µs                   |      |     |     |

| 2-0 |   | 0   | 0    | 1   | 32µs                                     | 128µs                   | 256µs                   |      | 000 | R/W |

|     |   | 0   | 1    | 0   | 64µs                                     | 256µs                   | 512µs                   |      |     |     |

|     |   | 0   | 1    | 1   | 128µs                                    | 512µs                   | 1.024ms                 |      |     |     |

|     |   | 1   | 0    | 0   | 256µs                                    | 1.024ms                 | 2.048ms                 |      |     |     |

|     |   | 1   | 0    | 1   | 512µs                                    | 2.048ms                 | 4.096ms                 |      |     |     |

|     |   | 1   | 1    | 0   | 1.024ms                                  | 4.096ms                 | 8.192ms                 |      |     |     |

|     |   | 1   | 1    | 1   | 2.048ms                                  | 8.192ms                 | 16.384ms                |      |     |     |

### REG [A1h] Key-Scan Controller Register 2(KSCR2)

| Bit | Description                                                                                                                                                                                                                                           | Default | Access |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7   | Key-Scan Wakeup Function Enable Bit<br>0: Key-Scan Wakeup function is disable.<br>1: KEY-SCAN Wakeup function is enable.                                                                                                                              | 0       | R/W    |

| 6-4 | Reserved                                                                                                                                                                                                                                              | 000     | R      |

| 3-2 | Long Key Timing Adjustment<br>00 : About 0.625sec(for 8MHz Clock source)<br>01 : About 1.25sec(for 8MHz Clock source)<br>10 : About 1.875 sec(for 8MHz Clock source)<br>11 : About 2.5 sec(for 8MHz Clock source)                                     | 00      | R/W    |

| 1-0 | Numbers of Key Hit.<br>00 : No key is pressed<br>01 : One key is pressed, read REG[A2h] for the key number.<br>10 : Two key is pressed, read REG[A2h ~ A3h] for the key number.<br>11 : Three key is pressed, read REG[A2h ~ A4h] for the key number. | 00      | R      |

### REG [A2h ~ A4h] Key-Scan Data Register (KSDR0 ~ 2)

| Bit | Description                                                                                                  | Default | Access |

|-----|--------------------------------------------------------------------------------------------------------------|---------|--------|

| 7-0 | Key Strobe Data<br>The corresponding key number that is pressed. Please reference<br>Section 6-5 "Key-Scan". | 00h     | R      |

#### REG [B0h] Memory Write Command Register (MWCR)

| Bit | Description                                                                                    | Default | Access |

|-----|------------------------------------------------------------------------------------------------|---------|--------|

|     | Memory data write command from the cursor position.                                            |         |        |

| 7-0 | <b>Note:</b> Write memory data, user must write the MWCR command first, then write DATA cycle. | NA      | R/W    |

REG [B1h] Memory Read Command Register (MRCR)

Access

| Bit | Description                                                                                                                                                                                                  | Default |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|     | Memory data read command from the cursor position.                                                                                                                                                           |         |

| 7-0 | <b>Note:</b> Memory read cycle in text mode, the cursor move in same behavior like graphic mode. B1h will perform a pre-read function. So the cursor position will increase after the MRCR command is write. | NA      |

NA R/W

#### REG [C0h] Touch Panel Control Register 1 (TPCR1)

LCD MODULE

| Bit | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Default | Access |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7   | Touch Panel Enable Bit<br>1 : Enable.<br>0 : Disable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0       | R/W    |

| 6-4 | <ul> <li>TP Sample Time Adjusting</li> <li>000 : Wait 50µs for ADC data ready.</li> <li>001 : Wait 100µs for ADC data ready.</li> <li>010 : Wait 200µs for ADC data ready.</li> <li>011 : Wait 400µs for ADC data ready.</li> <li>100 : Wait 800µs for ADC data ready.</li> <li>101 : Wait 1.6ms for ADC data ready.</li> <li>101 : Wait 1.6ms for ADC data ready.</li> <li>110 : Wait 3.2ms for ADC data ready.</li> <li>111 : Wait 6.4ms for ADC data ready.</li> <li>Note: When touch panel detects the Touch event, to avoid the signal instability, the sampled time is delayed to wait the signal stable. The TP Sample Time Adjusting and ADC Clock Convert Speed relation just refer to Section 6-4-3.</li> </ul> | 000     | R/W    |

| 3   | <ul> <li>Touch Panel Wake-up Enable:</li> <li>1 : Touch panel can wake-up the Sleep mode(At the condition that ADC is enabled).</li> <li>0 : Disable the touch panel wake-up function</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0       | R/W    |

| 2-0 | ADC Clock Convert Speed<br>0 0 0 : CLK / 4<br>0 0 1 : CLK / 8<br>0 1 0 : CLK / 16<br>0 1 1 : CLK / 32<br>1 0 0 : CLK / 64<br>1 0 1 : CLK / 128<br>1 1 0 : CLK / 256<br>1 1 1 : CLK / 512<br>The "CLK" means system clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 000     | R/W    |

REG [C1h] Touch Panel X High Byte Data Register (TPXR)

| Bit | Description                          | Default | Access |

|-----|--------------------------------------|---------|--------|

| 7-0 | Touch Panel X Data Bit[9:2](Segment) | 00h     | R      |

#### REG [C2h] Touch Panel Y High Byte Data Register (TPYR)

| Bit | Description                          | Default | Access |

|-----|--------------------------------------|---------|--------|

| 7-0 | Touch Panel Y Data Bit[9:2] (Common) | 00h     | R      |

REG [C3h] Touch Panel Segment/Common Low Byte Data Register (TPZR)

| Bit | Description                           | Default | Access |

|-----|---------------------------------------|---------|--------|

| 7-4 | Reserved                              | 0000    | R      |

| 3-2 | Touch Panel Y Data Bit[1:0] (Common)  | 00      | R      |

| 1-0 | Touch Panel X Data Bit[1:0] (Segment) | 00      | R      |

#### REG [C4h] Touch Panel Control Register 2 (TPCR2)

| Bit | Description                                                                                                                                                                                                                                                                                                                                                                             | Default | Access |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7   | <b>TP Manual Mode Enable</b><br>1 : Using the manual mode.<br>0 : Auto mode.                                                                                                                                                                                                                                                                                                            | 0       | R/W    |