# Infrared Filter Switch Driver

#### **Features**

- 1.8V to 5.5V operation voltage range

- 1.8V input pulse driving

- Ultra low saturation voltage

- 0.36V@200mA, VDD=5V

- 0.57V@300mA, VDD=5V

- Ultra-low standby current

- Build-in MOSFET shoot through protection circuit to prevent from device damage by fast output transient

- SOT23-6L package

- A/B versions selectable

- Ver. A in dual-wire control

- Ver. B in one-shot mode control

#### **Applications**

- IR surveillance camera filter driver

- Body worn video

- Wearable IR camera

- Smart locker

#### Description

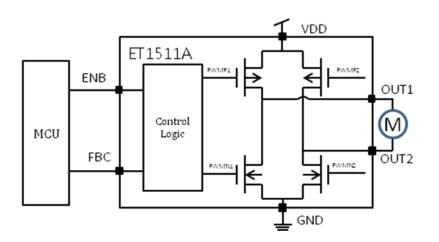

ET1511A/B is an infrared filter switch driver IC which designed for filter control driving in IR cut module in camera. ET1511A/B could functions as a one-channel, low output headroom voltage, bi-directional H-bridge driver by appropriate input controls. Build-in protection diode circuit can minimize the disturbance caused by the feedback current when IR cut is shutdown or ESD transient pulses appeared.

The output driver impedance of ET1511A/B is  $2\Omega$  in typical. The current driven through the actuator is determined by the impedance of the IR cut. In case of 5V power supply, the 300mA driving current through actuator is around 300mA with 0.48V output voltage headroom.

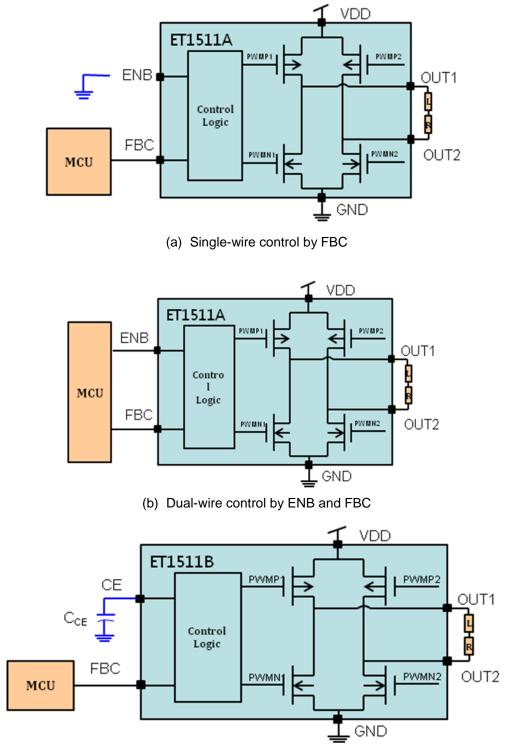

There are 2 versions (Ver. A and Ver. B) of ET1511, which offers to support single-wire input control, dual-wire input control, and one-shot control. In one-shot control mode, the on time could be configured by external capacitor.

#### Simplified Application Circuit

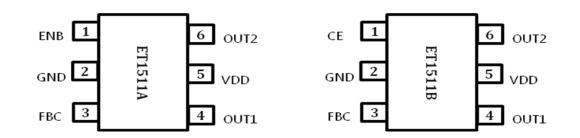

# Pin Assignments

#### **Pin Description**

| Pin<br>Name | Pin No.        | I/O | DESCRIPTION                                                                                                                                                    |  |

|-------------|----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ENB         | 1<br>(ET1511A) | I   | <ul> <li>ENB input.</li> <li>Single-wire control mode, ENB is active low.</li> <li>Dual-wire control mode, ENB and FBC are used for 2-wire control.</li> </ul> |  |

| CE          | 1<br>(ET1511B) | I   | Connect to external capacitor. (One-shot mode control only.)                                                                                                   |  |

| GND         | 2              | Р   | System ground.                                                                                                                                                 |  |

| FBC         | 3              | Ι   | Forward/Backward control                                                                                                                                       |  |

| OUT1        | 4              | 0   | Half-bridge driver output 1                                                                                                                                    |  |

| VDD         | 5              | Р   | Power supply                                                                                                                                                   |  |

| OUT2        | 6              | 0   | Half-bridge driver output 2                                                                                                                                    |  |

#### **Ordering Information**

| Product ID       | Package  | Packing / MPQ                               | Comments |

|------------------|----------|---------------------------------------------|----------|

| ET1511A          | SOT23-6L | 3000 Units / Reel<br>3000 Units / Small Box | Green    |

| ET1511B SOT23-6L |          | 3000 Units / Reel<br>3000 Units / Small Box | Green    |

#### **Marking Information**

Marking Information Line 1 : Product Name Line 2 : Tracking Number

### Absolute Maximum Ratings

Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device.

| SYMBOL           | PARAMETER                           | TEST CONDITIONS       | MIN  | MAX | UNIT       |  |

|------------------|-------------------------------------|-----------------------|------|-----|------------|--|

| VDD              | Supply voltage                      | VDD                   | -0.3 | 7.0 | V          |  |

| V <sub>IN</sub>  | Input pin voltage                   | ENB, FBC, CE          | -0.3 | 7.0 | V          |  |

| ΙΟυΤ             | Quitaut aurrant                     | Continuous operation  | _    | 500 | <u>س</u> ۸ |  |

| 1001             | Output current                      | 50% duty pulse output | _    | 600 | mA         |  |

| T <sub>A</sub>   | Operating ambient temperature range |                       |      | 85  | °C         |  |

| T <sub>stg</sub> | Storage temperature range           |                       |      | 150 | °C         |  |

| ESD              | Human Body Model                    |                       | _    | ±2K | v          |  |

| 200              | Charged Device Model                |                       | _    | ±1K | v          |  |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratingsonly, which do not imply functional operation of the device at these or any other conditions beyond those indicated under RecommendedOperating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to network ground terminal.

(3) Power dissipation and thermal limits must be observed.

#### **Recommended Operating Conditions**

| SYMBOL          | PARAMETER         | TEST CONDITIONS      | MIN | MAX | UNIT |

|-----------------|-------------------|----------------------|-----|-----|------|

| VDD             | Supply voltage    | VDD                  | 1.8 | 5.5 | V    |

| V <sub>IN</sub> | Input pin voltage | ENB, FBC, CE         | 0   | 5.5 | V    |

| IOUT            | Output current    | Continuous operation | Ι   | 400 | mA   |

#### **Thermal Information**

| Package Type | Device No. | θ <sub>JA</sub> (℃/₩) | θ <sub>JC</sub> (°C/W) | W\_JT(°C/W) | Exposed Thermal Pad |

|--------------|------------|-----------------------|------------------------|-------------|---------------------|

| SOT23-6L     | ET1511A/B  | 210.3                 | 105                    | 6.1         | None                |

Note 1.1:  $\theta_{JA}$  is simulated n a room temperature ( $T_A=25$ °C), natural convection environment test board, which is constructed with a thermally efficient, 4-layers PCB (2S2P). The measurement is simulated using the JEDEC51-5 thermal measurement standard.

Note 1.2:  $\theta_{JC}$  represents the thermal resistance for the heat flow between the chip junction and the package`stop surface. It`s extracted from the simulation data with obtaining a cold plate on the package top.

Note 1.3:  $\Psi_{JT}$  represents the thermal parameter for the heat flow between the chip junction and the package's top surface center. It's extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-5.

### **Electrical Characteristics**

• VDD=5V, T<sub>A</sub>=25°C (unless otherwise noted)

| SYMBOL            | PARAMETER CONDITION                        |                                | MIN  | TYP  | MAX    | UNIT |

|-------------------|--------------------------------------------|--------------------------------|------|------|--------|------|

| VDD               | Supply voltage                             | Normal operation               | 1.8  | 5.0  | 5.5    | V    |

| I <sub>VDD</sub>  | Quiescent supply                           | ET1511A (No load)              | —    | _    | 12     | uA   |

| VDD               | Quicocont Supply                           | ET1511B (No load)              | —    | _    | 45     | uA   |

| I <sub>TRAN</sub> | Transient current                          | Output transit state           | 0.5  | 0.8  | 1      | mA   |

|                   |                                            | Input control ENB/FBC          |      |      |        |      |

| V <sub>IH</sub>   | Input logic "H"                            | _                              | 1.6  |      | 5.5    | V    |

| V <sub>IL</sub>   | Input logic "L"                            | _                              | 0    |      | 0.2VDD | V    |

| R <sub>PL</sub>   | Input pull-low resistor                    | ENB & FBC pins                 | 120  | 160  | 200    | kΩ   |

|                   |                                            | Driver output OUT1/OUT2        |      |      |        |      |

|                   | Output voltage headroom<br>(upper + lower) | Voltage                        | 3V   | 3.3V | 5V     |      |

| V <sub>OUT</sub>  |                                            | I <sub>OUT</sub> =200mA        | 0.48 | 0.47 | 0.36   | V    |

| VOUT              |                                            | I <sub>OUT</sub> =300mA        | 0.83 | 0.76 | 0.57   | V    |

|                   |                                            | I <sub>OUT</sub> =400mA        | 1.34 | 1.15 | 0.81   | V    |

| T <sub>R</sub>    | Rising transit time                        | From 0.1VDD to 0.9VDD          | _    | 2.5  | 5      | ns   |

| T <sub>F</sub>    | Falling transit time                       | From 0.9VDD to 0.1VDD          | —    | 2    | 4      | ns   |

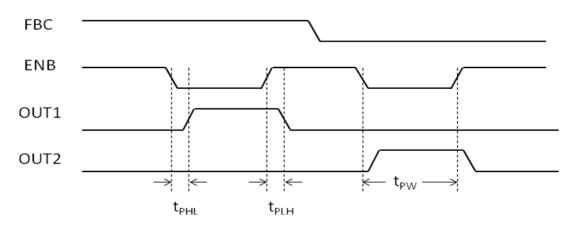

|                   |                                            | Propagation delay time         |      |      |        |      |

| T <sub>PLH</sub>  | ENB (L to H) $\rightarrow$ OUT1/2          | VDD=5V, R <sub>LOAD</sub> =18Ω | _    | 13   | 16     | ns   |

| T <sub>PHL</sub>  | ENB (H to L) $\rightarrow$ OUT1/2          |                                | _    | 24   | 40     | ns   |

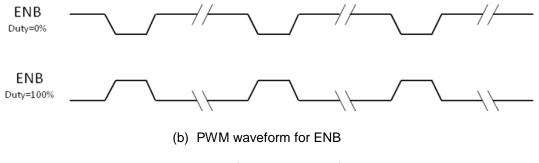

| T <sub>PW</sub>   | Pulse width of ENB                         |                                | 100  | _    | —      | ns   |

| F <sub>MAX</sub>  | Max. frequency of ENB                      |                                | _    | _    | 5      | MHz  |

(a) Propagation delay time between ENB and OUT1/OUT2

Figure1. Waveform timing definition

### **Truth Table and Diagram Controls**

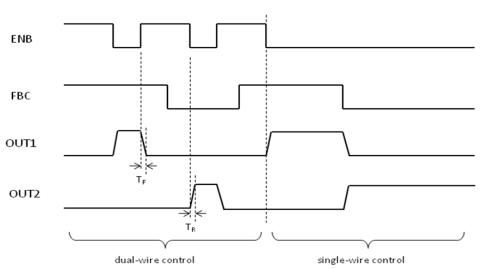

### (1) ET1511A

| Ing | out | Output |      |  |

|-----|-----|--------|------|--|

| ENB | FBC | OUT1   | OUT2 |  |

| Н   |     | L      | L    |  |

| L   | Н   | Н      | L    |  |

| L   | L   | L      | Н    |  |

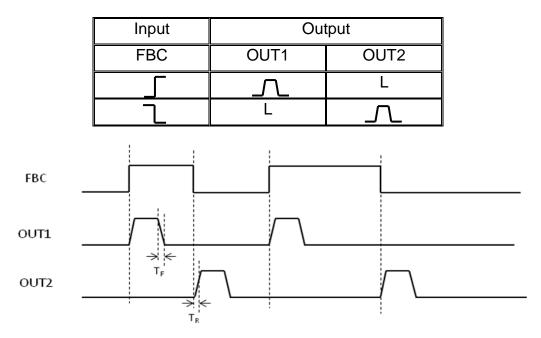

(2) ET1511B

The one-shot period is determined by external capacitor which connected to CE pin of ET1511B.

$T_{OS} = 1.6 \times 10^6 \times C_{CE}$  (sec.)

# **Application Circuits**

(c) One-shot control by FBC and external capacitor  $C_{\text{CE}}$  connect to CE pin

Figure3. Typical application circuit of ET1511A/B

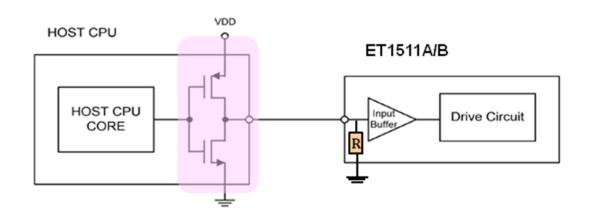

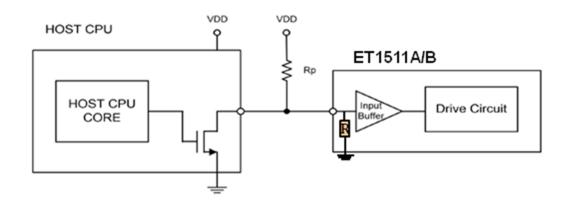

### MCU control

The ENB and FBC pins of ET1511A/B are internal pull-low to ground, which is in safety if input port are floating from unknown output states. The input voltage of input pins must higher than  $V_{IH}$  or small than  $V_{IL}$  to ensure the logic states of the input buffers are stable.

In most cases, ET1511A/B is controlled by GPIO ports of host microcontroller. In general, MCU has 2 types of GPIO ports, open-drain output and buffer output.

The output level of buffer output is VDD in high level and VSS in low level, the GPIO port could connect to ENB and FBC pins directly.

The open-drain output of GPIO port should external pull-up resistor, which does not have pull up driving capability. Because of  $150K\Omega$  internal pull-low resistor, the external pull up resistor could be setup to  $100K\Omega$  maximum. The smaller external pullup resistor will result in faster rise time of output stage but more current consumption when open-drain driven device turns on.

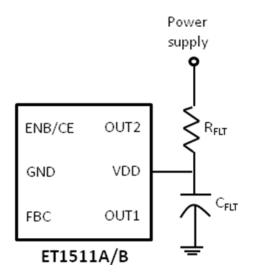

### Layout Guidelines

The output coil motor will actuate back EMF voltage, an unexpected high and low voltage level may force on OUT1 and OUT2 pins during output transient. It is recommended to place a  $R_{FLT}$ - $C_{FLT}$  filter on VDD pin to protect ET1511A/B from higher extreme transient voltage stress. The resistor  $R_{FLT}$  and capacitor  $C_{FLT}$  should place as close to VDD pin as possible.

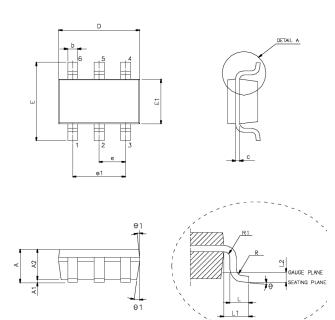

### Package Dimensions SOT23-6L

DETAIL A

| SYMBOL | MIN.      | NOM.      | MAX. |  |

|--------|-----------|-----------|------|--|

| А      |           |           | 1.45 |  |

| A1     | -         | -         | 0.15 |  |

| A2     | 0.90      | 1.15      | 1.30 |  |

| b      | 0.30      | -         | 0.50 |  |

| С      | 0.08      | -         | 0.22 |  |

| D      | 2.90 BSC. |           |      |  |

| E      | 2.80 BSC. |           |      |  |

| E1     | 1.60 BSC. |           |      |  |

| е      | 0.95 BSC. |           |      |  |

| e1     |           | 1.90 BSC. |      |  |

| L      | 0.30      | 0.60      |      |  |

| L1     |           | 0.60      |      |  |

| L2     |           | 0.25      |      |  |

| R      | 0.10 – –  |           |      |  |

| R1     | 0.10 –    |           | 0.25 |  |

| θ      | 0         | 4°        | 8°   |  |

| θ1     | 5°        | 10°       | 15°  |  |

### **Revision History**

| Revision | Date       | Description |

|----------|------------|-------------|

| 1.0      | 2022.10.05 | Original.   |

|          |            |             |

|          |            |             |

|          |            |             |

|          |            |             |

|          |            |             |

|          |            |             |

|          |            |             |

|          |            |             |

|          |            |             |

|          |            |             |

|          |            |             |

### Important Notice

All rights reserved.

No part of this document may be reproduced or duplicated in any form or by any means without the prior permission of ESMT.

The contents contained in this document are believed to be accurate at the time of publication. ESMT assumes no responsibility for any error in this document, and reserves the right to change the products or specification in this document without notice.

The information contained herein is presented only as a guide or examples for the application of our products. No responsibility is assumed by ESMT for any infringement of patents, copyrights, or other intellectual property rights of third parties which may result from its use. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of ESMT or others.

Any semiconductor devices may have inherently a certain rate of failure. To minimize risks associated with customer's application, adequate design and operating safeguards against injury, damage, or loss from such failure, should be provided by the customer when making application designs.

ESMT's products are not authorized for use in critical applications such as, but not limited to, life support devices or system, where failure or abnormal operation may directly affect human lives or cause physical injury or property damage. If products described here are to be used for such kinds of application, purchaser must do its own quality assurance testing appropriate to such applications.