# 4A, 18V, 500KHz Synchronous Step-Down Converter

#### DESCRIPTION

The EUP3485 is a 500KHz fixed frequency synchronous current mode buck regulator. The device integrates both  $110 \mathrm{m}\Omega$  high-side switch and  $30 \mathrm{m}\Omega$  low-side switch that provide 4A of continuous load current over a wide operating input voltage of 4.5V to 18V. The internal synchronous power switch increases efficiency and eliminates the need for an external Schottky diode. Current mode control provides fast transient response and cycle-by-cycle current limit.

The EUP3485 features short circuit and thermal protection circuits to increase system reliability. In shutdown mode, the supply current drops below  $1\mu A.$  The EUP3485 is available in SOP-8 package with an exposed pad.

#### **FEATURES**

- 4A Continuous Output Current

- 100ns Minimum On Time

- Integrated 110mΩ High-side Switch

- Integrated 30mΩ Low-side Switch

- Wide 4.5V to 18V Operating Input Range

- Output Adjustable from 0.8V

- Fixed 500KHz Switching Frequency

- Sync from 300KHz to 2MHz External Clock

- Internal Compensation

- Internal Soft-Start

- <1µA Shutdown Current

- Thermal Shutdown and Over current Protection

- Input Under Voltage Lockout

- Available in SOP-8 (EP) Package

- RoHS Compliant and 100% Lead(Pb)-Free Halogen-Free

#### **APPLICATIONS**

- Distributed Power Systems

- Networking Systems

- Notebook Systems and I/O Power

- Flat Panel Television and Monitors

- Personal Video Recorders

- Digital Set Top Boxes

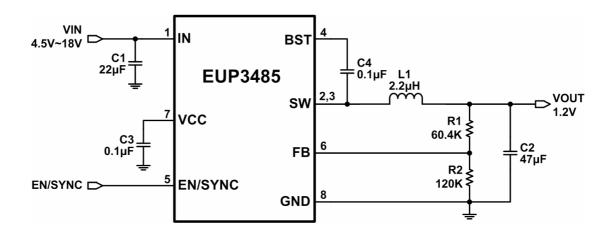

#### **Typical Application Circuit**

Figure 1.

1

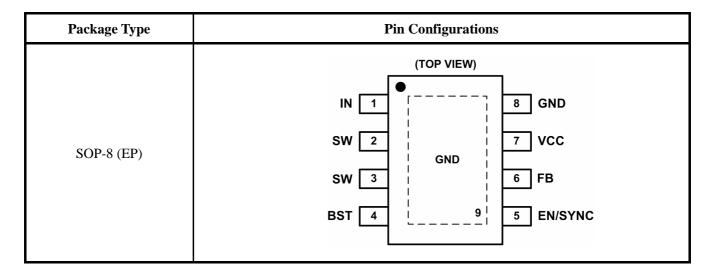

# **Pin Configurations**

# **Pin Description**

| Number              | Pin Name | Description                                                                                                                                                                                                                                                                                                                        |  |  |

|---------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1                   | IN       | Power Input. IN supplies the power to the IC, as well as the step-down converter switches. Drive IN with a 4.5V to 18V power source. Bypass IN to GND with a suitably large capacitor to eliminate noise on the input to the IC. See Input Capacitor.                                                                              |  |  |

| 2,3                 | SW       | Power Switching Output. SW is the switching node that supplies power to the output. Connect the output LC filter from SW to the output load.                                                                                                                                                                                       |  |  |

| 4                   | BST      | High-Side Gate Drive Boost Input. BST supplies the drive for the high-side N-Channel DMOS switch. Connect a $0.01\mu F$ or greater capacitor from SW to BST to power the high side switch.                                                                                                                                         |  |  |

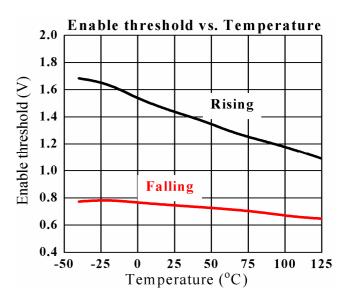

| 5                   | EN/SYNC  | Enable Input. EN is a digital input that turns the regulator on or off. Drive EN high to turn on the regulator; low to turn it off. Attach to IN with a $100k\Omega$ pull up resistor for automatic startup. External clock can be applied to EN pin for changing switching frequency.                                             |  |  |

| 6                   | FB       | FB Feedback Input. FB senses the output voltage and regulates it. Drive FB wiresistive voltage divider connected to it from the output voltage. To prevent curlimit run away during a short circuit fault condition the frequency fold-transcription comparator lowers the oscillator frequency when the FB voltage is below 600mV |  |  |

| 7                   | VCC      | Bias Supply. Decouple with 0.1μF or greater capacitor.                                                                                                                                                                                                                                                                             |  |  |

| 8<br>9(Exposed Pad) | GND      | System Ground. This pin is the reference ground of the regulated output voltage. For this reason care must be taken in PCB layout. Suggested to be connected to GNI with copper and vias.                                                                                                                                          |  |  |

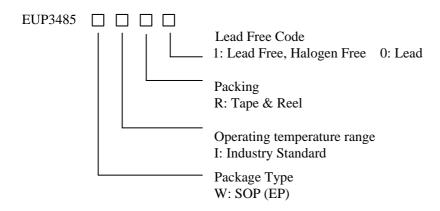

# **Ordering Information**

| Order Number | Package Type | Marking        | Operating Temperature Range |

|--------------|--------------|----------------|-----------------------------|

| EUP3485WIR1  | SOP-8 (EP)   | xxxxx<br>P3485 | -40 °C to +85°C             |

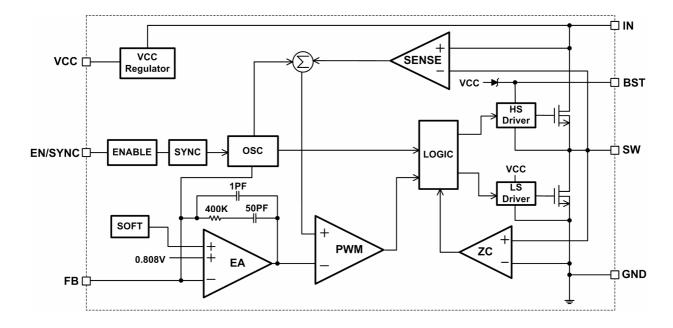

# **Block Diagram**

Figure 3.

# **Absolute Maximum Ratings (1)**

|   | Supply Voltage ( $V_{IN}$ )                                    |

|---|----------------------------------------------------------------|

| • | EN Voltage ( $V_{EN}$ )                                        |

| • | Switch Voltages ( $V_{SW}$ )                                   |

| • | Bootstrap Voltage ( $V_{BST}$ ) $V_{SW}$ -0.3V to $V_{SW}$ +6V |

| • | All Other Pins                                                 |

| • | Junction Temperature 150°C                                     |

| • | Lead Temperature 260°C                                         |

| • | Storage Temperature                                            |

| • | Thermal Resistance: $\theta_{JA}$ (SOP-8_EP)                   |

| • | ESD Ratings: Human Body Mode ±2kV                              |

# **Recommend Operating Conditions (2)**

- Note (1): Stress beyond those listed under "Absolute Maximum Ratings" may damage the device.

Note~(2): The~device~is~not~guaranteed~to~function~outside~the~recommended~operating~conditions.

## **Electrical Characteristics**

$V_{IN}$ =12V , $T_A$ =+25°C, unless otherwise specified.

| Symbol                       | Parameter                                                     | Conditions                         | EUP3485 |      |      | Unit      |

|------------------------------|---------------------------------------------------------------|------------------------------------|---------|------|------|-----------|

|                              |                                                               |                                    | Min.    | Тур. | Max. | Omt       |

| $I_{IN}$                     | Supply Current(Shutdown)                                      | V <sub>EN</sub> =0V                |         | 0.1  |      | μΑ        |

| $I_{IN}$                     | Supply Current(Quiescent)                                     | $V_{EN}=2V$ , $V_{FB}=1V$          |         | 0.9  |      | mA        |

| $R_{DSONH}$                  | High-side Switch On<br>Resistance                             |                                    |         | 110  |      | mΩ        |

| $R_{DSONL}$                  | Low-side Switch On Resistance                                 |                                    |         | 30   |      | $m\Omega$ |

| $\mathrm{SW}_{\mathrm{LKG}}$ | Switch Leakage                                                | $V_{EN}=0V$ , $V_{SW}=0V$ or $12V$ |         | 0    | 10   | μΑ        |

| $I_{LIMIT}$                  | Current Limit                                                 |                                    | 4.6     | 6    |      | A         |

| $F_{SW}$                     | Oscillator Frequency                                          | $V_{FB} = 0.75V$                   | 350     | 500  | 650  | KHz       |

| $F_{FB}$                     | Fold-back Frequency                                           | $V_{FB}=300mV$                     |         | 0.25 |      | $f_{sw}$  |

| $D_{MAX}$                    | Maximum Duty Cycle                                            | $V_{FB}=700mV$                     | 85      | 90   |      | %         |

| F <sub>SYNC</sub>            | Sync Frequency Range                                          |                                    | 0.3     |      | 2    | MHz       |

| $V_{\mathrm{FB}}$            | Feedback Voltage                                              |                                    | 788     | 808  | 828  | mV        |

| $I_{\mathrm{FB}}$            | Feedback Current                                              | $V_{FB}=800 \text{mV}$             |         | 10   | 50   | nA        |

| $V_{\mathrm{ENL}}$           | EN/SYNC Input Low Voltage                                     |                                    |         |      | 0.4  | V         |

| $V_{ENH}$                    | EN/SYNC Input High Voltage                                    |                                    | 2       |      |      | V         |

| т                            | EN Input Current                                              | V <sub>EN</sub> =2V                |         | 2    |      | μΑ        |

| $I_{EN}$                     |                                                               | V <sub>EN</sub> =0V                |         | 0    |      |           |

| $EN_{Td-off}$                | EN Turn Off Delay                                             |                                    |         | 8    |      | μs        |

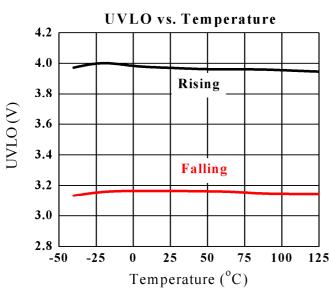

| $V_{\rm UVLO}$               | V <sub>IN</sub> Under Voltage Lockout<br>Threshold Rising     |                                    | 3.8     | 4.0  | 4.2  | V         |

| V <sub>UVLO HYS</sub>        | V <sub>IN</sub> Under Voltage Lockout<br>Threshold Hysteresis |                                    |         | 0.9  |      | V         |

| $V_{CC}$                     | VCC Regulator                                                 |                                    |         | 5    |      | V         |

|                              | VCC Load Regulation                                           | I <sub>CC</sub> =5mA               |         | 5    |      | %         |

| $T_{SD}$                     | Thermal Shutdown                                              |                                    |         | 170  |      | °C        |

| $T_{SDHYS}$                  | Thermal Shutdown Hysteresis                                   |                                    |         | 20   |      | °C        |

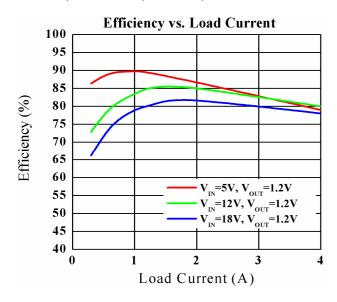

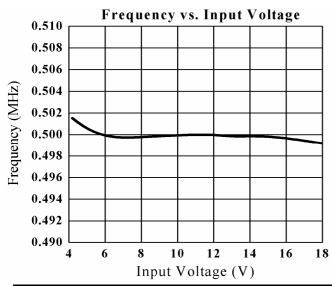

# **Typical Performance Characteristics**

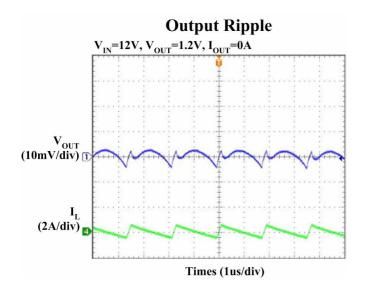

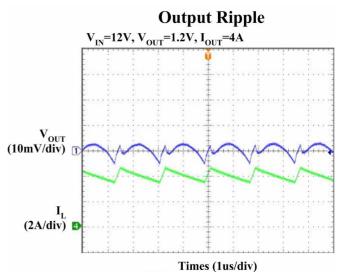

$C_{IN} = 22\mu F$ ,  $C_{OUT} = 47\mu F$ ,  $L = 2.2\mu H$ ,  $T_A = +25$ °C, unless otherwise noted.

EUTECH MICROELECTRONICS

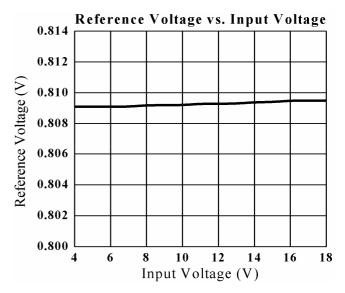

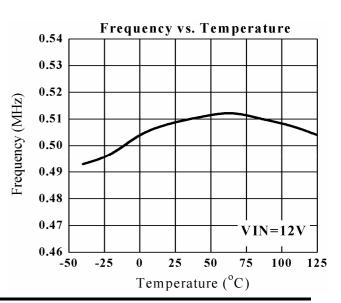

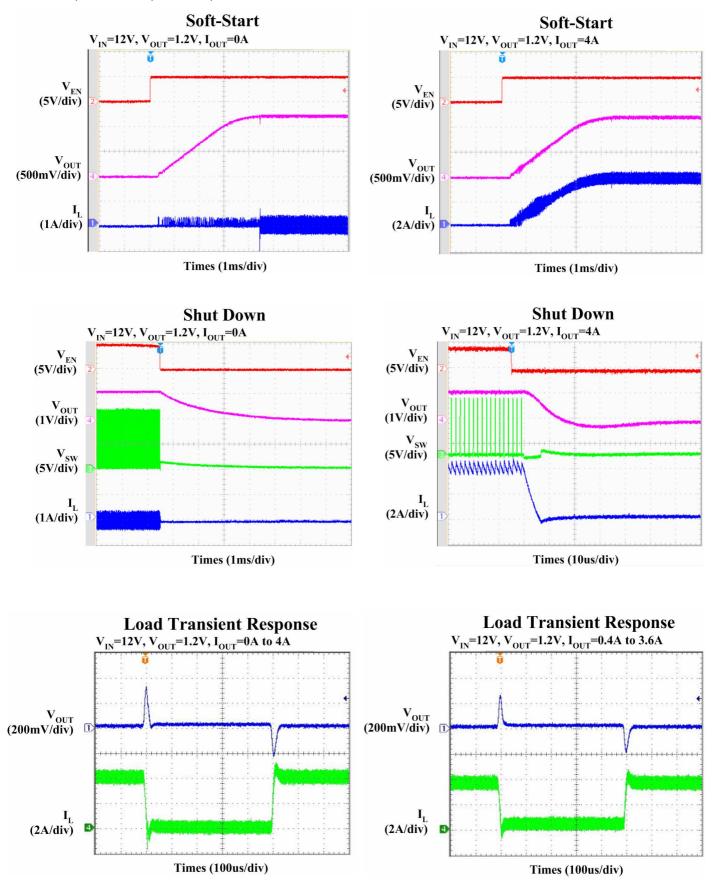

# **Typical Performance Characteristics(continued)**

$C_{IN}$  = 22 $\mu$ F,  $C_{OUT}$ = 47 $\mu$ F, L= 2.2 $\mu$ H,  $T_A$ =+25 $^{\circ}$ C,unless otherwise noted.

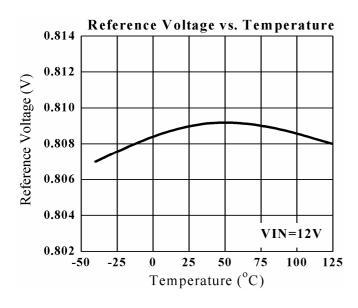

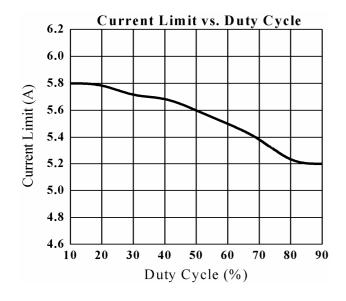

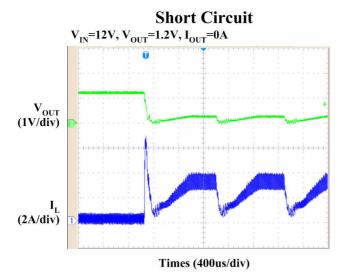

# **Typical Performance Characteristics(continued)**

$C_{IN}$  = 22 $\mu$ F,  $C_{OUT}$ = 47 $\mu$ F, L= 2.2 $\mu$ H,  $T_A$ =+25 $^{\circ}$ C,unless otherwise noted.

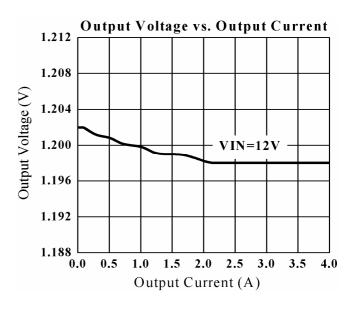

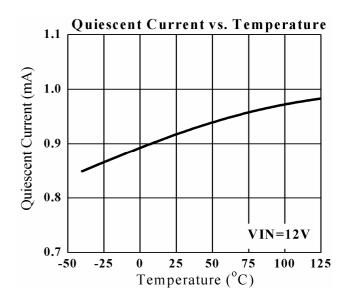

# **Typical Performance Characteristics(continued)**

$C_{IN} = 22\mu F$ ,  $C_{OUT} = 47\mu F$ ,  $L = 2.2\mu H$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.

## **Functional Description**

The EUP3485 regulates input voltages from 4.5V to 18V down to an output voltage as low as 0.8V, and supplies up to 4A of load current.

The EUP3485 uses a fixed frequency, peak current control mode to regulate the output voltage. A PWM cycle is initiated by the internal clock. The integrated high-side power MOSFET is turned on and remains on until its current reaches the value set by the COMP voltage. When the power switch is off, it remains off until the next clock cycle starts. If, in 90% of one PWM period, the current in the power MOSFET does not reach the COMP set current value, the power MOSFET will be forced to turn off.

## **Application Information**

#### **Setting the Output Voltage**

The output voltage is set using a resistive voltage divider connected from the output voltage to FB (see Figure 1.). The voltage divider divides the output voltage down to the feedback voltage by the ratio:

$$V_{FB} = V_{OUT} \, \frac{R_{\,2}}{R_{\,1} + R_{\,2}} \label{eq:VFB}$$

Thus the output voltage is:

$$V_{OUT} = 0.808 \times \frac{R_1 + R_2}{R_2}$$

The feedback resistor  $R_1$  also sets the feedback loop bandwidth with the internal compensation capacitor. Choose  $R_1$  for optimal transient response.  $R_2$  is then given by:

$$R_{2} = \frac{R_{1}}{\frac{V_{OUT}}{0.808V} - 1}$$

**Table 1. Recommended Divider Resistor Selection:**

| V <sub>OUT</sub> (V) | $R_1(k\Omega)$ | $R_2(k\Omega)$ |

|----------------------|----------------|----------------|

| 1.2                  | 60.4           | 124            |

| 1.8                  | 60.4           | 48.7           |

| 2.5                  | 60.4           | 28.7           |

| 3.3                  | 100            | 32.4           |

| 5                    | 150            | 28.7           |

#### **Inductor**

The inductor is required to supply constant current to the load while being driven by the switched input voltage. A larger value inductor will result in less ripple current that will in turn results in lower output ripple voltage. However, the larger value inductor will have a larger physical size, higher series resistance, and/or lower saturation current. A good rule for determining inductance is to allow the peak-to-peak ripple current to be approximately 30% of the maximum switch current limit. Also, make sure

that the peak inductor current is below the maximum switch current limit.

The inductance value can be calculated by:

$$L = \frac{V_{\text{OUT}}}{f_{\text{S}} \times \Delta I_{\text{L}}} \times (1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}})$$

Where  $V_{OUT}$  is the output voltage,  $V_{IN}$  is the input voltage,  $f_S$  is the switching frequency, and  $\Delta I_L$  is the peak-to-peak inductor ripple current.

Choose an inductor that will not saturate under the maximum inductor peak current, calculated by:

$$I_{LP} = I_{LOAD} + \frac{V_{OUT}}{2 \times f_{S} \times L} \times (1 - \frac{V_{OUT}}{V_{IN}})$$

Where  $I_{LOAD}$  is the load current.

The choice of which style inductor to use mainly depends on the price vs. size requirements and any EMI constraints.

#### **Optional Schottky Diode**

During the transition between the high-side switch and low-side switch, the body diode of the low-side power MOSFET conducts the inductor current. The forward voltage of this body diode is high. An optional Schottky diode may be paralleled between the SW pin and GND pin to improve overall efficiency.

#### **Input Capacitor**

The input current to the step-down converter is discontinuous, therefore a capacitor is required to supply the AC current while maintaining the DC input voltage. Use low ESR capacitors for the best performance. Ceramic capacitors are preferred, but tantalum or low-ESR electrolytic capacitors will also suffice. Choose X5R or X7R dielectrics when using ceramic capacitors.

Since the input capacitor  $(C_{IN})$  absorbs the input switching current, it requires an adequate ripple current rating. The RMS current in the input capacitor can be estimated by:

$$I_{\text{CIN}} = I_{\text{LOAD}} \times \sqrt{\frac{V_{\text{OUT}}}{V_{\text{IN}}} \times (1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}})}$$

The worst-case condition occurs at  $V_{\rm IN}=2V_{\rm OUT}$ , where  $IC_{\rm IN}=I_{\rm LOAD}/2$ . For simplification, use an input capacitor with a RMS current rating greater than half of the maximum load current.

The input capacitor can be electrolytic, tantalum or ceramic. When using electrolytic or tantalum capacitors, a small high quality ceramic capacitor, i.e.  $0.1\mu F$ , should be placed as close to the IC as possible. When using ceramic capacitors, make sure that they have enough capacitance to provide sufficient charge to prevent excessive voltage ripple at input. The input voltage ripple for low ESR capacitors can be

estimated by:

$$\Delta V_{IN} = \frac{I_{LOAD}}{C_{IN} \times f_S} \times \frac{V_{OUT}}{V_{IN}} \times (1 - \frac{V_{OUT}}{V_{IN}})$$

where  $C_{\text{IN}}$  is the input capacitor value. For simplification, choose the input capacitor whose RMS current rating greater than half of the maximum load current.

#### **Output Capacitor**

The output capacitor ( $C_{OUT}$ ) is required to maintain the DC output voltage. Ceramic, tantalum, or low ESR electrolytic capacitors are recommended. Low ESR capacitors are preferred to keep the output voltage ripple low. The output voltage ripple can be estimated by:

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{f_{\text{S}} \times L} \times (1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}) \times (R_{\text{ESR}} + \frac{1}{8 \times f_{\text{S}} \times C_{\text{OUT}}})$$

Where  $C_{OUT}$  is the output capacitance value and  $R_{ESR}$  is the equivalent series resistance (ESR) value of the output capacitor.

When using ceramic capacitors, the impedance at the switching frequency is dominated by the capacitance which is the main cause for the output voltage ripple. For simplification, the output voltage ripple can be estimated by:

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{8 \times f_s^2 \times L \times C_{\text{OUT}}} \times (1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}})$$

When using tantalum or electrolytic capacitors, the ESR dominates the impedance at the switching frequency. For simplification, the output ripple can be approximated to:

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{f_{\text{S}} \times L} \times (1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}) \times R_{\text{ESR}}$$

The characteristics of the output capacitor also affect the stability of the regulation system. The EUP3485 can be optimized for a wide range of capacitance and ESR values.

## **PCB** Layout Guide

PCB layout is very important to achieve stable operation. Please follow these guidelines.

- 1) Keep the connection of input ground and GND pin as short and wide as possible.

- 2) Keep the connection of anode of input capacitor and IN pin as short and wide as possible.

- Ensure all feedback connections are short and direct. Place the feedback resistors and compensation components as close to the chip as possible.

- 4) Route SW away from sensitive analog areas such as FB

- 5) Connect IN, SW, and especially GND respectively to a large copper area to cool the chip to improve thermal performance and long-term reliability.

10

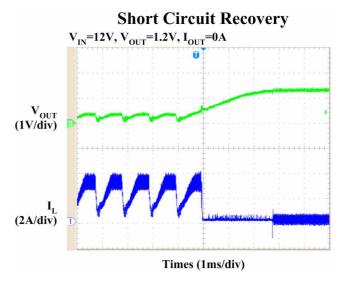

# Packaging Information

# SOP-8 (EP)

| SYMBOLS | MILLIMETERS |      | INCHES     |       |     |

|---------|-------------|------|------------|-------|-----|

|         | MIN.        | MAX. | MIN.       | MAX.  |     |

| A       | 1.35        | 1.75 | 0.053      | 0.069 |     |

| A1      | 0.10        | 0.25 | 0.004      | 0.010 |     |

| D       | 4.          | 90   | 0.193      |       |     |

| E1      | 3.          | 90   | 0.153      |       |     |

| D1      | 2.97        |      | 0.117      |       |     |

| E2      | 2.18        |      | 0.086      |       |     |

| Е       | 5.80        | 6.20 | 0.228      | 0.244 |     |

| L       | 0.40        | 1.27 | 0.016      | 0.050 |     |

| b       | 0.31        | 0.51 | 0.012      | 0.020 |     |

| e       | 1.27        |      | 1.27 0.050 |       | 050 |