## **Flash**

# 4 Gbit (512M x 8) 1.8V NAND Flash Memory

#### **FEATURES**

- Organization

- Memory cell array 4352 x 128K x 8

- Register 4352 x 8

- Page size 4352 bytes

- Block size (256K + 16K) bytes

- Modes

Read, Reset, Auto Page Program, Auto Block Erase, Status Read, Page Copy, Multi Page Program, Multi Block Erase, Multi Page Copy, Multi Page Read

- Mode control

- Serial input/output

- Command control

- Number of valid blocks

- Min 2008 blocks

- Max 2048 blocks

- Power supply

- Vcc = 1.7V to 1.95V

- Access time

- Cell array to register 30 µs max

- Serial Read Cycle 30ns min (CL= 30pF)

- Program/Erase time

- Auto Page Program 300 µs/page typ.

- Auto Block Erase 3.5 ms/block typ.

- Operating current

- Read (30 ns cycle) 30 mA max.

- Program (avg.) 30 mA max

- Erase (avg.) 30 mA max

- Standby 50 µA max

- 8 bit ECC for each 512Byte is required.

### ORDERING INFORMATION

| Product ID          | Speed | Package     | Comments |

|---------------------|-------|-------------|----------|

| F59D4G81CA - 45BG2L | 30 ns | 63 ball BGA | Pb-free  |

### **GENERAL DESCRIPTION**

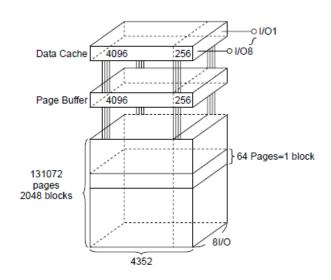

The device is a single 1.8V 4 Gbit (4,563,402,752 bits) NAND Electrically Erasable and Programmable Read-Only Memory organized as (4096 + 256) bytes  $\times$  64 pages  $\times$  2048blocks.

The device has two 4352-byte static registers which allow program and read data to be transferred between the register and the memory cell array in 4352-byte increments. The Erase operation is implemented in a single block unit (256 Kbytes + 16 Kbytes: 4352 bytes × 64 pages).

The device is a serial-type memory device which utilizes the I/O pins for both address and data input/output as well as for command inputs. The Erase and Program operations are automatically executed making the device most suitable for applications such as solid-state file storage, voice recording, image file memory for still cameras and other systems which require high-density non-volatile memory data storage.

# **BALL CONFIGURATION (x8) (TOP VIEW)**

(BGA 63 BALL, 9mm X 11mm Body, 0.8 Ball Pitch)

# **Ball Descriptions**

| Pin Name  | Туре          | Function                                                                                                                                                                         |

|-----------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCC       | Supply        | NAND Power Supply                                                                                                                                                                |

| VSS       | Supply        | Ground                                                                                                                                                                           |

| I/O1-I/O8 | Input/output  | Data inputs/outputs: The bidirectional I/Os transfer address, data, and instruction information.  Data is output only during READ operations; at other times the I/Os are inputs |

| ALE       | Input         | Address latch enable: When ALE is HIGH, addresses can be transferred to the on-chip address register.                                                                            |

| CLE       | Input         | Command latch enable: When CLE is HIGH, commands can be transferred to the on-chip command register.                                                                             |

| CE        | Input         | Chip enable: Gates transfers between the host system and the NAND device.                                                                                                        |

| RE        | Input         | Read enable: Gates information from the NAND device to the host system.                                                                                                          |

| WE        | Input         | Write enable: Gates information from the host system to the NAND device.                                                                                                         |

| WP        | Input         | Write protect: Driving WP# LOW blocks ERASE and PROGRAM operations.                                                                                                              |

| RY/BY     | Output        | Ready/busy: Open-drain, active-LOW output that indicates when an internal operation is in progress.                                                                              |

| NC        | No Connection | Lead is not internally connected.                                                                                                                                                |

Publication Date: Sep. 2018 Revision: 1.0 3/67

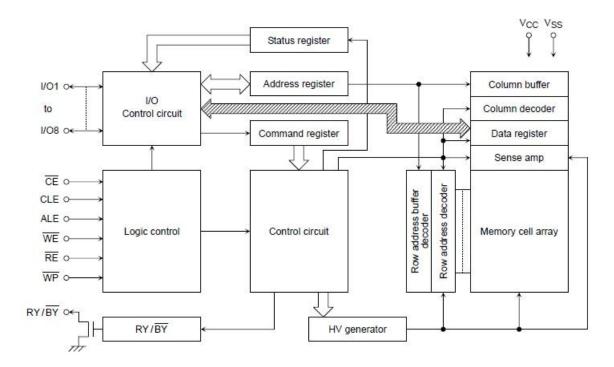

### **BLOCK DIAGRAM**

### **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL              | RATING                       | VALUE                                   | UNIT                   |

|---------------------|------------------------------|-----------------------------------------|------------------------|

| V <sub>CC</sub>     | Power Supply Voltage         | -0.6 to 2.5                             | V                      |

| $V_{IN}$            | Input Voltage                | -0.6 to 2.5                             | V                      |

| V <sub>I/O</sub>    | Input /Output Voltage        | -0.6 to V <sub>CC</sub> + 0.3 (≤ 2.5 V) | V                      |

| $P_D$               | Power Dissipation            | 0.3                                     | W                      |

| T <sub>SOLDER</sub> | Soldering Temperature (10 s) | 260                                     | $^{\circ}\!\mathbb{C}$ |

| T <sub>STG</sub>    | Storage Temperature          | −55 to 125                              | $^{\circ}\mathbb{C}$   |

| T <sub>OPR</sub>    | Operating Temperature        | 0 to 70                                 | $^{\circ}\!\mathbb{C}$ |

### **CAPACITANCE**

$(T_A = 25^{\circ}C, f = 1 \text{ MHz})$

| SYMBOL           | PARAMETER          | CONDITION             | MIN | MAX | UNIT |

|------------------|--------------------|-----------------------|-----|-----|------|

| C <sub>IN</sub>  | Input Capacitance  | $V_{IN} = 0V$         | _   | 10  | pF   |

| C <sub>OUT</sub> | Output Capacitance | V <sub>OUT</sub> = 0V | _   | 10  | pF   |

NOTE: This parameter is periodically sampled and is not tested for every device.

### **VALID BLOCK**

| SYMBOL   | PARAMETER              | MIN  | TYP. | MAX  | UNIT   |

|----------|------------------------|------|------|------|--------|

| $N_{VB}$ | Number of Valid Blocks | 2008 | _    | 2048 | Blocks |

NOTE: The device occasionally contains unusable blocks. Refer to Application Note (13) toward the end of this document.

The first block (Block 0) is guaranteed to be a valid block at the time of shipment.

The specification for the minimum number of valid blocks is applicable over lifetime

The number of valid blocks is on the basis of single plane operations, and this may be decreased with two plane operations.

## **RECOMMENDED DC OPERATING CONDITIONS**

| SYMBOL          | PARAMETER                | MIN                   | TYP. | MAX                   | UNIT |

|-----------------|--------------------------|-----------------------|------|-----------------------|------|

| Vcc             | Power Supply Voltage     | 1.7                   | _    | 1.95                  | V    |

| V <sub>IH</sub> | High Level input Voltage | V <sub>CC</sub> x 0.8 | _    | V <sub>CC</sub> + 0.3 | V    |

| V <sub>IL</sub> | Low Level Input Voltage  | -0.3*                 | _    | V <sub>CC</sub> x 0.2 | V    |

NOTE \*: -2 V (pulse width lower than 20 ns)

### **DC CHARACTERISTICS**

$(T_A = 0 \text{ to } 70^{\circ}\text{C}, V_{CC} = 1.7\text{V to } 1.95\text{V})$

| SYMBOL                          | PARAMETER                     | CONDITION                                                                                            | MIN                   | TYP. | MAX | UNIT |

|---------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------|-----------------------|------|-----|------|

| I <sub>IL</sub>                 | Input Leakage Current         | $V_{IN} = 0 \text{ V to } V_{CC}$                                                                    | _                     | _    | ±10 | uA   |

| I <sub>LO</sub>                 | Output Leakage Current        | $V_{OUT} = 0 \text{ V to } V_{CC}$                                                                   | _                     | _    | ±10 | uA   |

| I <sub>CCO1</sub>               | Serial Read Current           | $\overline{CE} = V_{IL}, I_{OUT} = 0 \text{ mA},$<br>tcycle = 25 ns                                  | _                     | _    | 30  | mA   |

| I <sub>CCO2</sub>               | Programming Current           | _                                                                                                    | _                     | _    | 30  | mA   |

| I <sub>CCO3</sub>               | Erasing Current               | _                                                                                                    | _                     | _    | 30  | mA   |

| Iccs                            | Standby Current               | $\frac{\overline{CE}}{\overline{WP}} = V_{CC} - 0.2 \text{ V},$ $\overline{WP} = 0 \text{ V/V}_{CC}$ | _                     | _    | 50  | uA   |

| V <sub>OH</sub>                 | High Level Output Voltage     | I <sub>OH</sub> = -0.1 mA                                                                            | V <sub>CC</sub> - 0.2 | _    | _   | V    |

| V <sub>OL</sub>                 | Low Level Output Voltage      | I <sub>OL</sub> = 0.1 mA                                                                             | _                     | _    | 0.2 | V    |

| $I_{OL}$ (RY/ $\overline{BY}$ ) | Output current of RY / BY pin | V <sub>OL</sub> = 0.2 V                                                                              | _                     | 4    | _   | mA   |

Publication Date: Sep. 2018 Revision: 1.0 6/67

## AC CHARACTERISTICS AND RECOMMENDED OPERATING CONDITIONS

$(T_A=0 \text{ to } 70^{\circ}\text{C} \,,\, V_{CC}=1.7\text{V to } 1.95\text{V})$

| SYMBOL               | PARAMETER                                            | MIN | MAX        | UNIT |  |

|----------------------|------------------------------------------------------|-----|------------|------|--|

| t <sub>CLS</sub>     | CLE Setup Time                                       | 12  | _          | ns   |  |

| t <sub>CLH</sub>     | CLE Hold Time                                        | 5   | _          | ns   |  |

| tcs                  | CE Setup Time                                        | 20  | _          | ns   |  |

| t <sub>CH</sub>      | CE Hold Time                                         | 5   | _          | ns   |  |

| t <sub>WP</sub>      | Write Pulse Width                                    | 12  | _          | ns   |  |

| t <sub>ALS</sub>     | ALE Setup Time                                       | 12  | _          | ns   |  |

| t <sub>ALH</sub>     | ALE Hold Time                                        | 5   | _          | ns   |  |

| t <sub>DS</sub>      | Data Setup Time                                      | 12  | _          | ns   |  |

| t <sub>DH</sub>      | Data Hold Time                                       | 5   | _          | ns   |  |

| t <sub>WC</sub>      | Write Cycle Time                                     | 30  | _          | ns   |  |

| t <sub>WH</sub>      | WE High Hold Time                                    | 10  | _          | ns   |  |

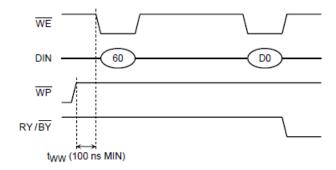

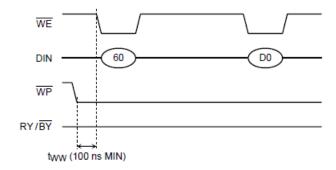

| t <sub>WW</sub>      | WP High to WE Low                                    | 100 | _          | ns   |  |

| t <sub>RR</sub>      | Ready to RE Falling Edge                             | 20  | _          | ns   |  |

| t <sub>RW</sub>      | Ready to WE Falling Edge                             | 20  | _          | ns   |  |

| t <sub>RP</sub>      | Read Pulse Width                                     | 12  | _          | ns   |  |

| t <sub>RC</sub>      | Read Cycle Time                                      | 30  | _          | ns   |  |

| t <sub>REA</sub>     | RE Access Time                                       | _   | 20         | ns   |  |

| t <sub>CEA</sub>     | CE Access Time                                       | _   | 25         | ns   |  |

| t <sub>CLR</sub>     | CLE Low to RE Low                                    | 10  | _          | ns   |  |

| t <sub>AR</sub>      | ALE Low to RE Low                                    | 10  | _          | ns   |  |

| t <sub>RHOH</sub>    | RE High to Output Hold Time                          | 25  | _          | ns   |  |

| t <sub>RLOH</sub>    | RE Low to Output Hold Time                           | 5   | _          | ns   |  |

| t <sub>RHZ</sub>     | RE High to Output High Impedance                     | _   | 60         | ns   |  |

| t <sub>CHZ</sub>     | CE High to Output High Impedance                     | _   | 20         | ns   |  |

| t <sub>CSD</sub>     | CE High to ALE or CLE Don't Care                     | 0   | _          | ns   |  |

| t <sub>REH</sub>     | RE High Hold Time                                    | 10  | _          | ns   |  |

| t <sub>IR</sub>      | Output-High-impedance-to-RE Falling Edge             | 0   | _          | ns   |  |

| t <sub>RHW</sub>     | RE High to WE Low                                    | 30  | _          | ns   |  |

| t <sub>WHC</sub>     | WE High to CE Low                                    | 30  | _          | ns   |  |

| t <sub>WHR</sub>     | WE High to RE Low                                    | 60  | _          | ns   |  |

| t <sub>R</sub>       | Memory Cell Array to Starting Address                | _   | 30         | μs   |  |

| t <sub>DCBSYR1</sub> | Data Cache Busy in Read Cache (following 31h and3Fh) | _   | 25         | μs   |  |

| t <sub>DCBSYR2</sub> | Data Cache Busy in Page Copy (following 3Ah)         | _   | 30         | μs   |  |

| t <sub>WB</sub>      | WE High to Busy                                      | _   | 100        | ns   |  |

| t <sub>RST</sub>     | Device Reset Time (Ready/Read/Program/Erase)         | _   | 5/5/10/500 | μs   |  |

### NOTE:

- 1.  $t_{CLS}$  and  $t_{ALS}$  can not be shorter than  $t_{WP}$ .

- 2.  $t_{CS}$  should be longer than  $t_{WP}$  + 8ns.

Publication Date: Sep. 2018 Revision: 1.0 7/67

#### **AC TEST CONDITIONS**

| DADAMETED                      | CONDITION                      |

|--------------------------------|--------------------------------|

| PARAMETER                      | V <sub>CC</sub> : 1.7 to 1.95V |

| Input level                    | V <sub>CC</sub> - 0.2 V, 0.2 V |

| Input pulse rise and fall time | 3 ns                           |

| Input comparison level         | V <sub>CC</sub> / 2            |

| Output data comparison level   | V <sub>CC</sub> / 2            |

| Output load                    | C <sub>L</sub> (30 pF) + 1 TTL |

NOTE: Busy to ready time depends on the pull-up resistor tied to the RY /  $\overline{\text{BY}}$  pin. (Refer to Application Note (9) toward the end of this document.)

#### PROGRAMMING AND ERASING CHARACTERISTICS

$(T_A = 0 \text{ to } 70^{\circ}\text{C}, V_{CC} = 2.7 \text{ to } 3.6\text{V})$

| SYMBOL               | PARAMETER                                           |   | TYP. | MAX | UNIT | NOTES |

|----------------------|-----------------------------------------------------|---|------|-----|------|-------|

| t <sub>PROG</sub>    | Average Programming Time                            | _ | 300  | 700 | μs   |       |

| t <sub>DCBSYW1</sub> | Data Cache Busy Time in Write Cache (following 11h) | _ | _    | 10  | μs   |       |

| t <sub>DCBSYW2</sub> | Data Cache Busy Time in Write Cache (following 15h) | _ | _    | 700 | μs   | 2     |

| N <sub>OP</sub>      | Number of Partial Program Cycles in the Same Page   | _ | _    | 4   |      | 1     |

| t <sub>BERASE</sub>  | Block Erasing Time                                  | _ | 3.5  | 10  | ms   |       |

#### NOTE:

- 1. Refer to Application Note (12) toward the end of this document.

- 2. t<sub>DCBSYW2</sub> depends on the timing between internal programming time and data in time.

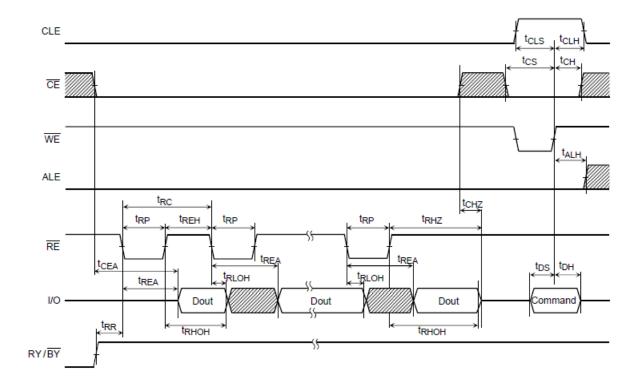

### **Data Output**

When  $t_{REH}$  is long, output buffers are disabled by  $\overline{RE}$  = High, and the hold time of data output depend on  $t_{RHOH}$  (25ns MIN). On this condition, waveforms look like normal serial read mode.

When  $t_{REH}$  is short, output buffers are not disabled by  $\overline{RE}$  = High, and the hold time of data output depend on  $t_{RLOH}$  (5ns MIN). On this condition, output buffers are disabled by the rising edge of CLE, ALE,  $\overline{CE}$  or falling edge of  $\overline{WE}$ , and waveforms look like Extended Data Output Mode.

### **TIMING DIAGRAMS**

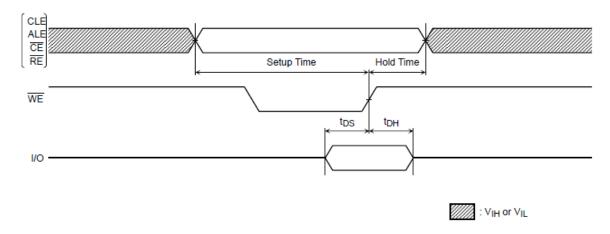

# Latch Timing Diagram for Command/Address/Data

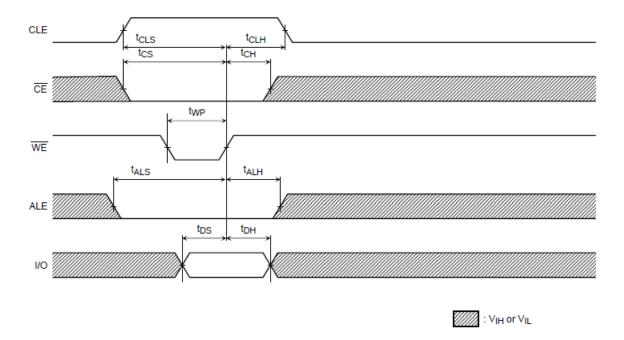

## **Command Input Cycle Timing Diagram**

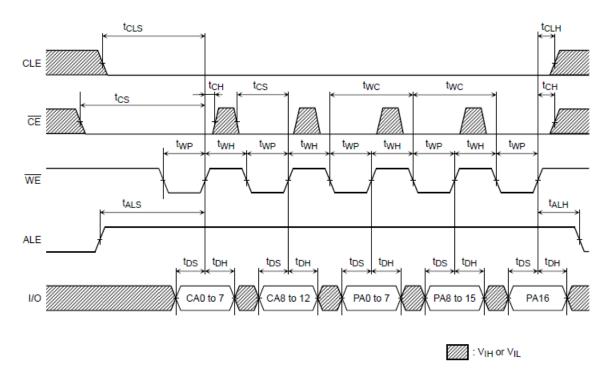

## **Address Input Cycle Timing Diagram**

# **Data Input Cycle Timing Diagram**

## **Serial Read Cycle Timing Diagram**

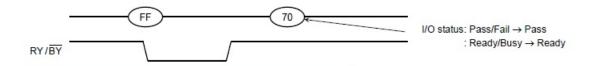

### **Status Read Cycle Timing Diagram**

\*: 70h represents the hexadecimal number

Publication Date: Sep. 2018 Revision: 1.0 11/67

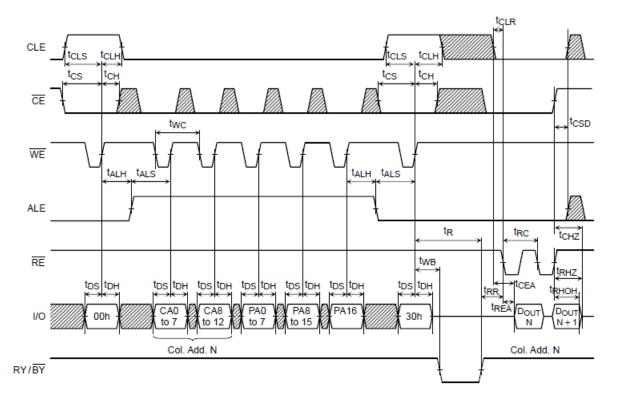

## **Read Cycle Timing Diagram**

# Read Cycle Timing Diagram: When Interrupted by $\overline{\text{CE}}$

Publication Date: Sep. 2018 Revision: 1.0 12/67

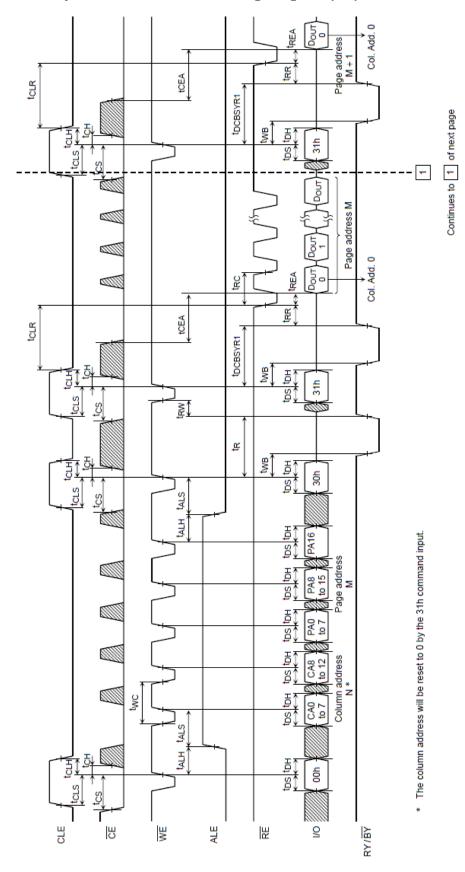

# Read Cycle with Data Cache Timing Diagram (1/2)

Publication Date: Sep. 2018 Revision: 1.0 13/67

# Read Cycle with Data Cache Timing Diagram (2/2)

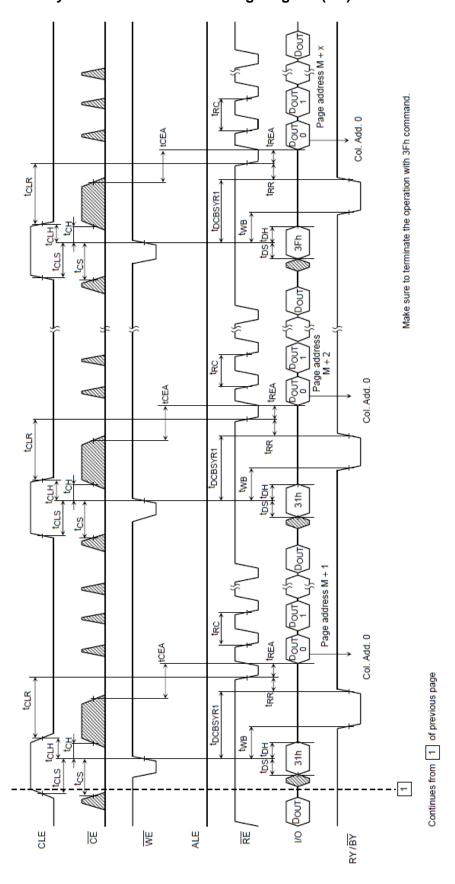

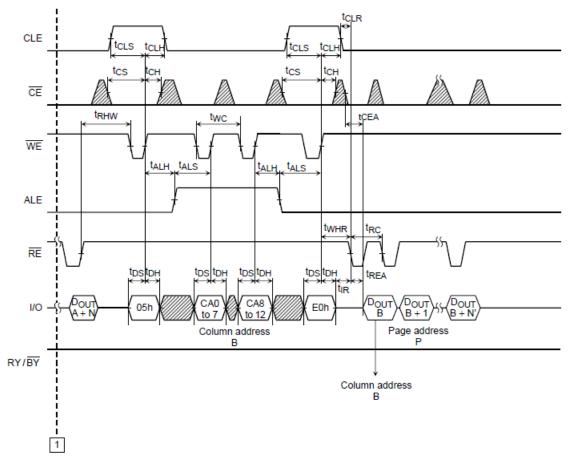

# Column Address Change in Read Cycle Timing Diagram (1/2)

Continues to 1 of next page

Publication Date: Sep. 2018 Revision: 1.0 15/67

## Column Address Change in Read Cycle Timing Diagram (2/2)

Publication Date: Sep. 2018 Revision: 1.0 16/67

## **Data Output Timing Diagram**

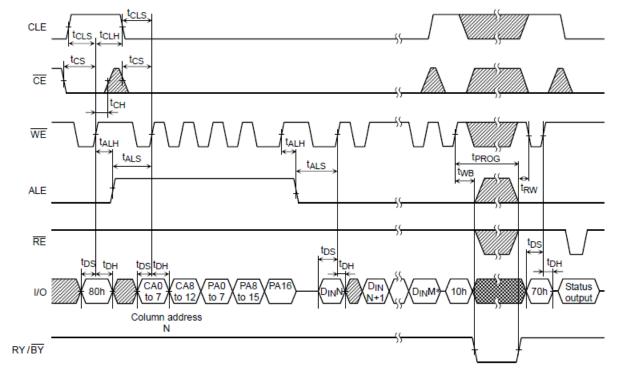

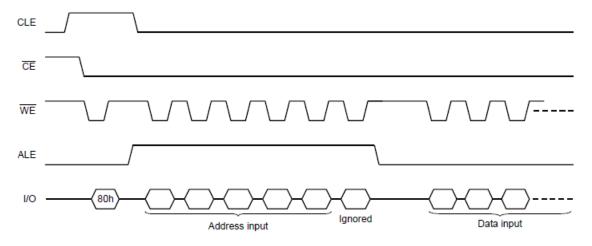

## **Auto-Program Operation Timing Diagram**

: Do not input data while data is being output.

: V<sub>IH</sub> or V<sub>IL</sub>

\*) M: up to 4351 (byte input data for ×8 device).

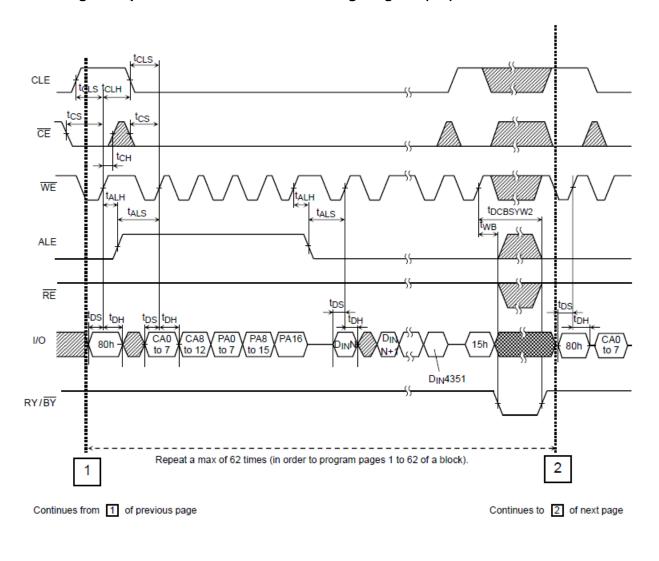

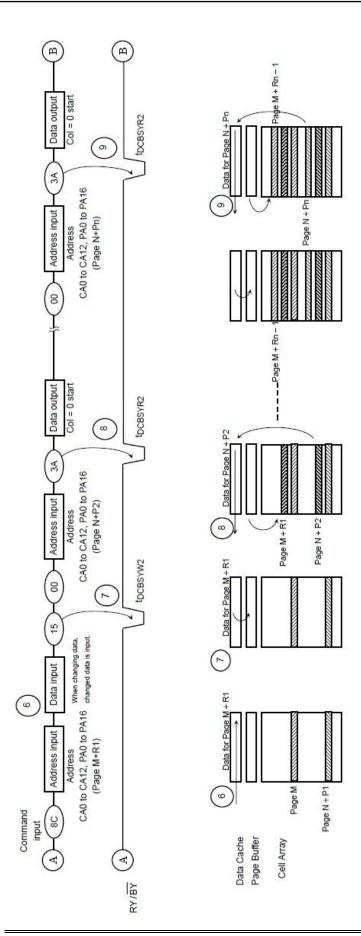

## **Auto-Program Operation with Data Cache Timing Diagram (1/3)**

## **Auto-Program Operation with Data Cache Timing Diagram (2/3)**

: Do not input data while data is being output.

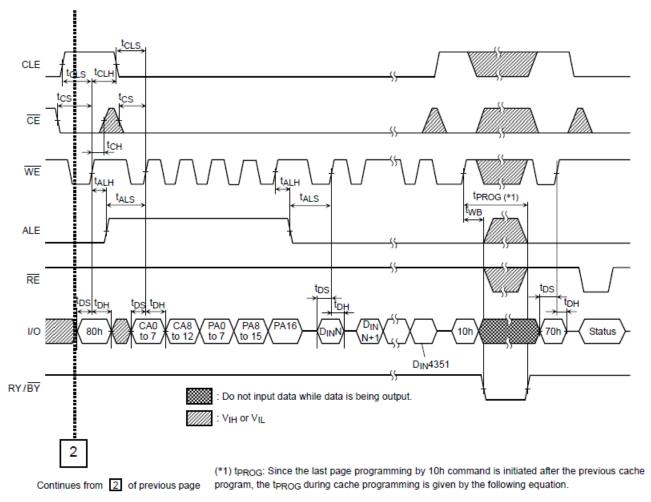

### **Auto-Program Operation with Data Cache Timing Diagram (3/3)**

tpROG = tpROG of the last page + tpROG of the previous page - A

A = (command input cycle + address input cycle + data input cycle time of the last page)

If "A" exceeds the tpROG of previous page, tpROG of the last page is tpROG max.

NOTE: Make sure to terminate the operation with 80h-10h- command sequence. If the operation is terminated by 80h-15h command sequence, monitor I/O 6 (Ready / Busy) by issuing Status Read command (70h) and make sure the previous page program operation is completed. If the page program operation is completed issue FFh reset before next operation.

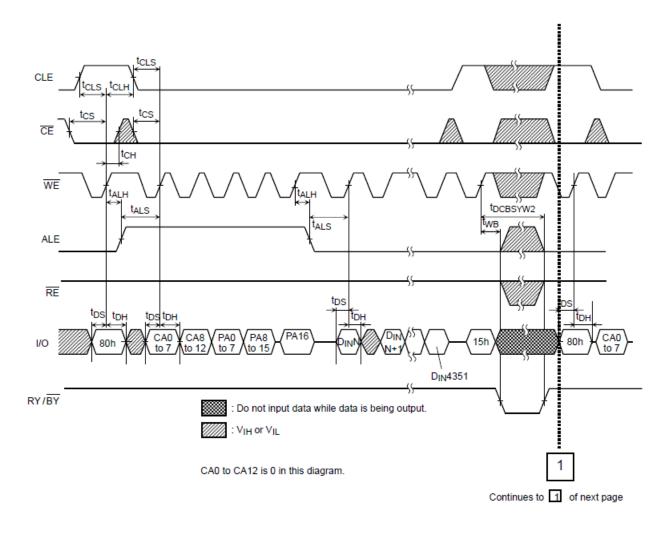

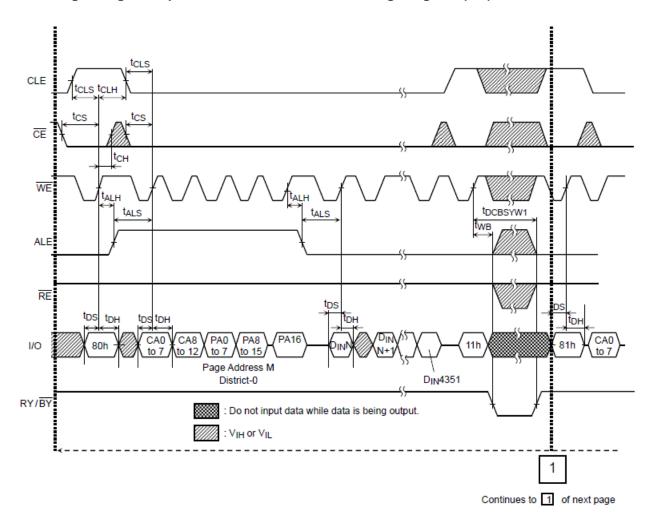

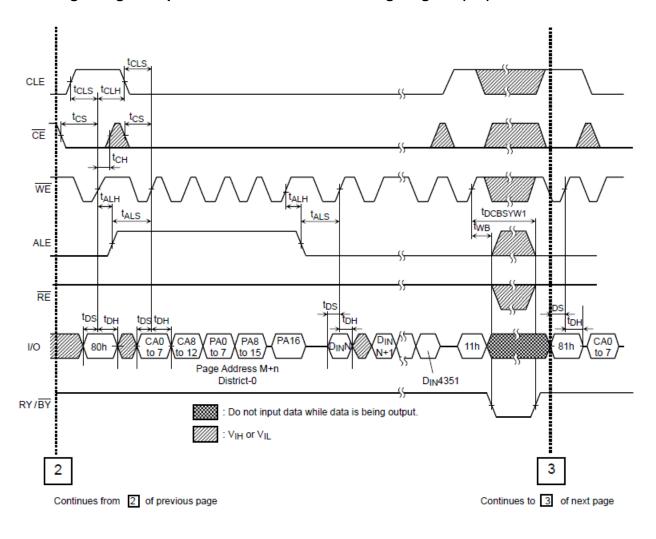

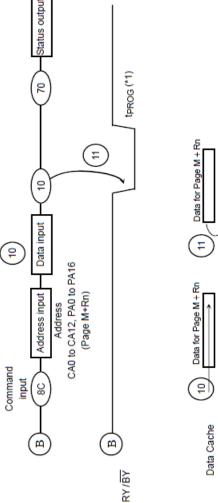

## Multi-Page Program Operation with Data Cache Timing Diagram (1/4)

## Multi-Page Program Operation with Data Cache Timing Diagram (2/4)

: Do not input data while data is being output.

: V<sub>IH</sub> or V<sub>IL</sub>

24/67

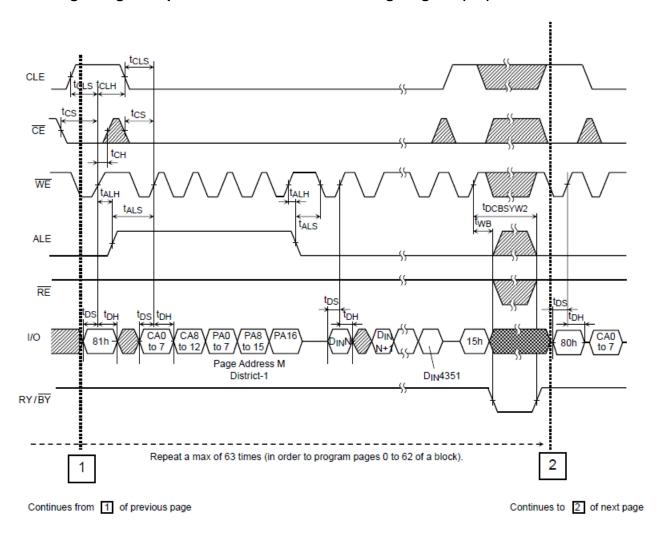

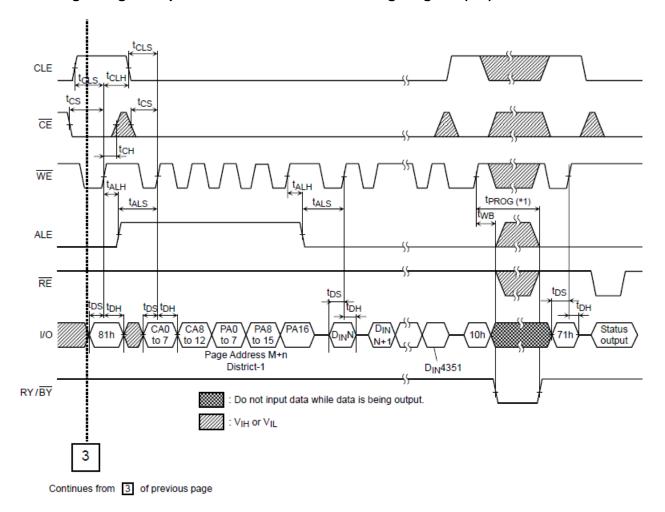

## Multi-Page Program Operation with Data Cache Timing Diagram (3/4)

### Multi-Page Program Operation with Data Cache Timing Diagram (4/4)

(\*1)  $t_{PROG}$ : Since the last page programming by 10h command is initiated after the previous cache program, the  $t_{PROG}$  during cache programming is given by the following equation.

tpROG = tpROG of the last page + tpROG of the previous page - A

A = (command input cycle + address input cycle + data input cycle time of the last page)

If "A" exceeds the tpROG of previous page, tpROG of the last page is tpROG max.

NOTE: Make sure to terminate the operation with 81h-10h- command sequence. If the operation is terminated by 81h-15h command sequence, monitor I/O 6 (Ready / Busy) by issuing Status Read command (70h) and make sure the previous page program operation is completed. If the page program operation is completed issue FFh reset before next operation.

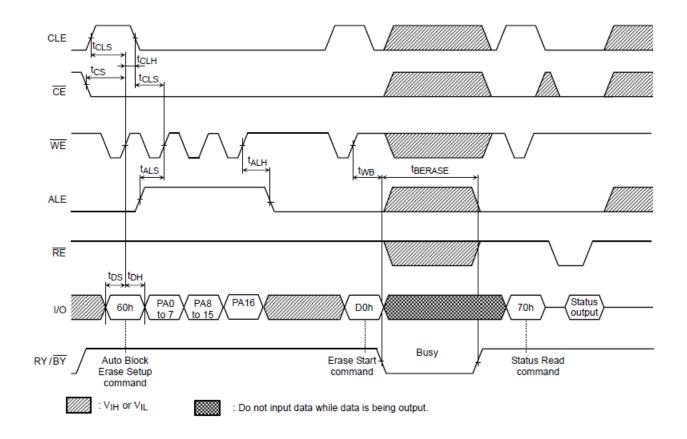

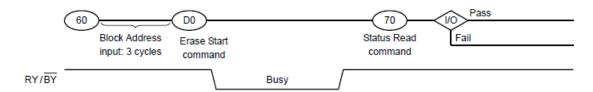

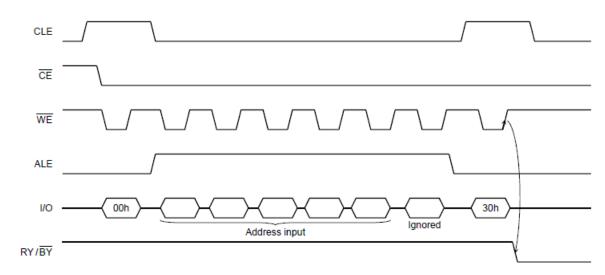

## **Auto Block Erase Timing Diagram**

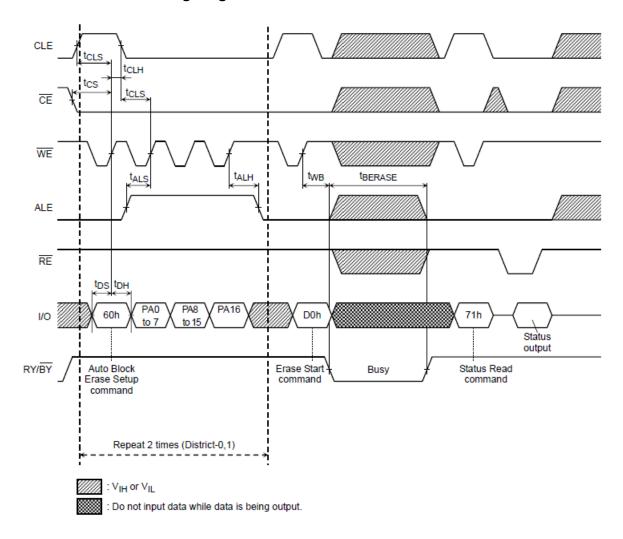

## **Multi Block Erase Timing Diagram**

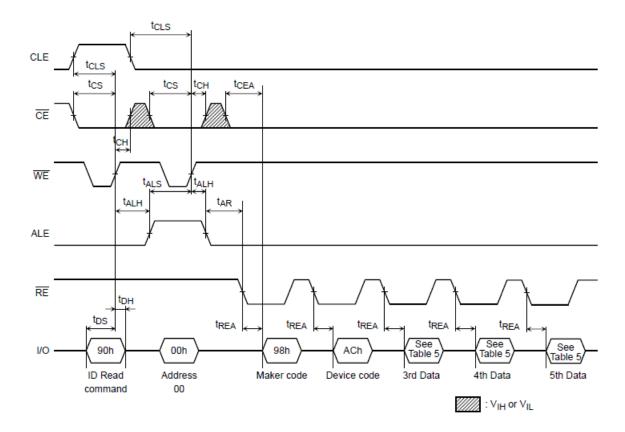

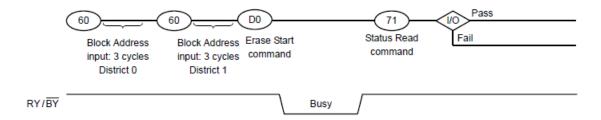

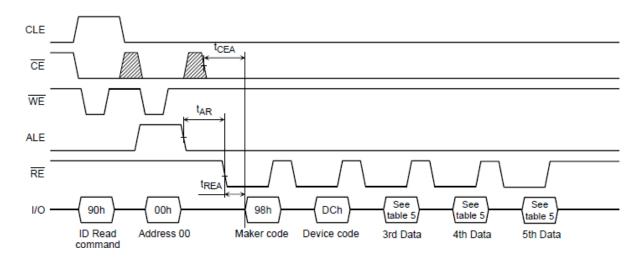

## **ID Read Operation Timing Diagram**

Publication Date: Sep. 2018 Revision: 1.0 28/67

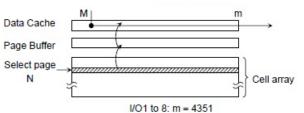

## **Schematic Cell Layout and Address Assignment**

The Program operation works on page units while the Erase operation works on block units.

A page consists of 4352 bytes in which 4096 bytes are used for main memory storage and 256 bytes are for redundancy or for other uses.

1 page = 4352 bytes 1 block = 4352 bytes × 64 pages = (256K + 16K) bytes Capacity = 4352 bytes × 64pages × 2048 blocks

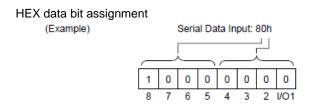

An address is read in via the I/O port over five consecutive clock cycles, as shown in Table 1.

Table 1. Addressing

|              | I/O8 | 1/07 | 1/06 | I/O5 | 1/04 | I/O3 | 1/02 | I/O1 |

|--------------|------|------|------|------|------|------|------|------|

| First cycle  | CA7  | CA6  | CA5  | CA4  | CA3  | CA2  | CA1  | CA0  |

| Second cycle | L    | L    | L    | CA12 | CA11 | CA10 | CA9  | CA8  |

| Third cycle  | PA7  | PA6  | PA5  | PA4  | PA3  | PA2  | PA1  | PA0  |

| Fourth cycle | PA15 | PA14 | PA13 | PA12 | PA11 | PA10 | PA9  | PA8  |

| Fifth cycle  | L    | L    | L    | L    | L    | L    | L    | PA16 |

CA0 to CA12: Column address PA0 to PA16: Page address

PA6 to PA16: Block address PA0 to PA5: NAND address in block

## **Operation Mode: Logic and Command Tables**

The operation modes such as Program, Erase, Read and Reset are controlled by command operations shown in Table 3. Address input, command input and data input/output are controlled by the CLE, ALE,  $\overline{CE}$ ,  $\overline{WE}$ ,  $\overline{RE}$  and  $\overline{WP}$  signals, as shown in Table 2.

Table 2. Logic Table

|                        | CLE | ALE | CE | WE              | RE              | <b>WP</b> *1       |

|------------------------|-----|-----|----|-----------------|-----------------|--------------------|

| Command Input          | Н   | L   | L  |                 | Н               | *                  |

| Data Input             | L   | L   | L  | <b>-</b>        | Н               | Н                  |

| Address Input          | L   | Н   | L  | <b>□</b>        | Н               | *                  |

| Serial Data Output     | L   | L   | L  | Н               | ₹.              | *                  |

| During Program (Busy)  | *   | *   | *  | *               | *               | Н                  |

| During Erase (Busy)    | *   | *   | *  | *               | *               | Н                  |

| During Dood (Dury)     | *   | *   | Н  | *               | *               | *                  |

| During Read (Busy)     | *   | *   | L  | H <sup>*2</sup> | H <sup>*2</sup> | *                  |

| Program, Erase Inhibit | *   | *   | *  | *               | *               | L                  |

| Standby                | *   | *   | Н  | *               | *               | 0V/V <sub>CC</sub> |

H:  $V_{IH}$ , L:  $V_{IL}$ , \*:  $V_{IH}$  or  $V_{IL}$  NOTE:

<sup>1.</sup> Refer to Application Note (10) toward the end of this document regarding the  $\overline{\text{WP}}$  signal when Program or Erase Inhibit.

<sup>2.</sup> If  $\overline{CE}$  is low during read busy,  $\overline{WE}$  and  $\overline{RE}$  must be held High to avoid unintended command/address input to the device or read to device. Reset or Status Read command can be input during Read Busy.

Table 3. Command table (HEX)

|                                                         | First Cycle | Second Cycle | Acceptable while Busy |

|---------------------------------------------------------|-------------|--------------|-----------------------|

| Serial Data Input                                       | 80          | _            |                       |

| Read                                                    | 00          | 30           |                       |

| Column Address Change in Serial Data Output             | 05          | E0           |                       |

| Read with Data Cache                                    | 31          | _            |                       |

| Read Start for Last Page in Read Cycle with Data Cache  | 3F          | _            |                       |

| Auto Page Program                                       | 80          | 10           |                       |

| Column Address Change in Serial Data Input              | 85          | _            |                       |

| Auto Program with Data Cache                            | 80          | 15           |                       |

|                                                         | 80          | 11           |                       |

| Multi Page Program                                      | 81          | 15           |                       |

|                                                         | 81          | 10           |                       |

| Read for Page Copy (2) with Data Out                    | 00          | 3A           |                       |

| Auto Program with Data Cache during Page Copy (2)       | 8C          | 15           |                       |

| Auto Program for last page during Page Copy (2)         | 8C          | 10           |                       |

| Auto Block Erase                                        | 60          | D0           |                       |

| ID Read                                                 | 90          | _            |                       |

| Status Read                                             | 70          | _            | 0                     |

| Status Read for Multi-Page Program or Multi Block Erase | 71          | _            | 0                     |

| Reset                                                   | FF          |              | 0                     |

Table 4. Read mode operation states

|                 | CLE | ALE | CE | WE | RE | I/O1 to I/O8   | Power  |

|-----------------|-----|-----|----|----|----|----------------|--------|

| Output select   | L   | L   | L  | Н  | L  | Data output    | Active |

| Output Deselect | L   | L   | L  | Н  | Н  | High impedance | Active |

$H \colon V_{IH}, \ L \colon V_{IL}$

32/67

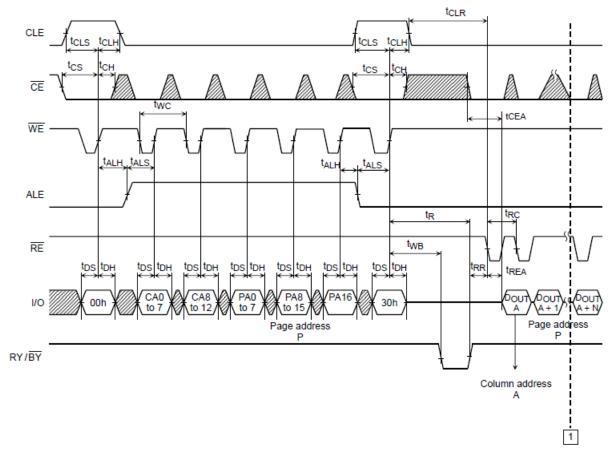

### **DEVICE OPERATION Read Mode**

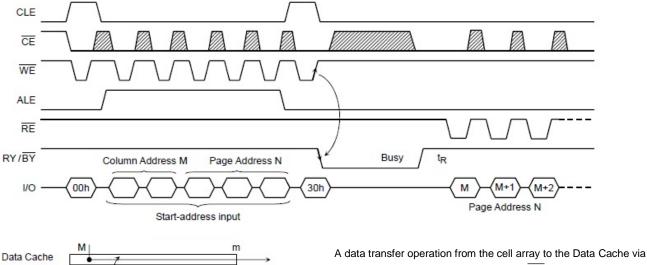

Read mode is set when the "00h" and "30h" commands are issued to the Command register. Between the two commands, a start address for the Read mode needs to be issued. After initial power on sequence, "00h" command is latched into the internal command register. Therefore read operation after power on sequence is executed by the setting of only five address cycles and "30h" command. Refer to the figures below for the sequence and the block diagram. (Refer to the detailed timing chart.)

Page Buffer starts on the rising edge of WE in the 30h command input cycle (after the address information has been latched). The device will be in the Busy state during this transfer period. After the transfer period, the device returns to Ready state. Serial data can be output synchronously with the RE clock from the start address designated in the address input cycle.

### Random Column Address Change in Read Cycle

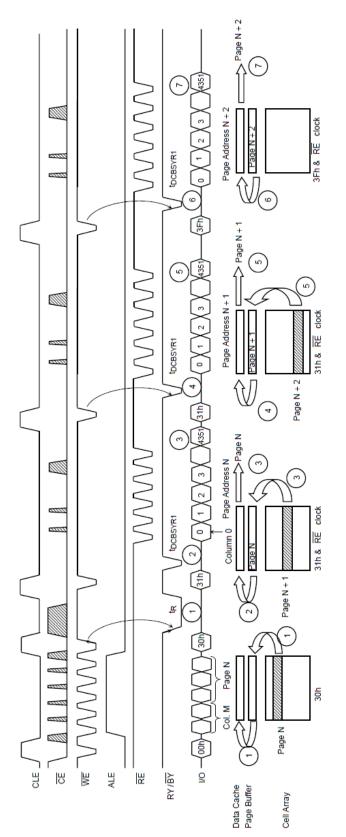

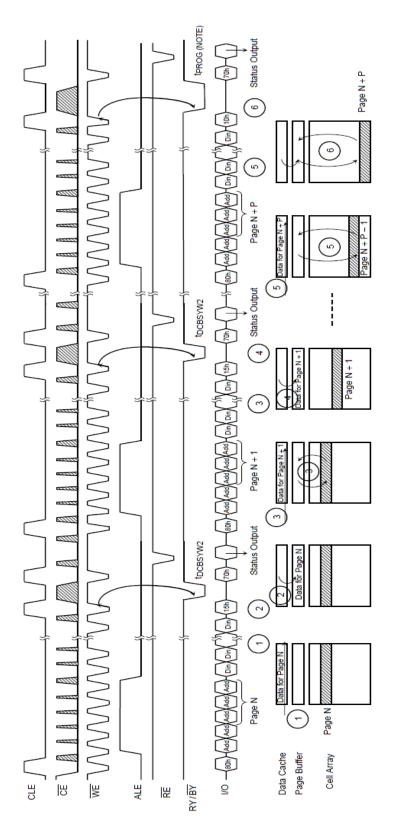

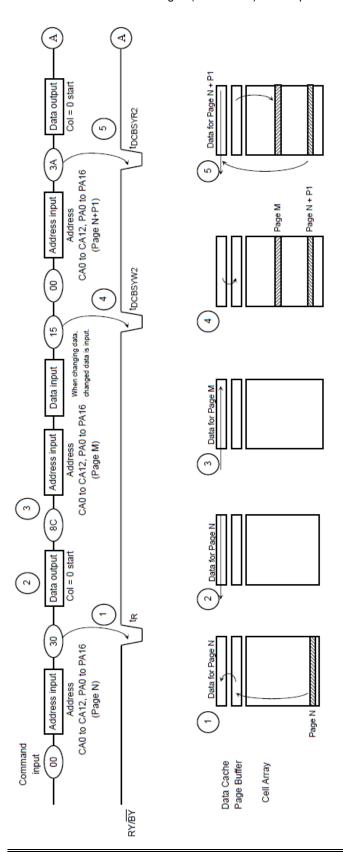

### **Read Operation with Read Cache**

The device has a Read operation with Data Cache that enables the high speed read operation shown below. When the block address changes, this sequence has to be started from the beginning.

If the 31h command is issued to the device, the data content of the next page is transferred to the Page Buffer during serial data out from the Data Cache, and therefore the t<sub>R</sub> (Data transfer from memory cell to data register) will be reduced. Normal read. Data is transferred from Page N to Data Cache through Page Buffer. During this time period, the device outputs Busy state for

After the Ready/Busy returns to Ready, 31h command is issued and data is transferred to Data Cache from Page Buffer again. This data transfer takes t<sub>DCBSVR1</sub> max and the completion of this time period can be detected by Ready/Busy signal ď

Data of Page N+1 is transferred to Page Buffer from cell while the data of Page N in Data cache can be read out by /RE clock simultaneously. ω.

The 31h command makes data of Page N + 1 transfer to Data Cache from Page Buffer after the completion of the transfer from cell to Page Buffer. The device outputs Busy state for tocesyra max.. This Busy period depends on the combination of the internal data transfer time from cell to Page buffer and the serial data out time. 4.

Page N + 2 is transferred to Page Buffer from cell while the data of Page N + 1 in Data cache can be read out by /RE clock simultaneously. Data of 5

The 3Fh command makes the data of Page N + 2 transfer to the Data Cache from the Page Buffer after the completion of the transfer from cell to Page Buffer. The device outputs Busy state for tocasyra max.. This Busy period depends on the combination of the internal data ransfer time from cell to Page buffer and the serial data out time. ö.

Data of Page N + 2 in Data Cache can be read out, but since the 3Fh command does not transfer the data from the memory cell to Page the device can accept new command input immediately after the completion of serial data out.

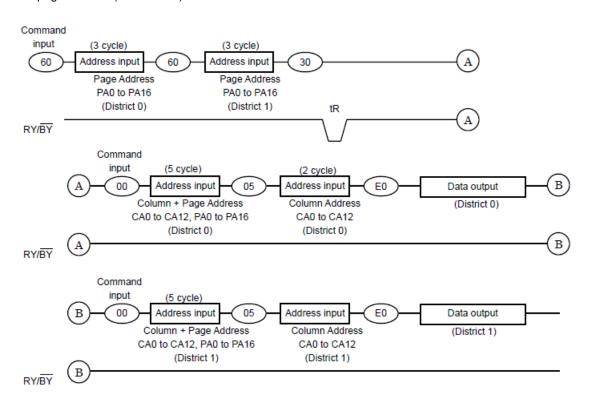

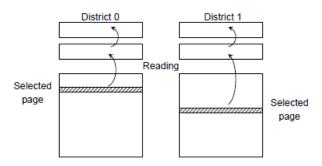

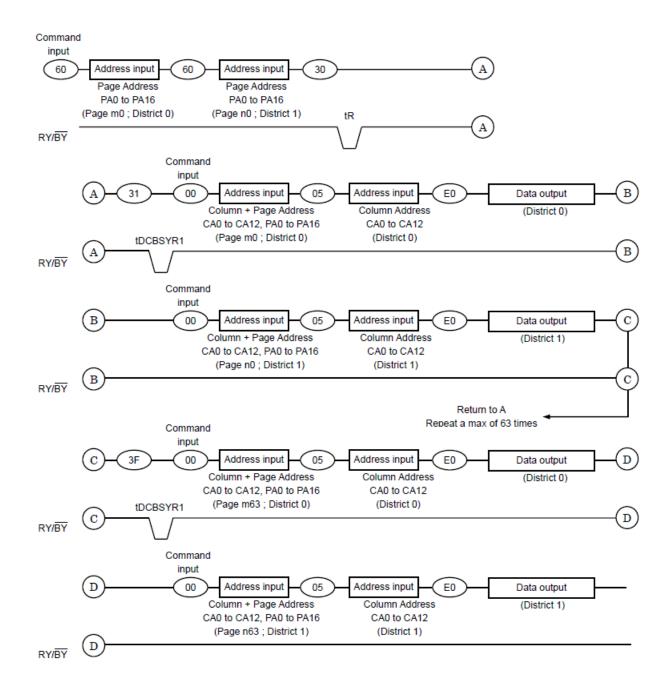

### **Multi Page Read Operation**

The device has a Multi Page Read operation and Multi Page Read with Data Cache operation.

#### (1) Multi Page Read without Data Cache

The sequence of command and address input is shown below. Same page address (PA0 to PA5) within each district has to be selected.

The data transfer operation from the cell array to the Data Cache via Page Buffer starts on the rising edge of  $\overline{\text{WE}}$  in the 30h command input cycle (after the 2 Districts address information has been latched). The device will be in the Busy state during this transfer period. After the transfer period, the device returns to Ready state. Serial data can be output synchronously with the  $\overline{\text{RE}}$  clock from the start address designated in the address input cycle.

#### (2) Multi Page Read with Data Cache

When the block address changes (increments) this sequenced has to be started from the beginning. The sequence of command and address input is shown below.

Same page address (PA0 to PA5) within each district has to be selected.

#### (3) Notes

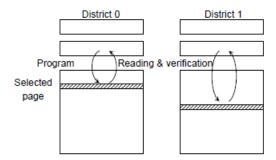

(a) Internal addressing in relation with the Districts

To use Multi Page Read operation, the internal addressing should be considered in relation with the District.

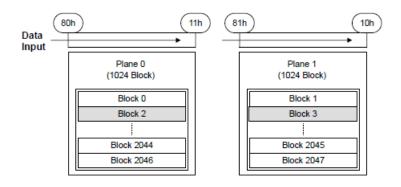

- The device consists from 2 Districts.

- Each District consists from 1024 erase blocks.

- The allocation rule is follows.

```

District 0: Block 0, Block 2, Block 4, Block 6,..., Block 2046 District 1: Block 1, Block 3, Block 5, Block 7,..., Block 2047

```

(b) Address input restriction for the Multi Page Read operation

There are following restrictions in using Multi Page Read;

#### (Restriction)

Maximum one block should be selected from each District.

Same page address (PA0 to PA5) within two districts has to be selected.

For example;

(60) [District 0, Page Address 0x00000] (60) [District 1, Page Address 0x00040] (30)

(60) [District 0, Page Address 0x00001] (60) [District 1, Page Address 0x00041] (30)

#### (Acceptance)

There is no order limitation of the District for the address input.

For example, following operation is accepted;

(60) [District 0] (60) [District 1] (30)

(60) [District 1] (60) [District 0] (30)

It requires no mutual address relation between the selected blocks from each District.

### (c) WP signal

Make sure WP is held to High level when Multi Page Read operation is performed.

Publication Date: Sep. 2018 Revision: 1.0 36/67

## **Auto Page Program Operation**

The device carries out an Automatic Page Program operation when it receives a "10h" Program command after the address and data have been input. The sequence of command, address and data input is shown below. (Refer to the detailed timing chart.)

## Random Column Address Change in Auto Page Program Operation

The column address can be changed by the 85h command during the data input sequence of the Auto Page Program operation. Two address input cycles after the 85h command are recognized as a new column address for the data input. After the new data is input to the new column address, the 10h command initiates the actual data program into the selected page automatically. The Random Column Address Change operation can be repeated multiple times within the same page.

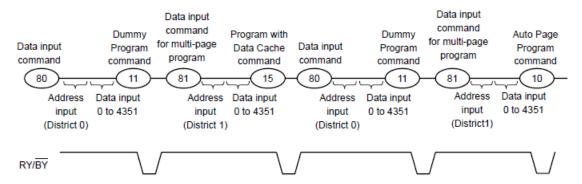

## **Multi Page Program**

The device has a Multi Page Program, which enables even higher speed program operation compared to Auto Page Program. The sequence of command, address and data input is shown below. (Refer to the detailed timing chart.)

Although two planes are programmed simultaneously, pass/fail is not available for each page by "70h" command when the program operation completes. Status bit of I/O 1 is set to "1" when any of the pages fails. Limitation in addressing with Multi Page Program is shown below.

NOTE: Any command between 11h and 81h is prohibited except 70h and FFh.

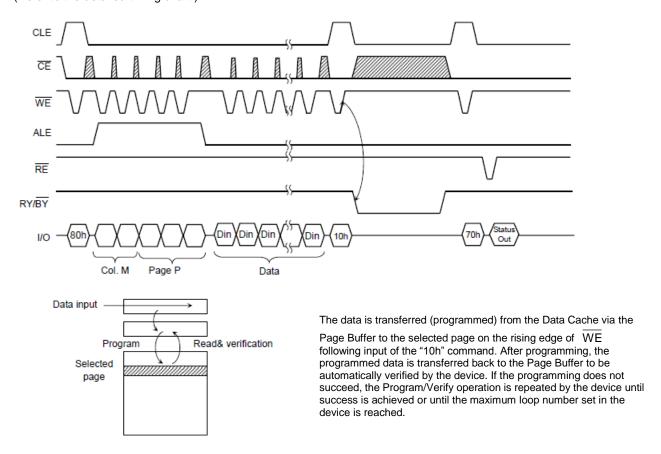

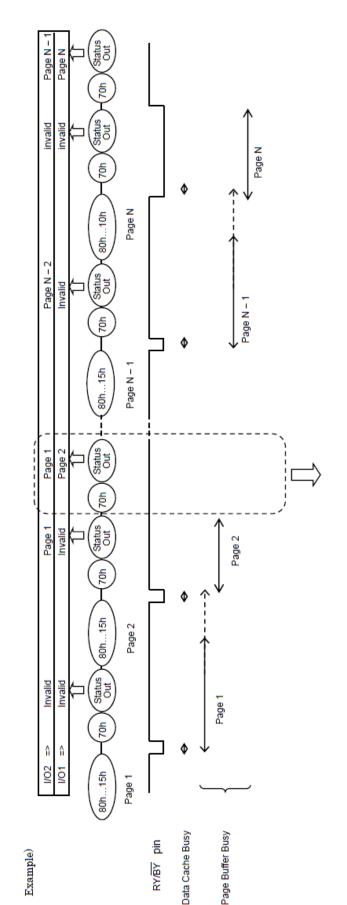

# **Auto Page Program Operation with Data Cache**

The device has an Auto Page Program with Data Cache operation enabling the high speed program operation shown below. When the block address changes this sequenced has to be started from the beginning.

Issuing the 15h command to the device after serial data input initiates the program operation with Data Cache Data for Page N is input to Data Cache.

Data is transferred to the Page Buffer by the 15h command. During the transfer the Ready/Busy outputs Busy State (tocssywz). Data is programmed to the selected page while the data for page N + 1 is input to the Data Cache.

By the 15h command, the data in the Data Cache is transferred to the Page Buffer after the programming of page N is completed. The device output busy state from the 15h command until the Data Cache becomes empty. The duration of this period depends on timing between the internal programming of page N and serial data input for Page N + 1 (tocssywz)

NOTE: Since the last page programming by the 10h command is initiated after the previous cache program, the tprog during cache programming of the Page N + P is completed

The programming with Data Cache is terminated by the 10h command. When the device becomes Ready, it shows that the internal

Data for Page N + P is input to the Data Cache while the data of the Page N + P - 1 is being programmed.

6.5

terog = terog for the last page + terog of the previous page - ( command input cycle + address input cycle + data input cycle time of the last

programming is given by the following;

Pass/fail status for each page programmed by the Auto Page Programming with Data Cache operation can be detected by the Status Read operation.

I/O1: Pass/fail of the current page program operation. I/O2: Pass/fail of the previous page program operation.

The Pass/Fail status on I/O1 and I/O2 are valid under the following conditions.

Status on I/O1: Page Buffer Ready/Busy is Ready State.

The Page Buffer Ready/Busy is output on I/O6 by Status Read operation or RY / /BY pin after the 10h command Status on I/O2: Data Cache Read/Busy is Ready State.

The Data Cache Ready/Busy is output on I/O7 by Status Read operation or RY / /BY pin after the 15h command.

If the Page Buffer Busy returns to Ready before the next 80h command input, and if Status Read is done during this Ready period, the Status Read provides pass/fail for Page 2 on I/O1 and pass/fail result for Page1 on I/O2

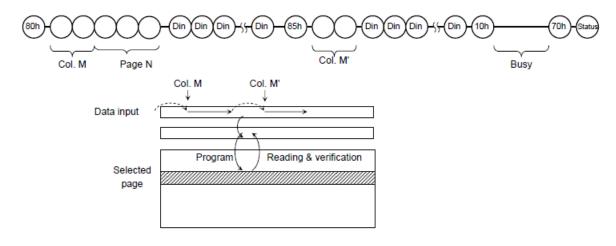

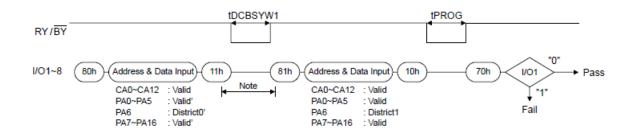

## Multi Page Program with Data Cache

The device has a Multi Page Program with Data Cache operation, which enables even higher speed program operation compared to Auto Page Program with Data Cache as shown below. When the block address changes (increments) this sequenced has to be started from the beginning.

The sequence of command, address and data input is shown below. (Refer to the detailed timing chart.)

After "15h" or "10h" Program command is input to device, physical programming starts as follows. For details of Auto Program with Data Cache, refer to "Auto Page Program with Data Cache".

The data is transferred (programmed) from the page buffer to the selected page on the rising edge of  $\overline{\text{WE}}$  following input of the "15h" or "10h" command. After programming, the programmed data is transferred back to the register to be automatically verified by the device. If the programming does not succeed, the Program/Verify operation is repeated by the device until success is achieved or until the maximum loop number set in the device is reached.

Starting the above operation from 1st page of the selected erase blocks, and then repeating the operation total 64 times with incrementing the page address in the blocks, and then input the last page data of the blocks, "10h" command executes final programming. Make sure to terminate with 81h-10h- command sequence.

In this full sequence, the command sequence is following.

After the "15h" or "10h" command, the results of the above operation are shown through the "71h" Status Read command.

The 71h command Status description is as below.

|      | STATUS                              | 0          | UTPUT          |

|------|-------------------------------------|------------|----------------|

| I/O1 | Chip Status1 : Pass/Fail            | Pass: 0    | Fail: 1        |

| I/O2 | District 0 Chip Status1 : Pass/Fail | Pass: 0    | Fail: 1        |

| I/O3 | District 1 Chip Status1 : Pass/Fail | Pass: 0    | Fail: 1        |

| 1/04 | District 0 Chip Status2 : Pass/Fail | Pass: 0    | Fail: 1        |

| 1/05 | District 1 Chip Status2 : Pass/Fail | Pass: 0    | Fail: 1        |

| 1/06 | Ready/Busy                          | Ready: 1   | Busy: 0        |

| 1/07 | Data Cache Ready/Busy               | Ready: 1   | Busy: 0        |

| I/O8 | Write Protect                       | Protect: 0 | Not Protect: 1 |

I/O1 describes Pass/Fail condition of district 0 and 1(OR data of I/O2 and I/O3). If one of the districts fails during multi page program operation, it shows "Fail".

I/O2 to 5 shows the Pass/Fail condition of each district. For details on "Chip Status1" and "Chip Status2", refer to section "Status Read".

# Internal addressing in relation with the Districts

To use Multi Page Program operation, the internal addressing should be considered in relation with the District.

- The device consists from 2 Districts.

- Each District consists from 1024 erase blocks.

- The allocation rule is follows.

District 0: Block 0, Block 2, Block 4, Block 6,..., Block 2046 District 1: Block 1, Block 3, Block 5, Block 7,..., Block 2047

## Address input restriction for the Multi Page Program with Data Cache operation

There are following restrictions in using Multi Page Program with Data Cache;

#### (Restriction)

Maximum one block should be selected from each District.

Same page address (PA0 to PA5) within two districts has to be selected.

For example:

(80) [District 0, Page Address 0x00000] (11) (81) [District 1, Page Address 0x00040] (15 or 10)

(80) [District 0, Page Address 0x00001] (11) (81) [District 1, Page Address 0x00041] (15 or 10)

#### (Acceptance)

There is no order limitation of the District for the address input.

For example, following operation is accepted;

(80) [District 0] (11) (81) [District 1] (15 or 10)

(80) [District 1] (11) (81) [District 0] (15 or 10)

It requires no mutual address relation between the selected blocks from each District.

# Operating restriction during the Multi Page Program with Data Cache operation

#### (Restriction)

The operation has to be terminated with "10h" command.

Once the operation is started, no commands other than the commands shown in the timing diagram is allowed to be input except for Status Read command and reset command.

Publication Date: Sep. 2018 Revision: 1.0 43/67

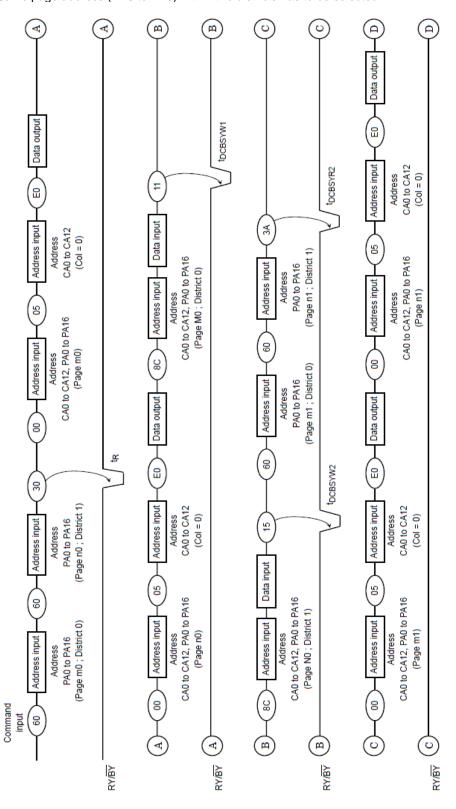

# Page Copy (2)

By using Page Copy (2), data in a page can be copied to another page after the data has been read out. When the block address changes (increments) this sequenced has to be started from the beginning.

Page Copy (2) operation is as following.

Data for Page N is transferred to the Data Cache.

Data for Page N is read out.

Copy Page address M is input and if the data needs to be changed, changed data is input. Data Cache for Page M is transferred to the Page Buffer.

After the Ready state, Data for Page N + P1 is output from the Data Cache while the data of Page M is being programmed.

After programming of page M is completed, Data Cache for Page M + R1 is transferred to the Page Buffer. Copy Page address (M + R1) is input and if the data needs to be changed, changed data is input. 9 7 8 9

By the 15h command, the data in the Page Buffer is programmed to Page M + R1. Data for Page N + P2 is transferred to the Data cache. The data in the Page Buffer is programmed to Page M + Rn – 1. Data for Page N + Pn is transferred to the Data Cache.

10. Copy Page address (M + Rn) is input and if the data needs to be changed, changed data is input.

11. By issuing the 10h command, the data in the Page Buffer is programmed to Page M + Rn.

(\*1) Since the last page programming by the 10h command is initiated after the previous cache program, the teros here will be expected as the following,

lerge = terge of the last page + terge of the previous page - ( command input cycle + address input cycle + data output/input cycle time of the last page)

(NOTE) This operation needs to be executed within District-0 or District-1.

Data input is required only if previous data output needs to be altered.

If the data has to be changed, locate the desired address with the column and page address input after the 8Ch command, and change only the data that needs be changed.

If the data does not have to be changed, data input cycles are not required.

Also make sure the Page Copy operation is terminated with 8Ch-10h command sequence Make sure /WP is held to High level when Page Copy (2) operation is performed.

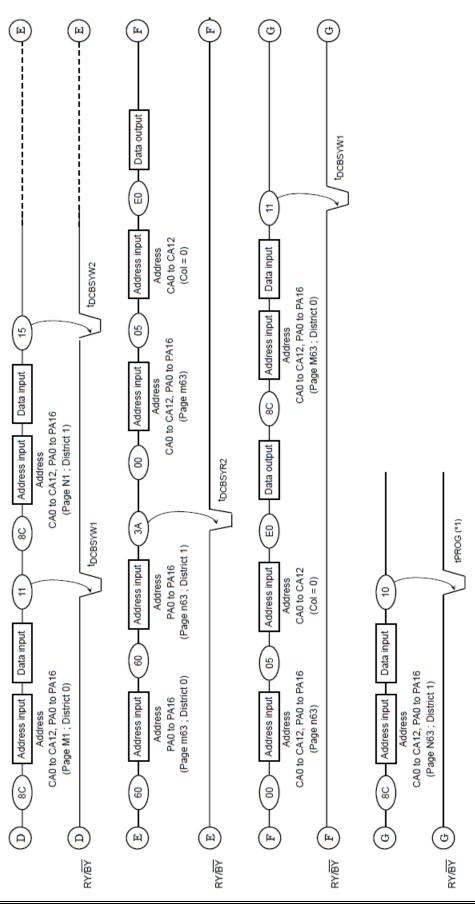

# Multi Page Copy (2)

By using Multi Page Copy (2), data in two pages can be copied to other pages after the data has been read out. When each block address changes (increments) this sequence has to be started from the beginning. Same page address (PA0 to PA5) within two districts has to be selected.

(\*1) throo: Since the last page programming by 10h command is initiated after the previous cache program, the tPROG\* during cache programming is given by the following equation

PROG = tprog of the last page + tprog of the previous page-A

A = (command input cycle + address input cycle + data output/input cycle time of the last page)

f "A" exceeds the tprog of previous page, tprog of the last page is tprog max

This operation needs to be executed within each District.

Data input is required only if previous data output needs to be altered.

If the data has to be changed, locate the desired address with the column and page address input after the 8Ch command, and change only the data that needs be changed.

if the data does not have to be changed, data input cycles are not required.

Also make sure the Multi Page Copy operation is terminated with 8Ch-10h command sequence. Make sure /WP is held to High level when Multi Page Copy (2) operation is performed.

48/67

#### **Auto Block Erase**

The Auto Block Erase operation starts on the rising edge of WE after the Erase Start command "D0h" which follows the Erase Setup command "60h". This two-cycle process for Erase operations acts as an extra layer of protection from accidental erasure of data due to external noise. The device automatically executes the Erase and Verify operations.

#### Multi Block Erase

The Multi Block Erase operation starts by selecting two block addresses before D0h command as in below diagram. The device automatically executes the Erase and Verify operations and the result can be monitored by checking the status by 71h status read command. For details on 71h status read command, refer to section "Multi Page Program with Data Cache".

## Internal addressing in relation with the Districts

To use Multi Block Erase operation, the internal addressing should be considered in relation with the District.

- The device consists from 2 Districts.

- Each District consists from 1024 erase blocks.

- The allocation rule is follows. District 0: Block 0, Block 2, Block 4, Block 6,..., Block 2046 District 1: Block 1, Block 3, Block 5, Block 7,..., Block 2047

## Address input restriction for the Multi Block Erase

There are following restrictions in using Multi Block Erase

(Restriction)

Maximum one block should be selected from each District.

For example;

(60) [District 0] (60) [District 1] (D0)

(Acceptance)

There is no order limitation of the District for the address input.

For example, following operation is accepted;

(60) [District 1] (60) [District 0] (D0)

It requires no mutual address relation between the selected blocks from each District.

Make sure to terminate the operation with D0h command. If the operation needs to be terminated before D0h command input, input the FFh reset command to terminate the operation.

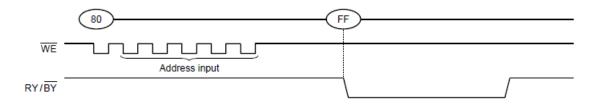

## **ID Read**

The device contains ID codes which can be used to identify the device type, the manufacturer, and features of the device. The ID codes can be read out under the following timing conditions:

Table 5. Code table

|          | Description                      | 1/08 | 1/07 | I/O6 | I/O5 | I/O4 | I/O3 | I/O2 | I/O1 | Hex Data |

|----------|----------------------------------|------|------|------|------|------|------|------|------|----------|

| 1st Data | Maker Code                       | 1    | 0    | 0    | 1    | 1    | 0    | 0    | 0    | 98h      |

| 2nd Data | Device Code                      | 1    | 0    | 1    | 0    | 1    | 1    | 0    | 0    | ACh      |

| 3rd Data | Chip Number, Cell Type           | 1    | 0    | 0    | 1    | 0    | 0    | 0    | 0    | 90h      |

| 4th Data | Page Size, Block Size, I/O Width | 0    | 0    | 1    | 0    | 0    | 1    | 1    | 0    | 26h      |

| 5th Data | Plane Number                     | 0    | 1    | 1    | 1    | 0    | 1    | 1    | 0    | 76h      |

#### 3rd Data

|                      | Description   | 1/08 | 1/07 | 1/06 | 1/05 | 1/04 | 1/03 | 1/02 | I/O1 |

|----------------------|---------------|------|------|------|------|------|------|------|------|

|                      | 1             |      |      |      |      |      |      | 0    | 0    |

| Internal Chin Number | 2             |      |      |      |      |      |      | 0    | 1    |

| Internal Chip Number | 4             |      |      |      |      |      |      | 1    | 0    |

|                      | 8             |      |      |      |      |      |      | 1    | 1    |

|                      | 2 Level Cell  |      |      |      |      | 0    | 0    |      |      |

| Call Type            | 4 Level Cell  |      |      |      |      | 0    | 1    |      |      |

| Cell Type            | 8 Level Cell  |      |      |      |      | 1    | 0    |      |      |

|                      | 16 Level Cell |      |      |      |      | 1    | 1    |      |      |

| Reserved             |               | 1    | 0    | 0    | 1    |      |      |      |      |

# 4th Data

|                          | Description | 1/08 | 1/07 | I/O6 | 1/05 | I/O4 | I/O3 | 1/02 | I/O1 |

|--------------------------|-------------|------|------|------|------|------|------|------|------|

|                          | 1KB         |      |      |      |      |      |      | 0    | 0    |

| Page Size                | 2KB         |      |      |      |      |      |      | 0    | 1    |

| (without redundant area) | 4KB         |      |      |      |      |      |      | 1    | 0    |

|                          | 8KB         |      |      |      |      |      |      | 1    | 1    |

|                          | 64KB        |      |      | 0    | 0    |      |      |      |      |

| Block Size               | 128KB       |      |      | 0    | 1    |      |      |      |      |

| (without redundant area) | 256KB       |      |      | 1    | 0    |      |      |      |      |

| ,                        | 512KB       |      |      | 1    | 1    |      |      |      |      |

| I/O Width                | x8          |      | 0    |      |      |      |      |      |      |

|                          | x16         |      | 1    |      |      |      |      |      |      |

| Reserved                 | •           | 0    |      |      |      | 0    | 1    |      |      |

## 5th Data

|                | Description | I/O8 | 1/07 | 1/06 | 1/05 | 1/04 | I/O3 | 1/02 | I/O1 |

|----------------|-------------|------|------|------|------|------|------|------|------|

| Diagon Namedon | 1 Plane     |      |      |      |      | 0    | 0    |      |      |

|                | 2 Plane     |      |      |      |      | 0    | 1    |      |      |

| Plane Number   | 4 Plane     |      |      |      |      | 1    | 0    |      |      |

|                | 8 Plane     |      |      |      |      | 1    | 1    |      |      |

| Reserved       |             | 0    | 1    | 1    | 1    |      |      | 1    | 0    |

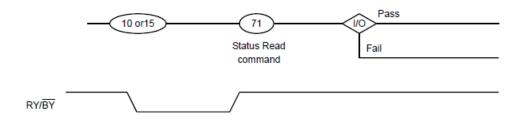

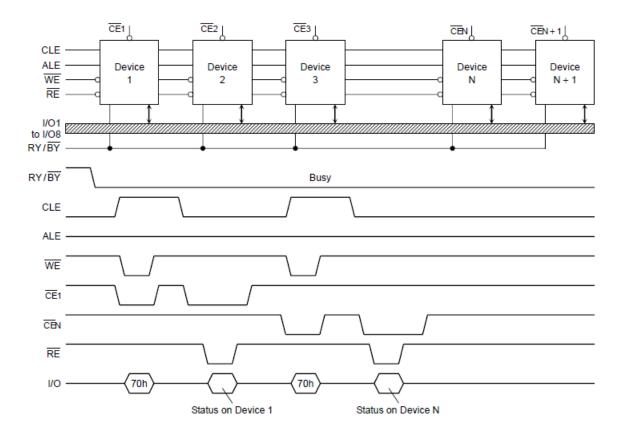

#### **Status Read**

The device automatically implements the execution and verification of the Program and Erase operations. The Status Read function is used to monitor the Ready/Busy status of the device, determine the result (pass/fail) of a Program or Erase operation, and determine whether the device is in Protect mode. The device status is output via the I/O port using  $\overline{RE}$  after a "70h" command input. The Status Read can also be used during a Read operation to find out the Ready/Busy status. The resulting information is outlined in Table 6.

Table 6. Status output table

|      | Definition                     |                   | Page Program<br>Block Erase | Cache Program | Read<br>Cache Read |

|------|--------------------------------|-------------------|-----------------------------|---------------|--------------------|

| I/O1 | Chip Status1<br>Pass: 0        | Fail: 1           | Pass/Fail                   | Pass/Fail     | Invalid            |

| 1/02 | Chip Status 2<br>Pass: 0       | Fail: 1           | Invalid                     | Pass/Fail     | Invalid            |

| I/O3 | Not Used                       |                   | 0                           | 0             | 0                  |

| I/O4 | Not Used                       |                   | 0                           | 0             | 0                  |

| I/O5 | Not Used                       |                   | 0                           | 0             | 0                  |

| I/O6 | Page Buffer Ready<br>Ready: 1  | y/Busy<br>Busy: 0 | Ready/Busy                  | Ready/Busy    | Ready/Busy         |

| 1/07 | Data Cache Ready<br>Ready: 1   | //Busy<br>Busy: 0 | Ready/Busy                  | Ready/Busy    | Ready/Busy         |

| I/O8 | Write Protect Not Protected :1 | Protected: 0      | Write Protect               | Write Protect | Write Protect      |

The Pass/Fail status on I/O1 and I/O2 is only valid during a Program/Erase operation when the device is in the Ready state.

#### Chip Status 1:

During a Auto Page Program or Auto Block Erase operation this bit indicates the pass/fail result.

During a Auto Page Programming with Data Cache operation, this bit shows the pass/fail results of the current page program operation, and therefore this bit is only valid when I/O6 shows the Ready state.

#### Chip Status 2:

This bit shows the pass/fail result of the previous page program operation during Auto Page Programming with Data Cache. This status is valid when I/O7 shows the Ready State.

The status output on the I/O6 is the same as that of I/O7 if the command input just before the 70h is not 15h or 31h.

Publication Date: Sep. 2018

Revision: 1.0 52/67

An application example with multiple devices is shown in the figure below.

System Design Note: If the RY /  $\overline{\text{BY}}$  pin signals from multiple devices are wired together as shown in the diagram, the Status Read function can be used to determine the status of each individual device.

#### Reset

The Reset mode stops all operations. For example, in case of a Program or Erase operation, the internally generated voltage is discharged to 0 volt and the device enters the Wait state.

Reset during a Cache Program/Page Copy may not just stop the most recent page program but it may also stop the previous program to a page depending on when the FF reset is input.

The response to a "FFh" Reset command input during the various device operations is as follows:

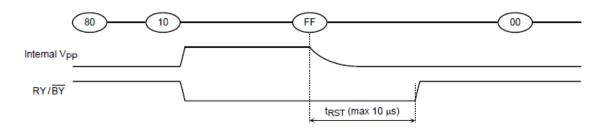

# When a Reset (FFh) command is input during programming

Publication Date: Sep. 2018 Revision: 1.0 53/67

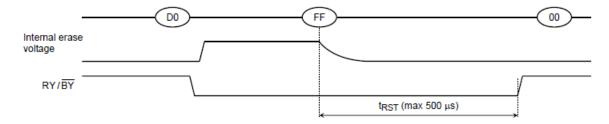

# When a Reset (FFh) command is input during erasing

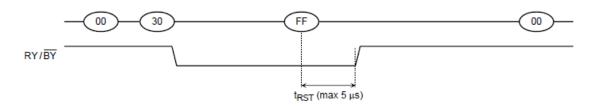

# When a Reset (FFh) command is input during Read operation

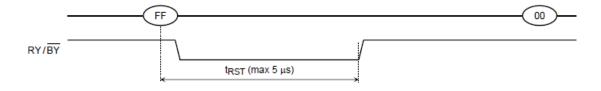

## When a Reset (FFh) command is input during Ready

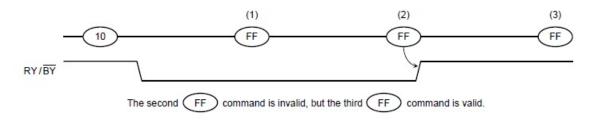

## When a Status Read command (70h) is input after a Reset

## When two or more Reset commands are input in succession

Publication Date: Sep. 2018 Revision: 1.0 54/67

## **APPLICATION NOTES AND COMMENTS**

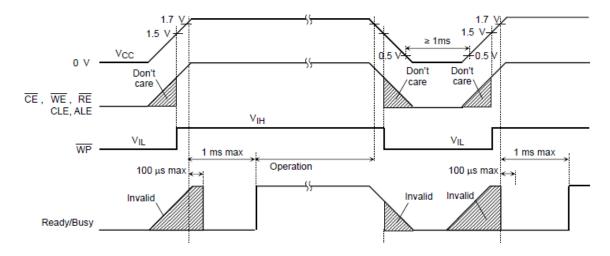

## (1) Power-on/off sequence:

The timing sequence shown in the figure below is necessary for the power-on/off sequence.

The device internal initialization starts after the power supply reaches an appropriate level in the power on sequence. During the initialization the device Ready/Busy signal indicates the Busy state as shown in the figure below. In this time period, the acceptable commands are FFh or 70h.

The WP signal is useful for protecting against data corruption at power-on/off.

#### (2) Power-on Reset

The following sequence is necessary because some input signals may not be stable at power-on.

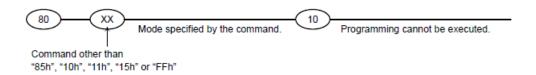

## (3) Prohibition of unspecified commands

The operation commands are listed in Table 3. Input of a command other than those specified in Table 3 is prohibited. Stored data may be corrupted if an unknown command is entered during the command cycle.

#### (4) Restriction of commands while in the Busy state

During the Busy state, do not input any command except 70h(71h) and FFh.

#### (5) Acceptable commands after Serial Input command "80h"

Once the Serial Input command "80h" has been input, do not input any command other than the Column Address Change in Serial Data Input command "85h", Auto Program command "10h", Multi Page Program command "11h", Auto Program with Data Cache Command "15h", or the Reset command "FFh".

If a command other than "85h", "10h", "11h", "15h" or "FFh" is input, the Program operation is not performed and the device operation is set to the mode which the input command specifies.

## (6) Addressing for program operation

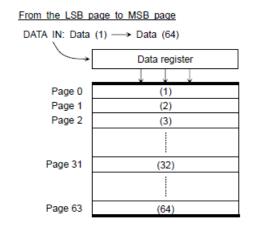

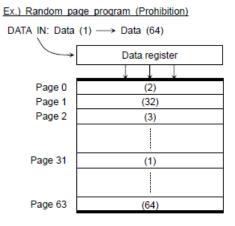

Within a block, the pages must be programmed consecutively from the LSB (least significant bit) page of the block to MSB (most significant bit) page of the block. Random page address programming is prohibited.

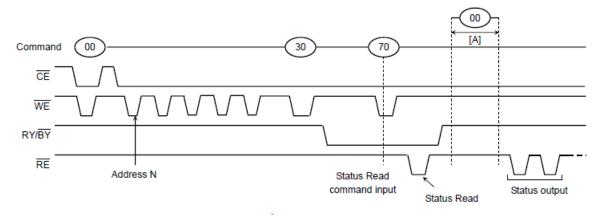

#### (7) Status Read during a Read operation

The device status can be read out by inputting the Status Read command "70h" in Read mode. Once the device has been set to Status Read mode by a "70h" command, the device will not return to Read mode unless the Read command "00h" is inputted during [A]. If the Read command "00h" is inputted during [A], Status Read mode is reset, and the device returns to Read mode. In this case, data output starts automatically from address N and address input is unnecessary.

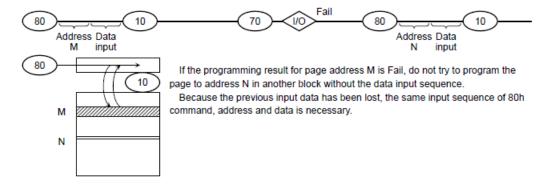

#### (8) Auto programming failure

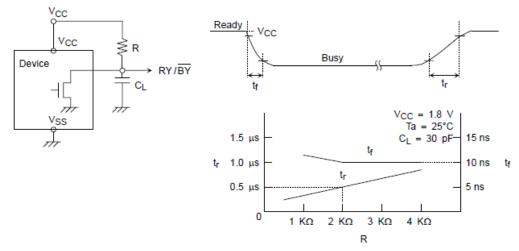

# (9) RY / $\overline{BY}$ : termination for the Ready/Busy pin (RY / $\overline{BY}$ )

A pull-up resistor needs to be used for termination because the RY /  $\overline{\text{BY}}$  buffer consists of an open drain circuit.

This data may vary from device to device.

We recommend that you use this data as a reference when selecting a resistor value.

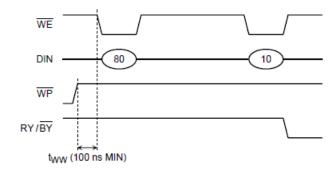

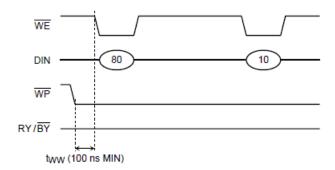

# (10) Note regarding the $\overline{WP}$ signal

The Erase and Program operations are automatically reset when  $\overline{\text{WP}}$  goes Low. The operations are enabled and disabled as follows:

# **Enable Programming**

#### Disable Programming

## **Enable Erasing**

# Disable Erasing

Publication Date: Sep. 2018 Revision: 1.0 59/67

## (11) When six address cycles are input

Although the device may read in a sixth address, it is ignored inside the chip.

# Read operation

## Program operation

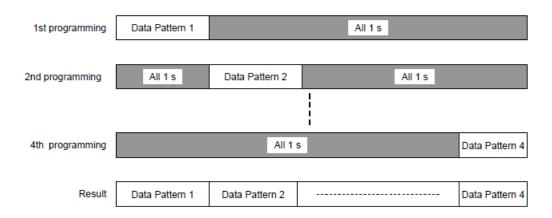

## (12) Several programming cycles on the same page (Partial Page Program)

Each segment can be programmed individually as follows:

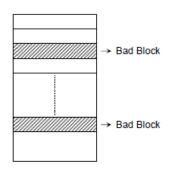

## (13) Invalid blocks (bad blocks)

The device occasionally contains unusable blocks. Therefore, the following issues must be recognized:

Please do not perform an erase operation to bad blocks. It may be impossible to recover the bad block information if the information is erased.

Check if the device has any bad blocks after installation into the system.

Refer to the test flow for bad block detection. Bad blocks which are detected by the test flow must be managed as unusable blocks by the system.

A bad block does not affect the performance of good blocks because it is isolated from the bit lines by select gates.

The number of valid blocks over the device lifetime is as follows:

|                           | MIN  | TYP. | MAX  | UNIT  |

|---------------------------|------|------|------|-------|

| Valid (Good) Block Number | 2008 | _    | 2048 | Block |

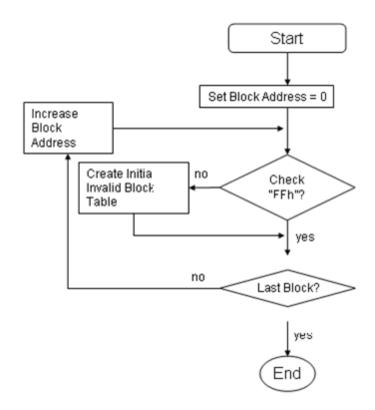

## Identifying Initial Invalid Block(s) and Block Replacement Management

All device locations are erased (FFh) except locations where the initial invalid block(s) information is written prior to shipping. The initial invalid block(s) status is defined by the 1st byte in the spare area. ESMT makes sure that either the 1st or 2nd page of every initial invalid block has non-FFh data at the 1st byte column address in the spare area.

Do not erase or program factory-marked bad blocks. The host controller must be able to recognize the initial invalid block information and to create a corresponding table to manage block replacement upon erase or program error when additional invalid blocks develop with Flash memory usage.

Check "FFh" at the 1st Byte column address in the spare area of the 1st and 2nd page in the block.

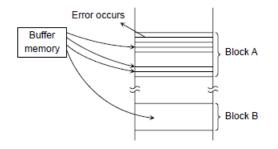

(14) Failure phenomena for Program and Erase operations

The device may fail during a Program or Erase operation.

The following possible failure modes should be considered when implementing a highly reliable system.

| FAILURE MODE |                     | DETECTION AND COUNTERMEASURE SEQUENCE         |

|--------------|---------------------|-----------------------------------------------|

| Block        | Erase Failure       | Status Read after Erase → Block Replacement   |

| Page         | Programming Failure | Status Read after Program → Block Replacement |

| Read         | Bit Error           | ECC Correction / Block Refresh                |

- ECC: Error Correction Code. 8 bit correction per 512 Bytes is necessary.

- Block Replacement

#### Program

When an error happens in Block A, try to reprogram the data into another Block (Block B) by loading from an external buffer. Then, prevent further system accesses to Block A (by creating a bad block table or by using another appropriate scheme).

#### **Erase**

When an error occurs during an Erase operation, prevent future accesses to this bad block (again by creating a table within the system or by using another appropriate scheme).

- (15) Do not turn off the power before write/erase operation is complete. Avoid using the device when the battery is low. Power shortage and/or power failure before write/erase operation is complete will cause loss of data and/or damage to data.

- (16) The number of valid blocks is on the basis of single plane operations, and this may be decreased with two plane operations.

#### (17) Reliability Guidance

This reliability guidance is intended to notify some guidance related to using NAND flash with 8 bit ECC for each 512 bytes. For detailed reliability data, please refer to reliability note.

Although random bit errors may occur during use, it does not necessarily mean that a block is bad.

Generally, a block should be marked as bad when a program status failure or erase status failure is detected.

The other failure modes may be recovered by a block erase.

ECC treatment for read data is mandatory due to the following Data Retention and Read Disturb failures.

#### Write/Erase Endurance

Write/Erase endurance failures may occur in a cell, page, or block, and are detected by doing a status read after either an auto program or auto block erase operation. The cumulative bad block count will increase along with the number of write/erase cycles.

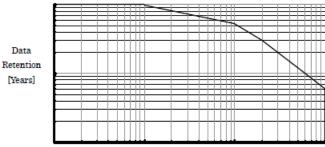

#### Data Retention

The data in memory may change after a certain amount of storage time. This is due to charge loss or charge gain. After block erasure and reprogramming, the block may become usable again.

Here is the combined characteristics image of Write/Erase Endurance and Data Retention.

Write/Erase Endurance [Cycles]

#### Read Disturb

A read operation may disturb the data in memory. The data may change due to charge gain. Usually, bit errors occur on other pages in the block, not the page being read. After a large number of read cycles (between block erases), a tiny charge may build up and can cause a cell to be soft programmed to another state. After block erasure and reprogramming, the block may become usable again.

Publication Date: Sep. 2018 Revision: 1.0 64/67

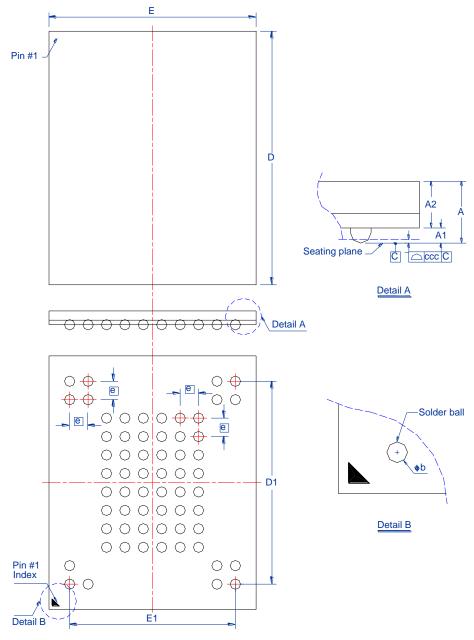

## PACKING DIMENSIONS

# 63-BALL NAND Flash (9x11 mm)

|                       | Di                  | mension in mi | n     | Dimension in inch |       |       |  |

|-----------------------|---------------------|---------------|-------|-------------------|-------|-------|--|

| Symbol                | Min                 | Norm          | Max   | Min               | Norm  | Max   |  |

| Α                     |                     |               | 1.00  |                   |       | 0.039 |  |

| <b>A</b> <sub>1</sub> | 0.25                |               | 0.35  | 0.010             |       | 0.014 |  |

| $A_2$                 |                     | 0.60 BSC      |       | 0.024 BSC         |       |       |  |

| Фb                    | 0.40                |               | 0.50  | 0.016             |       | 0.020 |  |

| D                     | 10.90               | 11.00         | 11.10 | 0.429             | 0.433 | 0.437 |  |

| E                     | 8.90                | 9.00          | 9.10  | 0.350             | 0.354 | 0.358 |  |

| D <sub>1</sub>        | 0.346 BSC 0.346 BSC |               |       | 0.346 BSC         |       |       |  |

| E <sub>1</sub>        |                     | 7.20 BSC      |       | 0.283 BSC         |       |       |  |

| е                     | 0.8 BSC             |               |       | 0.031 BSC         |       |       |  |

| ccc                   |                     |               | 0.10  |                   |       | 0.004 |  |

**Controlling dimension: Millimeter.**

# **Revision History**

| Revision | Date       | Description              |

|----------|------------|--------------------------|

| 0.1      | 2017.11.14 | Original                 |

| 0.2      | 2018.01.23 | Modify bad block marking |

| 1.0      | 2018.09.18 | Delete Preliminary       |

Publication Date: Sep. 2018 Revision: 1.0 66/67

# **Important Notice**

All rights reserved.

No part of this document may be reproduced or duplicated in any form or by any means without the prior permission of ESMT.

The contents contained in this document are believed to be accurate at the time of publication. ESMT assumes no responsibility for any error in this document, and reserves the right to change the products or specification in this document without notice.

The information contained herein is presented only as a guide or examples for the application of our products. No responsibility is assumed by ESMT for any infringement of patents, copyrights, or other intellectual property rights of third parties which may result from its use. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of ESMT or others.

Any semiconductor devices may have inherently a certain rate of failure. To minimize risks associated with customer's application, adequate design and operating safeguards against injury, damage, or loss from such failure, should be provided by the customer when making application designs.

ESMT's products are not authorized for use in critical applications such as, but not limited to, life support devices or system, where failure or abnormal operation may directly affect human lives or cause physical injury or property damage. If products described here are to be used for such kinds of application, purchaser must do its own quality assurance testing appropriate to such applications.

Publication Date: Sep. 2018 Revision: 1.0 67/67