F5N50K-TC Power MOSFET

# 5.0A, 500V N-CHANNEL POWER MOSFET

#### ■ DESCRIPTION

The UTC **F5N50K-TC** is a N-channel power MOSFET adopting UTC's advanced technology to provide customers with DMOS, planar stripe technology. This technology is designed to meet the requirements of the minimum on-state resistance and perfect switching performance. It also can withstand high energy pulse in the avalanche and communication mode.

The UTC **F5N50K-TC** can be used in applications, such as active power factor correction, high efficiency switched mode power supplies, electronic lamp ballasts based on half bridge topology.

#### **■** FEATURES

- \*  $R_{DS(ON)} \le 1.8\Omega$  @  $V_{GS}=10V$ ,  $I_{D}=2.5A$

- \* 100% avalanche tested

- \* High switching speed

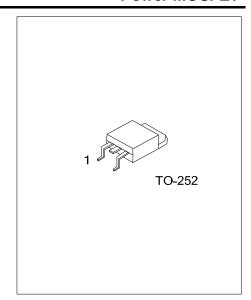

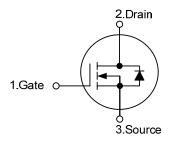

### ■ SYMBOL

#### **■ ORDERING INFORMATION**

| Ordering Number |               | Doolsons | Pin Assignment |   |   | Daakina   |  |

|-----------------|---------------|----------|----------------|---|---|-----------|--|

| Lead Free       | Halogen Free  | Package  | 1              | 2 | 3 | Packing   |  |

| F5N50KL-TN3-R   | F5N50KG-TN3-R | TO-252   | G              | D | S | Tape Reel |  |

Note: Pin Assignment: G: Gate D: Drain S: Source

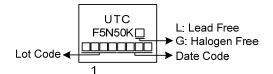

F5N50KG-TN3-R

(1)Packing Type

(2)Package Type

(3)Green Package

(3) G: Halogen Free and Lead Free, L: Lead Free

www.unisonic.com.tw 1 of 6

F5N50K-TC

## ■ MARKING

F5N50K-TC Power MOSFET

## ■ ABSOLUTE MAXIMUM RATINGS (T<sub>C</sub>=25°C, unless otherwise specified)

| PARAMETER                          |                                     | SYMBOL           | RATINGS            | UNIT |

|------------------------------------|-------------------------------------|------------------|--------------------|------|

| Drain-Source Voltage               |                                     | $V_{DSS}$        | 500                | V    |

| Gate-Source Voltage                |                                     | $V_{GSS}$        | ±30                | V    |

| Drain Current                      | Continuous                          | I <sub>D</sub> 5 |                    | Α    |

|                                    | Pulsed (Note 2)                     | $I_{DM}$         | 20                 | Α    |

| Avalanche Energy                   | anche Energy Single Pulsed (Note 3) |                  | 104                | mJ   |

| Peak Diode Recovery dv/dt (Note 4) |                                     | dv/dt            | 6.3                | V/ns |

| Power Dissipation                  |                                     | $P_D$            | 54                 | W    |

| Junction Temperature               |                                     | $T_J$            | +150               | °C   |

| Storage Temperature                |                                     | $T_{STG}$        | -55 ~ <b>+</b> 150 | °C   |

Notes: 1. Absolute maximum ratings are those values beyond which the device could be permanently damaged.

Absolute maximum ratings are stress ratings only and functional device operation is not implied.

- 2. Repetitive Rating: Pulse width limited by maximum junction temperature

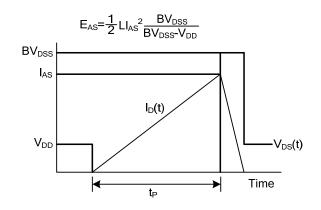

- 3. L = 16mH,  $I_{AS}$  = 3.6A,  $V_{DD}$  = 50V,  $R_{G}$  = 25 $\Omega$ , Starting  $T_{J}$  = 25 $^{\circ}$ C

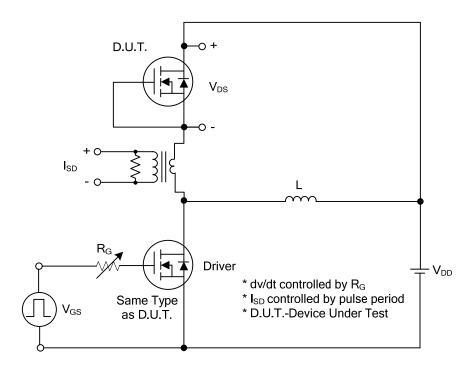

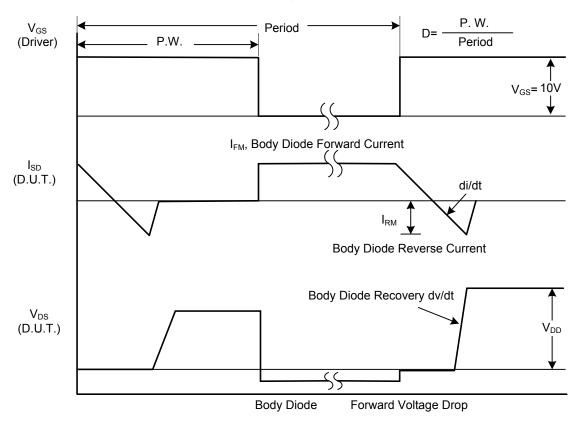

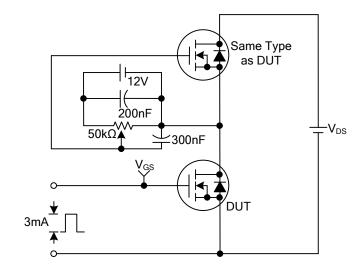

- 4.  $I_{SD} \le 5.0A$ , di/dt  $\le 200A/\mu s$ ,  $V_{DD} \le BV_{DSS}$ , Starting  $T_J = 25^{\circ}C$

#### ■ THERMAL DATA

| PARAMETER           | SYMBOL          | RATINGS | UNIT |  |

|---------------------|-----------------|---------|------|--|

| Junction to Ambient | $\theta_{JA}$   | 110     | °C/W |  |

| Junction to Case    | θ <sub>JC</sub> | 2.3     | °C/W |  |

#### ■ **ELECTRICAL CHARACTERISTICS** (T<sub>J</sub> =25°C, unless otherwise specified)

| PARAMETER                                   |            | SYMBOL              | TEST CONDITIONS                                                   | MIN | TYP  | MAX  | UNIT |

|---------------------------------------------|------------|---------------------|-------------------------------------------------------------------|-----|------|------|------|

| OFF CHARACTERISTICS                         |            |                     |                                                                   |     |      |      |      |

| Drain-Source Breakdown Voltage              |            | $BV_{DSS}$          | $I_D=250\mu A, V_{GS}=0V$                                         | 500 |      |      | V    |

| Drain-Source Leakage Current                |            | $I_{DSS}$           | V <sub>DS</sub> =500V, V <sub>GS</sub> =0V                        |     |      | 1    | μΑ   |

| Gate- Source Leakage Current                | Forward    |                     | $V_{GS}$ =30V, $V_{DS}$ =0V                                       |     |      | 100  | nA   |

|                                             | Reverse    | I <sub>GSS</sub>    | $V_{GS}$ =-30V, $V_{DS}$ =0V                                      |     |      | -100 | nA   |

| ON CHARACTERISTICS                          |            |                     |                                                                   |     |      |      |      |

| Gate Threshold Voltage                      |            | $V_{GS(TH)}$        | $V_{DS}=V_{GS}$ , $I_D=250\mu A$                                  |     |      | 4.0  | V    |

| Static Drain-Source On-State Resistance     |            | R <sub>DS(ON)</sub> | V <sub>GS</sub> =10V, I <sub>D</sub> =2.5A                        |     |      | 1.8  | Ω    |

| DYNAMIC PARAMETERS                          |            |                     |                                                                   |     |      |      |      |

| Input Capacitance                           |            | $C_{ISS}$           | \\\\ -0\\\\ -25\\                                                 |     | 585  |      | pF   |

| Output Capacitance                          |            | Coss                | V V <sub>GS</sub> =0V,V <sub>DS</sub> =25V,<br>-f=1.0MHz          |     | 58   |      | pF   |

| Reverse Transfer Capacitance                |            | $C_{RSS}$           |                                                                   |     | 7.0  |      | pF   |

| SWITCHING PARAMETERS                        |            |                     |                                                                   |     |      |      |      |

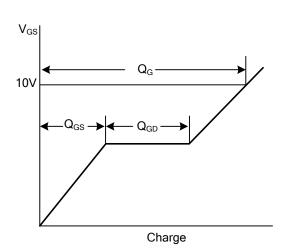

| Total Gate Charge (Note 1)                  |            | $Q_G$               | V <sub>DS</sub> =200V, V <sub>GS</sub> =10V, I <sub>D</sub> =5.0A |     | 5.2  |      | nC   |

| Gate to Source Charge                       |            | $Q_GS$              | I <sub>G</sub> =1mA (Note 1, 2)                                   |     | 2.8  |      | nC   |

| Gate to Drain Charge                        |            | $Q_GD$              | IG-IIIA (Note 1, 2)                                               |     | 1.1  |      | nC   |

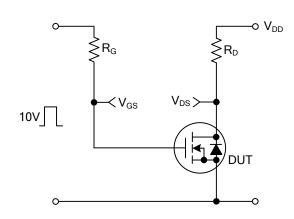

| Turn-ON Delay Time (Note 1)                 |            | $t_{D(ON)}$         |                                                                   |     | 7.6  |      | ns   |

| Rise Time                                   |            | $t_R$               | $V_{DD}$ =30V, $V_{GS}$ =10V, $_{D}$ =0.75A,                      |     | 18.6 |      | ns   |

| Turn-OFF Delay Time                         |            | t <sub>D(OFF)</sub> | $R_G = 25\Omega$ (Note 1, 2)                                      |     | 36   |      | ns   |

| Fall-Time                                   |            | $t_{F}$             |                                                                   |     | 18   |      | ns   |

| SOURCE- DRAIN DIODE RATI                    | NGS AND CH | ARACTERIST          | ICS                                                               |     |      |      |      |

| Maximum Body-Diode Continuous Current       |            | I <sub>S</sub>      |                                                                   |     |      | 5    | Α    |

| Maximum Body-Diode Pulsed Current           |            | I <sub>SM</sub>     |                                                                   |     |      | 20   | Α    |

| Drain-Source Diode Forward Voltage (Note 1) |            | $V_{SD}$            | I <sub>S</sub> =5.0A, V <sub>GS</sub> =0V                         |     |      | 1.4  | V    |

| Body Diode Reverse Recovery Time (Note 1)   |            | t <sub>rr</sub>     | I <sub>S</sub> =5.0A, V <sub>GS</sub> =0V,                        |     | 102  |      | ns   |

| Body Diode Reverse Recovery Charge          |            | $Q_{rr}$            | dI <sub>F</sub> /dt=100A/µs                                       |     | 0.33 |      | μC   |

Notes: 1. Pulse Test: Pulse width ≤ 300µs, Duty cycle ≤ 2%

2. Essentially independent of operating temperature.

## ■ TEST CIRCUITS AND WAVEFORMS

## Peak Diode Recovery dv/dt Test Circuit

Peak Diode Recovery dv/dt Waveforms

F5N50K-TC Power MOSFET

## **■ TEST CIRCUITS AND WAVEFORMS**

**Gate Charge Test Circuit**

**Gate Charge Waveforms**

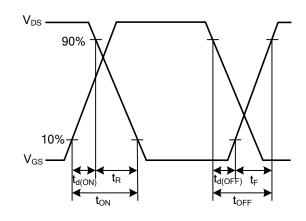

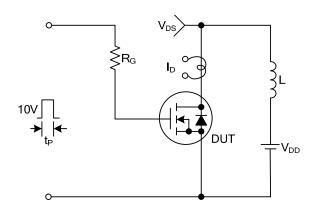

**Resistive Switching Test Circuit**

**Resistive Switching Waveforms**

**Unclamped Inductive Switching Test Circuit**

**Unclamped Inductive Switching Waveforms**

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. UTC reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.