May 2024

# **FAN41501 Ground Fault Interrupter Self-Test Digital Controller**

#### **Features**

- Meets 2015 UL943 Self-Test GFCI Requirement

- Internal 1-Second and 90-Minute Self-Test Timers

- Periodic Functional Testing for Key GFIC Components: GFCI Controller, Solenoid, Sense Transformer, and Silicon-Controlled Rectifier (SCR)

- Periodic EOL Testing without Compromising Normal GFCI Protection

- Built-in Noise Filters Reduce False EC ana.

- Automatic EOL Reset Capability

- Easily Added to Existing GF( Applica

- Built-in 5 V Shunt R Jula.or

- Energy-Saving Sys m Solu on

- Minimum kternal Co.

- Space Saving Sup SOT™ 6-Pin Packag

#### nlic: ions

- GrCl Ou put Receptable

- GFC! Circuit Breakers

- Portable GFCI Cords

# Description

tal untroller for periodic The FAN41501 is a k Ground Fault Circuit functional to ing Interrupte (G. 1) corponents In combination with an existing Fathild Controller, it periodically tests for peration of the GFCI controller, solenoid, nse transurmer SCR, and other discrete co non its without disrupting power to the load or com, amising normal GFC1 protection functionality. If the FAN/1501 detects a faulty GFCI component, it generates an End of Life (EOL) fault signal that can be used to deny power and/or automatically reset after the denial of power.

When the AC power is first applied, an internal timer starts a test cycle at one second. After this initial test cycle, the internal timer starts a test cycle every 90 minutes. During a test cycle, the FAN41501 simulates a ground fault and monitors the key GFCI components. If the FAN41501 detects a component fault, it verifies the ault several times to prevent a false EOL signal. At no time during a test cycle is the normal GFCI protection disabled or compromised.

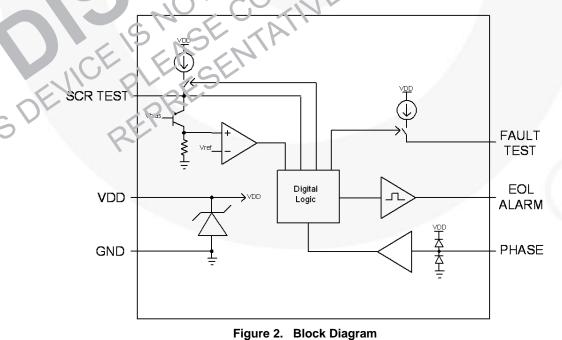

The FAN41501 includes a 5 V shunt regulator, onesecond timer, 90-minute timer, digital control logic, detection comparators, and an EOL driver output.

The FAN41501, together with a GFCI controller such as FAN4149, provides a complete UL943 GFCI function with automatic monitoring capability, low system power, and a minimum number of external components.

The 6-pin, SuperSOT™ package enables a low-cost, compact design and layout.

# **Ordering Information**

| Part Number | Operating<br>Temperature Range | Package                                 | Packing Method |  |

|-------------|--------------------------------|-----------------------------------------|----------------|--|

| FAN41501SX  | -35°C to +85°C                 | 6-Lead, SuperSOT™, JEDEC M0-193, 1.6 mm | Tape and Reel  |  |

# **Typical Application**

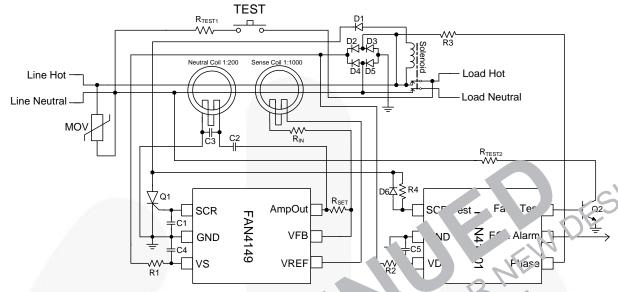

Figure 1. Typicai api. ati.

# Table 1. Typical Values (3)

R4: 909 tΩ Re(12:)11 R<sub>3</sub> ¹ MΩ R1: 75 k $\Omega$ R2: 75  $k\Omega$

$R_{SET}$ : 750  $k\Omega^{(4)}$ R<sub>IN</sub>: 470 Ω  $R_{Tes}$ , 15 k $\Omega$

C1: 22 nF C2: 10 n 3: 5.6 ni C5: 1 µF

#### Notes:

- Contact Fairchild S niconductor ... self-tos, requirement details.

- Portions of the actic as subject to U.S. paterns 8,005,516 and 8,760,824.

- XMFR: Mr ,netic Met. 50 J/F3006.

- nse coil characteristics and application. Value 1ep

# **Pin Configuration**

Figure 3. Pin Assignments

# **Pin Definitions**

| 1                                   | Name       | De rip on                                 |  |

|-------------------------------------|------------|-------------------------------------------|--|

| '                                   | SCR Test   | SCR test input for SCR functionalit       |  |

| 2 GND Ground for FAN41501 circuitry |            | Ground for FAN41501 circuitry             |  |

| 3                                   | VDD        | Voltage supply input for V4150 ircu y     |  |

| 4                                   | Phase      | Phase input for V <sub>AC</sub> requent   |  |

| 5                                   | EOL Alarm  | Alarm for end life s. hal                 |  |

| 6                                   | Fault Test | Fault to tou igno ground-fault simulation |  |

| 0                                   |            | RECONTACTOR INFO                          |  |

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           | Parameter                          | Condition                                            |      | Max. | Unit |

|------------------|------------------------------------|------------------------------------------------------|------|------|------|

| Icc              | Supply Current                     | Continuous Current, VDD to GND                       |      | 10   | mA   |

| \/               | Supply Voltage                     | Continuous Voltage, VDD to GND                       | -0.8 | 7.0  | V    |

| V <sub>CC</sub>  |                                    | Continuous Voltage to Neutral, All Other Pins        | -0.8 | 7.0  | V    |

| T <sub>STG</sub> | Storage Temperature Range          |                                                      |      | +150 | °C   |

| ESD              | Electrostatic Discharge Capability | Human Body Model, ANSI / ESDA / JEDEC<br>JS-001-2012 |      | 2.5  | av.  |

|                  |                                    | Charged Device Model, JESD22-C1                      |      | 1.0  |      |

# **Recommended Operating Conditions**

The Recommended Operating Conditions table definer the notions to actual device operation. Recommended operating conditions are specified to ensure optimal to a data sine specifications. Fairchild does not recommend exceeding them or designing to Absolute Malmum Kings. Unless otherwise specified, refer to Figure 1.  $T_A=25^{\circ}C$ ,  $I_{SHUNT}=1$  mA, and phase=60 Hz.

| Symbol               | Parameter                            | Conditions                            | Min.  | 7yp.  | Max.  | Unit |

|----------------------|--------------------------------------|---------------------------------------|-------|-------|-------|------|

| $V_{REG}$            | Power Supply Shunt R gulator Voltage | DD to GND                             | 5.10  | 5.35  | 5.70  | V    |

| V                    | Under-Voltaç Reset                   | YDD to GND                            | 2.2   | 2.5   | 2.7   | V    |

| $V_{UVLO\_RST}$      |                                      | Rising 'Avs'eresis                    |       | 150   |       | mV   |

| ΙQ                   | Qu scer yre                          | ソロロ to GND 4.5 V                      | 350   | 450   | 550   | μA   |

| t <sub>FIRST</sub>   | 'st Timer riod                       | V <sub>DD</sub> > 2.5 V               | 0.812 | 1.016 | 1.220 | S    |

| 4PER                 | Pe dic ı mer                         | Stendy State                          | 4400  | 5400  | 6400  | S    |

| тоит                 | est Cycle Tin e Out                  | Fault Testing                         | 54    | 66    | 78    | ms   |

| t <sub>PHA</sub>     | Phase Continuity Chock Time Out      | Phase Pin Continuity Check at Startup | 40    | 60    | 80    | ms   |

| V <sub>PHASE_H</sub> | Phase Voltage Clamp FIC'1            | Ι <sub>Η</sub> = 170 μΑ               | 5.8   | 6.3   | 6.6   | V    |

| V PHASE_L            | Phase Voltage Cla np LOW             | I <sub>L</sub> = -170 μA              | -0.8  | -0.6  | -0.4  | V    |

| PHASE_MAX            | Phase Maximum Current                | I <sub>SHUNT</sub> = 1.5 mA           | -300  |       | 300   | μΑ   |

| V <sub>SCR_H</sub>   | SCR Test Input Clamp HIGH            | I <sub>H</sub> = 170 μA               | 5.0   | 5.4   | 5.8   | V    |

| V <sub>SCR_L</sub>   | SCR Test Input Clamp LOW             | I <sub>L</sub> = -170 μA              | -0.8  | -0.6  | -0.4  | V    |

| I <sub>SCR_MAX</sub> | SCR Test Maximum Current             | I <sub>SHUNT</sub> = 1.5 mA           | -300  |       | 300   | μΑ   |

| I <sub>TEST</sub>    | Fault Test Current                   | Test Cycle                            | 400   | 500   |       | μΑ   |

| $V_{EOL\_L}$         | EOL Alarm V <sub>OL</sub>            | DL Alarm V <sub>OL</sub> No Load      |       | 0     | 200   | mV   |

| $V_{EOL_H}$          | EOL Alarm V <sub>OH</sub>            | No Load                               | 4.80  | 5.25  |       | V    |

| f <sub>EOL</sub>     | EOL Alarm                            | Latched Fault Output                  | 3.00  | 3.75  | 4.25  | Hz   |

| I <sub>EOL</sub>     | EOL Alarm I <sub>OUT</sub>           | I <sub>SHUNT</sub> = 2.0 mA           | 1     |       | _     | mA   |

# **Functional Description**

(Refer to Figure 1)

Starting in June 2015, UL943 will require all permanently connected GFCI products to perform a self test function. The FAN41501, together with a GFI controller device – like the FAN4149 – provides GFI fault protection and periodic self testing of the key GFCI components: solenoid, SCR, GFI controller, sense coil, and other discrete components.

The FAN41501 has an internal 5.35 V shunt regulator. With diodes D2-5 and resistor R2, the shunt regulator clamps the FAN41501  $V_{DD}$  supply voltage to 5.35 V. Capacitor C5 provides bias during the V<sub>AC</sub> zero phase crossing so the FAN41501 is continuously biased. When power is first applied, an internal Power-On-Reset (POR) circuit detects when V<sub>DD</sub> is greater than 2.5 V. The POR circuit generates an internal reset pulse and initializes a one-second timer. After one second, the first self-test cycle starts. During the positive half cycle when the "line-hot" voltage is positive with respect to the "lineneutral" voltage, the SCR anode voltage is monitored by means of resistor R4 connected to pin 1 (SCR Test). The FAN41501 clamps this pin to VDD, mirrors the current through R4 to an internal low-pass filter ci all and compares its value to an internal re rence threshold. When the current level exceeds the refunce threshold, an internal latch is set. This tes. . the continuity of the solenoid and The thres. J level is determined by:

$$Vth_{rms} = (65 \mu A \times R) \qquad (1)$$

where  $Vth_{rm}$  is the ms  $V_{AC}$  iput voltage with a tolerance  $t \pm t 0\%$ .

With the commende application values the SCR anode voltal must be seed a whist-case peak voltage of uppromations of control of the seed in a line with shell a voltage value is obtained to allow this test a particular of the province of voltage sages of dition.

To tex the functionality of the GFCI convoller, sense coil, and SCR; a simulated ground fault condition is generaled. Like the SCR Test pin, the Phase pin (pin 4) is clarged to V<sub>DD</sub> + 700 mV, mirrors the current through k3 .o an internal low-pass filter circuit, and compares its value to an internal reference. This internal circuit detects when the phase signal is near the end of the positive half cycle. When this occurs, an internal current source is enabled to bias the SCR Test pin. This prevents the SCR anode voltage from discharging to zero during the negative half cycle since it is reversebiased by diode D1. At the end of the positive half cycle. the FAN41501 generates a current pulse for the Fault Test pin (pin 6). This current pulse enables transistor Q2, which biases the collector voltage of Q2 to a low voltage. During the negative half cycle when the lineneutral voltage is positive with respect to the line-hot voltage, current flows through resistor R<sub>TEST2</sub> when Q2 is enabled. This current creates a simulated ground fault from line-neutral to load hot. This current is detected by

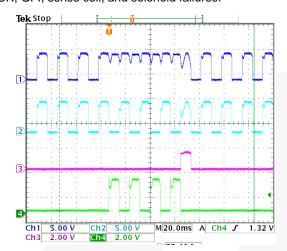

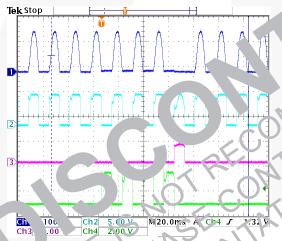

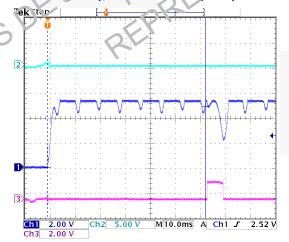

the GFI controller (i.e. FAN4149) and, when it exceeds the programmed trip threshold set by R<sub>SET</sub> (typically 5 mA<sub>rms</sub>), the controller enables the SCR Q1 (see FAN4149 datasheet for I<sub>FAULT</sub> trip threshold equation). The SCR quickly discharges the anode voltage, which is pre-biased by the FAN41501 control logic. The discharge of the anode voltage also biases the voltage at the SCR Test pin to a low voltage by forward-biasing diode D6. The FAN41501 monitors the SCR Test pin during this test cycle and sets a latch if the SCR is triggered. The simulated ground fault tests for the functionality of the controller, R1, D1 D2-5<sup>(5)</sup>, sense coil, and SCR without opening the lace acts. The load contacts do not open during a test cause D1 is reversed biased, which reverse to rent to menergizing the solenoid. Once the ANA 01 c is the triggering of the SCR, the culint per for O2 is disabled and the bias current for pin R. At i emoved. This disables the SCR so it during the next positive half cycle the no ener zed. With the recommended solenoid tion blue a simulated ground fault triggers ap; with a VAC input voltage greater than `e t V<sub>rms</sub> If a unrerent voltage threshold is required, the R<sub>TL 2</sub> sistor can be adjust to (per the FAN4149 data eet). Figure 4, Figure 5 and Figure 6 show a passing selitest cycle. The wavelown of channel 4 shows when the C2 transistor is enabled and a ground fault is simulated by the current through resistor R<sub>TEST2</sub>. The channel 3 waveform shows the gate of the SCR Q1. Figure 3 shows the pre-bias for the SCR anode voltage, waveforing thannel 1. Figure 6 illustrates that, when the gate of the SCR is enabled by the controller, the voltage of the SCR anode is quickly discharged. The FAN41501 detects this and a self-test cycle is completed with all of the required components passing. The Q2 bias is disabled, which causes the GFCI controller to disable the SCR gate bias.

#### Note:

5. Redundant diodes may be required.

If the first self-test cycle passes after power up, subsequent self-test cycles occur every 90 minutes. At no time does the FAN41501 disable the normal controller GFI protection circuitry.

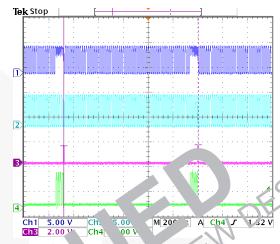

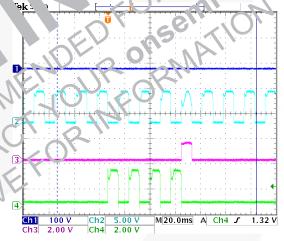

If any one of the above self tests fail, the FAN41501 repeats the self testing until a 66 ms timer expires. If this occurs, the EOL latch is enabled and the FAN41501 EOL Alarm pin 5 goes HIGH. This signal can be connected to a separate SCR or to the gate of Q1 with a series diode. When the EOL Alarm goes HIGH, the SCR is enabled and energizes the solenoid, which opens the load contacts. When the EOL Alarm pin goes HIGH, if it is connected to the gate of an SCR, VDD drops below 2.5 V. This generates a Power-On-Reset that resets the logic and repeats a self-test cycle in one second. Figure 7 to Figure 10 show a FAN41501 self-test cycle for a SCR, GFI controller, sense coil, and solenoid failure.

The self test cycle lasts for 66 ms to allow four self-test cycle attempts. After the timer has expired, the EOL alarm is enabled. Figure 7 to Figure 10 show an example of the EOL alarm signal connected to the gate of an SCR. When the EOL alarm signal is enabled, the  $V_{DD}$  voltage is discharged, which causes a POR. The EOL alarm is disabled and a self-test cycle is repeated in one second.

In addition to the above GFCI tests, the FAN41501 also performs a pin 4 (Phase pin) continuity check when power is first detected. When  $V_{DD}$  exceeds 2.5 V, pin 4 is checked for an open or short. If this continuity check fails after 60 ms, the EOL alarm is enabled. Figure 11 shows an example of the Phase pin with R3 removed (floating pin). After approximately 60ms, the EOL alarm is enabled.

After a self-test cycle failure, the EOL alarm is latched HIGH for 133 ms. This signal generates a repetitive 3.75 Hz digital square wave. There are two ways to reset the EOL alarm signal. The first is POR as described above, which can occur if the AC power is cycled. Since it may be undesirable to cycle the AC power, the EOL alarm signal can also be connected to the gate of a SCR or "clamp diode" to generate a PO" If the EOL alarm signal is diode clamped when the LOL alarm signal goes HIGH, a high I<sub>OH</sub> current is generated. This current is dependent on R2 and C5, herever, the datasheet values are used, the typical I<sub>OH</sub>, ... can be greater than 5 mA. This given can be used to "latch on" a SCR and ca se V<sub>DD</sub> dr below 2.5 V, which generates a POP Figure 11 s ows the Vpp signal when the EOL at an signal conjected to the gate of a SCR with a sc es diodo. The nigh EOL alarm. IOH current caus 'DD drop slow 2.5 / during the DEVICE PLEASENTAT V<sub>AC</sub> zero cross ig.

Another way to reset the EOL alarm signal is to detect a successful manual test cycle. If the FAN41501 is latched in an EOL state and detects a "manual test" (i.e., the TEST button is pressed) the FAN41501 disables the EOL alarm and perform sa self-test cycle in one second. If an EOL alarm state has occurred due to a pin 4 continuity check failure, the "manual test" reset option is disabled.

Referring to Figure 1, the EOL alarm signal must be used to open the load contacts (power denial) if a selftest cycle fails for the tested components (with the exception for a solenoid or SCR open failure). As described above, this can be done with a redundant SCR or by connecting the EOL 2' and nal to Q1 via a series diode. If Q1 is used to o, n the id contacts, a gate resistor must be ad a fro. the CCI controller gate drive pin to the ate of the CC. If O1 or the solenoid fails due 'an circuit, a visual FO signal can be generated in leach find an denial. This can be accomplished y mak in the Jeries alook from the EOL Alarm pin o to gate f Q1 a LEO diode. This diode flas' eve sec additionally, an LED diode can be dde 11. with R<sub>TE sT2</sub> and the corlector of Q2. This L D a de ca., be used to provide a self-test signal at point and then every 90 conutes. If the self-test cycle ails, it flashes every sound.

n summary, the FAN415'1 can be added to an existing UL943 choult to comply with the 2015 UL self-test requirement. The small package size and the minimum required components allow for a compact, low-cost, GFC' self-test solution.

Cortact a Farchild Semiconductor representative for details about how to test the FAN41501 self-test features in production or for details about the 2015 UL943 self-test application requirements.

# **Typical Performance Characteristics**

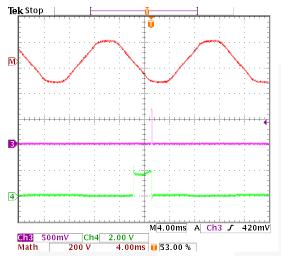

Pass testing of all key components. Refer to evaluation board (see www.fairchildsemi.com for details).

Figure 4. Pass GFCI, Sense Coil, Solenoid, SCR Tests; Ch Math: V<sub>AC</sub> Input 200 V/Div, Ch3: SCR Gate, Ch4: Fault Test (Pin 6)<sup>(6)</sup>

Figure Parts in lated Ground Fault Test;

Vac input 200 V/Div, Ch3: SCR Gate,

Ch4: Fault Test (Pin t)

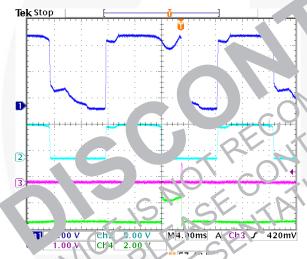

Figure 8. Pass Simulated Ground Fault Test; th1: SCR Test (Pin 1) Ch2: Phase (Pin 4), Ch3: SCR Gate, Ch4: Fault Test (Pin 6)<sup>(7)</sup>

#### Notes:

- 6. Anode voltage is tested during the positive half cycle (internal latch set when  $V_{AC} > 85 V_{rms}$ ).

- 7. During the simulated ground fault test, the SCR discharges the pre-biased SCR Test pin.

### **Ground Fault Tests**

SCR, GFI, sense coil, and solenoid failures.

Figure 7. SCR Test Ch1: SCR Test (Pin 1), Ch 2: Phase (Pin 4), Ch 3: EOL Alarm (Pin 5), Ch 4: Fault Test (Pin 6)<sup>(8)</sup>

Figu 8. CR To t Ch1: SCR Test (Pin 1); Ch2. 'hao (Pi 4); Ch3: FOL Alarm (Pin 5), Cha. Fault Test (Pin 6)<sup>(9)</sup>

Fur .. GFiri Sense Coi Tests Ch1: SCR Anode ...00 V/div). Ch2: Phase (Fin 4). Ch3: EOL Alarm (Pin 5), Ch4: Fault Test (Fin 6)<sup>(10)</sup>

Figure 10. Solenoid Test Ch1: SCR Anode (100 V/Div), Ch2: Phase (Pin 4), Ch3: EOL Alarm (Pin 5), Ch4: Fault Test (Pin 6)<sup>(11)</sup>

Figure 11. Phase Pin, Continuity Test; Ch1: VDD (Pin 3), Ch2: Phase (Pin 4), Ch3: EOL Alarm (Pin 5)<sup>(12,13)</sup>

#### Notes:

- This test is with the SCR disabled. The EOL alarm signal is enabled after "time out" 66 ms timer has expired. The EOL alarm signal is connected to the gate of a SCR.

- This test is the same as Figure 7, except for the time scale. After a self-test failure, an EOL alarm pulse is generated every one second.

- 10. This test is with the FAN4149 GFI controller disabled.

- 11. This test is with the solenoid open.

- 12. This test is with the Phase pin open.

- 13. If no signal is detected for the Phase pin within 60 ms of the POR, an EOL alarm is enabled. The SCR is enabled, which causes the V<sub>DD</sub> voltage to drop and generates a POR cycle.

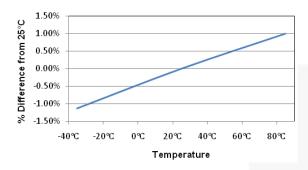

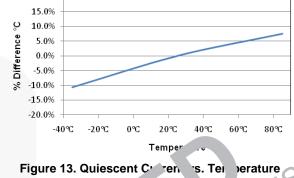

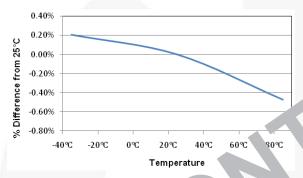

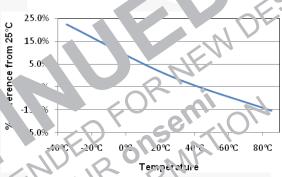

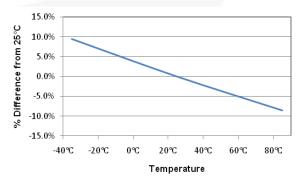

# **Typical Temperature Characteristics**

Figure 12. Shunt Regulator Voltage vs. Temperature

20.0%

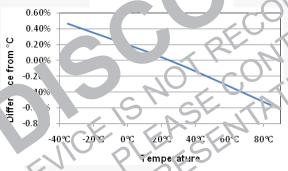

Figure 14. Under-Voltage Res .. Ten gratu.

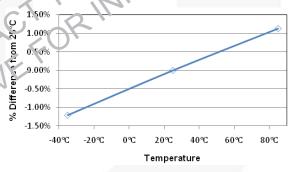

Figure 15. Phase Pin Continuity Check Time vs. Temperature

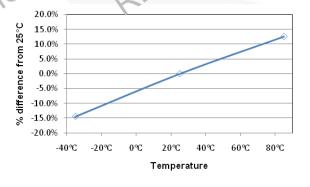

กัญนาย 16. Phase Pin Volage Clamp High vs. ∫e. nperature

Figure 17. SCR Test Pin Voltage Clamp High vs. Temperature

Figure 18. Fault Test Pin Current vs. Temperature

Figure 19. EOL Alarm Pin I<sub>OUT</sub> vs. Temperature

# **Physical Dimensions** SYMM E 0.95 -0.951.00 6 В 3.00 2.60 1.70 1.50 3 0.50 0.30 0.95 ◆ 0.20 M A B 1.90 RECOMME (0.30)-1.00 0.70 0.20 0.08 0.1 NOTES: UNLESS OTHERWISE SPECIFIED THIS PACKAGE CONFORMS TO JEDEC MO-193. VAR. AA, ISSUE C, DATED JANUARY 2000. ALL DIMENSIONS ARE IN MILLIMETERS. 0.25 0.55 0.35 SEATING PLANE -0.60 REF DETAIL A

Figure 20. 6-Lead, SuperSOT™-6, JEDEC M0-193, 1.6 mm

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: <a href="http://www.fairchildsemi.com/dwg/MA/MA06A.pdf">http://www.fairchildsemi.com/dwg/MA/MA06A.pdf</a>

For current packing container specifications, visit Fairchild Semiconductor's online packaging area: <a href="http://www.fairchildsemi.com/packing\_dwg/PKG-MA06A.pdf">http://www.fairchildsemi.com/packing\_dwg/PKG-MA06A.pdf</a>

MA06AREVD

#### **TRADEMARKS**

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

F-PFS™ AccuPower™ AX-CAP FRFET® BitSiC™ Global Power Resource GreenBridge™ Build it Now™ Green FPS™ CorePLUS™ CorePOWER™ Green FPS™ e-Series™ Gmax™ CROSSVOLT™

GTO™ CTL™ Current Transfer Logic™ IntelliMAX™ DEUXPEED® ISOPLANAR™

Dual Cool™ Making Small Speakers Sound Louder and Better™ EcoSPARK®

EfficientMax™ MegaBuck™ MICROCOUPLER™ ESBC™ MicroFET™ MicroPak™

Fairchild<sup>®</sup> MicroPak2™ Fairchild Semiconductor® MillerDrive™ FACT Quiet Series™ MotionMax™ FACT® mWSaver OptoHiT™ FastvCore™ OPTOLOGIC® FETBench™ OPTOPLANAR® **FPS™**

PowerTrench® PowerXS™ Programmable Active Droop™ **QFĔT** OS™ Quiet Series™

Saving our world, 1mW/W/kW at a SignalWise™

SmartMax™ SMART START™ Solutions for Your Success STEALTH1

SuperFET® Sup upe erS

RapidConfigure™

St MC Syn T Sync-

Semiconducto

SYSTEM GENERAL®

TinyBoost® TinyBuck<sup>®</sup> TinyCalc™ TinyLogic<sup>®</sup> TINYOPTO\*\* TinvPower™

rinyWn. TranSiC Fault Γ 'EC RENT

UI (C Ultra FRFET UniFET\* Visuali.¹ax™ Voi agoPlus

#### DISCLAIMER

JES WITI JOINT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE FAIRCHILD SEMICONDUCTOR RESERVES TH TC KEL. RELIABILITY, FUNCTION, OR DESIGN, FAIF WILD DO NO SSUME ANY LISELY PARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHE DOES IT C. WE NY LICENS: UNIDER ITS PAIR ITS PAIR RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TO AS OF FA CHILD'S WOR'LLW DE TERMS AND CONDITIONS, PECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PROD

#### LIFE SUPPORT POLICY

TAUTI RIZED FOR USLIAS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE FAIRCHILD'S PROF ARE EXPRESS WRIT | APPROVAL LHILD SEMIC ONDUCTOR CORPORATION.

- As used he: :: 1. Life su, rt devices or stems are divices or systems which, (a) are plant into the body or (b) support or suctain ndea. r sur whose failure to perform when properly used in h instructions for use provided in the laboring, can be reaso bly expected to requir in a significant injury of the user.

- critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### JATERFEITING POLICY

Fairchild Semicor ductor Corporation's Avai-Count of enting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Sales Support.

Counter of semiconductor parts is a proving problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their narts. Cur tomers who inadvertently pur have counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed explications, and increased cost or production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the publiferation of counterfeit parts. Fairchild or from Authorized Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by a untry on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

| Definition of Terms                                                                |                   |                                                                                                                                                                                                     |  |  |

|------------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Datasheet Identification Product Status  Advance Information Formative / In Design |                   | Definition                                                                                                                                                                                          |  |  |

|                                                                                    |                   | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |  |  |

| Preliminary                                                                        | First Production  | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |  |  |

| No Identification Needed                                                           | Full Production   | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |  |  |

| Obsolete                                                                           | Not In Production | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor. The datasheet is for reference information only.                                                    |  |  |

Rev. 168

<sup>\*</sup> Trademarks of System General Corporation, used under licen. 'by Fairch.

ON Semiconductor and III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns me rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.

Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada

Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative