June 2007

# FAN5350 3MHz, 600mA Step-Down DC-DC Converter in Chip-Scale Packaging

#### **Features**

- 3MHz Fixed-Frequency Operation

- 16µA Typical Quiescent Current

- 600mA Output Current Capability

- 2.7V to 5.5V Input Voltage Range

- 1.82V Fixed Output Voltage

- Synchronous Operation

- Power-Save Mode

- Soft-Start Capability

- Input Under-Voltage Lockout (UVLO)

- Thermal Shutdown and Overload Protection

- 6-Lead 3 x 3mm MLP

- 5-Bump 1 x 1.37mm WLCSP

### **Applications**

- Cell Phones, Smart-Phones

- Pocket PCs

- WLAN DC-DC Converter Modules

- PDA, DSC, PMP, and MP3 Players

- Portable Hard Disk Drives

### Description

The FAN5350 is a step-down switching voltage regulator that delivers a fixed 1.82V from an input voltage supply of 2.7V to 5.5V. Using a proprietary architecture with synchronous rectification, the FAN5350 is capable of delivering 600mA at over 90% efficiency, while maintaining a very high efficiency of over 80% at load currents as low as 1mA. The regulator operates at a nominal fixed frequency of 3MHz at full load, which reduces the value of the external components to  $1\mu H$  for the output inductor and  $4.7\mu F$  for the output capacitor.

At moderate and light loads, pulse frequency modulation is used to operate the device in power-save mode with a typical quiescent current of 16 $\mu$ A. Even with such a low quiescent current, the part exhibits excellent transient response during large load swings. At higher loads, the system automatically switches to fixed-frequency control, operating at 3MHz. In shutdown mode, the supply current drops below 1 $\mu$ A, reducing power consumption.

The FAN5350 is available in a 6-lead Molded Leadless Package (MLP) and a 5-bump Wafer Level Chip Scale Package (WLCSP).

### **Ordering Information**

| Part Number | Pb-Free | b-Free Operating Package |                  | Packing Method               |  |

|-------------|---------|--------------------------|------------------|------------------------------|--|

| FAN5350UCX  | Yes     | -40°C to 85°C            | WLCSP-5 1x1.37mm | Tape and Reel <sup>(1)</sup> |  |

| FAN5350MPX  | Yes     | -40°C to 85°C            | MLP-6 3 x 3mm    | Tape and Reel <sup>(1)</sup> |  |

#### Note:

1. Please refer to tape and reel specifications on www.fairchildsemi.com; http://www.fairchildsemi.com/packaging.

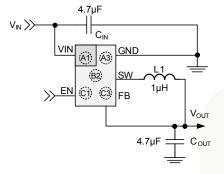

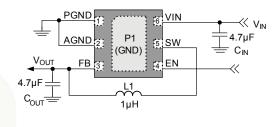

## **Typical Applications**

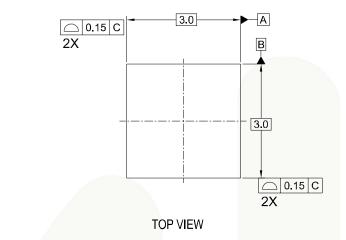

Figure 1. WLCSP (top view)

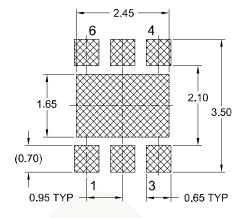

Figure 2. MLP (top view)

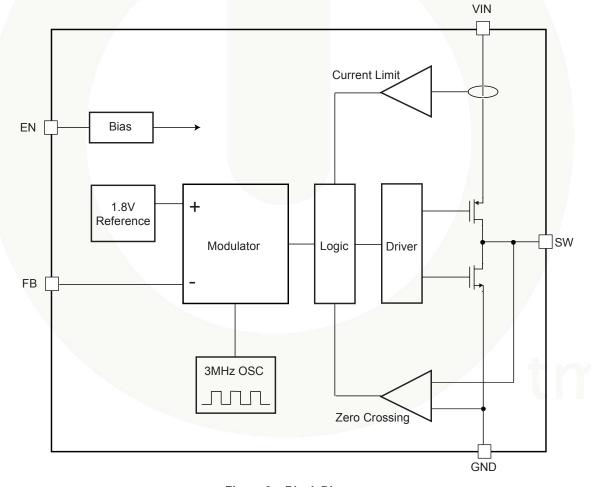

### **Block Diagram**

Figure 3. Block Diagram

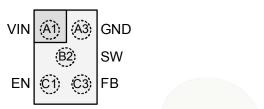

## **Pin Configurations**

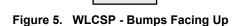

Figure 4. WLCSP - Bumps Facing Down

GND

SW

(A1) VIN

ΕN

Figure 6. 3x3mm MLP - Leads Facing Down

### **Pin Definitions**

#### **WLCSP**

| Pin# | Name     | Description                                                                                                                                  |

|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| A1   | $V_{IN}$ | Power Supply Input.                                                                                                                          |

| A3   | GND      | Ground Pin. Signal and power ground for the part.                                                                                            |

| C1   | EN       | <b>Enable Pin</b> . The device is in shutdown mode when voltage to this pin is <0.4V and enabled when >1.2V. Do not leave this pin floating. |

| C3   | FB       | Feedback Analog Input. Connect directly to the output capacitor.                                                                             |

| B2   | SW       | Switching Node. Connection to the internal PFET switch and NFET synchronous rectifier.                                                       |

#### MLP

| Pin# | Name            | Description                                                                                                                                  |  |  |  |

|------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1    | PGND            | wer Ground Pin. Power stage ground. Connect PGND and AGND together via the board bund plane.                                                 |  |  |  |

| 2    | AGND            | Analog Ground Pin. Signal ground for the part.                                                                                               |  |  |  |

| 3    | FB              | eedback Analog Input. Connect directly to the output capacitor.                                                                              |  |  |  |

| 4    | EN              | <b>Enable Pin</b> . The device is in shutdown mode when voltage to this pin is <0.4V and enabled when >1.2V. Do not leave this pin floating. |  |  |  |

| 5    | SW              | Switching Node. Connection to the internal PFET switch and NFET synchronous rectifier.                                                       |  |  |  |

| 6    | V <sub>IN</sub> | Power Supply Input.                                                                                                                          |  |  |  |

### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           | Parameter                                   | Min.                 | Max.     | Unit |    |

|------------------|---------------------------------------------|----------------------|----------|------|----|

| \/               | Input Voltage with respect to GND           |                      | -0.3     | 6.0  | V  |

| V <sub>IN</sub>  | Voltage on any other pin with respect to GI | -0.3                 | $V_{IN}$ | V    |    |

| T <sub>J</sub>   | Junction Temperature                        |                      | -40      | 150  | °C |

| T <sub>STG</sub> | Storage Temperature                         |                      | -65      | 150  | °C |

| $T_L$            | Lead Temperature (Soldering 10 Seconds)     |                      |          | 260  | °C |

| ESD              | Electrostatic Discharge Protection Level    | Human Body Model     | 4        |      | kV |

| LSD              | Liectiostatic Discharge Protection Level    | Charged Device Model | 2        |      | NV |

### **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol           | Parameter                      | Min. | Тур. | Max. | Unit |

|------------------|--------------------------------|------|------|------|------|

| V <sub>CC</sub>  | Supply Voltage Range           | 2.7  |      | 5.5  | V    |

| I <sub>OUT</sub> | Output Current                 | 0    |      | 600  | mA   |

| L                | Inductor                       | 0.7  | 1.0  | 3.0  | μH   |

| C <sub>IN</sub>  | Input Capacitor                | 3.3  | 4.7  | 12.0 | μF   |

| C <sub>OUT</sub> | Output Capacitor               | 3.3  | 4.7  | 12.0 | μF   |

| T <sub>A</sub>   | Operating Ambient Temperature  | -40  |      | +85  | °C   |

| TJ               | Operating Junction Temperature | -40  |      | +125 | °C   |

### **Thermal Properties**

| Symbol               | Parameter                                             | Min. | Тур. | Max. | Units |

|----------------------|-------------------------------------------------------|------|------|------|-------|

| $\Theta_{JA\_WLCSP}$ | Junction-to-Ambient Thermal Resistance <sup>(2)</sup> |      | 180  |      | °C/W  |

| $\Theta_{JA\_MLP}$   | Junction-to-Ambient Thermal Resistance <sup>(2)</sup> |      | 49   |      | °C/W  |

#### Note:

Junction-to-ambient thermal resistance is a function of application and board layout. This data is measured with four-layer 1s2p boards in accordance to JESD51- JEDEC standard. Special attention must be paid not to exceed junction temperature T<sub>J(max)</sub> at a given ambient temperate T<sub>A</sub>.

#### **Electrical Characteristics**

Minimum and maximum values are at  $V_{IN}$  = 2.7V to 5.5V,  $T_A$  = -40°C to +85°C,  $C_{IN}$  =  $C_{OUT}$  = 4.7 $\mu$ F, L = 1 $\mu$ H, unless otherwise noted. Typical values are at  $T_A$  = 25°C,  $V_{IN}$  =3.6V.

| Symbol             | Parameter                                         | Conditions                                  | Min.  | Тур.  | Max.  | Units |

|--------------------|---------------------------------------------------|---------------------------------------------|-------|-------|-------|-------|

| Power Su           | pplies                                            |                                             | •     |       | •     | •     |

|                    | Quiescent Current                                 | Device is not switching, EN=V <sub>IN</sub> |       | 16    |       | μA    |

| IQ                 | Quiescent Current                                 | Device is switching, EN=V <sub>IN</sub>     |       | 18    | 25    | μΑ    |

| I <sub>(SD)</sub>  | Shutdown Supply Current                           | V <sub>IN</sub> = 3.6V, EN = GND            |       | 0.05  | 1.00  | μΑ    |

| \/                 | V <sub>UVLO</sub> Under-Voltage Lockout Threshold | Rising Edge                                 | 1.8   |       | 2.1   | V     |

| <b>V</b> UVLO      |                                                   | Falling Edge                                | 1.75  |       | 1.95  | V     |

| V <sub>(ENH)</sub> | Enable HIGH-Level Input Voltage                   |                                             | 1.2   |       |       | V     |

| V <sub>(ENL)</sub> | Enable LOW-Level Input Voltage                    |                                             |       |       | 0.4   | V     |

| I <sub>(EN)</sub>  | Enable Input Leakage Current                      | EN = V <sub>IN</sub> or GND                 |       | 0.01  | 1.00  | μA    |

| Oscillator         |                                                   |                                             |       |       |       |       |

| f <sub>0SC</sub>   | Oscillator Frequency                              |                                             | 2.5   | 3.0   | 3.5   | MHz   |

| Regulatio          | n                                                 |                                             |       |       |       |       |

| V                  | Output Voltage Accuracy                           | I <sub>LOAD</sub> = 0 to 600mA              | 1.775 | 1.820 | 1.865 | V     |

| Vo                 | Output Voltage Accuracy                           | ССМ                                         | 1.784 | 1.820 | 1.856 | V     |

| t <sub>SS</sub>    | Soft-Start                                        | EN = 0 -> 1                                 |       |       | 300   | μs    |

| Output Di          | river                                             |                                             |       |       |       |       |

| _                  | PMOS On Resistance                                | $V_{IN} = V_{GS} = 3.6V$                    |       | 180   |       | mΩ    |

| $R_{DS(on)}$       | NMOS On Resistance                                | $V_{IN} = V_{GS} = 3.6V$                    |       | 170   |       | mΩ    |

| I <sub>LIM</sub>   | PMOS Peak Current Limit                           | Open-Loop <sup>(3)</sup>                    | 650   | 800   | 900   | mA    |

| T <sub>TSD</sub>   | Thermal Shutdown                                  | CCM Only                                    |       | 150   |       | °C    |

| T <sub>HYS</sub>   | Thermal Shutdown Hysteresis                       |                                             |       | 20    |       | °C    |

#### Note:

3. The Electrical Characteristics table reflects open-loop data. Refer to Operation Description and Typical Characteristic for closed-loop data.

#### **Operation Description**

The FAN5350 is a step-down switching voltage regulator that delivers a fixed 1.82V from an input voltage supply of 2.7V to 5.5V. Using a proprietary architecture with synchronous rectification, the FAN5350 is capable of delivering 600mA at over 90% efficiency, while maintaining a light load efficiency of over 80% at load currents as low as 1mA. The regulator operates at a nominal frequency of 3MHz at full load, which reduces the value of the external components to 1 $\mu$ H for the output inductor and 4.7 $\mu$ F for the output capacitor.

#### **Control Scheme**

The FAN5350 uses a proprietary non-linear, fixed-frequency PWM modulator to deliver a fast load transient response, while maintaining a constant switching frequency over a wide range of operating conditions. The regulator performance is independent of the output capacitor ESR, allowing for the use of ceramic output capacitors. Although this type of operation normally results in a switching frequency that varies with input voltage and load current, an internal frequency loop holds the switching frequency constant over a large range of input voltages and load currents.

For very light loads, the FAN5350 operates in discontinuous current (DCM) single-pulse PFM mode, which produces low output ripple compared with other PFM architectures. Transition between PWM and PFM is seamless, with a glitch of less than 14mV at  $V_{\rm OUT}$  during the transition between DCM and CCM modes.

Combined with exceptional transient response characteristics, the very low quiescent current of the controller (<16 $\mu$ A) maintains high efficiency, even at very light loads, while preserving fast transient response for applications requiring very tight output regulation.

#### **Enable and Soft Start**

Maintaining the EN pin LOW keeps the FAN5350 in non-switching mode in which all circuits are off and the part draws ~50nA of current. Increasing EN above its threshold voltage activates the part and starts the soft-start cycle. During soft start, the current limit is increased in discrete steps so that the inductor current is increased in a controlled manner. This minimizes any large surge currents on the input and prevents any overshoot of the output voltage.

#### **Under-Voltage Lockout**

When EN is high, the under-voltage lock-out keeps the part from operating until the input supply voltage rises high enough to properly operate. This ensures no misbehavior of the regulator during start-up or shutdown.

#### **Current Limiting**

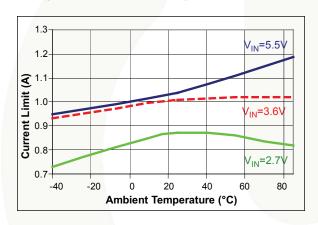

A heavy load or short circuit on the output causes the current in the inductor to increase until a maximum current threshold is reached in the high-side switch. Upon reaching this point, the high-side switch turns off, preventing high currents from causing damage.

The peak current limit shown in Figure 16,  $I_{\text{LIM}(PK)}$  is slightly higher than the open-loop tested current limit,  $I_{\text{LIM}(OL)}$ , in the Electrical Characteristics table. This is primarily due to the effect of propagation delays of the IC current limit comparator.

#### **Thermal Shutdown**

When the die temperature increases, due to a high load condition and/or a high ambient temperature, the output switching is disabled until the temperature on the die has fallen sufficiently. The junction temperature at which the thermal shutdown activates is nominally 150°C with a 20°C hysteresis.

### **Applications Information**

#### Selecting the Inductor

The output inductor must meet both the required inductance and the energy handling capability of the application.

The inductor value affects the average current limit, the PWM-to-PFM transition point, the output voltage ripple, and the efficiency.

The ripple current ( $\Delta I$ ) of the regulator is:

$$\Delta I \approx \frac{V_{OUT}}{V_{IN}} \bullet \left( \frac{V_{IN} - V_{OUT}}{L \bullet F_{SW}} \right) \label{eq:deltaI}$$

EQ. 1

The maximum average load current,  $I_{MAX(LOAD)}$  is related to the peak current limit,  $I_{LIM(PK)}$  (see figure 17) by the ripple current:

$$I_{MAX(LOAD)} = I_{LIM(PK)} - \frac{\Delta I}{2}$$

EQ. 2

The transition between PFM and PWM operation is determined by the point at which the inductor valley current crosses zero. The regulator DC current when the inductor current crosses zero, I<sub>DCM</sub>, is:

$$I_{DCM} = \frac{\Delta I}{2}$$

EQ. 3

The FAN5350 is optimized for operation with L=1 $\mu$ H, but is stable with inductances ranging from 700nH to 3.0 $\mu$ H. The inductor should be rated to maintain at least 80% of its value at I<sub>LIM(PK)</sub>.

Efficiency is affected by the inductor DCR and inductance value. Decreasing the inductor value for a given physical size typically decreases the DCR; but since  $\Delta I$  increases, the RMS current increases, as do the core and skin effect losses.

$$I_{RMS} = \sqrt{I_{OUT(DC)}^2 + \frac{\Delta I^2}{12}}$$

EQ. 4

The increased RMS current produces higher losses through the  $R_{\text{DS(ON)}}$  of the IC MOSFETs as well as the inductor ESR.

Increasing the inductor value produces lower RMS currents, but degrades transient response. For a given physical inductor size, increased inductance usually results in an inductor with lower saturation current.

Table 1 shows the effects of inductance higher or lower than the recommended  $1\mu H$  on regulator performance.

#### **Output Capacitor**

Table 2 suggests 0603 capacitors. 0805 capacitors may further improve performance in that the effective capacitance is higher and ESL is lower than 0603. This improves the transient response and output ripple.

Increasing  $C_{\text{OUT}}$  has no effect on loop stability and can therefore be increased to reduce output voltage ripple or to improve transient response. Output voltage ripple,  $\Delta V_{\text{OUT}}$ , is:

$$\Delta V_{OUT} = \Delta I \bullet \left( \frac{1}{8 \bullet C_{OUT} \bullet F_{SW}} + ESR \right)$$

EQ. 5

#### **Input Capacitor**

The  $4.7\mu F$  ceramic input capacitor should be placed as close as possible between the VIN pin and GND to minimize the parasitic inductance. If a long wire is used to bring power to the IC, additional "bulk" capacitance (electrolytic or tantalum) should be placed between  $C_{IN}$  and the power source lead to reduce ringing that can occur between the inductance of the power source leads and  $C_{IN}$ .

| Inductor Value | I <sub>MAX(LOAD)</sub> EQ. 2 | I <sub>LIM(PK)</sub> | ∆V <sub>OUT</sub> EQ. 5 | Transient Response |

|----------------|------------------------------|----------------------|-------------------------|--------------------|

| Increase       | Increase                     | Decrease             | Decrease                | Degraded           |

| Decrease       | Decrease                     | Increase             | Increase                | Improved           |

Table 1. Effects of changes in inductor value (from 1µH recommended value) on regulator performance

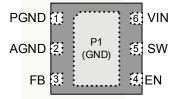

#### **PCB Layout Guidelines**

For the bill of materials of the FAN5350 evaluation board, see Table 1. There are only three external components: the inductor and the input and output capacitors. For any buck switcher IC, including the FAN5350, it is always important to place a low-ESR input capacitor very close to the IC, as shown in Figure 7. That ensures good input decoupling, which helps reduce the noise appearing at the output terminals and

ensures that the control sections of the IC do not behave erratically due to excessive noise. This reduces switching cycle jitter and ensures good overall performance. It is not considered critical to place either the inductor or the output capacitor very close to the IC. There is some flexibility in moving these two components further away from the IC.

| Description                            |                                      | Qty. | Ref.              | Vendor      | Part Number        |

|----------------------------------------|--------------------------------------|------|-------------------|-------------|--------------------|

|                                        | $1.2\mu$ H, $1.8$ A, $55$ m $\Omega$ |      |                   | TOKO        | 1117AS-1R2M        |

| Inductor                               | 1.3μH, 1.2A, 90mΩ                    | 1    | L1                | FDK         | MIPSA2520D1R0      |

|                                        | 1.5μH, 1.3A                          |      |                   | Taiyo Yuden | CBC3225T15MR       |

| Capacitor 4.7μF, ±10%, 6.3V, X5R, 0603 |                                      | 2    | $C_{IN}, C_{OUT}$ | MURATA      | GRM39 X5R 475K 6.3 |

| IC DC/DC Regulator in CSP, 5 bumps     |                                      | 1    | U1                | Fairchild   | FAN5350UCX         |

| Load Resistor (Optional)               |                                      | 1    | $R_{LOAD}$        | Any         |                    |

Table 2. FAN5350 Evaluation Board Bill of Materials (optional parts are installed by request only)

Figure 7. The FAN5350 Evaluation Board PCB (CSP)

### Feedback Loop

One key advantage of the non-linear architecture is that there is no traditional feedback loop. The loop response to changes in  $V_{\text{OUT}}$  is essentially instantaneous, which explains its extraordinary transient response. The absence of a traditional, high-gain compensated linear loop means that the FAN5350 is inherently stable over a wide range of  $L_{\text{OUT}}$  and  $C_{\text{OUT}}$ .

$L_{\text{OUT}}$  can be reduced further for a given application, provided it is confirmed that the calculated peak current for the required maximum load current is less than the minimum of the closed-loop current limit. The advantage is that this generally leads to improved transient response, since a small inductance allows for a much faster increase in current to cope with any sudden load demand.

The inductor can be increased to  $2.2\mu H$ ; but, for the same reason, the transient response gets slightly degraded. In that case, increasing the output capacitor to  $10\mu F$  helps significantly.

### **Typical Performance Characteristics**

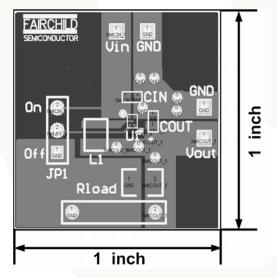

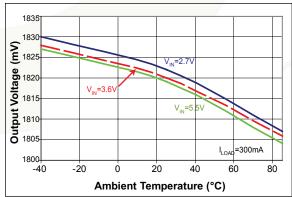

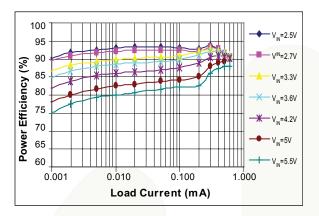

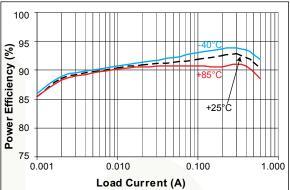

$V_{IN}$  = 3.6V,  $T_A$  = 25°C,  $V_{EN}$  =  $V_{IN}$ , according to the circuit in Figure 1 or Figure 2, unless otherwise specified.

Figure 8. Quiescent Current vs. Battery Voltage

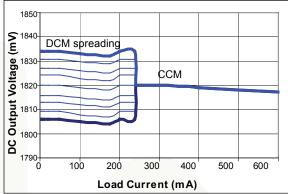

Figure 9. Load Regulation, Increasing Load

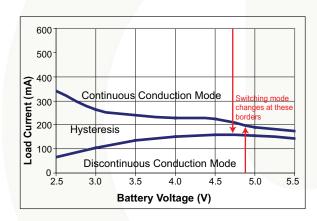

Figure 10. Switch Mode Operating Areas

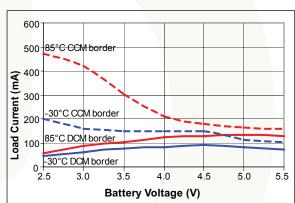

Figure 11. Switch Mode Over Temperature

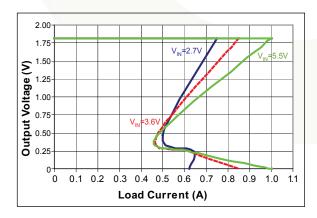

Figure 12. DC Current Voltage Output Characteristics

Figure 13. Output Voltage vs. Temperature

### Typical Performance Characteristics (Continued)

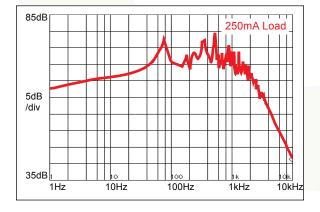

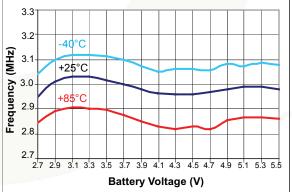

V<sub>IN</sub> = 3.6V, T<sub>A</sub> = 25°C, V<sub>EN</sub> = V<sub>IN</sub>, according to the circuit in Figure 1 or Figure 2, unless otherwise specified.

Figure 14. Power Efficiency vs. Load Current

Figure 15. Power Efficiency Over Temperature Range

Figure 16. PMOS Current Limit in Closed Loop

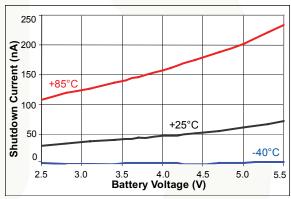

Figure 17. Shutdown Supply Current vs. Battery Voltage

Figure 18. Power Supply Rejection Ratio in CCM

Figure 19. Switching Frequency in CCM

### Typical Performance Characteristics (Continued)

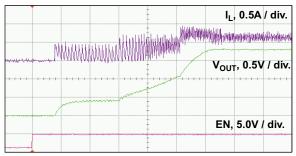

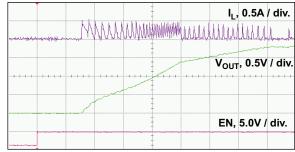

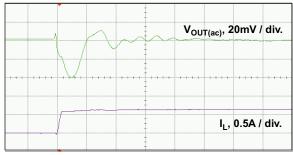

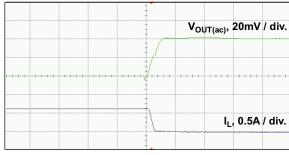

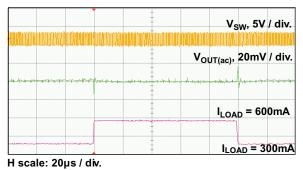

$V_{IN}$  = 3.6V,  $T_A$  = 25°C,  $V_{EN}$  =  $V_{IN}$ , according to the circuit in Figure 1 or Figure 2, unless otherwise specified.

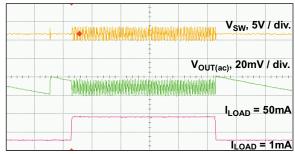

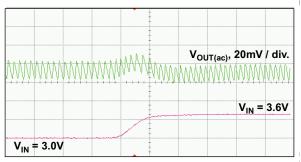

H scale: 20µs / div.

Figure 20. Start-Up, Full Load

H scale: 10µs / div.

Figure 21. Start-Up, No Load

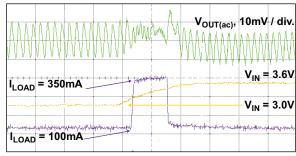

H scale: 1µs / div.

Figure 22. Fast Load Transient, No Load to Full Load

H scale: 1µs / div.

Figure 23. Fast Load Transient, Full Load to No Load

Figure 24. Fast Load Transient in CCM

H scale: 20µs / div.

Figure 25. Fast Load Transient in DCM

#### Typical Performance Characteristics (Continued)

V<sub>IN</sub> = 3.6V, T<sub>A</sub> = 25°C, V<sub>EN</sub> = V<sub>IN</sub>, according to the circuit in Figure 1 or Figure 2, unless otherwise specified.

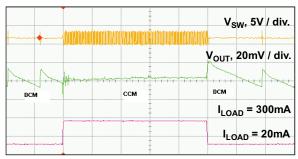

H scale: 20µs / div.

Figure 26. Fast Load Transient DCM - CCM - DCM

H scale: 2µs / div.

Figure 27. Slow Load Transient DCM - CCM - DCM

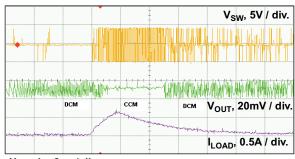

H scale: 10µs / div.

Figure 28. Line Transient, 600mV, 50mA Load

H scale: 10µs / div.

Figure 29. Line Transient, 600mV, 50mA Load

H scale: 5µs / div.

Figure 30. Combined Line (600mV) and Load (100mA to 350mA) Transient Response

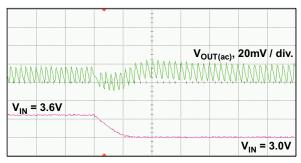

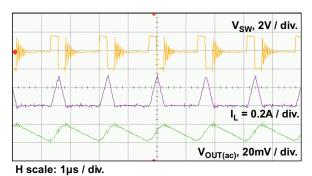

\_\_\_\_\_

Figure 31. Typical Waveforms in DCM, 50mA Load

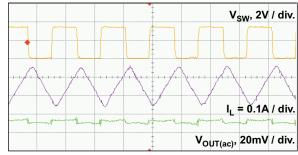

H scale: 200µs / div.

Figure 32. Typical Waveforms in CCM, 150mA Load

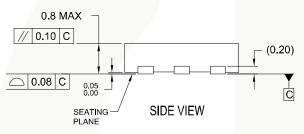

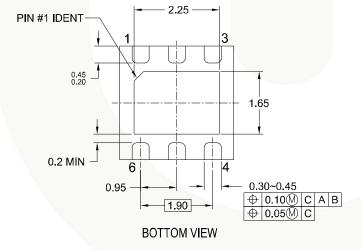

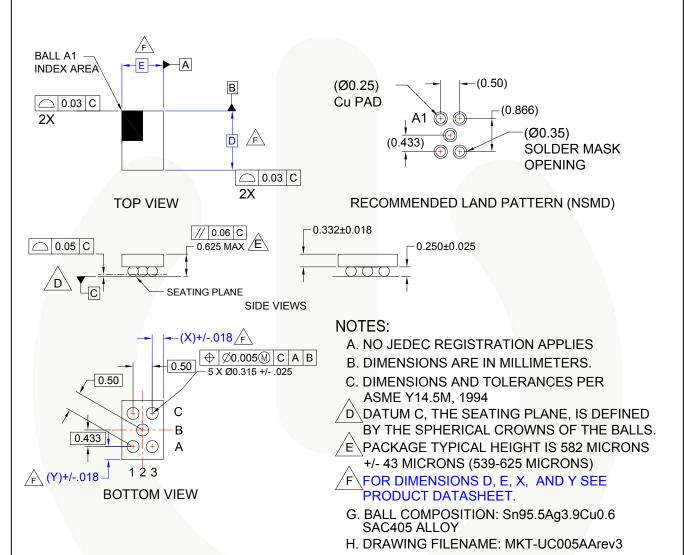

### **Physical Dimensions**

Dimensions are in millimeters unless otherwise noted.

**RECOMMENDED LAND PATTERN**

#### NOTES:

- A. CONFORMS TO JEDEC REGISTRATION MO-229, VARIATION WEEA, DATED 11/2001

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994

MLP06DrevA

Figure 33. 6-Lead Molded Leadless Package (MLP)

### Physical Dimensions (Continued)

Dimensions are in millimeters unless otherwise noted.

#### **Product Specific Dimensions**

| Product    | D               | E               | X     | Y     |

|------------|-----------------|-----------------|-------|-------|

| FAN5350UCX | 1.370 +/- 0.030 | 1.000 +/- 0.030 | 0.270 | 0.272 |

Figure 34. 5-Bump Wafer-Level Chip-Scale Package (WLCSP)

#### **TRADEMARKS**

The following are registered and unregistered trademarks and service marks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.

Green FPS™ e-Series™ POWEREDGE® SuperSOT™-8 Build it Now™ GTO™ Power-SPM™ SyncFET™ PowerTrench® The Power Franchise® CorePLUS™  $i-Lo^{TM}$ CROSSVOLT™ Programmable Active Droop™ IntelliMAX™ CTL™ QFET\* ISOPLANAR™ TinvBoost™ QS™ Current Transfer Logic™ MegaBuck™ TinvBuck™ EcoSPARK® QT Optoelectronics™ TinyLogic® MICROCOUPLER™ FACT Quiet Series™ Quiet Series™ TINYOPTO™ MicroFET™ FACT<sup>®</sup> MicroPak™ RapidConfigure™ TinyPower™ FAST<sup>®</sup> SMART START™ TinyPWM™ Motion-SPM™ FastvCore™ OPTOLOGIC® SPM® TinyWire™ FPS™ OPTOPLANAR® STEALTH™ uSerDes™ FRFET® SuperFET™ PDP-SPM™ UHC® Global Power Resources Power220® SuperSOT™3 UniFET™ Green FPS™ Power247® SuperSOT™-6  $VCX^{TM}$

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

- 1. Life support devices or systems are devices or systems 2. A critical component in any component of a life support, which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### PRODUCT STATUS DEFINITIONS

#### **Definition of Terms**

| Datasheet Identification Product Status |                        | Definition                                                                                                                                                                                               |

|-----------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information                     | Formative or In Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |

| Preliminary                             | First Production       | This datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed                | Full Production        | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design.                                                   |

| Obsolete                                | Not In Production      | This datasheet contains specifications on a product that has been discontinued by Fairchild Semiconductor. The datasheet is printed for reference information only.                                      |

Rev. 129