May, 2024

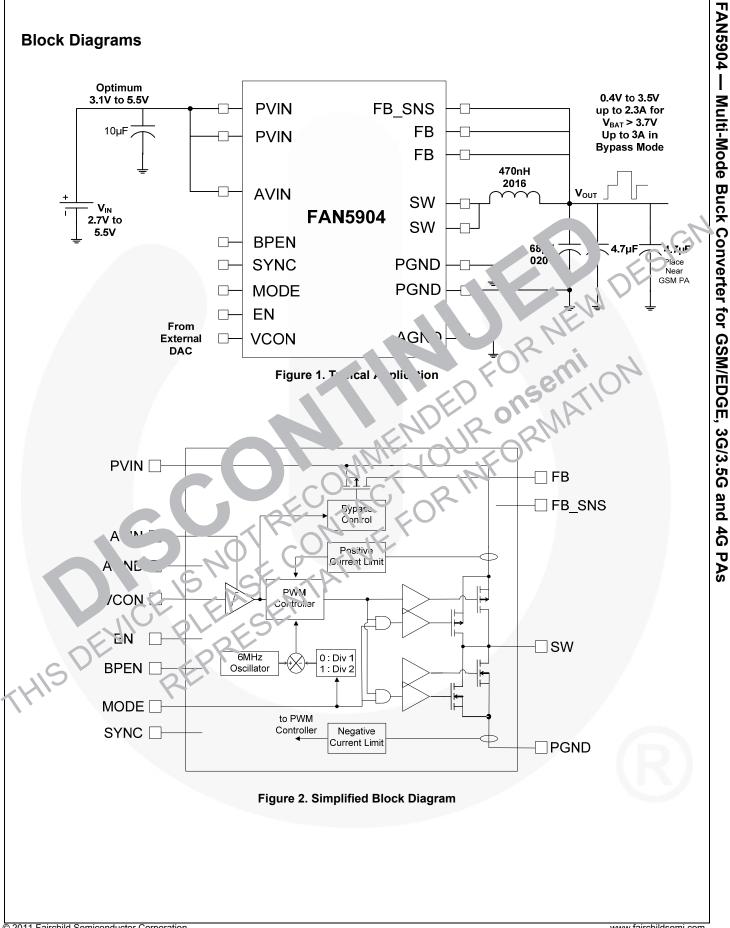

# FAN5904 Multi-Mode Buck Converter for GSM/EDGE, 3G/3.5G and 4G PAs

## Features

- 2.7 V to 5.5 V Input Voltage Range

- V<sub>OUT</sub> Range from 0.40 V to 3.50 V (or V<sub>IN</sub>)

- Single 470 nH Small Form Factor Inductor

- 35 mΩ Integrated Bypass FET

- 100% Duty Cycle for Low Dropout Operation

- Input Under-Voltage Lockout / Thermal Shutdown

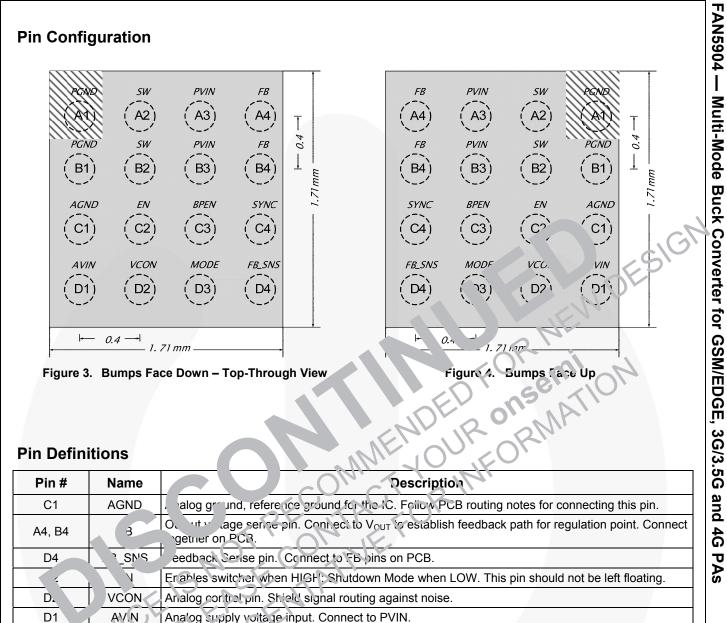

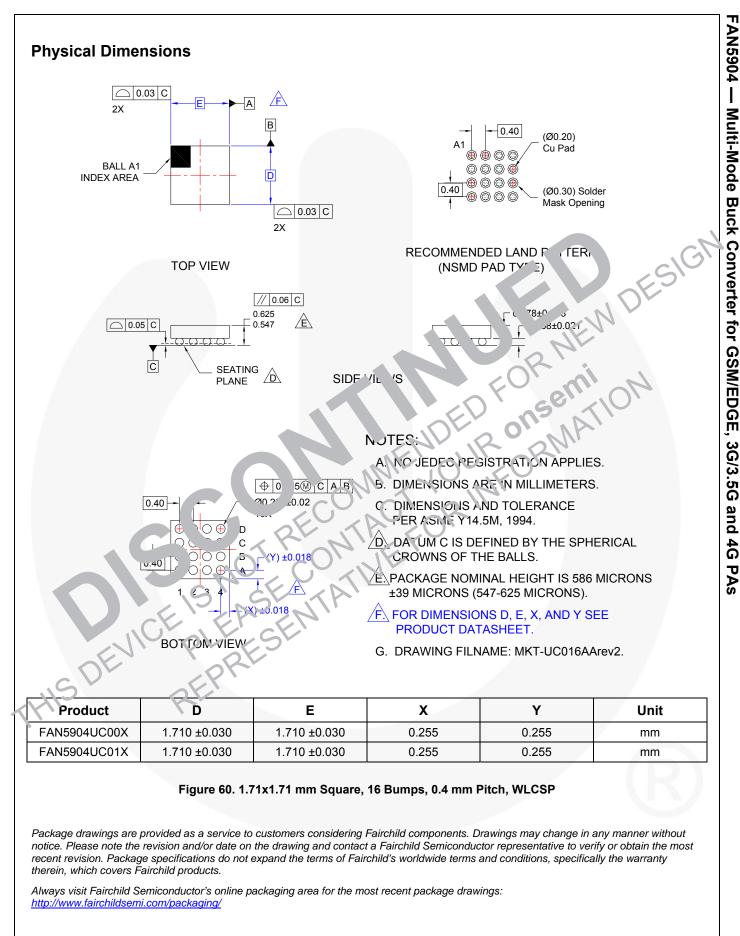

- 1.71 mm x 1.71 mm, 16-Bump, 0.4 mm Pitch WLCSP

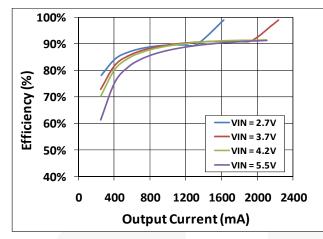

### High Power PWM Mode

- $\circ$  Up to 95% Efficient Synchronous Operation in High  $P_{\text{OUT}}$  Conditions

- Output current up to 2.3 A

- 10 µs Output Voltage Step Response for Early GSM Tx Power-Loop Settling

- 3MHz PWM Mode

### Low Power Auto Mode

- Up to 95% Efficient Svr no. Opera on at Higher Pout Conditio

- o Output Current up to 2 A

- 6 MHz F 'M Onere' in at High Power and PFwi pe. ion Lo... ower

- ь ass N de

- o L th A Loga Current

## Applications

Dynamic Supply Bias for Polar or Linear GSM/EDGE PAs and 3G/3.5G and 4G PAs

Dynamic Supply Bias in GSM/EDGE Quad Band Amplifiers for Mobile Handsets and Data Cards

## Description

The FAN5904 is a high-efficiency, low-noise, synchronous, step-down, DC-DC converter optimized for powering Radio Frequency (RF) Power Amplifier As) in handsets and other mobile applications. In gh-Pc ar Mode, GSM Trapower is enabled. In Lapha Pc ar Mode, up to 3.0 V is supported, enabling in the 29 dBr. uter power for 3C/3.5G and 4G platforms

The output voltas much aynamically adjusted from 0.40 V to 5 0 V, phone rial to an analog input voltage VCON logit from 0.16 V to 1.40 V, optimizing poweralleft, and, so transition times of less than 10  $\mu$ s are ac. We wing excellent inter-slot cettling.

h in mated bypass FET is submatically shabled when the battery voltage and voltage drop across the DC-DC PMOS dovice are within a set voltage range of the desired output voltage ( $V_{OUT} = V_{BAT} - V_{PACS} - V_{BP_TH}$ ). This dynamic hypass feature shables the FAI 15904 to support heavy load currents rander the most stringent VSWR conditions while maintaining high chiclency and superior spectral performance. The hypass FET may also be enabled by providing a VCON voltage nominally greater than or equal to 1.5 V or by driving BPEN high.

The FAN5904 operates in PWM Mode with a 6 MHz switching frequency in Low-Power Mode and at 3 MHz in High-Power Mode, which limits high-frequency spur levels. It uses a single, small form factor inductor of 470 nH. In addition, PFM operation is allowed in Low-Power Mode to improve efficiency at low load currents.

The FAN5904UC00X option allows PFM Mode only when  $V_{OUT}$  is less than 1 V, while the FAN5904UC01X permits PFM Mode at higher voltages for applications that can tolerate larger output ripple and that demand optimal low-to-moderate load current efficiency.

## **Ordering Information**

| Part Number  | LPM Mode PFM           | Output Voltage  | Temperature<br>Range | Package                                                 | Packing       |

|--------------|------------------------|-----------------|----------------------|---------------------------------------------------------|---------------|

| FAN5904UC00X | V <sub>OUT</sub> < 1 V | 0.4 V to PVIN   |                      | 1.71 mm x 1.71 mm, 16-Bump<br>0.4 mm Pitch, Wafer-Level | Tape and Reel |

| FAN5904UC01X | All V <sub>OUT</sub>   | 0.4 V 10 1 VIIV |                      | Chip-Scale Package (WLCSP)                              |               |

FAN5904

Force bypess when HIGH; Auto bypass when LOW. This pin should not be left floating.

Tis SYNC to AGND if not used or in Auto-PFM Mode. This pin should not be left floating. Low-Power Auto Mode / High-Power PWM Mode select. When MODE = 1, the DC-DC is

Supply voltage input to the internal MOSFET switches. Connect to input power source.

Switching node of the internal MOSFET switches. Connect to output inductor.

Exter a clock synchronization input. When SYNC is HIGH, the DC-DC does not allow PFM Mode.

configured for 6MHz Low-Power Auto Mode. When MODE = 0, the DC-DC is configured for 3MHz

Power ground of the internal MOSFET switches. Follow routing notes for connections between

**BPEN**

SYNC

MODE

**PVIN**

SW

PGND

PGND and AGND.

C3

C4

D3

A3, B3

A2. B2

A1, B1

3

High-Power PWM Mode. This pin should not be left floating.

## Absolute Maximum Ratings

Stresses exceeding the Absolute Maximum Ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           | Parameter                                |                                  | Min. | Max.                   | Unit      |

|------------------|------------------------------------------|----------------------------------|------|------------------------|-----------|

| N/               | Voltage on AVIN, PVIN                    | Voltage on AVIN, PVIN            |      | 6.0                    | V         |

| V <sub>IN</sub>  | Voltage on Any Other Pin                 |                                  | -0.3 | AV <sub>IN</sub> + 0.3 | V         |

| TJ               | Junction Temperature                     |                                  | -40  | +125                   | °C        |

| T <sub>STG</sub> | Storage Temperature                      |                                  | -65  | +150                   | °C        |

| TL               | Lead Soldering Temperature (10 Second    | s)                               |      | +260                   | <b>2°</b> |

| ESD              | Electrostatic Discharge Dratection Level | Human Body Model, JESD22-A114    | ?.0  |                        |           |

| ESD              | Electrostatic Discharge Protection Level | Charged Device Model, JESD2? 101 |      |                        |           |

## **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditio. Tak al dense operation. Recommended operating conditions are specified to ensure optimal performance to the dat, here recifications. Fairchild ones not recommend exceeding them or designing to Absolute Maximum Ratings

| Symbol               | Paramet                                | Min.        | Гур     | Max.              | Unit |

|----------------------|----------------------------------------|-------------|---------|-------------------|------|

| V <sub>IN</sub>      | Supply Voltage Range                   | 2.1         |         | 5.5               | V    |

| Vout                 | Output Voltage Range                   | 0.35        |         | <v<sub>IN</v<sub> | V    |

| I <sub>OUT_BYP</sub> | Output Current (Bypass lode)           | JEO         |         | 3.0               | А    |

| IOUT_LP_MODE         | Output Current J. Pov Mod              | <u>[7</u> . |         | 1.2               | А    |

| IOUT_HP_MODE         | Output Currer High-Priver worde)       |             |         | 2.3               | А    |

|                      | Indur a for Sm. St F B Footprint       |             | 470     |                   | nH   |

| L                    | 1uc. Jr o imum Efficiency Performar ce |             | 1.0     |                   | μH   |

| Circ                 | Inp. Cc                                |             | 10      |                   | μF   |

| Ć T                  |                                        |             | 2 x 4.7 |                   | μF   |

| TA                   | perating Ambient Temperature Range     | -40         |         | +85               | °C   |

| TJ                   | Operating Junction Temperature Range   | -40         |         | +125              | °C   |

Note:

1.

A large enough input capacitor value is required for limiting the input voltage drop during GSM bursts, bypass transitions, or during large output voltage transitions.

## **Dissipation Ratings**

| Symbol          | Parameter                                             | Min. | Тур. | Max. | Unit |

|-----------------|-------------------------------------------------------|------|------|------|------|

| Θ <sub>JA</sub> | Junction-to-Ambient Thermal Resistance <sup>(2)</sup> |      | 80   |      | °C/W |

Note:

Junction-to-ambient thermal resistance is a function of application and board layout. This data is measured with four-layer 2s2p boards in accordance to JESD51- JEDEC standard. Special attention must be paid not to exceed junction temperature T<sub>J(MAX)</sub> at a given ambient temperate T<sub>A</sub>.

## **Electrical Characteristics, All Power Modes**

$V_{IN} = V_{OUT} + 0.6 \text{ V}$ ,  $I_{OUT} = 200 \text{ mA}$ , EN =  $V_{IN}$ ,  $T_A = -40^{\circ}\text{C}$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$  and  $V_{IN} = 3.7 \text{ V}$ .

| Symbol                 | Parameter                                                | Condition                                                             | Min. | Тур. | Max.                                         | Unit |

|------------------------|----------------------------------------------------------|-----------------------------------------------------------------------|------|------|----------------------------------------------|------|

| Power Sup              | plies                                                    |                                                                       |      |      | ·                                            |      |

| V <sub>IN</sub>        | Input Voltage range                                      | I <sub>OUT</sub> ≤ 2.3 A                                              | 3.0  |      | 5.5                                          | V    |

| I <sub>SD</sub>        | Shutdown Supply Current                                  | EN = 0 V                                                              |      | 1.0  | 3.0                                          | μA   |

| M                      | Under Voltage Lockout Threshold                          | V <sub>IN</sub> Rising                                                | 2.30 | 2.45 | 2.60                                         | V    |

| $V_{UVLO}$             | Onder Voltage Lockout Threshold                          | Hysteresis                                                            |      | 175  |                                              | mV   |

| Logic Cont             | rol                                                      |                                                                       |      |      | <u>.                                    </u> |      |

| V <sub>IH</sub>        | Logic Threshold Voltage                                  | Input HIGH Threshold                                                  | 1.2  |      |                                              |      |

| VIL                    | EN, BPEN, SYNC, MÕDE                                     | Input LOW Threshold                                                   |      |      | 0.4                                          | S    |

| I <sub>CTRL</sub>      | Logic Control Input Bias Current<br>EN, BPEN, SYNC, MODE | V <sub>IN</sub> or GND                                                |      | 0.61 | 1.00                                         | μA   |

| Analog Cor             | ntrol                                                    |                                                                       | Ţ    |      |                                              |      |

| V <sub>CON_BP_EN</sub> | V <sub>CON</sub> Forced Bypass Enter                     | $V_{CON}$ Voltage that Forc. By, s:<br>$V_{IN} = 2.70 V - 4.$         | 1.6  | Hr.  |                                              | V    |

| V <sub>CON_BP_EX</sub> | V <sub>CON</sub> Forced Bypass Exit                      | $V_{CON}$ V uge at L is Forced;<br>Byr V <sub>IN</sub> = 2 0 V 4.75 V |      | en   |                                              | V    |

| Gain                   | Gain in Control Range: 0.16 V to<br>1.40 V               | IDE                                                                   | 01   | 2.5  |                                              |      |

| V <sub>OUT_ACC</sub>   | V <sub>OUT</sub> Accuracy                                | 2.5 x Von                                                             | -50  |      | +50                                          | mV   |

| Bypass                 |                                                          |                                                                       | 20.  |      |                                              |      |

| R <sub>FET</sub>       | Bypass FET Resir pe                                      | Ob. Z IP                                                              |      | 35   |                                              | mΩ   |

| $\Delta V_{OUT\_BP}$   | Bypass Mode ( tput Voltagep                              | OUT = 2 A                                                             |      | 70   |                                              | mV   |

| Over Temp              | eraturectic                                              | C THEO                                                                |      |      |                                              |      |

| т                      |                                                          | Rising Temperature                                                    |      | +150 |                                              | °C   |

| TOTP                   | C r-1empera re Protection                                | Hysteresis                                                            |      | +20  |                                              | °C   |

3. B, ass Ft resistance does not include PFET RDSON and inductor DCR in parallel with the bypass FET in Bypass Mode. FLERE

HISDEVICE

## Electrical Characteristics, Low-Power Auto Mode (MODE = 1)

$V_{IN} = V_{OUT} + 0.6 \text{ V}$ ,  $I_{OUT} = 200 \text{ mA}$ , EN =  $V_{IN}$ ,  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$  and  $V_{IN} = 3.7 \text{ V}$ .

| Symbol                 | Parameter                                                            | Condition                                                                                                        | Min.             | Тур.               | Max.      | Unit      |

|------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------|--------------------|-----------|-----------|

| Oscillator             | / Synchronization                                                    |                                                                                                                  |                  | •                  | · · · · · |           |

| f <sub>SW</sub>        | Average Oscillator Frequency                                         |                                                                                                                  | 5.4              | 6.0                | 6.6       | MHz       |

| f <sub>SYNC</sub>      | Synchronization Frequency Range <sup>(4)</sup>                       |                                                                                                                  | 4.8              | 6.0                | 7.2       | MHz       |

| DC-DC                  |                                                                      |                                                                                                                  |                  |                    |           |           |

| D                      | PMOS On Resistance                                                   | $V_{IN} = V_{GS} = 3.7 V$                                                                                        |                  | 210                |           | mΩ        |

| R <sub>DSON</sub>      | NMOS On Resistance                                                   | $V_{IN} = V_{GS} = 3.7 V$                                                                                        |                  | · <sup>-</sup> - 5 |           | mΩ        |

| I <sub>LIMp</sub>      | P-Channel Current Limit                                              |                                                                                                                  | 1.35             | 1.6                | 1.95      | A         |

| I <sub>LIMn</sub>      | N-Channel Current Limit                                              |                                                                                                                  | .00              | 1.30               | 1.70      | <b>SA</b> |

| V <sub>OUT_MIN</sub>   | Minimum Output Voltage                                               | V <sub>CON</sub> = 0.16 V                                                                                        | 0                | .+0                | 0.45      | V         |

|                        | Maximum Output Voltage                                               | V <sub>CON</sub> = 1.40 V                                                                                        | 15               | 3.50               | 3.55      | V         |

| DC-DC Effi             | iciency                                                              |                                                                                                                  |                  | IE V               |           |           |

|                        |                                                                      | V <sub>OUT</sub> = 3.1 V, I <sub>L</sub> = 25 mA                                                                 |                  | 95                 |           |           |

| $\eta_{Power}$         | Power Efficiency,                                                    | V <sub>OUT</sub> = 1.9 V OAL 22                                                                                  |                  | 91                 | -         | %         |

|                        | Low-Power Auto Mode, $V_{IN}$ = 3.7 V                                | $V_{01}$ 5 $V_{1}$ $p = 7 mA$                                                                                    |                  | 65                 | 77        |           |

| Output Re              | gulation                                                             |                                                                                                                  |                  |                    |           |           |

| V <sub>OUT_RLine</sub> | V <sub>OUT</sub> Line Regulation                                     | $\boxed{3. \leq V_{\rm IN} \leq 7}$                                                                              | 0,               | +5                 |           | mV        |

| _                      | V <sub>OUT</sub> Load Regulation                                     | 12 ≤ I <sub>OUT</sub> ≤ 800 mA                                                                                   |                  | +25                |           | mV        |

| _                      | V <sub>OUT</sub> Slew Rate                                           | Puring Bypess Enabling                                                                                           | <u>50,      </u> | 0.25               |           | V/µs      |

| $V_{BP\_ThH}$          | Voltage Threshold .tei vpass                                         | VIN - VPMOS - VOLT                                                                                               | 140              | 190                | 240       | mV        |

| V <sub>BP ThL</sub>    | Voltage Threshc to Exit Bypace                                       | VIN - VOUT                                                                                                       | 340              | 400                | 440       | mV        |

| _                      |                                                                      | PFM Mode, VIN = 3.8 V,                                                                                           |                  | 11                 |           | mV        |

|                        |                                                                      | PWM Mode. VIN = 3.8 V                                                                                            |                  | 4                  |           |           |

| Timir                  | C C C C                                                              |                                                                                                                  |                  |                    |           |           |

| tss                    | S' .tup Time                                                         | V <sub>IN</sub> = 3.7 V, V <sub>OUT</sub> from 0 V to<br>5.1 V, C <sub>OUT</sub> = 2 x 4.7 µF, 10 V,<br>X5R      |                  | 50                 | 60        | μs        |

| t <sub>DC-DC_TR</sub>  | V <sub>ເປT</sub> Step Response Risຈິ∑in.e <sup>(5)</sup>             | $V_{OUT}$ from 5% to 95%, $\Delta V_{OUT}$ < 2 V (1.4 V – 3.4 V), $R_{LOAD}$ ≤ 7 $\Omega$                        |                  |                    | 10        | μs        |

| t⊔c.nc_7F              | V <sub>OUT</sub> Step Responsจ Fall Time <sup>(5)</sup>              | V <sub>OUT</sub> from 95% to 5%, $\Delta$ V <sub>OUT</sub> < 2 V (3.4 V – 1.4 V), R <sub>LOAD</sub> ≤ 7 $\Omega$ |                  |                    | 10        | μs        |

| t <sub>DC-DC_CL</sub>  | Maximum Allowed Time for<br>Consecutive Current Limit <sup>(6)</sup> |                                                                                                                  |                  | 40                 |           | μs        |

| t <sub>DCDC_CLR</sub>  | Consecutive Current Limit Recovery Time <sup>(4)</sup>               |                                                                                                                  |                  | 180                |           | μs        |

Notes:

4. Guaranteed by design; not tested in production.

5. Guaranteed by design; not tested in production. Voltage transient only. Maximum specified  $V_{OUT}$  transition step is 3.1 V. Assumes  $C_{OUT} = 2 \times 4.7 \mu F$ .

Protects part under short-circuit conditions. After 40 μs nominally, operation halts and restarts after 180 μs nominally. Under heavy capacitive loads, V<sub>CON</sub> slew rate should be reduced to avoid consecutive current limits. Under typical conditions for a 3 V change at the output, a capacitive only load of up to 40 μF is supported (assuming a step at the V<sub>CON</sub> input).

## Electrical Characteristics, High-Power PWM Mode (MODE = 0)

$V_{IN} = V_{OUT} + 0.6 \text{ V}$ ,  $I_{OUT} = 200 \text{ mA}$ ,  $EN = V_{IN}$ ,  $T_A = -40^{\circ}\text{C}$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$  and  $V_{IN} = 3.7 \text{ V}$ .

| Symbol                       | Parameter                                                             | Condition                                                                                                        | Min.  | Тур.           | Max. | Unit |

|------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------|----------------|------|------|

| Oscillator                   | / Synchronization                                                     |                                                                                                                  |       |                |      |      |

| <b>f</b> <sub>SW</sub>       | Average Oscillator Frequency                                          |                                                                                                                  | 2.7   | 3.0            | 3.3  | MHz  |

| f <sub>SYNC</sub>            | Synchronization Frequency Range <sup>(7)</sup>                        |                                                                                                                  | 2.4   | 3.0            | 3.6  | MHz  |

| DC-DC                        |                                                                       |                                                                                                                  |       |                |      |      |

| Р                            | PMOS On Resistance                                                    | $V_{IN} = V_{GS} = 3.7 V$                                                                                        |       | 105            |      | mΩ   |

| R <sub>DSON</sub>            | NMOS On Resistance                                                    | $V_{IN} = V_{GS} = 3.7 V$                                                                                        |       |                |      | mΩ   |

| I <sub>LIMp</sub>            | P-Channel Current Limit                                               |                                                                                                                  | 2.7   | 3. <b>ર</b> ્ડ | 3.9  | A    |

| I <sub>LIMn</sub>            | N-Channel Current Limit                                               |                                                                                                                  | 0     | 1.3            | 1.7  | A    |

| V <sub>OUT_MIN</sub>         | Minimum Output Voltage                                                | V <sub>CON</sub> = 0.16 V                                                                                        | 0     | .+0            | 0.45 | V    |

| $V_{\text{OUT}\_\text{MAX}}$ | Maximum Output Voltage                                                | V <sub>CON</sub> = 1.40 V                                                                                        | 15    | 3.50           | 3.55 | V    |

| DC-DC Eff                    | iciency                                                               |                                                                                                                  |       | IE .           |      |      |

|                              | Power Efficiency,                                                     | $V_{OUT} = 3.3 \text{ V}, I_L = 1.c$                                                                             | 2     | 92             |      | 0/   |

| $\eta_{Power}$               | High-Power Auto Mode, $V_{IN}$ = 3.7 V                                | V <sub>OUT</sub> = 2.0 V OAL 0                                                                                   |       | ٩ر             | 1    | %    |

| Output Re                    | gulation                                                              |                                                                                                                  | ~ ~ @ |                | 0/   |      |

| $V_{OUT\_RLine}$             | Vout Line Regulation                                                  | $1 \leq V_{IN}$ 3.7                                                                                              | 13    | +5             |      | mV   |

| $V_{OUT\_RLoad}$             | V <sub>OUT</sub> Load Regulation                                      | 2L 1A ≤ IOL ≤ 2000 T.A                                                                                           | 0.    | +25            |      | mV   |

| VBYPSLEW                     | V <sub>OUT</sub> Slew Rate                                            | Bypass Frabling                                                                                                  |       | 0.25           |      | V/µs |

| $V_{BP\_ThH}$                | Voltage Threshold to Ente 3ypass                                      | VIN - VPMUS - VOUT                                                                                               | 295   | 340            | 385  | mV   |

| $V_{BP\_ThL}$                | Voltage Threshold it L hass                                           | VIN - VOUT                                                                                                       | 550   | 650            | 750  | mV   |

| $V_{OUT_Ripple}$             | V <sub>OUT</sub> Ripple <sup>(7)</sup>                                | .7WM Mode, VIN = 3.8 V                                                                                           |       | 4              |      | mV   |

| Timing                       | 2                                                                     | THEO.                                                                                                            |       |                |      |      |

| t <sub>ss</sub>              | Sta. o Time                                                           | V <sub>IN</sub> = 3.7 V, V <sub>≏UT</sub> from 0 V to<br>3.1 V, C <sub>CUT</sub> = 2 x 4.7 µF, 10 V,<br>X5R      |       | 50             | 60   | μs   |

| t <sub>DC-DC_</sub>          | Vo Step Response Rise Time <sup>(8</sup>                              | $v_{OU}$ from 5% to 95%, ΔV <sub>OUT</sub> < 1.5 V (0.5 V − 2.0 V), R <sub>LOAD</sub> ≤ 7 Ω                      |       |                | 10   | μs   |

| t <sub>DC-DC_TF</sub>        | Vour Step Response Fall Time                                          | $V_{OUT}$ from 95% to 5%, Δ $V_{OUT}$ < 1.5 V (2.0 V – 0.5 V), $R_{LOAD} \le 7 \Omega$                           |       |                | 10   | μs   |

| t <sub>DC-DC_TR</sub>        | Vour Step Response Rise Time <sup>(8)</sup>                           | $V_{OUT}$ from 5% to 95%, $\Delta V_{OUT}$ < 3.0 V (0.4 V – 3.4 V), $R_{LOAD}$ ≤ 7 $\Omega$                      |       |                | 10   | μs   |

| UC-DC_TF                     | V <sub>OUT</sub> Step Response Fall Time <sup>(8)</sup>               | $V_{\text{OUT}}$ from 95% to 5%, $\Delta V_{\text{OUT}}$ < 3.0 V (3.4 V – 0.4 V), $R_{\text{LOAD}}$ ≤ 7 $\Omega$ |       |                | 12   | μs   |

| t <sub>DC-DC_CL</sub>        | Maximum Allowed Time for<br>Consecutive Current Limits <sup>(9)</sup> |                                                                                                                  |       | 40             |      | μs   |

| t <sub>DCDC_CLR</sub>        | Consecutive Current Limit Recovery Time <sup>(4)</sup>                |                                                                                                                  |       | 180            |      | μs   |

#### Notes:

7. Guaranteed by design; not tested in production.

8. Guaranteed by design; not tested in production. Voltage transient only. Maximum specified V<sub>OUT</sub> transition step is 3.1 V. Assumes  $C_{OUT} = 2 \times 4.7 \mu F$ .

Protects part under short-circuit conditions. Under heavy capacitive loads, V<sub>CON</sub> slew rate may be adjusted to avoid consecutive current limits. Under typical conditions for a 3 V change at the output, a capacitive only load of up to 40 μF is supported (assuming a step at the V<sub>CON</sub> input).

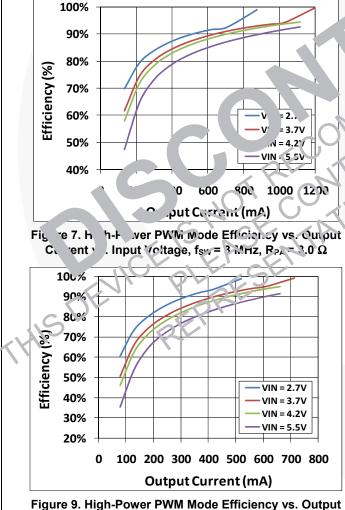

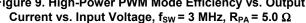

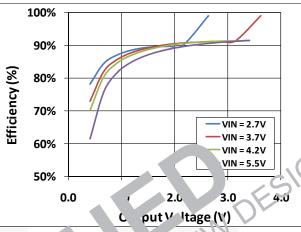

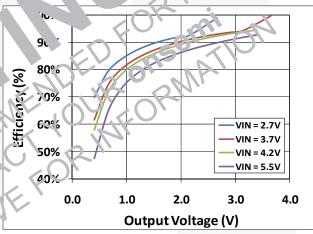

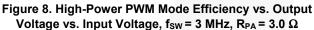

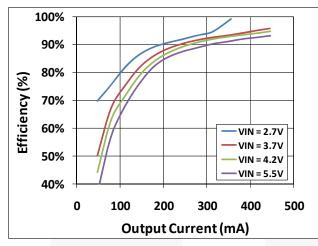

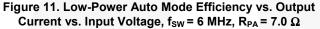

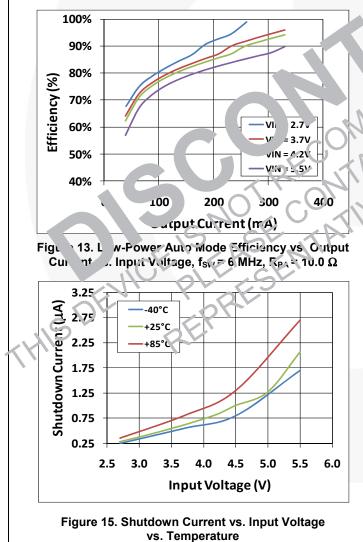

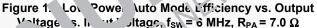

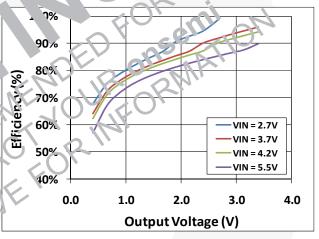

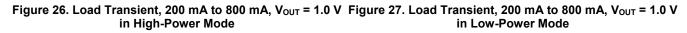

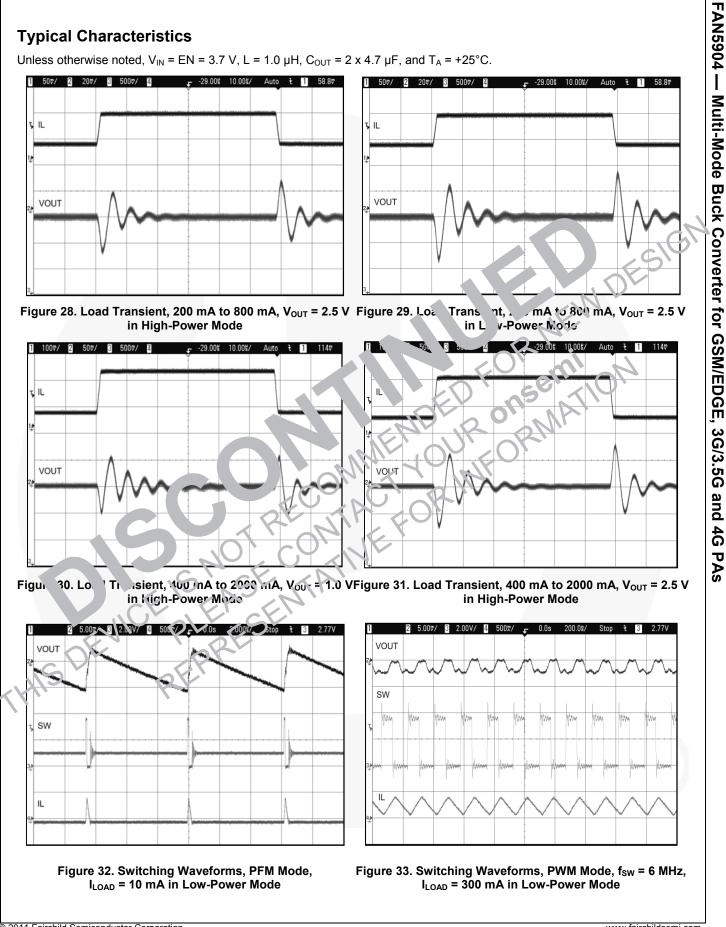

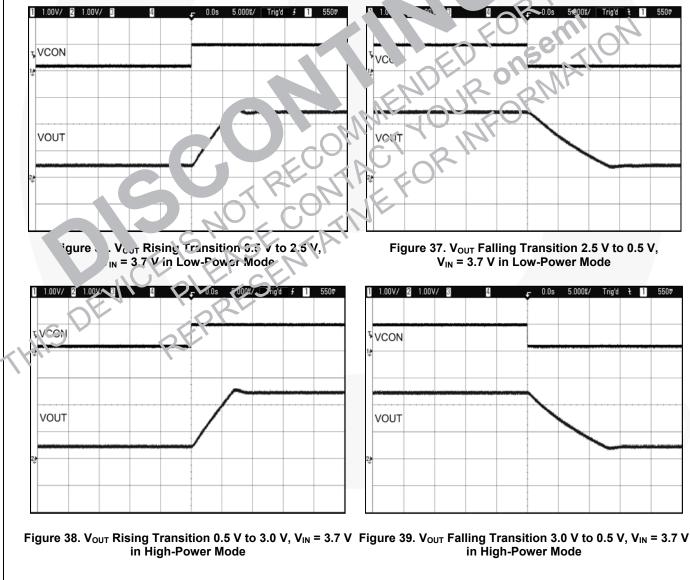

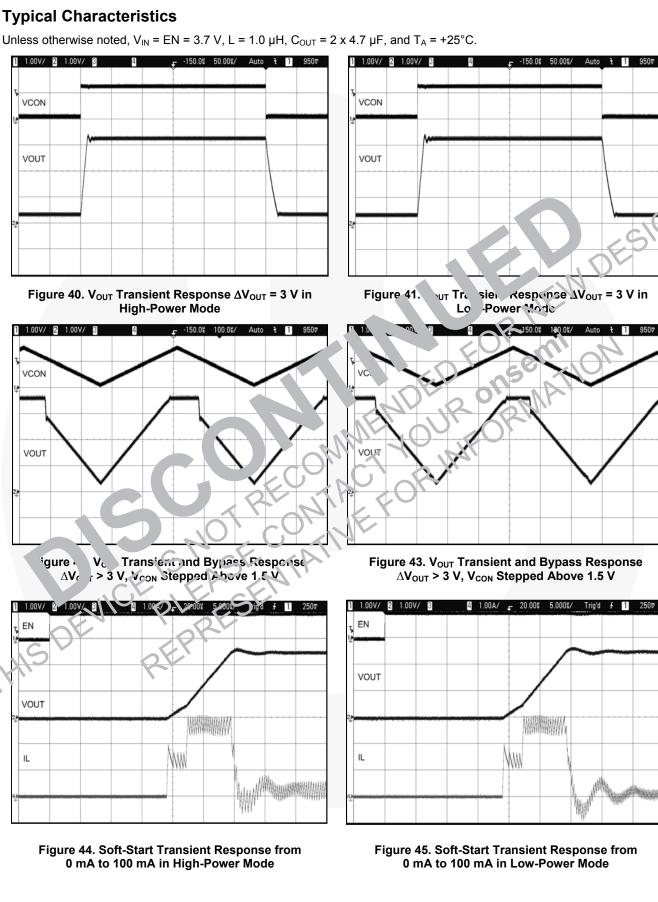

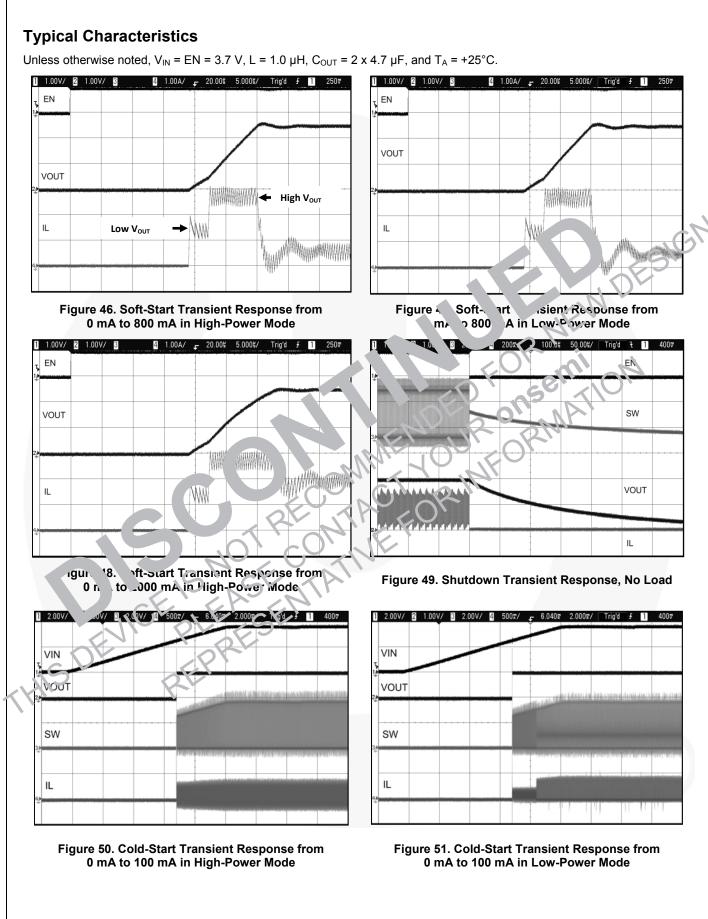

Unless otherwise noted,  $V_{IN}$  = EN = 3.7 V, L = 1.0  $\mu$ H,  $C_{OUT}$  = 2 x 4.7  $\mu$ F, and  $T_A$  = +25°C.

Unless otherwise noted,  $V_{IN}$  = EN = 3.7 V, L = 1.0  $\mu$ H,  $C_{OUT}$  = 2 x 4.7  $\mu$ F, and  $T_A$  = +25°C.

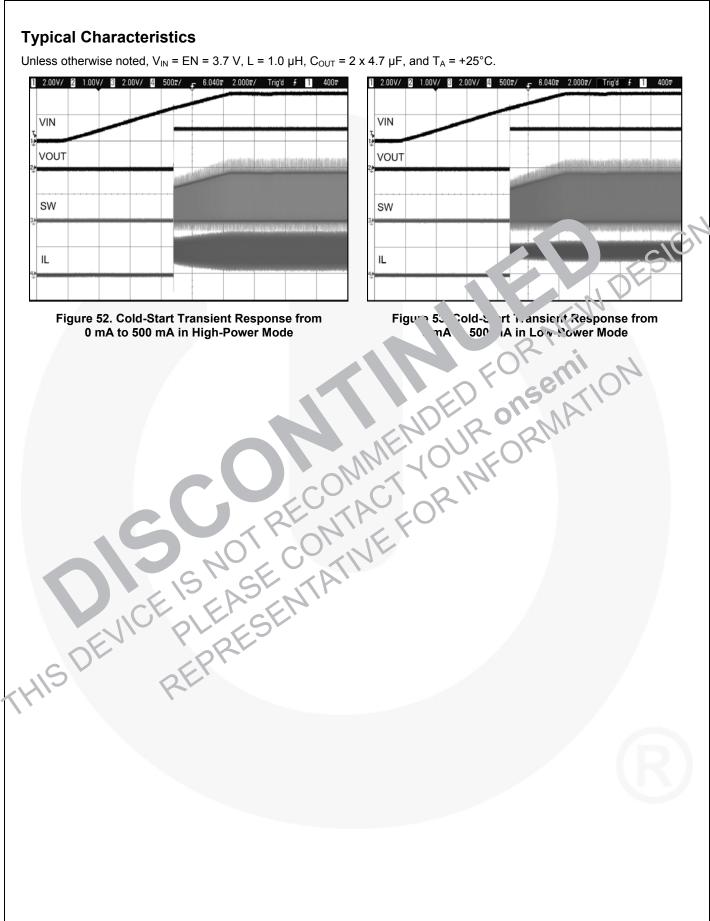

Unless otherwise noted,  $V_{IN}$  = EN = 3.7 V, L = 1.0  $\mu$ H,  $C_{OUT}$  = 2 x 4.7  $\mu$ F, and  $T_A$  = +25°C.

(VIN = 3.7 V)

r 300 m.V. 500 mV, and 2 V ΔV<sub>OUT</sub>

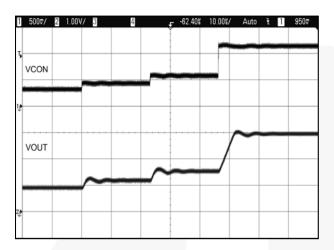

Figure 16. Rise Times for 300 mV, 500 mV, and 2 V  $\Delta V_{OUT}$  Figure 17. `ise `mes (V\_{IN} = 3.7 V)

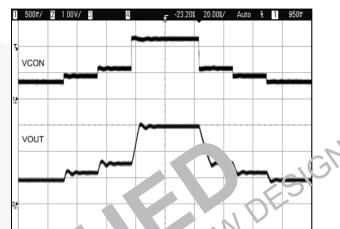

Figure 20. Line Transient V<sub>IN</sub> = 3.7 V to 4.2 V, V<sub>OUT</sub> = 1.0 V, Figure 21. Line Transient V<sub>IN</sub> = 3.7 V to 4.2 V, V<sub>OUT</sub> = 2.5 V, 5  $\Omega$  Load, 50 µs/div. 5  $\Omega$  Load, 50 µs/div.

Unless otherwise noted,  $V_{IN}$  = EN = 3.7 V, L = 1.0  $\mu$ H,  $C_{OUT}$  = 2 x 4.7  $\mu$ F, and  $T_A$  = +25°C.

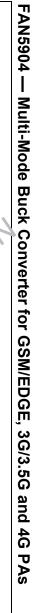

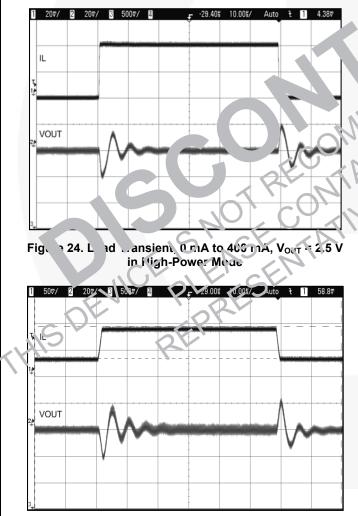

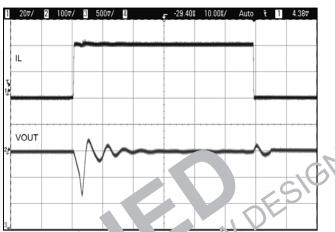

Figure 22. Load Transient, 0 mA to 400 mA, V<sub>OUT</sub> = 1.0 V in High-Power Mode

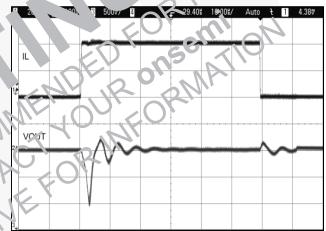

Figure 23 Lo 'Tran, nt, mA tc 400 mA, V<sub>OUT</sub> = 1.0 V in L v-Powe, Mode

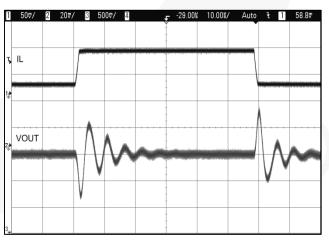

Figure 25. Load Transient, 0 mA to 400 mA, V<sub>OUT</sub> = 2.5 V in Low-Power Mode

FAN5904 — Multi-Mode Buck Converter for GSM/EDGE, 3G/3.5G and 4G PAs

t 3 2.77V

Stop

# Unless otherwise noted, $V_{IN}$ = EN = 3.7 V, L = 1.0 $\mu$ H, $C_{OUT}$ = 2 x 4.7 $\mu$ F, and $T_A$ = +25°C. 2 5.00♥/ 3 2.00V/ 4 500♥/ ₽ 4.000% 200.0%/ Stop € 3 2.77V VOUT SW

**Typical Characteristics**

IL

VOUT SW IL

2 5.00%/ 3 2.00V/ 4 500%/ F 4.000% 200.0%/

Figure 34. Switching Waveforms, PWM Mode, f<sub>sw</sub> = 3 MHz, Figure 35. Switching V vet ins, PWM Node, fsw = 3 MHz, AD = J00 mA in High-Power Mode ILOAD = 800 mA in High-Power Mode

1

William .

1 2500

FAN5904 ---

Multi-Mode Buck Converter for GSM/EDGE,

3G/3.5G and 4G PAs

## **Operating Description**

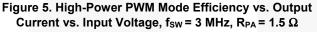

The FAN5904 is a high-efficiency, synchronous, stepdown converter operating with current-mode control. A wide range of load currents is supported. High-current applications, up to a DC output of 2.3 A demanded by GSM/EDGE applications, are allowed. Performance degradation due to spurs is mitigated by selection of a 3 MHz or 6 MHz switching rate. Moreover, the FAN5904 offers Bypass Mode, where the output is shorted to the battery input via a low on-state resistance bypass FET.

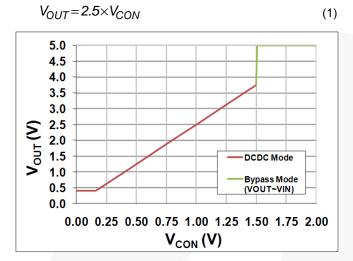

The output voltage  $V_{OUT}$  is regulated to 2.5 times the input control voltage,  $V_{CON}$ , set by an external DAC. The FAN5904 operates in either PWM or PFM Mode, depending on the output voltage and load current.

In Pulse Width Modulation (PWM) Mode, regulation begins with an on-state where a P-channel transistor is turned on and the inductor current is ramped up until the off-state begins. In off-state, the P-channel is switched off and an N-channel transistor is turned on. The inductor current decreases to maintain an average value equal to the DC load current. The inductor current is continuously monitored. A current sense detects when the P-channel transistor current exceeds the current limit and the switcher is turned back to off-state to decrease the inductor current sense detects when the N-channel transistor current exceeds the current limit and redirects dischar, cur, of through the inductor back to the battery.

In Pulse Frequency Modulation (F M) M 'e, t low load currents, the FAN5904 operates a const it on-time mode. During the on-state, the man list head on for a specified on-time before witching to state, curing which the N-channel itch enab d until the inductor

De.

"nd

current decreases to 0 A. The switcher output is then put in high-impedance state until a new regulation cycle starts.

PFM operation is allowed only in Low-Power Mode. At low load currents, PFM achieves higher efficiencies than PWM. To allow optimization of system performance, two versions of the FAN5904 are available. The FAN5904UC00X enables PFM only when  $V_{OUT}$  is less than approximately 1 V. The FAN5904UC01X allows PFM to be entered at higher output voltages.

PFM Mode is only enabled for output load currents nominally less than 100 mA. This realizes high efficiency down to 10mA load current. This is ported in High-Power Mode (MODE = 0) and f. / be c. abled in Low-Power Mode by tying the SYM input IIGH.

### Low-Power Auto M 'e / OD 1)

Low-Power Auto Mc is the? or 3G'3.5G and 4G applications C ent series are normally 1.65 Apk and powers rels to 2% IBm are supported.

### High 'a, ?Www.Mode (MODE = 0)

Du to e large current requirements in GEM/FDGE applition only FWM Mode is supported when the FAN5s 1 is configured for High Power Mode. Currentinse limits are increased to allow for large load currents up to a maximum of approximately 3.3 A.

## Bypass Mode

JE F

In Bypass Mode, the DG-DC turns into 100% duty cycle and the bypass FET is turned on, which allows a very low voltage droport and up to 3.0 A load current.

|   |   | ode                        | Mode Description                              |      | Cond | itions |    |

|---|---|----------------------------|-----------------------------------------------|------|------|--------|----|

|   |   | out                        |                                               | MODE | SYNC | BPEN   | EN |

|   | 1 | Standby Mcde               | Whole IC disabled                             | Х    | Х    | Х      | 0  |

|   | 2 | Auto Mea + Low Power       | ກວ-ມC in Auto Mode <sup>(10)</sup>            | 1    | 0    | 0      | 1  |

|   | 3 | Forced 2WM Mode Low Forver | DC-DC in PWM Mode only                        | 1    | 1    | 0      | 1  |

| ~ | 4 | PWM Mode High Powe         | DC-DC in PWM High-Power Mode                  | 0    | 0    | 0      | 1  |

|   | 5 | Bypass Mode                | Bypass FET and PFET forced to 100% duty-cycle | Х    | Х    | 1      | 1  |

#### Note:

Table 1

10. When V<sub>OUT</sub> exceeds the bypass threshold, the bypass FET is enabled and the DC-DC goes to 100% duty cycle. When V<sub>OUT</sub> is less than the exit threshold, the bypass FET is disabled and the DC-DC re-enters Auto Mode.

(2)

## **DC Output Voltage**

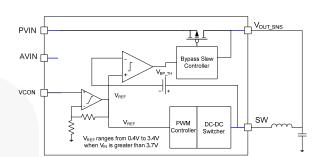

The output voltage of the FAN5904 is determined by  $V_{\text{CON}}$  provided by an external DAC or voltage reference:

#### Figure 54. Output Voltage vs. Control Voltage

The FAN5904 is able to provide a regulated V<sub>OUT</sub> only if V<sub>C</sub> falls within the typical range from 0.16 V to 1.40 V. This a web V<sub>OUT</sub> to be adjusted between 0.4 V and 3.5 V. If V<sub>COL</sub> is less than 0.16 V, V<sub>OUT</sub> is clamped to 0.40 V.The part enters Bypass Mode for V<sub>CON</sub> > 1.50 V. In Low-Power 1. (M<sub>1</sub> DE = 1), the FAN5904 automatically switches betwee PVvM and Bypass Modes and PFM oper on since valle<sup>k</sup>.

When  $V_{OUT}$  approaches the batter voltage, the DC-DC operates in a constant off-time more and the frequency is adjusted to achieve high the cycle. The system operates in this regulated in de unul the typass condition is satisfied.

### Byr Jsh na

As V<sub>0</sub> and he battery voltage converge, the DC-DC begins to on ate in constant off-time mode until eventually the DC-DC transitions to 100% duty cycle and the low R<sub>DSON</sub> bypass FET is turned on. The battery voltage that results in 100% duty cycle operation depends on the output voltage, the voltage drop across the DC-DC converter, and the DC voltage drop across the inductor. In other words, the duty cycle is set by the ratio of the voltages across the inductor.

In many RF applications, it is undesirable for the DC-DC to reach 100% duty cycle since this would result in excessive output ripple. To minimize ripple, the FAN5904 implements a dynamic bypass threshold based on the voltage difference between the battery voltage (sensed through the AVIN pin), the voltage drop across the DC-DC PMOS device, and the internally generated reference voltage V<sub>REF</sub>, as described in Figure 55. The Bypass Mode enter and exit thresholds are higher in High-Power Mode due to the higher load current capability. Bypass Mode is also entered when V<sub>CON</sub> exceeds 1.5 V and exited when V<sub>CON</sub> is less than 1.4 V.

#### Figure 55. Enabling Bypass Transistor Circuit

The bypass FET is turned on process. 'y using a slew rate controller to limit the inrush corrent size Bypass Woor effectively shorts the input apply is to a parcitive load.

The resulting inrush cup of expreted as a function of the specified slew rate of follows:

$I_{INRU} \approx U_{T} \frac{\Delta}{dt} = C_{UUT} \cdot V_{BP_SLEW}$

2

### M. hokout Mode and Synchronization

It not be desirable to prevent the DC-DC converter from operating in PFM Mode. For example, the low PFM witching frequency may interfere with audio circuitry and using PWM may eliminate the mentionence. When configured for Low-Power Mode (MODE = 1) a logic 1 on the SYNC pin forces the IC to avoid PFM Mode. Logic 0 allows the IC to automatically switch to PFM Mode during light loads.

In Low-Power or High-Power Modes, toggling the SYNC pin forces the converter to synchronize its switching frequency to the frequency on the SYNC pin (f<sub>SYNC</sub>). The signal must be within the oscillator synchronization frequency range and most the threshold voltage requirements.

### **Dynamic Output Voltage Transitions**

FAN5904 has a complex voltage transition controller that realizes  $10\mu$ s transition times with a large output capacitor and output voltage ranges.

The transition controller manages five transitions:

- ΔV<sub>OUT</sub> positive step

- ΔV<sub>OUT</sub> transition from or to Bypass Mode

- ΔV<sub>OUT</sub> transition after BPEN

In all cases, it is recommended that sharp  $V_{\text{CON}}$  transitions be applied, letting the transition controller optimize the output voltage slew rate.

#### ΔV<sub>OUT</sub> Positive Step

After a V<sub>CON</sub> positive step, the FAN5904 goes into a current limit mode, where V<sub>OUT</sub> ramps with a constant slew rate dictated by the output capacitor and the current limit  $I_{LIMp}$

#### **∆V**<sub>OUT</sub> Negative Step

After a V<sub>CON</sub> negative step, the FAN5904 enters a current limit mode where V<sub>OUT</sub> is reduced with a constant slew rate dictated by the output capacitor and the current limit  $I_{LIMn}$ .

#### V<sub>OUT</sub> Transition to or from Bypass Mode

The transition to or from Bypass Mode requires that the bypass conditions be met. The FAN5904 performs detection of the bypass conditions 2  $\mu s$  after  $V_{CON}$  transition and enables the required charging / discharging circuit to realize a transition time of 20  $\mu s.$

**V**<sub>OUT</sub> Transition at Startup

### **Application Information**

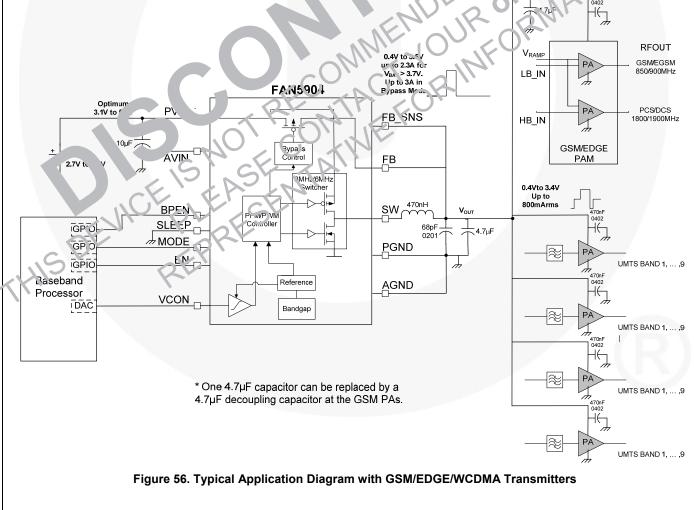

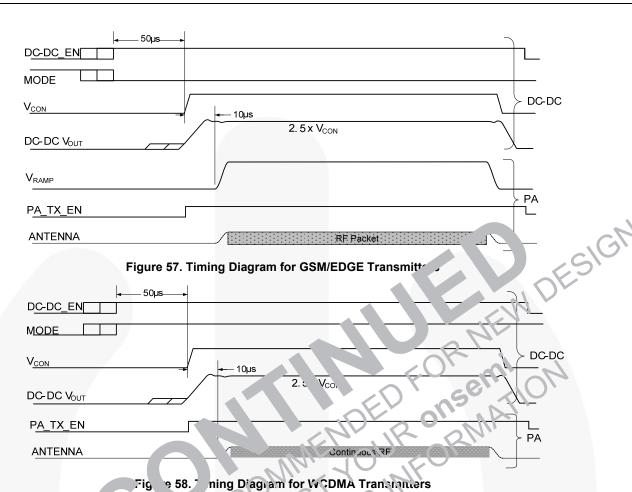

Figure 56 illustrates an application of the FAN5904 in a GSM/EDGE/WCDMA transmitter configuration. The FAN5904 is ideal for driving multiple GSM/EDGE and 3G/3.5G and 4G PAs. Figure 57 presents a timing diagram designed to meet GSM specifications. The FAN5904

At startup, after EN rising edge is detected, the system requires  $25 \ \mu s$  to allow all internal voltage references and amplifiers to start before enabling the DC-DC function.

#### VOUT Transition after BPEN

When BPEN goes HIGH, the controller dismisses the internal bypass flags and sensors and enables Bypass Mode. However, the transition is managed with the same current limits and slew rate used during regular transitions.

#### **Thermal Protection**

When the junction temperature exceeds the maximum specified junction temperature, the FAN5904 enters Power-Down Mode (except the thermal detection circuit).

designed to upport roltage transients of 10 µs when configured for TM/F GE applications (MODE = 0) and driv loa capacitance of opproximately 10 µF. Figure 58 ow a time tiagram for NCDMA conditions.

## Application Informa on

### Inductor Selec

The FAN5904 verates a 6 MHz switching frequency in Low-Piver inde no civilHz in High-Power Mode and as such, 70 nH 1.1. IH inductors can be used, respectively. For aplication requiring the smallest possible PCB area, use a 4. m 2016 inductor; or a 1.0 µH 3000 inductor for optimum eniciency performance).

### Table 2. Recommended Inductors

| Inductor | Description                                                    |

|----------|----------------------------------------------------------------|

| (HIG     | 470 nH, ±30½, 2.3 A, 2016 (metric)<br>TDK: VLS201610MT-R47N    |

|          | 470 nH, ±30%, 2.8 A, 2520 (metric)<br>TDK: VLS252010T-R47N     |

| L        | 470 nH, ±20%, 2.3 A, 2520 (metric)<br>Samsung: CIG22HR47MNE    |

|          | 470 nH, ±20%, 1.8 A, 2520 (metric)<br>Taiyo-Yuden: CKP2520R47M |

|          | 1.0 μH, ±20%, 2.4 A, 3030 (metric)<br>Coilcraft: XFL3010-102ME |

## **Capacitor Selection**

The minimum required output capacitor  $C_{OUT}$  should be two (2) 4.7  $\mu$ F, 10 V, X5R with an ESR of 10 m $\Omega$  or lower, and an ESL of 0.3 nH or lower placed in parallel after inductor L1. Larger case sizes result in increased loop parasitic inductance and higher noise. One of the 4.7  $\mu$ F capacitors should be used as a decoupling capacitor at the GSM/EDGE PA V<sub>CC</sub> pin.

A 0.1  $\mu F$  capacitor may be added in parallel with  $C_{\text{OUT}}$  to reduce the capacitor's parasitic inductance.

| Capacitor              | Description                  |

|------------------------|------------------------------|

| C <sub>IN</sub>        | 10 μF, ±20%, X5R, 10 V       |

| C <sub>OUT</sub>       | (2) 4.7 µF, ±20%, X5R, 6.3 V |

| C for $V_{\text{CON}}$ | 470 pF, ±20%, X5R, 25 V      |

## **Filter VCON**

VCON is the analog control pin of the DC-DC and should be connected to an external Digital-to-Analog Converter (DAC). It is recommended to add up to 470 pF decoupling capacitance between VCON and AGND to filter DAC noise. This capacitor also helps protect the DAC from the DC-DC high-frequency switching noise inherently coupled through the VCON pin. The value of the capacitor must be selected according to the DAC performance since it could limit the DAC output voltage slew rate. 470 pF is typically used.

Any noise on the V<sub>CON</sub> input is transferred to V<sub>OUT</sub> with a gain of two and a half (2.5). If the DAC output is noisy, a series resistor may be inserted between the DAC output and the capacitor to form an RC filter.

Follow these guidelines:

- Use a low noise source or a driver with good PSRR to generate V<sub>CON</sub>.

- The V<sub>CON</sub> driver must be referenced to AGND.

- V<sub>CON</sub> routing must be protected against PVIN, SW, and PGND signals, as well as other noisy signals. Use AGND shielding for better isolation.

- Be sure the DAC output can drive the capacitor VCON. It may be necessary to insert a low-value resistor to ensure DAC stability while not slowin V<sub>CON</sub> fast transition times.

### **No Floating Inputs**

The FAN5904 does not have internal ull-dow results or or its inputs. Therefore, unuse put, should not be left floating and should be pulled fIGH or Lo

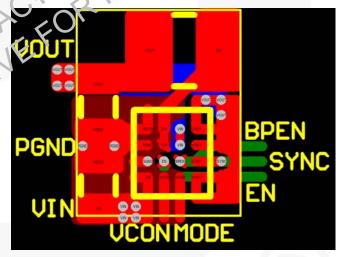

### PCB Layout and Jmp nent Placement

- The key pine to acement is the power ground PGND cont ction shr id between the FA 95904, C1, ar or This pine test the parasitic inductance of the titching op ths.

- Pla the inductor away from the feedback pins to preve anprecipitable loop behavior.

- Ensure the traces are wide chough to handle the maximum current value, especially in Bypass mode.

- Ensure the vias are able to handle the current density.

Use filled vias if available.

- Refer to Fairchild's application note: AN9726 The Importance of PCB Design for FAN5903 and FAN5904.

### Assembly

- Use lead-free solder reflow temperature profile.

- Use metal-filled or solder-filled vias, if available.

- Poor soldering can cause low DC-DC conversion efficiency. If the efficiency is low, X-ray the solder connections to verify their integrity.

- PVIN and PGND must be routed with the widest and shortest traces possible. It is acceptable for the traces connecting the inductor to be long rather than having long PVIN or PGND traces.

- Ensure that the routing loop, PVIN PGND VOUT is as short as possible.

- Place PGND on the t p is an connect it to the AGND ground plan .ext to C usin several yeas

- Two mail ias an used to contract the SW node to the induct L1. Sectider-filled vias, if available.

e ction from C<sub>DUT</sub> to FE should be wide to m. mize the Bypess Mode voic ge drop and the series indultance. Even if the curront in Bypass Mode is small, the princ trace short and at least 5 mm wide.

The AGND ground plane should not be broken into pieces. Ground currents must have a direct, wide path from input to output.

Each capacitor should have at least two dedicated ground vias. Prace vias within 0.1 mm of the capacitors.

Figure 59. Example PCB Layout of FAN5904

NOT RECONNENDED FOR MENDESIGN ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5817–1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

© Semiconductor Components Industries, LLC