# Floppy Disk Hard Sector Data Handler HSDH

# FEATURES

- Hard-Sectored Operation performs all data operations

- Single or Double Density Operation recording code independent

- Minifloppy or Standard Floppy compatible

- □ Programmable Sync Byte

- Internal Sync Byte Detection and Byte Framing

- Fully Double Buffered

- Data Overrun/Underrun Detection

- □ Dual Disk Operation Write on one disk drive while simultaneously reading from another

- Tri-State Output Bus for processor compatibility

- TTL Compatible Inputs and Outputs

# SECTION VI

# **GENERAL DESCRIPTION**

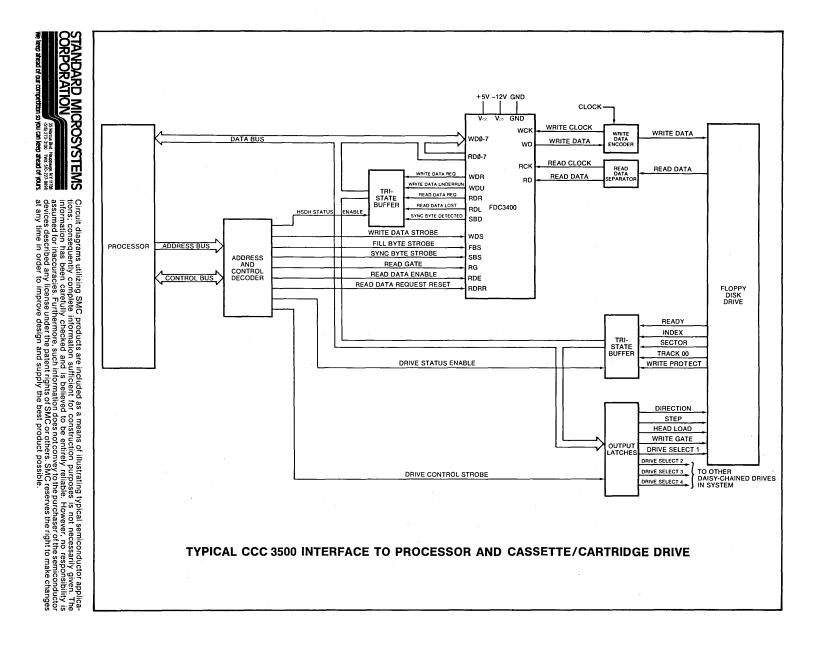

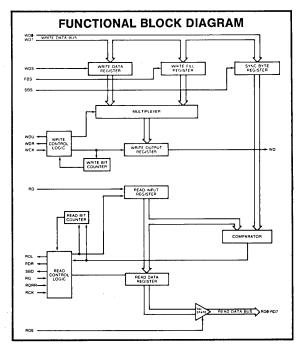

The FDC3400 is an MOS integrated circuit which simplifies the data interface between a processor and a floppy disk drive. During a write operation, the HSDH receives data from the processor and shifts it out bit-serially to the floppy disk data encoding logic. Similarly, during a read operation the HSDH receives a bit-serial stream of read data from the floppy disk data separator, establishes byte synchronization by detecting the sync byte, and transfers data on a byte by byte basis to the processor.

The HSDH detects data overrun and underrun conditions and indicates these conditions on its status lines. A data underrun causes write data to be written onto the disk from a special programmable fill register until new data is entered into the write data buffer or until the write operation is ended.

Separate read and write data registers permit simultaneous read and write operations on two different drives for enhanced system throughput. The HSDH is fully double buffered and all inputs and outputs are TTL compatible.

# **DESCRIPTION OF OPERATION**

Prior to reading or writing on the disk, the read/write head must be positioned and loaded onto the desired track.

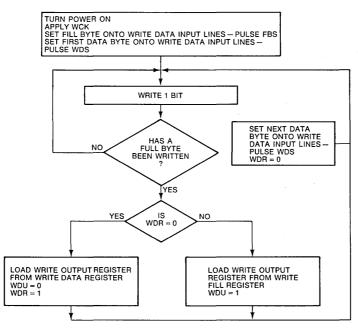

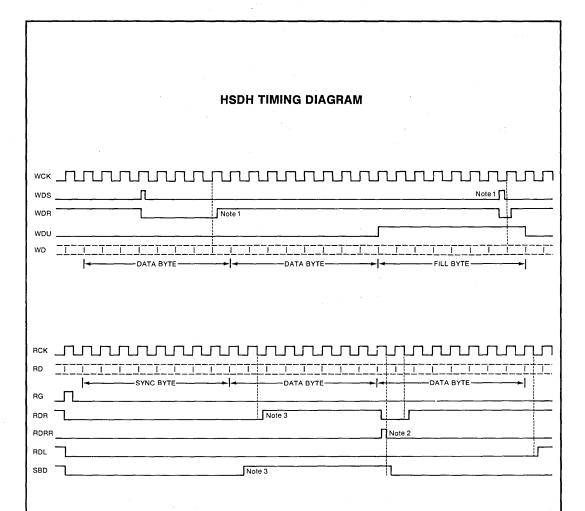

#### Write Operation

The Write Clock is set at the desired bit rate (usually 125, 250, or 500KHz), and the desired fill byte is written into the Write Fill Register. After the external logic makes the write enable to the drive active, the first byte to be written should be loaded into the Write Data Register. This byte is then loaded into the Write Output Register and shifted out bit serially to the external write encoding logic. The first bit shifted out of each byte is the LSB. Whenever a byte is transferred from the Write Data Register to the Write Output Register, Write Data Request becomes active and requests another byte from the processor. If new data is not loaded into the Write Data Register before the Write Output Register becomes empty, then the Write Output Register is loaded with data from the Write Fill Register and the Write Data Underrun status line is set. WDU is reset the next time WDS is pulsed. At the end of the write operation, the processor should return the external write enable line to an inactive state.

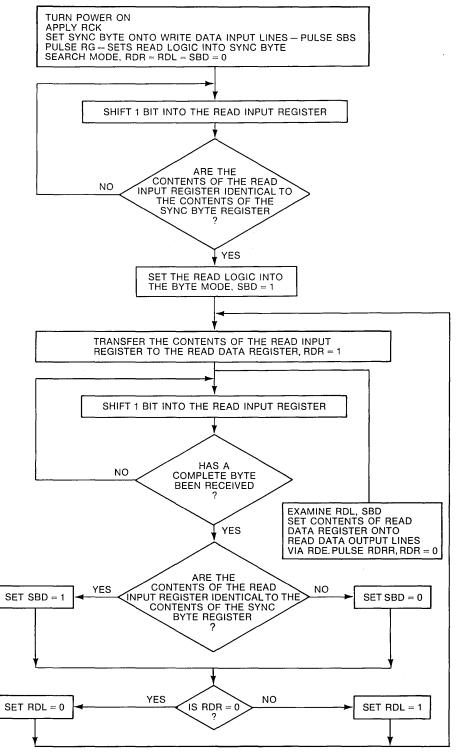

#### **Read Operation**

The Read Clock is set at the desired bit rate (usually 125, 250, or 500KHz) and the desired sync byte is loaded into the Sync Byte Register. When the processor wishes to read a sector of data it causes a transition on the Read Gate input to set the read logic into a sync byte search mode. In the search mode the serial read data bit stream is examined on a bit by bit basis until a sync byte is found. A sync byte Register and the Read Input Register are identical. When this occurs the Sync Byte Detected output is set high. This byte is the loaded into the Read Data Register and the read logic is set into the

byte mode. In this mode each byte read is loaded into the Read Data Register and Read Data Request is made active high for each byte. The processor responds to each Read Data Request by enabling the output bus with Read Data Register, and resetting Read Data Request by pulsing Read Data Request Reset. If the processor fails to respond to Read Data Request within one byte time, the Read Data Lost status line is set. When the processor has read the required amount of data it may reset Read Gate to an inactive-high level.

#### System Operation – Additional Features

#### Automatic Sector Fill

In some applications, such as the end of a logical file, the system buffer may contain less than a full sector of data. In this case the processor need supply only this data to the FDC3400. The FDC3400 will then underrun, setting the Write Data Underrun Status line and thereby causing the remainder of the sector to fill with bytes taken from the Write Fill Register. This operation continues until the processor returns the disk's write enable signal to an inactive level.

#### Byte Search

After byte synchronization has been established during a read operation, the processor may load a different byte into the Sync Byte Register. Whenever that byte occurs in the data being read, the Sync Byte Detected status line will go high. This feature permits the processor to search for the occurence of a specific byte while reading a sector.

#### Multiple Byte Synchronization

Some systems use two or more contiguous sync bytes to establish byte synchronization. For these applications, the number of Read Data Requests received while Sync Byte Detected remains active-high may be counted by the processor to establish valid synchronization.

## FLOW DIAGRAM - WRITE DATA

# FLOW DIAGRAM - READ DATA

# **DESCRIPTION OF PIN FUNCTIONS**

| PIN NO. | SYMBOL  | NAME                       | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|---------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | RD      | Read Data                  | The Read Data input accepts the serial data stream<br>from the floppy disk data separator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2       | RCK     | Read Clock                 | The negative-going edge of the Read Clock input shifts Read Data into the Read Input Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3       | RDRR    | Read Data<br>Request Reset | An active-high pulse input on the Read Data Request<br>Reset input resets the RDR output to a low level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4       | RDE     | Read Data<br>Enable        | An active-high level on the Read Data Enable line gates the outputs of the Read Data Register onto the Read Data Output lines.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5       | RDR     | Read Data<br>Request       | The Read Data Request output is made active-high wher<br>an assembled byte is transferred from the Read Input<br>Register to the Read Data Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6       | RDL     | Read Data Lost             | The Read Data Lost output is made active-high, if the<br>byte presently in the Read Data Register is not read<br>(RDR not reset) by the processor before the next byte is<br>loaded into the Read Data Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7-14    | RD7-RDØ | Read Data<br>Output        | When enabled by RDE the tri-state Read Data Output<br>lines present the data in the Read Data Register to the<br>processor. When RDE is inactive-low the RD7-RDØ lines<br>are held at a high-impedance state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15-19   | NC      |                            | Not Connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 20      | Vcc     | Power Supply               | + 5 volt supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 21      | NC      |                            | Not Connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 22      | WDR     | Write Data<br>Request      | The Write Data Request output is made active-high<br>when the Write Data Register becomes empty and<br>requires a data byte. It is reset to a low level when WDS<br>occurs to load the Write Data Register. If WDR is not<br>serviced by the time the next byte is required by the<br>Write Output Register, the byte stored in the Write Fill<br>Register is written onto the disk and the WDU line is<br>made active high.                                                                                                                                                                                                                                                                                                                      |

| 23      | WD      | Write Data                 | The Write Data output presents the serial stream of data<br>to the external write data encoder. Each byte is normally<br>provided from the Write Data Register provided that a<br>WDS pulse occurs during the presently written byte.<br>If WDS is not pulsed, the next byte to be written will be<br>extracted from the Write Fill Register.                                                                                                                                                                                                                                                                                                                                                                                                     |

| 24      | GND     | Ground                     | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 25      | WDU     | Write Data<br>Underrun     | The Write Data Underrun output is set active-high when<br>the processor fails to respond to the WDR signal<br>within one byte time. When WDU occurs the data<br>written on the disk is extracted from the Write Fill<br>Register. This line is reset when WDS is pulsed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 26      | VDD     | Power Supply               | —12 volt supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 27-34   | WDØ-WD7 | Write Data<br>Input        | The Write Data Input lines present information to the<br>Write Data Register, the Write Fill Register, and the<br>Sync Byte Register under control of their respective<br>strobes. The strobes operate independently of each<br>other. The LSB should always be placed on WDØ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 35      | RG      | Read Gate                  | This input should be pulsed to a high-level after<br>power turn on to reset RDR, SBD, and RDL to an inactive<br>low level. The high-to-low transition of RG sets the read<br>logic into the sync byte search mode. In this mode<br>the serial Read Data stream is examined on a bit by bit<br>basis until a sync byte is found. A sync byte is found by<br>definition when the contents of the Sync Byte Register<br>and the Read Input Register are identical. When this<br>occurs the SBD output is set active-high. The sync byte<br>just read is then transferred into the Read Data Register<br>RDR is set high, and the read logic is set into the byte<br>mode. In this mode each byte read is transferred into<br>the Read Data Register. |

| 36      | SBD     | Sync Byte<br>Detected      | The Sync Byte Detected output is set active-high each<br>time the byte loaded into the Read Data Register is<br>identical to the byte in the Sync Byte Register. This<br>output is reset low the next time the Read Data Register<br>is loaded with a byte which is not a sync byte.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

# **DESCRIPTION OF PIN FUNCTIONS**

| PIN NO. | SYMBOL | NAME                 | FUNCTION                                                                                                                          |

|---------|--------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 37      | FBS    | Fill Byte<br>Strobe  | The Fill Byte Strobe is an active-high input strobe which<br>loads the byte on the WDØ-WD7 lines into the Write<br>Fill Register. |

| 38      | WCK    | Write Clock          | Each positive-going edge of this clock shifts one bit<br>out of the Write Output Register onto WD.                                |

| 39      | WDS    | Write Data<br>Strobe | The Write Data Strobe is an active-high input strobe which loads the byte on the WDØ-WD7 lines into the Write Data Register.      |

| 40      | SBS    | Sync Byte<br>Strobe  | The Sync Byte Strobe is an active-high input strobe which loads the byte on the WDØ-WD7 lines into the Sync Byte Register.        |

|         |        |                      | 1                                                                                                                                 |

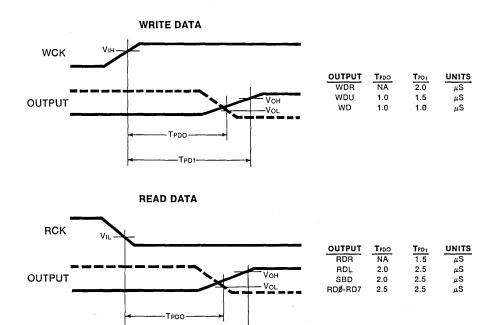

# ADDITIONAL TIMING INFORMATION (Typical Propagation Delays)

-TPD1-

#### NOTE 1

The Write Output Register is loaded with the next byte at the positive clock transition corresponding to the leading edge of the last bit of the current byte on the WD output. WDR is set high approximately two microseconds after this clock transition. If it is desired that the next byte be extracted from the Write Data Register the leading edge of the WDS should occur at least one microsecond prior to this clock transition.

#### NOTE 2

In order to avoid an RDL indication the leading edge of the RDRR pulse should occur at least one microsecond prior to the negative clock transition corresponding to the center of the first bit after the last bit of the previous byte on the RD input.

#### NOTE 3

The RDL, SBD and RD0-RD7 output are set to their correct levels approximately two microseconds after the negative clock transition corresponding to the center of the first bit after the last bit of the previous byte on the RD input. The RDR output is set high at the next negative clock transition.

| Operating Temperature Range           | 0°C to +70°C   |

|---------------------------------------|----------------|

| Storage Temperature Range             | 55°C to +150°C |

| Load Temperature (soldering, 10 sec.) | +325°C         |

| Positive Voltage on any Pin, Vcc      | + 0.3V         |

| Negative Voltage on any Pin, Vcc      | 25V            |

\*Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied.

## ELECTRICAL CHARACTERISTICS (TA=0°C to 70°C, Vcc= +5V ±5% Voo= -12V±5%, unless otherwise noted)

| Parameter                                                                                         | Min.                          | Тур.       | Max.       | Unit                       | Conditions                                                                                                            |

|---------------------------------------------------------------------------------------------------|-------------------------------|------------|------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------|

| D.C. CHARACTERISTICS                                                                              |                               |            |            |                            |                                                                                                                       |

| INPUT VOLTAGE LEVELS<br>Low-level, Vı⊾<br>High-level, Vı⊩                                         | V₀₀<br>V₅с-1.5                |            | 0.8<br>Vcc | v<br>v                     |                                                                                                                       |

| OUTPUT VOLTAGE LEVELS<br>Low-level, Vo⊾<br>High-level, V୦н                                        | 2.4                           | 0.2<br>4.0 | 0.4        | v<br>v                     | l₀. = 1.6mA<br>l₀ <sub>H</sub> = −100μA                                                                               |

| INPUT CURRENT<br>Low-level, In                                                                    |                               |            | 1.6        | mA                         | See note 1                                                                                                            |

| OUTPUT CURRENT<br>Leakage, Ito<br>Short circuit, Ios**                                            |                               |            | -1<br>10   | μA<br>mA                   | $\begin{aligned} \text{RDE} = V_{\text{il}}, & 0 \leq V_{\text{out}} \leq +5V \\ V_{\text{out}} = & 0V \end{aligned}$ |

| INPUT CAPACITANCE<br>All inputs, C⊪                                                               |                               | 5          | 10         | pF                         | V <sub>™</sub> =Vcc, f=1MHz                                                                                           |

| OUTPUT CAPACITANCE<br>All outputs, Cour                                                           |                               | 10         | 20         | pF                         | RDE=V <sub>it</sub> , f=1MHz                                                                                          |

| POWER SUPPLY CURRENT<br>Icc<br>Ioo                                                                |                               |            | 28<br>28   | mA<br>mA                   | All outputs = V₀н                                                                                                     |

| A.C. CHARACTERISTICS                                                                              |                               |            |            |                            | T₄= +25°C                                                                                                             |

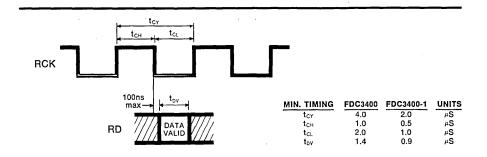

| CLOCK FREQUENCY                                                                                   | DC<br>DC                      |            | 250<br>500 | KHz<br>KHz                 | RCK, WCK<br>RCK, WCK, FDC3400-1                                                                                       |

| PULSE WIDTH<br>Clock                                                                              | 1<br>0.5                      |            |            | μS<br>μS                   | RCK, WCK<br>RCK, WCK, FDC3400-1                                                                                       |

| Read Gate<br>Write Data Strobe<br>Fill Byte Strobe<br>Sync Byte Strobe<br>Read Data Request Reset | 1<br>200<br>200<br>200<br>200 |            |            | μs<br>ns<br>ns<br>ns<br>ns | RG<br>WDS<br>FBS<br>SBS<br>RDRR                                                                                       |

| INPUT SET-UP TIME<br>Write Data Inputs                                                            | 0                             |            |            | ns                         | WDØ-WD7                                                                                                               |

| INPUT HOLD TIME<br>Write Data Inputs                                                              | 0                             |            |            | ns                         | WDØ-WD7                                                                                                               |

| STROBE TO OUTPUT DELAY<br>Read Data Enable                                                        |                               | 180        | 250        | ns                         | Load = 20pf + 1 TTL input<br>RDE: TFDI, TFDO                                                                          |

| OUTPUT DISABLE DELAY                                                                              |                               | 100        | 250        | ns                         | RDE                                                                                                                   |

\*\*Not more than one output should be shorted at a time.

NOTES:

1. Under steady state condition no current flows for TTL or MOS interfacing. A switching current of 1.6mA maximum flows during a high to low transition of the input.

The tri-state output has 3 states:

1) low-impedance to V<sub>cc</sub>

2) low-impedance to GND

3) high-impedance OFF ≅ 10M ohms

The OFF state is controlled by the RDE input.