---

## **32-bit ARM® Cortex™-M0+ MCU With 3-Channel 20-Bit 1KSPS Low Noise, Low Power AFE**

---

### **Features**

#### **MCU Block**

- Core:32-bit ARM ® Cortex™-M0+ CPU

- 24 MHz maximum frequency

- support 0 wait state access

- Memories

- 64Kbytes Flash

- 4KB SRAM

- Power Supply: 2.7V~3.6V

- Operation temperature: (-40~85°C)

- Low Voltage Detector (LVD) / Voltage Comparator (VCMP)

- Clock management

- 4 ~24MHz External high speed clock(HSE)

- 4 ~24MHz Internal high speed clock(HIS)

- 32.768KHz External low speed clock(LSE)

- 38.4/32.768KHz Internal low speed clock(LSI)

- Three operation: run mode, sleep mode, deep sleep mode

- Maximum 16 I/O ports

- Debug mode

- Serial wire debug (SWD) , 2 watch points/4 break points

- 128-bit unique ID

- 6 communication interfaces

- Up to 2 UART

- 1 LPUART

- 1 SPI

- 1 I2C

- one 1-wire

- Buzzer generator

- Up to 10 timers

- 1 16-bit advanced timers , 3 pairs of complementary outputs

- 1 16-bit general purpose timer

- 1 16-bit programmable timer

- Up to two 16/32bit basic timer

- 2 watchdog timers (Independent and Window)

- 1 16-bit low power timer

- 1 SysTick timer

- 1 8-bit automatic wake-up timer

- RTC clock counter(record the year, month, day, hour, minute and second )

- One 12-bit ADC(SAR)

- Max convert rate: 1Msps

- Maximum 16 channels

- CRC-16 calculation Unit

#### **AFE Block**

- 2.7V to 3.6V operation voltage range

- Up to 20 bits ENOB

- RMS noise

- 1.14uV RMS noise @4Hz, PGA=1X

- 82nV RMS noise @ 4Hz, PGA=128X

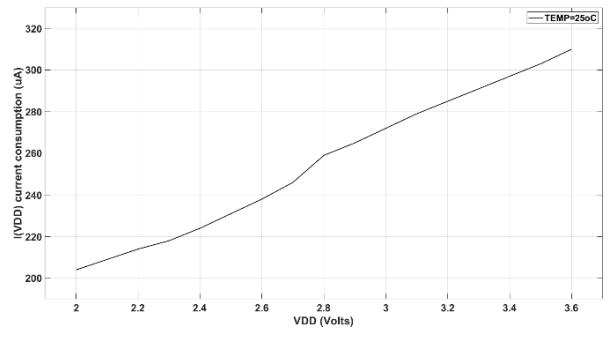

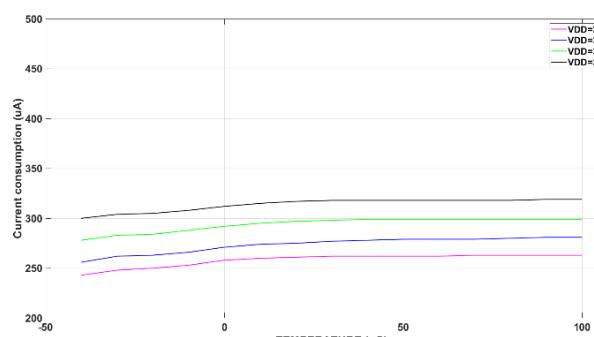

- 300uA ultra-low current consumption

- 6uA (typ.) standby-mode current

- ADC I/O Channels

- 3CH fully differential analog input channels

- 2CH fully differential VREF input channels

- Internal temperatures sensor

- Power supply voltage detector

- Sensors burn-out diagnostic

- Internal precision clock oscillator

- 2-stage Programmable gain amplifier

- x1 ~ x128 1<sup>st</sup>-stage gain

- x1 ~ x16 2<sup>nd</sup>-stage gain

- Programmable 2x IDACs current sources

- -40 ~ 85°C operation temperature

- 4Hz to 1KHz data rates

## Content

|                                                                |    |

|----------------------------------------------------------------|----|

| MCU Block Diagram .....                                        | 5  |

| AFE Block Diagram .....                                        | 6  |

| Package Outline and Pin Configuration .....                    | 6  |

| Electrical Characteristics .....                               | 12 |

| AFE .....                                                      | 12 |

| MCU .....                                                      | 15 |

| Description .....                                              | 23 |

| Analog Front End (AFE) .....                                   | 23 |

| System Description .....                                       | 23 |

| Power Supplies .....                                           | 24 |

| Reset .....                                                    | 24 |

| Power Supply Monitors .....                                    | 24 |

| Digital Communication Interface and Data Ready Indicator ..... | 24 |

| Bus Fault Timeout .....                                        | 24 |

| I2C Digital Communication Timing Diagrams .....                | 25 |

| Slave Address .....                                            | 26 |

| Register File .....                                            | 28 |

| Channel Multiplexer Configuration .....                        | 28 |

| Instrumentation Amplifier .....                                | 29 |

| ADC Configuration .....                                        | 29 |

| Calibration .....                                              | 29 |

| IDAC Excitation Current Sources for Sensor Stimulation .....   | 30 |

| Reference Signal Configuration .....                           | 30 |

| Clock Oscillator .....                                         | 30 |

| Sensor Fault Detection .....                                   | 30 |

| Linear Regulators .....                                        | 31 |

| Digital Filters .....                                          | 31 |

| PDM data input .....                                           | 31 |

| Local Temperature Sensor .....                                 | 31 |

| On-Chip Sensor Switch .....                                    | 32 |

| Operation Mode Overview .....                                  | 32 |

| ADC Digital Data Output .....                                  | 33 |

| Multiplexer Connection Network .....                           | 33 |

---

|                                                            |    |

|------------------------------------------------------------|----|

| Performance Characteristics .....                          | 34 |

| Noise and Resolution .....                                 | 35 |

| Register Description .....                                 | 37 |

| Layout Note and Grounding Guidelines .....                 | 49 |

| 32-bit ARM® Cortex™-M0+ MCU .....                          | 50 |

| Core with Embedded Flash and SRAM .....                    | 50 |

| CRC Calculation Unit.....                                  | 50 |

| Nested Vectored Interrupt Controller (NVIC) .....          | 50 |

| System Reset .....                                         | 50 |

| Clock.....                                                 | 50 |

| Power supply supervisors (POR/BOR/LVD) .....               | 51 |

| Voltage regulator (LDO) .....                              | 51 |

| Power mode.....                                            | 51 |

| Real Time Clock (RTC) .....                                | 51 |

| Timers and Watchdogs.....                                  | 51 |

| Advanced Timer (TIM1) .....                                | 51 |

| General purpose timer (TIM2) .....                         | 51 |

| Programmable Counter Array (PCA).....                      | 52 |

| Low Power Timer (LPTIM).....                               | 52 |

| Basic timer (TIM10/11) .....                               | 52 |

| Independent Watchdog (IWDG) .....                          | 52 |

| System Watchdog (WWDG).....                                | 52 |

| SysTick timer (SysTick) .....                              | 52 |

| I2C Bus .....                                              | 52 |

| Universal Asynchronous Transceiver (UART1/UART2) .....     | 52 |

| Low Power Universal Asynchronous Transceiver (LPUART)..... | 52 |

| Serial Peripheral Interface (SPI).....                     | 52 |

| General purpose input and output (GPIO) .....              | 53 |

| Analog to Digital Converter (ADC) .....                    | 53 |

| Voltage Comparator (VCMP).....                             | 53 |

| Buzzer (BEEP).....                                         | 53 |

| Automatic wake-up timer (AWK) .....                        | 53 |

| Clock Trim/Monitoring Module (CLKTRIM) .....               | 53 |

---

|                                       |    |

|---------------------------------------|----|

| Unique ID (UID) .....                 | 53 |

| Embedded Debug System.....            | 53 |

| Embedded Debug (DBG) .....            | 53 |

| Absolute Maximum Rating.....          | 54 |

| AFE.....                              | 54 |

| MCU.....                              | 54 |

| Recommended Operating Condition ..... | 55 |

| AFE.....                              | 55 |

| MCU.....                              | 55 |

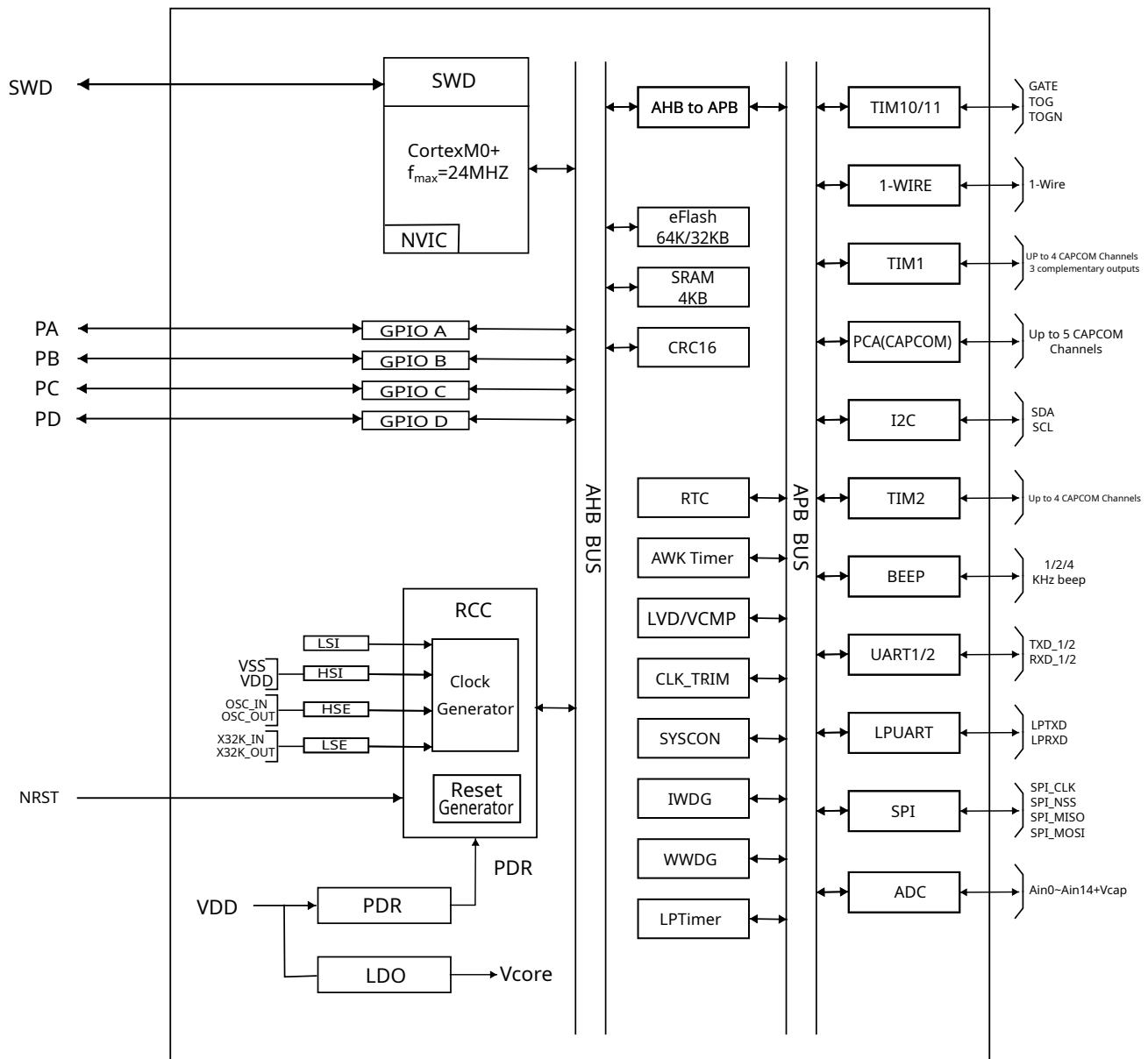

MCU Block Diagram

Figure1. MCU Block Diagram of FE82160

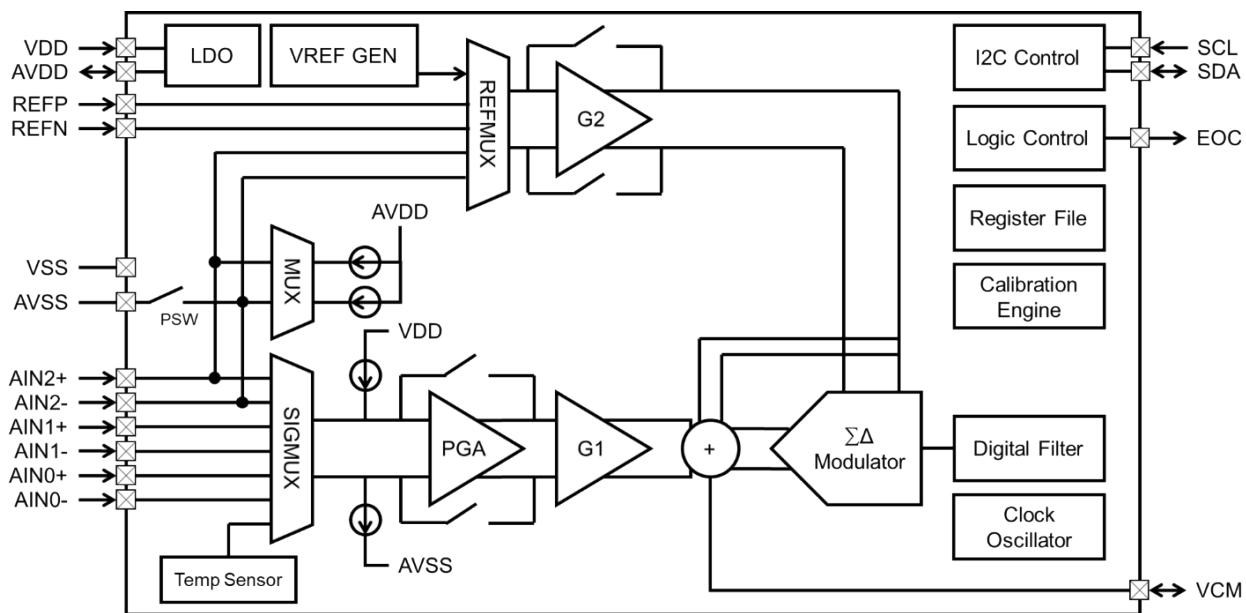

### AFE Block Diagram

Figure 2. AFE Block Diagram

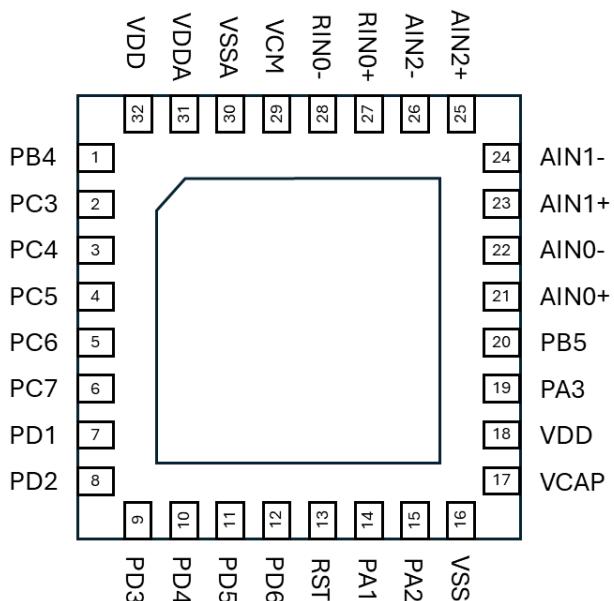

### Package Outline and Pin Configuration

Figure 3. FE82160 Pin Configuration (QFN32 4x4)

Table. QFN32-4x4 pins

| Pin | Name    | Type       | Function                                       |

|-----|---------|------------|------------------------------------------------|

| 1   | SCL/PB4 | X32K_OUT   | 32K Clock source output                        |

|     |         | PB4        | PB4 GPIO                                       |

|     |         | LPTIM_GATE | LPTIM gating                                   |

|     |         | PCA_ECI    | PCA External clock                             |

|     |         | SPI_NSS    | SPI module slave chip selects signals          |

|     |         | I2C_SCL    | I2C clock                                      |

|     |         | UART1_TX   | UART1 TX                                       |

|     |         | TIM11_TOGN | TIM11 Toggle inverting output                  |

|     |         | SCL        | AFE I2C digital interface clock input          |

| 2   | PC3/EOC | PC3        | PC3 GPIO                                       |

|     |         | TIM1_CH3   | TIM1 PWM output 3                              |

|     |         | TIM1_CH1N  | TIM1 PWM output 1 Inverting                    |

|     |         | I2C_SDA    | I2C data                                       |

|     |         | UART2_TX   | UART2 TX                                       |

|     |         | PCA_CH1    | PCA Input capture/Output compare 1             |

|     |         | 1-WIRE     | 1-wire Input/output                            |

|     |         | TIM2_CH3   | TIM2 Input capture/Output compare 3            |

|     |         | AIN1       | ADC Analog input channel 1                     |

|     |         | EOC        | AFE Data converter end of conversion interrupt |

| 3   | PC4     | PC4        | PC4 GPIO                                       |

|     |         | TIM1_CH4   | TIM1 PWM output 4                              |

|     |         | TIM1_CH2N  | TIM1 PWM output 2 Inverting                    |

|     |         | I2C_SCL    | I2C clock                                      |

|     |         | UART2_RX   | UART2 RX                                       |

|     |         | PCA_CH0    | PCA Input capture/Output compare 0             |

|     |         | CLK_MCO    | CPU Clock output                               |

|     |         | TIM2_CH4   | TIM2 Input capture/Output compare 4            |

|     |         | AIN2       | ADC Analog input channel 2                     |

|     |         | PC5        | PC5 GPIO                                       |

| 4   | PC5     | TIM1_BKIN  | TIM1 Brake signal input                        |

|     |         | PCA_CH0    | PCA Input capture/Output compare 0             |

|     |         | SPI_CLK    | SPI Module clock signal                        |

|     |         | LPUART_TX  | LPUART TX                                      |

|     |         | TIM11_GATE | TIM11 gating                                   |

|     |         | LVD_OUT    | Low voltage detection comparator output        |

|     |         | TIM2_CH1   | TIM2 Input capture/Output compare 1            |

|     |         | VCMPIN1    | Analog input                                   |

| Pin | Name | Type      | Function                                       |

|-----|------|-----------|------------------------------------------------|

| 5   | PC6  | PC6       | PC6 GPIO                                       |

|     |      | TIM1_CH1  | TIM1 PWM output 1                              |

|     |      | PCA_CH3   | PCA Input capture/Output compare 3             |

|     |      | SPI_MOSI  | SPI module host output slave input signal      |

|     |      | LPUART_RX | LPUART RX                                      |

|     |      | TIM11_EXT | TIM11 External pulse input                     |

|     |      | CLK_MCO   | CPU Clock output                               |

|     |      | TIM2_CH4  | TIM2 Input capture/Output compare 4            |

|     |      | AIN0      | ADC Analog input channel 0                     |

| 6   | PC7  | SWDIO     | SWD IO                                         |

|     |      | PC7       | PC7 GPIO                                       |

|     |      | TIM1_CH2  | TIM1 PWM output 2                              |

|     |      | PCA_CH4   | PCA Input capture/Output compare 4             |

|     |      | SPI_MISO  | SPI module host input slave output signal      |

|     |      | UART2_RX  | UART2 RX                                       |

|     |      | LSI_OUT   | Internal low frequency RC clock 38.4KHZ output |

|     |      | X32K_OUT  | External low frequency crystal output          |

| 7   | PD1  | SWDCLK    | SWD clock                                      |

|     |      | PD1       | PD1 GPIO                                       |

|     |      | PCA_ECI   | PCA External clock                             |

|     |      | UART2_TX  | UART2 TX                                       |

|     |      | HSE_OUT   | Internal high frequency RC clock 24MHZ output  |

|     |      | VCMP0_OUT | VCMP0 output                                   |

| 8   | PD2  | PD2       | PD2 GPIO                                       |

|     |      | TIM1_CH2  | TIM1 PWM output 2                              |

|     |      | PCA_CH2   | PCA Input capture/Output compare 2             |

|     |      | SPI_MISO  | SPI module host input slave output signal      |

|     |      | RTC_1HZ   | RTC 1HZ output                                 |

|     |      | LPUART_TX | LPUART TX                                      |

|     |      | LPTIM_TOG | LPTIM Toggle output                            |

|     |      | 1-WIRE    | 1-wire Input/output                            |

|     |      | TIM2_CH3  | TIM2 Input capture/Output compare 3            |

|     |      | VCMPIN0   | VCMP input channel 0                           |

|     |      | AIN3      | ADC Analog input channel 3                     |

| Pin | Name | Type       | Function                                  |

|-----|------|------------|-------------------------------------------|

| 9   | PD3  | PD3        | PD3 GPIO                                  |

|     |      | TIM1_CH3N  | TIM1 PWM output 3 Inverting               |

|     |      | PCA_CH1    | PCA Input capture/Output compare 1        |

|     |      | SPI_MOSI   | SPI module host output slave input signal |

|     |      | LSE_OUT    | External high frequency crystal output    |

|     |      | UART1_RX   | UART1 RX                                  |

|     |      | LPTIM_TOGN | LPTIM Toggle inverting output             |

|     |      | TIM2_CH2   | TIM2 Input capture/Output compare 2       |

|     |      | AIN4       | ADC Analog input channel 4                |

| 10  | PD4  | PD4        | PD4 GPIO                                  |

|     |      | TIM1_CH1   | TIM1 PWM output 1                         |

|     |      | PCA_CH0    | PCA Input capture/Output compare 0        |

|     |      | RTC_1HZ    | RTC 1HZ output                            |

|     |      | TIM10_TOG  | TIM10 Toggle output                       |

|     |      | UART1_TX   | UART1 TX                                  |

|     |      | TIM10_EXT  | TIM10 External pulse                      |

|     |      | BEEP       | Buzzer output                             |

|     |      | TIM2_CH1   | TIM2 Input capture/Output compare 1       |

|     |      | VCIN2      | VC input channel 2                        |

| 11  | PD5  | PD5        | PD5 GPIO                                  |

|     |      | TIM1_CH1N  | TIM1 PWM output 1 Inverting               |

|     |      | PCA_CH4    | PCA Input capture/Output compare 4        |

|     |      | SPI_MISO   | SPI module host input slave output signal |

|     |      | I2C_SCL    | I2C clock                                 |

|     |      | UART2_TX   | UART2 TX                                  |

|     |      | TIM10_GATE | TIM10 gating                              |

|     |      | UART1_TX   | UART1 TX                                  |

|     |      | TIM2_CH4   | TIM2 Input capture/Output compare 4       |

|     |      | AIN5       | ADC Analog input channel5                 |

| 12  | PD6  | PD6        | PD6 GPIO                                  |

|     |      | TIM1_CH2   | TIM1 PWM output 2                         |

|     |      | PCA_CH3    | PCA Input capture/Output compare 3        |

|     |      | SPI_MOSI   | SPI module host output slave input signal |

|     |      | I2C_SDA    | I2C data                                  |

|     |      | UART2_RX   | UART2 RX                                  |

|     |      | LPTIM_EXT  | LPTIM External pulse input                |

|     |      | UART1_RX   | UART1 RX                                  |

|     |      | TIM2_CH2   | TIM2 PWM output 2                         |

|  |  |      |                            |

|--|--|------|----------------------------|

|  |  | AIN6 | ADC Analog input channel 6 |

|--|--|------|----------------------------|

| Pin | Name | Type       | Function                                                           |

|-----|------|------------|--------------------------------------------------------------------|

| 13  | RST  | NRST       | Reset input port, low valid, chip reset                            |

| 14  | PA1  | OSC_IN     | External clock source input                                        |

|     |      | PA1        | PA1 GPIO                                                           |

|     |      | TIM1_CH2N  | TIM1 PWM output 2 Inverting                                        |

|     |      | SPI_CLK    | SPI Module clock signal                                            |

|     |      | I2C_SDA    | I2C data                                                           |

|     |      | UART1_RX   | UART1 RX                                                           |

|     |      | TIM10_TOG  | TIM10 Toggle output                                                |

|     |      | UART2_RX   | UART2 RX                                                           |

| 15  | PA2  | OSC_OUT    | External clock source output                                       |

|     |      | PA2        | PA2 GPIO                                                           |

|     |      | TIM1_CH3   | TIM1 PWM output 3                                                  |

|     |      | SPI_NSS    | SPI module slave chip selects signals                              |

|     |      | I2C_SCL    | I2C clock                                                          |

|     |      | UART1_TX   | UART1 TX                                                           |

|     |      | TIM10_TOGN | TIM10 Toggle inverting output                                      |

|     |      | UART2_TX   | UART2 TX                                                           |

|     |      | TIM2_CH2   | TIM2 Input capture/Output compare 2                                |

| 16  | VSS  | GND        | Ground                                                             |

| 17  | VCAP | Power      | LDO kernel power supply (internal circuit use, external capacitor) |

| 18  | VDD  | Power      | power                                                              |

| 19  | PA3  | PA3        | PA3 GPIO                                                           |

|     |      | TIM1_CH3N  | TIM1 PWM output 3 Inverting                                        |

|     |      | PCA_CH2    | PCA Input capture/Output compare 2                                 |

|     |      | SPI_NSS    | SPI module slave chip selects signals                              |

|     |      | RTC_1HZ    | RTC 1HZ output                                                     |

|     |      | LPUART_RX  | LPUART RX                                                          |

|     |      | PCA_ECI    | PCA External clock                                                 |

|     |      | VCMP0_OUT  | Voltage comparator 0 output                                        |

|     |      | TIM2_CH3   | TIM2 Input capture/Output compare 3                                |

|     |      | UART2_TX   | UART2 TX                                                           |

| Pin | Name    | Type         | Function                                           |

|-----|---------|--------------|----------------------------------------------------|

| 20  | PB5/SDA | X32K_IN      | 32K Clock source input                             |

|     |         | PB5          | PB5 GPIO                                           |

|     |         | TIM1_BKIN    | TIM1 Brake signal input                            |

|     |         | PCA_CH4      | PCA Input capture/Output compare 4                 |

|     |         | SPI_CLK      | SPI Module clock signal                            |

|     |         | I2C_SDA      | I2C data                                           |

|     |         | UART1_RX     | UART1 RX                                           |

|     |         | TIM11_TOG    | TIM11 Toggle output                                |

|     |         | LVD_OUT      | LVD comparator output                              |

|     |         | TIM2_CH1     | TIM2 Input capture/Output compare 1                |

|     | SDA     |              | AFE I2C digital interface data I/O                 |

| 21  | VIP0    | Analog input | AFE CH0 differential analog signal input           |

| 22  | VIN0    | Analog input | AFE CH0 differential analog signal input           |

| 23  | VIP1    | Analog input | AFE CH1 differential analog signal input           |

| 24  | VIN1    | Analog input | AFE CH1 differential analog signal input           |

| 25  | VIP2    | Analog input | AFE CH2 differential analog/reference signal input |

| 26  | VIN2    | Analog input | AFE CH2 differential analog/reference signal input |

| 27  | RIP0    | Analog input | AFE CH0 differential reference voltage input       |

| 28  | RIN0    | Analog input | AFE CH0 differential reference voltage input       |

| 29  | VCM     | Input        | AFE Common-mode voltage regulation                 |

| 30  | AVSS    | GND          | AFE Analog ground                                  |

| 31  | AVDD    | Power        | AFE Analog power                                   |

| 32  | VDD     | Power        | AFE Digital power                                  |

**Electrical Characteristics****● AFE**

Table. Electrical Characteristics

| Symbol                        | Description                       | Conditions                                                                   | Min                     | Typ                     | Max                     | Unit   |

|-------------------------------|-----------------------------------|------------------------------------------------------------------------------|-------------------------|-------------------------|-------------------------|--------|

| <b>POWER SUPPLY</b>           |                                   |                                                                              |                         |                         |                         |        |

| I <sub>VDD</sub>              | Supply current                    | PGA bypass                                                                   | —                       | 260                     | 310                     | uA     |

|                               |                                   | PGA mode, gain=1                                                             | —                       | 300                     | 350                     | uA     |

|                               |                                   | Power-down mode                                                              | —                       | 6                       | 9                       | uA     |

| <b>PGA</b>                    |                                   |                                                                              |                         |                         |                         |        |

| PGAGN                         | PGA Gain setting                  |                                                                              | 1,2,4,8,16,32,64,128    |                         |                         | V/V    |

|                               | RFI filter 3dB frequency          | Design guaranteed                                                            | —                       | 12.8                    | —                       | MHz    |

| V <sub>CMPGA</sub>            | Input common-mode voltage         |                                                                              | 0.4                     |                         | AVDD-0.6                | V      |

| <b>PERFORMANCE</b>            |                                   |                                                                              |                         |                         |                         |        |

|                               | Resolution                        |                                                                              | —                       | 20                      | —                       | bits   |

| ODR                           | Output data rate                  |                                                                              | 2                       | —                       | 2000                    | SPS    |

| V <sub>os</sub>               | Offset voltage                    | 20 bits resolution                                                           | —                       | 1                       | —                       | LSB    |

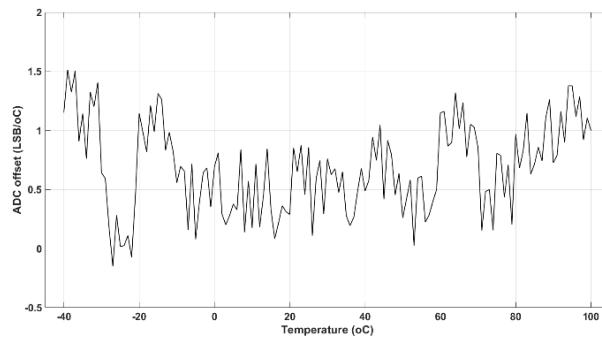

| V <sub>os,TC</sub>            | V <sub>os</sub> temperature drift |                                                                              | —                       | 1                       | —                       | LSB/°C |

| GE                            | Gain error                        |                                                                              | -1                      | ±0.5                    | +1                      | %      |

| CMRR                          | common-mode rejection ratio       | ODR=500SPS@60Hz                                                              | —                       | 80                      | —                       | dB     |

| PSRR                          | power-supply rejection ratio      | VDD to VSS                                                                   | —                       | 90                      | —                       | dB     |

| R <sub>PSW</sub>              | Sensor switch                     | I <sub>PSW</sub> =1mA                                                        | 8                       | 10                      | 12                      | Ω      |

| <b>ANALOG INPUTS/OUTPUTS</b>  |                                   |                                                                              |                         |                         |                         |        |

| V <sub>A<sub>IN</sub>x</sub>  | Absolute input voltage            | PGA enabled                                                                  | Note(1)                 |                         |                         |        |

|                               |                                   | PGA disabled                                                                 | AVSS-0.1                | —                       | AVDD+0.1                | V      |

| V <sub>IN</sub>               | Differential input voltage        | V <sub>IN</sub> =V <sub>A<sub>INP</sub></sub> – V <sub>A<sub>INN</sub></sub> | —                       | ±V <sub>REF</sub> /Gain | —                       | V      |

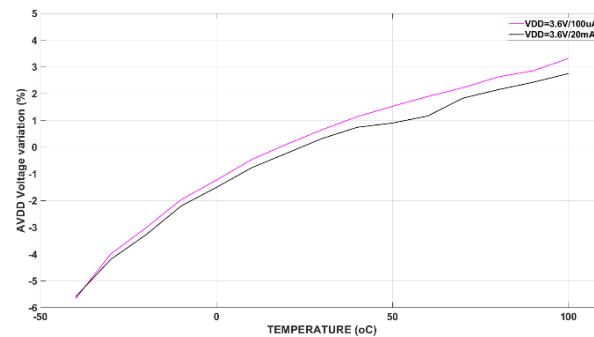

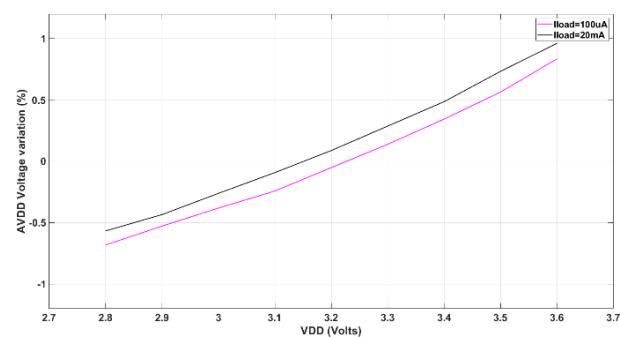

| V <sub>AVDD</sub>             | LDO output voltage                |                                                                              | 2.5                     | 2.8                     | 3.1                     | V      |

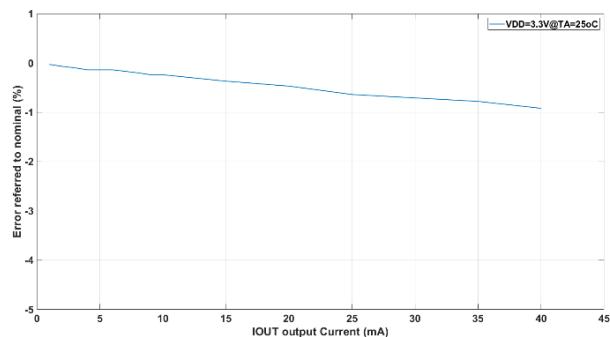

| L <sub>R<sub>AVDD</sub></sub> | AVDD load regulation              | I <sub>OUT</sub> =30mA                                                       | -1%                     | —                       | +1%                     | %      |

| V <sub>CVM</sub>              | Common-mode voltage               |                                                                              | -5%                     | AVDD/2                  | +5%                     | V      |

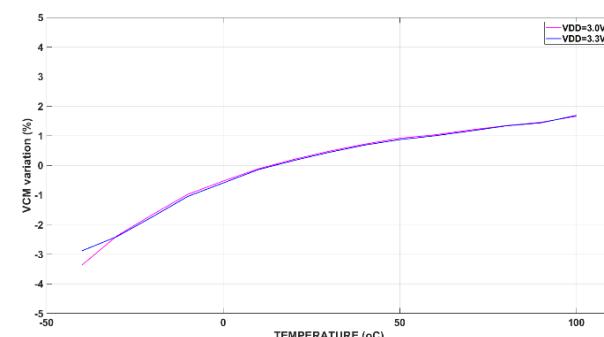

| T <sub>C<sub>VCM</sub></sub>  | VCM temperature coefficient       | AVDD=3.3V                                                                    | -4                      | —                       | +4                      | %      |

| <b>REFERENCE INPUTS</b>       |                                   |                                                                              |                         |                         |                         |        |

| V <sub>R<sub>IN</sub>X</sub>  | Differential reference voltage    | V <sub>REF</sub> =V <sub>REFP</sub> – V <sub>REFN</sub>                      | 0.3                     | —                       | AVDD-AVSS               | V      |

| V <sub>REFP</sub>             | Positive reference voltage        |                                                                              | V <sub>REFN</sub> + 0.3 | —                       | AVDD                    | V      |

| V <sub>REFN</sub>             | Negative reference voltage        |                                                                              | AVSS                    | —                       | V <sub>REFP</sub> - 0.3 | V      |

| VRGN                          | Reference voltage ratio           | VRGN[1:0]=00                                                                 | —                       | 1                       | —                       | V/V    |

|                               |                                   | VRGN[1:0]=01                                                                 | —                       | 0.5                     | —                       | V/V    |

|                                               |                                         |                        |        |          |          |     |

|-----------------------------------------------|-----------------------------------------|------------------------|--------|----------|----------|-----|

|                                               |                                         | VRGN[1:0]=10           | —      | 0.75     | —        | V/V |

|                                               |                                         | VRGN[1:0]=11           | —      | 0.25     | —        | V/V |

| VREF <sub>IN1</sub>                           | Internal VREF1                          | RxMUX[1:0]=10          | —      | 1.2      | —        | V   |

| VREF <sub>IN2</sub>                           | Internal VREF2                          | RxMUX[1:0]=11          | —      | 1.0      | —        | V   |

| <b>DC INPUT OFFSET</b>                        |                                         |                        |        |          |          |     |

| DCSET                                         | Input DC offset adjustment              | DCSET[2:0]=000         | —      | 0        | —        | V   |

|                                               |                                         | DCSET[2:0]=001         | —      | 1/12VREF | —        | V   |

|                                               |                                         | DCSET[2:0]=010         | —      | 2/12VREF | —        | V   |

|                                               |                                         | DCSET[2:0]=011         | —      | 3/12VREF | —        | V   |

|                                               |                                         | DCSET[2:0]=100         | —      | 4/12VREF | —        | V   |

|                                               |                                         | DCSET[2:0]=101         | —      | 5/12VREF | —        | V   |

|                                               |                                         | DCSET[2:0]=110         | —      | 6/12VREF | —        | V   |

|                                               |                                         | DCSET[2:0]=111         | —      | 7/12VREF | —        | V   |

| <b>IDAC CURRENT SOURCES (IDAC1, IDAC2)</b>    |                                         |                        |        |          |          |     |

| IDACx                                         | Current settings@V <sub>CM</sub> = 1.0V | IDACx[6:0]=0000000     | —      | 5        | —        | uA  |

|                                               |                                         | IDACx[6:0]=0000001     | —      | 10       | —        | uA  |

|                                               |                                         | IDACx[6:0]=0000010     | —      | 20       | —        | uA  |

|                                               |                                         | IDACx[6:0]=0000100     | —      | 40       | —        | uA  |

|                                               |                                         | IDACx[6:0]=0001000     | -1%    | 80       | +1%      | uA  |

|                                               |                                         | IDACx[6:0]=0010000     | —      | 160      | —        | uA  |

|                                               |                                         | IDACx[6:0]=0100000     | —      | 320      | —        | uA  |

|                                               |                                         | IDACx[6:0]=1000000     | —      | 700      | —        | uA  |

|                                               |                                         | IDACx[6:0]=1111111     | —      | 1200     | —        | uA  |

|                                               | Compliance voltage                      |                        | AVSS   | —        | AVDD-0.6 | V   |

| <b>BURN-OUT CURRENT</b>                       |                                         |                        |        |          |          |     |

| I <sub>BODP</sub>                             | Burn-out source current                 | VDD=3.3V               | 4      | 5        | 6        | uA  |

| I <sub>BODN</sub>                             | Burn-out sink current                   | VDD=3.3V               | 3.5    | 4.5      | 5.5      | uA  |

| <b>DIGITAL INPUTS/OUTPUTS (SDA, SCL, EOC)</b> |                                         |                        |        |          |          |     |

| V <sub>OL</sub>                               | Low-level output voltage                | I <sub>SINK</sub> =4mA | —      | —        | 0.4      | V   |

| V <sub>IL</sub>                               | Low-level input voltage                 | SDA, SCL               | 0.7VDD | —        | —        | V   |

| V <sub>IH</sub>                               | Low-level output voltage                | SDA, SCL               | —      | —        | 0.3VDD   | V   |

| I <sub>LEAK</sub>                             | Input leakage current                   | SDA, SCL               | —      | —        | 1        | uA  |

| <b>INTERNAL CLOCK OSCILLATOR</b>              |                                         |                        |        |          |          |     |

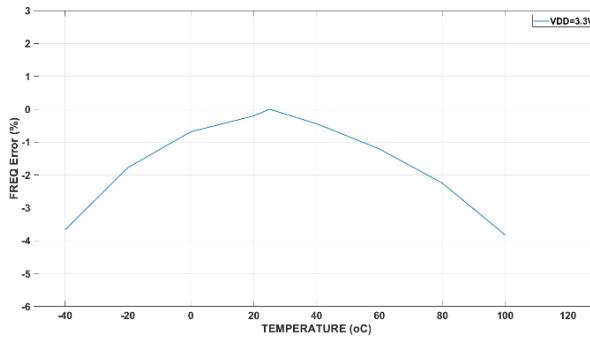

| F <sub>CLK</sub>                              | Master clock frequency                  | VDD=3.3V               | -1%    | 1.024    | +1%      | MHz |

| T <sub>SUP</sub>                              | Clock start-up time                     | VDD=3.3V               | 1      | —        | —        | ms  |

| <b>INTERNAL TEMPERATURE SENSOR</b> |                      |             |     |      |     |     |

|------------------------------------|----------------------|-------------|-----|------|-----|-----|

|                                    | Temperature accuracy | -40 to 85°C | —   | ± 3  | —   | °C  |

|                                    | Current consumption  |             | 28  | 32   | 36  | uA  |

| <b>SUPPLY VOLTAGE DETECTOR</b>     |                      |             |     |      |     |     |

|                                    | VDD DIVIDER          |             | 0.2 | 0.25 | 0.3 | V/V |

| <b>OPERATION TEMPERATURE</b>       |                      |             |     |      |     |     |

| T <sub>A</sub>                     | Ambient temperature  |             | -40 | —    | 85  | °C  |

## • MCU

Table. DC supply characteristics

| Symbol               | parameter                                         | Condition |                            |                | Typical | Max | Unit |

|----------------------|---------------------------------------------------|-----------|----------------------------|----------------|---------|-----|------|

| IDD(active mode)     | Peripheral clock on,code runs from Flash          | VDD=3.3V  | HSI clock source           | 4M             | 468     |     | µA   |

|                      |                                                   |           |                            | 8M             | 839     |     |      |

|                      |                                                   |           |                            | 16M            | 1575    |     |      |

|                      |                                                   |           |                            | 24M            | 2298    |     |      |

|                      | Peripheral clock off,code runs from Flash         | VDD=3.3V  | HSI clock source           | 4M             | 397     |     | µA   |

|                      |                                                   |           |                            | 8M             | 696     |     |      |

|                      |                                                   |           |                            | 16M            | 1291    |     |      |

|                      |                                                   |           |                            | 24M            | 1871    |     |      |

|                      | Peripheral clock on,code runs from Flash          | VDD=3.3V  | LSE 32.768KHz clock source | Ta=-40 to 25°C | 34      |     | µA   |

|                      | Peripheral clock off,code runs from Flash         | VDD=3.3V  | LSE 32.768KHz clock source | Ta=-40 to 25°C | 34      |     | µA   |

| IDD(sleep mode)      | Peripheral clock on                               | VDD=3.3V  | HSI clock source           | 4M             | 181     |     | µA   |

|                      |                                                   |           |                            | 8M             | 282     |     |      |

|                      |                                                   |           |                            | 16M            | 486     |     |      |

|                      |                                                   |           |                            | 24M            | 689     |     |      |

|                      | Peripheral clock off                              | VDD=3.3V  | HSI clock source           | 4M             | 122     |     | µA   |

|                      |                                                   |           |                            | 8M             | 166     |     |      |

|                      |                                                   |           |                            | 16M            | 252     |     |      |

|                      |                                                   |           |                            | 24M            | 338     |     |      |

|                      | Peripheral clock on                               | VDD =3.3V | LSE 32.768KHz clock source | Ta=-40 to 25°C | 26      |     | µA   |

|                      | Peripheral clock off                              | VDD =3.3V | LSE 32.768KHz clock source | Ta=-40 to 25°C | 25      |     | µA   |

|                      | Peripheral clock on                               | VDD =3.3V | HSE 32.768KHzclock source  | Ta=-40 to 25°C | 884     |     | µA   |

|                      | Peripheral clock off                              | VDD =3.3V | HSE 32.768KHzclock source  | Ta=-40 to 25°C | 534     |     | µA   |

| IDD(Deep sleep mode) | Peripheral clock off,exclude AWK, IWDG, LTIM, RTC | VDD =3.3V | LSE 32.768KHzclock source  | Ta=-40 to 25°C | 1.20    |     | µA   |

|                      | Peripheral clock off,exclude IWDG                 | VDD =3.3V | LSE 32.768KHzclock source  | Ta=-40 to 25°C | 1.20    |     | µA   |

| symbol | parameter                          | Condition |                                 |                | Typical | Max | Unit |

|--------|------------------------------------|-----------|---------------------------------|----------------|---------|-----|------|

|        | Peripheral clock off,exclude LPTIM | VDD =3.3V | LSE<br>32.768KHzclock<br>source | Ta=-40 to 25°C | 1.18    |     | µA   |

|        | Peripheral clock off,exclude RTC   | VDD =3.3V | LSE<br>32.768KHzclock<br>source | Ta=-40 to 25°C | 1.19    |     | µA   |

|        | Peripheral clock off               | VDD =3.3V | .                               | Ta=-40 to 25°C | 0.89    |     | µA   |

Table. Power-on/Power-down reset

| Symbol    | Parameter             | Min | Typical | Max | Unit |

|-----------|-----------------------|-----|---------|-----|------|

| $V_{POR}$ | POR voltage(power-up) | 2.2 | 2.25    | 2.3 | V    |

| $V_{BOR}$ | BOR voltage(brownout) |     |         |     |      |

Table. AC supply current characteristics

| Symbol    | Parameter                             | Condition                 | Min     | Max     | Unit |

|-----------|---------------------------------------|---------------------------|---------|---------|------|

| $V_{OH}$  | High level output source current      | Source 4 mA, VDD = 3.3 V  | VDD-0.2 |         | V    |

|           |                                       | Source 6 mA, VDD = 3.3 V  | VDD-0.3 |         |      |

| $V_{OL}$  | Low level output sink current         | sink 4 mA, VDD = 3.3 V    |         | VSS+0.2 | V    |

|           |                                       | sink 6 mA, VDD = 3.3 V    |         | VSS+0.3 |      |

| $V_{OHD}$ | High level output dual source current | Source 8 mA, VDD = 3.3 V  | VDD-0.2 |         | V    |

|           |                                       | Source 12 mA, VDD = 3.3 V | VDD-0.3 |         |      |

| $V_{OLD}$ | Low level output dual current sink    | sink 8 mA, VDD = 3.3 V    |         | VSS+0.2 | V    |

|           |                                       | sink 12 mA, VDD = 3.3 V   |         | VSS+0.3 |      |

Table. Port characteristic - PA, PB, PC, PD

| Symbol    | Parameter       | Condition | VDD         | Max | Unit |

|-----------|-----------------|-----------|-------------|-----|------|

| $I_{lkg}$ | leakage current | V         | 2.5V / 3.6V | ±50 | nA   |

Table. Port PA, PB, PC, PD

| Symbol         | Parameter                                        | Condition      | Min | Typical | Max | Unit |

|----------------|--------------------------------------------------|----------------|-----|---------|-----|------|

| $V_{IT+}$      | Positive Input Threshold Voltage                 | $VDD=2.5$      | 1.4 |         |     | V    |

|                |                                                  | $VDD=3.3$      | 1.8 |         |     | V    |

|                |                                                  | $VDD=3.6$      | 3   |         |     | V    |

| $V_{IT-}$      | Reverse Input Threshold Voltage                  | $VDD=2.5$      |     |         | 0.9 | V    |

|                |                                                  | $VDD=3.3$      |     |         | 1.3 | V    |

|                |                                                  | $VDD=3.6$      |     |         | 2.4 | V    |

| $V_{hys}$      | Input voltage hysteresis ( $V_{IT+} - V_{IT-}$ ) | $VDD=2.5$      |     | 0.5     |     | V    |

|                |                                                  | $VDD=3.3$      |     | 0.5     |     | V    |

|                |                                                  | $VDD=3.6$      |     | 0.6     |     | V    |

| $R_{pullhigh}$ | Pull-up resistor                                 | pull-up enable | 40  | 50      | 60  | Kohm |

| $C_{input}$    | input capacitance                                |                |     | 5       |     | pf   |

Table. Timer input sampling requirements

| Symbol      | Parameter             | Condition                                             | Min | Max             | Unit    |

|-------------|-----------------------|-------------------------------------------------------|-----|-----------------|---------|

| $T_{(int)}$ | external interrupt    | External trigger interrupt flag                       | 30  |                 | ns      |

| $T_{(cap)}$ | Timer capture time    | TIM1/2 capture pulse width $f_{systme} = 4MHz$        | 0.5 |                 | $\mu s$ |

| $f_{EXT}$   | Timer clock frequency | TIM1/2/10/11 External clock input $f_{systme} = 4MHz$ | 0   | $f_{TIMxCLK}/2$ | MHz     |

| $T_{(PCA)}$ | PCA clock frequency   | PCA External clock input $f_{systme} = 4MHz$          | 0   | $f_{PCACLK}/2$  | MHz     |

Table. Internal High Speed Oscillator (HSI)

| Symbol       | Parameter                     | Condition                                                        | Min  | Typical | Max  | Unit    |

|--------------|-------------------------------|------------------------------------------------------------------|------|---------|------|---------|

| $F_{MCLK}$   | Internal Oscillator Frequency |                                                                  | 4.0  | 16      | 24   | MHz     |

| $T_{Mstart}$ | build time                    | $F_{MCLK}=4MHz$                                                  | 2    | 2.4     | 4.7  | $\mu s$ |

|              |                               | $F_{MCLK}=8MHz$                                                  | 1.15 | 1.47    | 3.01 | $\mu s$ |

|              |                               | $F_{MCLK}=16MHz$                                                 | 1.04 | 1.31    | 2.74 | $\mu s$ |

|              |                               | $F_{MCLK}=24MHz$                                                 | 1.1  | 1.30    | 2.71 | $\mu s$ |

| $T_{MCLK}$   | current consumption           | $F_{MCLK}=4MHz$                                                  | 31   | 56      | 113  | $\mu A$ |

|              |                               | $F_{MCLK}=8MHz$                                                  | 40   | 72      | 151  | $\mu A$ |

|              |                               | $F_{MCLK}=16MHz$                                                 | 71   | 143     | 298  | $\mu A$ |

|              |                               | $F_{MCLK}=24MHz$                                                 | 93   | 196     | 383  | $\mu A$ |

| $DC_{MCLK}$  | duty cycle                    |                                                                  | 45   | 50      | 55   | %       |

| $D_{evM}$    | frequency deviation           | $VDD = 2.5V \sim 3.6V$<br>$TAMP = -40^{\circ}C \sim 85^{\circ}C$ | -2.5 | $\pm 1$ | +2.5 | %       |

|              |                               | $VDD = 2.5V \sim 3.6V$<br>$TAMP = -40^{\circ}C \sim 50^{\circ}C$ | -2.0 | $\pm 1$ | +2.0 | %       |

Table. Internal low-speed oscillator (LSI)

| Symbol       | Parameter                     | Condition                                | Min           | Typical        | Max           | Unit    |

|--------------|-------------------------------|------------------------------------------|---------------|----------------|---------------|---------|

| $F_{ACLK}$   | Internal Oscillator Frequency |                                          | 37.8<br>32.21 | 38.4<br>32.766 | 38.7<br>33.26 | KHz     |

| $T_{Astart}$ | build time                    |                                          | 50            | 75             | 150           | $\mu s$ |

| $I_{ACLK}$   | current consumption           |                                          | 0.2           | 0.25           | 0.35          | $\mu A$ |

| $DC_{ACLK}$  | duty cycle                    |                                          | 45            | 50             | 55            | %       |

| $D_{evA}$    | frequency deviation           | VDD = 2.5V ~ 3.6V<br>TAMP = -40°C ~ 85°C | -2.0          | $\pm 1$        | +2.0          | %       |

|              |                               | VDD = 2.5V ~ 3.6V<br>TAMP = -40°C ~ 50°C | -1.5          | $\pm 1$        | +1.5          | %       |

Table. External low-speed crystal (LSE)

| Symbol         | Parameter             | Condition                                          | Min   | Typical           | Max   | Unit |

|----------------|-----------------------|----------------------------------------------------|-------|-------------------|-------|------|

| $F_{SCLK}$     | Crystal frequency     |                                                    | 32.75 | 32.768            | 32.78 | KHz  |

| $ESR_{SCLK}$   | Equivalent resistance |                                                    | 40    | 65                | 85    | KOhm |

| $C_{SCLK}$     | Crystal external load |                                                    |       | 12 <sup>(2)</sup> |       | pF   |

| $I_{dd}^{(1)}$ | electric current      | ESR=65kOhm<br>$C_{SCLK}=12pF$                      | 200   | 250               | 350   | nA   |

| $DC_{SCLK}$    | duty cycle            |                                                    | 40    | 50                | 60    | %    |

| $T_{start}$    | build time            | ESR=65kOhm<br>$C_{SCLK}=12pF$<br>40%-60%duty cycle |       | 2                 |       | s    |

Table. External High Speed Crystal (HSE)

| Symbol       | Parameter             | Condition                                     | Min | Typical | Max  | Unit    |

|--------------|-----------------------|-----------------------------------------------|-----|---------|------|---------|

| $F_{FCLK}$   | Crystal frequency     |                                               | 4   | 16      | 24   | MHz     |

| $ESR_{FCLK}$ | Equivalent resistance |                                               | 30  | 60      | 1500 | Ohm     |

| $C_{FCLK}$   | Crystal external load |                                               |     | 12      |      | pF      |

| $I_{dd}$     | electric current      | 24MHz Crystal<br>ESR=30Ohm<br>$C_{FCLK}=12pF$ |     | 300     |      | $\mu A$ |

| $DC_{FCLK}$  | duty cycle            |                                               | 40  | 50      | 60   | %       |

| $T_{start}$  | build time            | 4M~24MHz                                      |     | 250     |      | $\mu s$ |

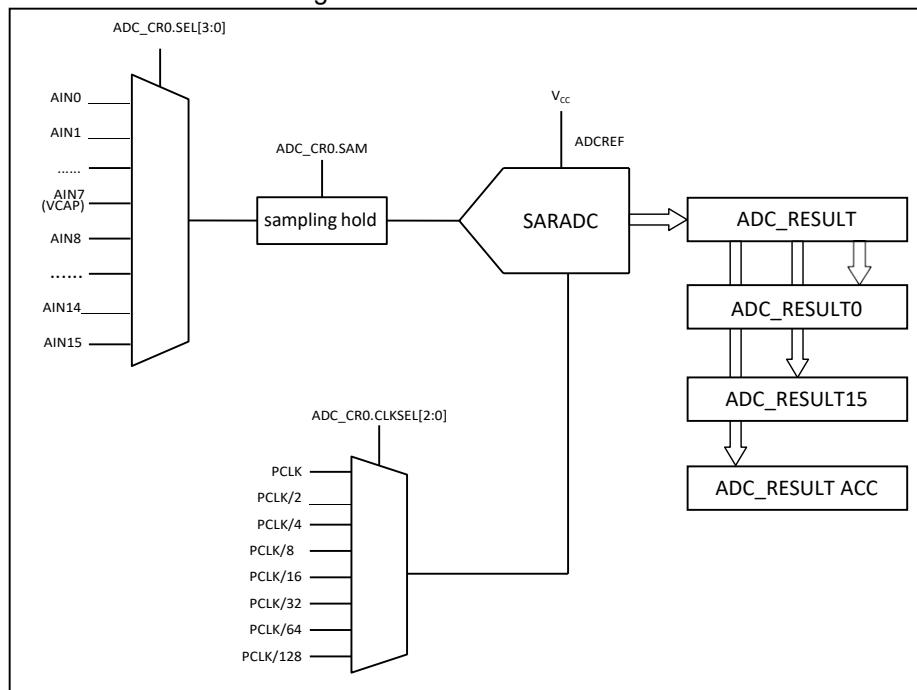

Figure 4. 12 bit A/D Converter

Table. 12 bit A/D Converter

| Symbol         | Parameter                  | Condition    | Min  | Typical | Max   | Unit    |

|----------------|----------------------------|--------------|------|---------|-------|---------|

| $V_{ADCIN}$    | Input voltage range        | single ended | 0    |         | $VDD$ | V       |

| $V_{REF}$      | reference voltage          |              |      | $VDD$   |       | V       |

| $I_{ADC}$      |                            |              | 0.65 | 0.9     | 1.23  | mA      |

| $C_{ADCIN}$    | input resistance           |              | 3.5  | 4       | 4.5   | pF      |

| $F_{ADCCLK}$   | Clock frequency            |              | 0.5  | 4       | 16    | MHz     |

| $T_{ADCSTART}$ | Bias Current Settling Time |              | 2    | 3       | 4     | $\mu s$ |

| $T_{ADCCONV}$  | conversion time            |              | 16   | 16      | 20    | cycle   |

| $ENOB$         |                            |              | 10   | 10.5    | 11    | Bit     |

| DNL            | differential nonlinearity  |              | -1.5 | $\pm 1$ | 1.5   | LSB     |

| INL            | integral nonlinearity      |              | -2   | $\pm 1$ | 2     | LSB     |

| $E_o$          | bias error                 |              | -2   | $\pm 1$ | 2     | LSB     |

| $E_g$          | gain error                 |              | -2   | $\pm 1$ | 2     | LSB     |

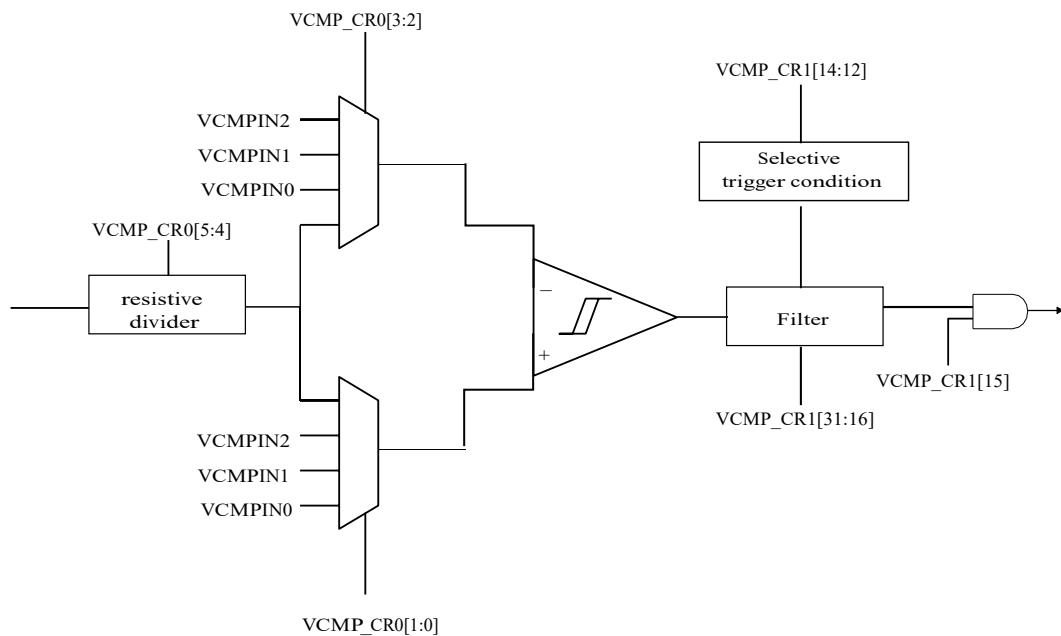

Figure 5. Analog Voltage Comparator

Table. Analog Voltage Comparator

| Symbol         | Parameter               | Min | Typical | Max | Unit    |

|----------------|-------------------------|-----|---------|-----|---------|

| $V_{in}$       | Input voltage range     | 0   |         | 3.6 | V       |

| $V_{incom}$    | Input Common Mode Range | 0   |         | 3.6 | V       |

| $V_{offset}$   | input bias              | -10 | $\pm 5$ | +10 | mV      |

| $I_{comp}$     | comparator current      |     | 12      |     | $\mu A$ |

| $T_{response}$ | Comparator Response     |     | 5       |     | $\mu s$ |

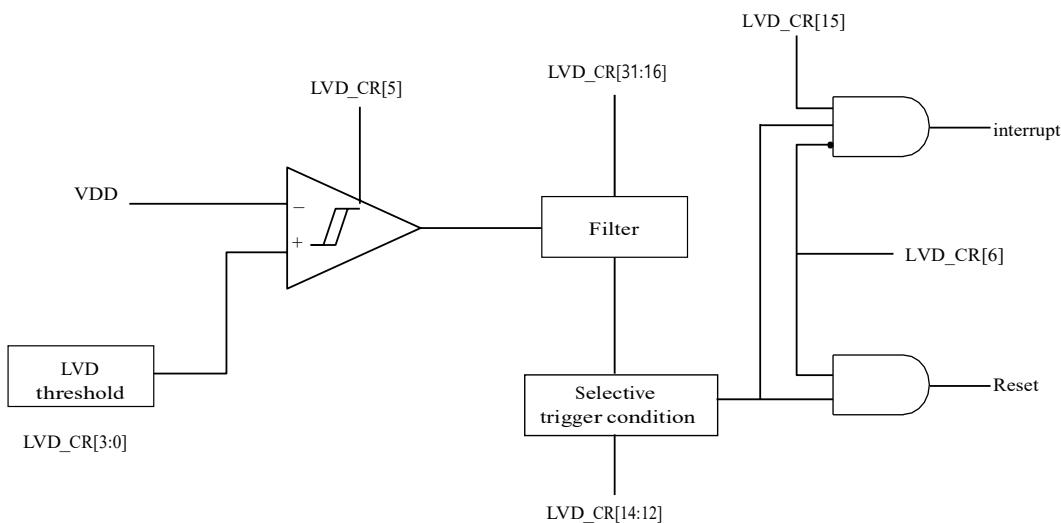

Figure 6. Low voltage detection

Table. Low voltage detection characteristics

| Symbol         | Parameter                                                           | Condition                                                                                                                                                                                                                                                                                                                                                    | Min | Typical                                                                                                                               | Max      | Unit    |   |

|----------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------|----------|---------|---|

| $V_{level}$    | VDD detectable Threshold (TSSOP20, QFN20, SOP20)                    | LVD_CR[3:0] = 0000<br>LVD_CR[3:0] = 0001<br>LVD_CR[3:0] = 0010<br>LVD_CR[3:0] = 0011<br>LVD_CR[3:0] = 0100<br>LVD_CR[3:0] = 0101<br>LVD_CR[3:0] = 0110<br>LVD_CR[3:0] = 0111                                                                                                                                                                                 |     | 4.4<br>4.0<br>3.6<br>3.3<br>3.1<br>2.9<br>2.7<br>2.5                                                                                  | Typ -0.1 | Typ+0.1 | V |

| $V_{level}$    | VDD detectable Threshold (LQFP32, QFN32)                            | LVD_CR[3:0] = 0000<br>LVD_CR[3:0] = 0001<br>LVD_CR[3:0] = 0010<br>LVD_CR[3:0] = 0011<br>LVD_CR[3:0] = 0100<br>LVD_CR[3:0] = 0101<br>LVD_CR[3:0] = 0110<br>LVD_CR[3:0] = 0111<br>LVD_CR[3:0] = 1000<br>LVD_CR[3:0] = 1001<br>LVD_CR[3:0] = 1010<br>LVD_CR[3:0] = 1011<br>LVD_CR[3:0] = 1100<br>LVD_CR[3:0] = 1101<br>LVD_CR[3:0] = 1110<br>LVD_CR[3:0] = 1111 |     | 4.6<br>4.4<br>4.2<br>4.0<br>3.8<br>3.6<br>3.4<br>3.2<br>3.0<br>2.8<br>2.6<br>Reserved<br>Reserved<br>Reserved<br>Reserved<br>Reserved | Typ-0.1  | Typ+0.1 | V |

| $I_{comp}$     | Detection current                                                   |                                                                                                                                                                                                                                                                                                                                                              | 1   | 1.5                                                                                                                                   | 2        | $\mu A$ |   |

| $T_{response}$ | VDD response time of monitor after falling below or above threshold |                                                                                                                                                                                                                                                                                                                                                              | 30  | 50                                                                                                                                    | 80       | $\mu s$ |   |

| $T_{setup}$    | Monitor build time                                                  |                                                                                                                                                                                                                                                                                                                                                              | 3   | 5                                                                                                                                     | 10       | $\mu s$ |   |

Table. Flash memory characteristics

| Symbol                    | Parameter        | Min | Typical | Max | Unit          |

|---------------------------|------------------|-----|---------|-----|---------------|

| $EC_{\text{flash}}$       | block erase      | 20K |         |     | one           |

| $RET_{\text{flash}}$      | data retention   | 20  |         |     | year          |

| $T_{\text{prog}}$         | byte programming |     |         | 20  | $\mu\text{s}$ |

| $T_{\text{Sector-erase}}$ | block erase      |     |         | 8   | ms            |

| $T_{\text{Chip-erase}}$   | Full Chip Erase  | 20  |         | 40  | ms            |

Table. Low power mode wakeup

| Symbol              | Parameter               | Condition | Min  | Typical | Max  | Unit          |

|---------------------|-------------------------|-----------|------|---------|------|---------------|

| $T_{\text{wakeup}}$ | Deep Sleep to operation | 4M        | 11.8 | 12.5    | 12.8 | $\mu\text{s}$ |

|                     |                         | 8M        | 11.3 | 11.6    | 12.5 |               |

|                     |                         | 16M       | 11.2 | 11.4    | 12.0 |               |

|                     |                         | 24M       | 10.5 | 11.3    | 11.8 |               |

## Description

### • Analog Front End (AFE)

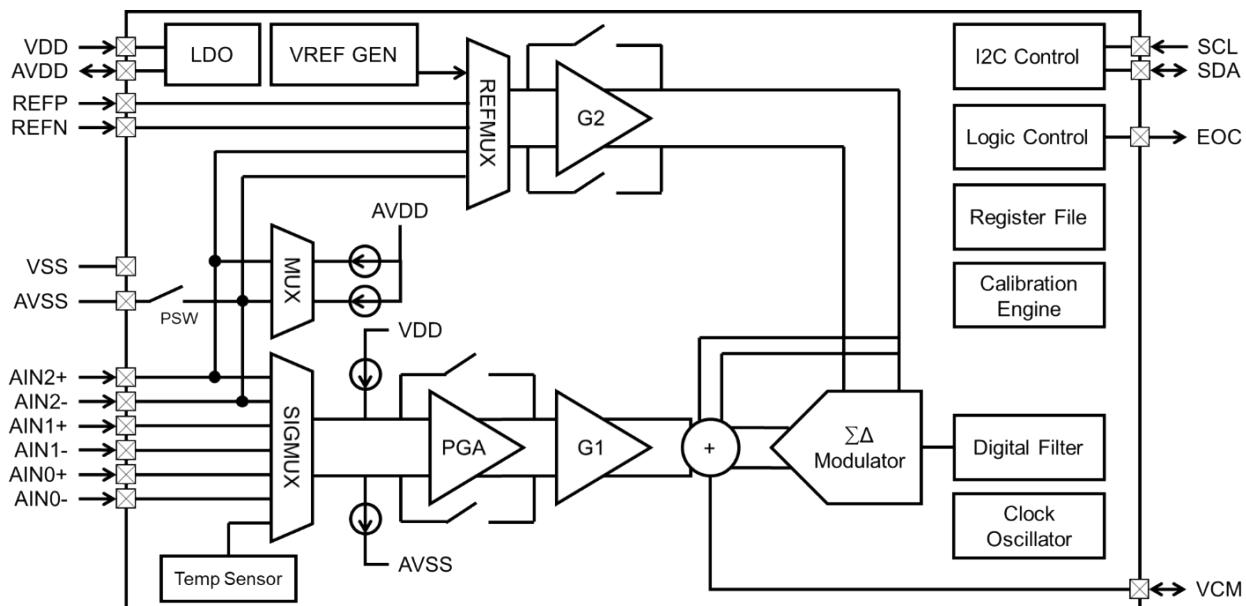

The FE82160 has a 3-channel, low noise, ultra-low power 20-bit sigma-delta analog-to-digital data converter for high precision measurement applications. Embedding with on-chip temperature sensor, supply voltage detector, the device can monitor environment conditions dynamically for self-data calibration. Operating with internal calibrated precisely 1MHz clock oscillators, no extra external crystal oscillator needed for BOM and area saved.

The FE82160 builds up 2-stage programmable PGA gain amplifiers. The gain of ach amplifier could be configured independently. The 1<sup>st</sup>-stage gain could program from x1 to x128 and the 2<sup>nd</sup> stage could program from x1 to x16. User could allocate the gain in each stage to acquire the low-noise and supreme stable analog signals.

The devices contain 3 external independent differential input signals, and 2 external independent reference voltages. Two on-chip IDACs on-chip could source independent currents to stimulate external sensor devices to generate electricalsignals.

The FE82160 is an oversampling sigma-delta data converter with a decimation filter to decimate the output data from modulator. The configurable output data rate from 4Hz to 1KHz, tradeoff the resolution and conversion speed in applications requirements.

The parts operate with a power supply from 2.5V to 3.6V. The data transacts through standard I2C digital interface with MCU. The device consumes 300uA ultra-low current consumption in typical.

### ➤ System Description

The AFE is a low-noise, low power 20-bit  $\Sigma\Delta$  ADC that offers many integrated features to reduce system BOM cost and component counts in measuring sensor signals. The device has 2 conversion modes, one-shot conversion and continuous conversion mode. Data can be read at any time if EOC signal is interrupted, it could avoid to access the corruption data and always reflect the most recently completed conversion.

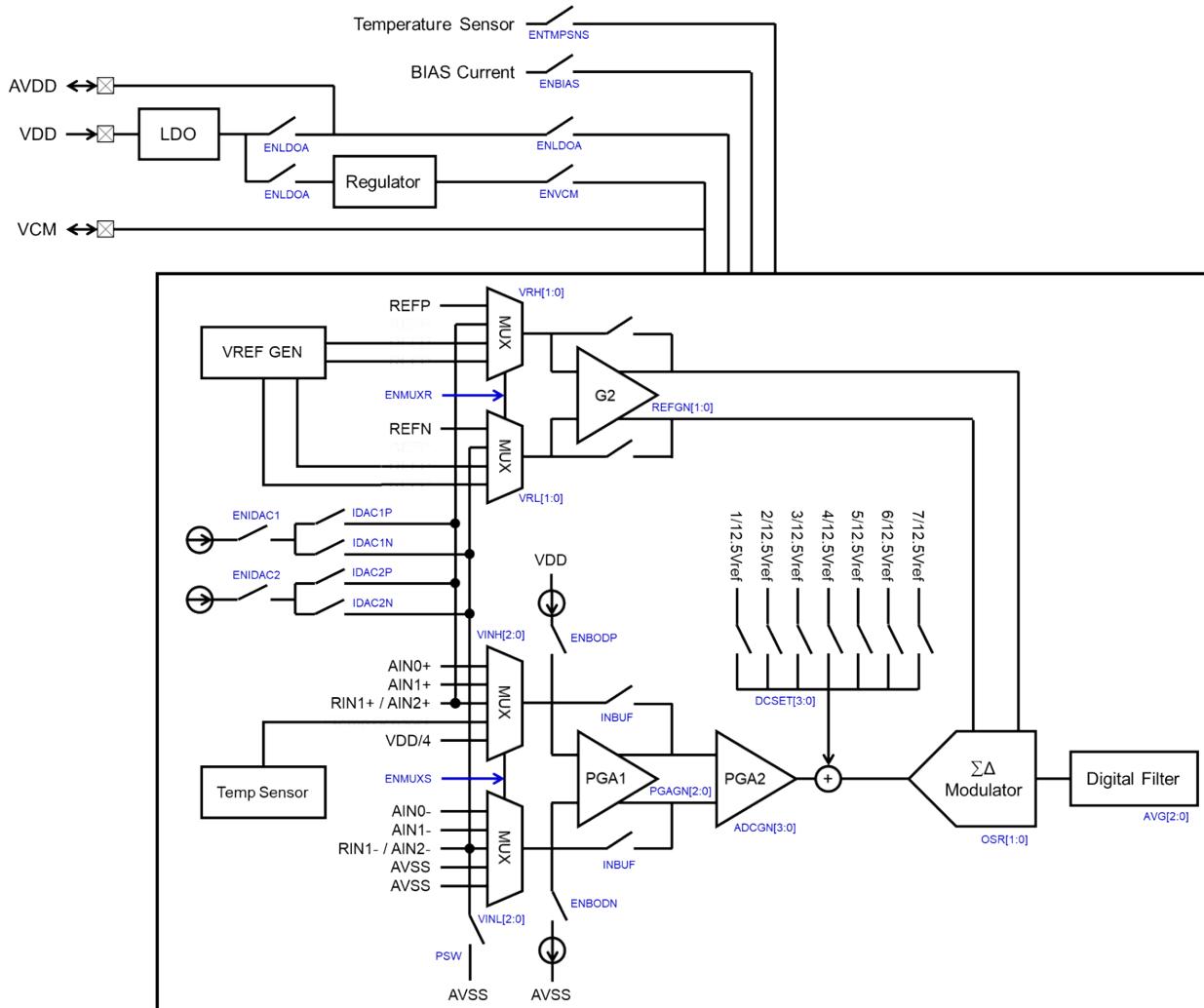

Figure 7. Function Block Diagram of AFE

### ➤ **Power Supplies**

The AFE has 2 independent power supply pins, AVDD and DVDD. AVDD powers the internal analog linear regulator. The regulator supplies a regulated voltage to critical analog section of the device contains programmable gain amplifier and delta-sigma data converters. AVDD is referenced to AVSS and the maximum voltage rating is 4.0V.

DVDD powers the digital section the AFE including clock generator and digital processing circuits. After the supply voltage is stable, internal power on sequence will reset all the circuits into an initial condition and register map will return to default value. The DVDD is reference to DVSS and the maximum voltage rating is 4.0V as same as AVDD.

### ➤ **Reset**

There is no external hardwire reset pin in AFE. In situations where interface synchronization is lost, user could power on/off the devices to reset the register data into default values and abort any operation conditions. User can re-command the register configurations after power on.

The AFE supports software reset where user could reset the device by a fixed I2C data pattern. The device responds to the two-wire general call address (0000 000) if the LSB bit is 0. The device acknowledges the general call address and responds to commands in the 2<sup>nd</sup> byte. If the 2<sup>nd</sup> byte is 0000 0110, the AFE resets the internal registers to the power-up reset values.

### ➤ **Power Supply Monitors**

Regard to monitor the supply voltage quality, the AFE build-in supply voltage detection function. The AVDD voltage will be attenuated internally by one-fourth and applied to data converter. The function is useful because of voltage variation from power supply could be monitored.

After initial power up sequence, the supply voltage will ramp up and stable in a short period of time, the internal power on reset will reset the digital register file into default value.

### ➤ **Digital Communication Interface and Data Ready Indicator**

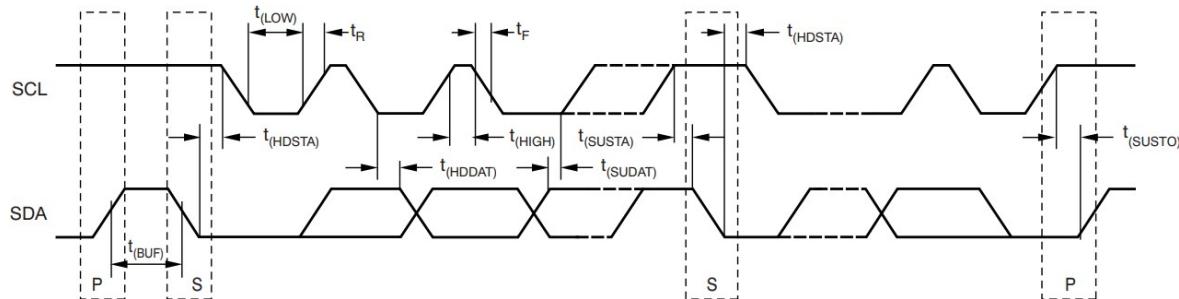

The AFE has a 2-wire serial interface that is compatible with standard I2C specification. It is operated as a slave device where a controller or master device could access the register data through I2C specified timing patterns. Connections to the bus are made through the open-drain I/O line SDA and SCL input pin. External pull-up resistor is needed for each of the two terminals. There are Schmitt triggers at SDA/SCL input signal chain to minimize the effects of signal fluctuations from harsh environment which couples noisy signals on data bus. The AFE supports the I2C transmission protocol up to 1MHz clock frequency of fast mode.

### ➤ **Bus Fault Timeout**

The AFE supports SMBus timeout feature. If the host holds the SCL pin in "L" more than 16ms(typ.) between a START and STOP condition, the AFE would reset its internal state machine to prevent a system bus hang-up. This feature is turned on by default and release SDA and waits for a START condition.

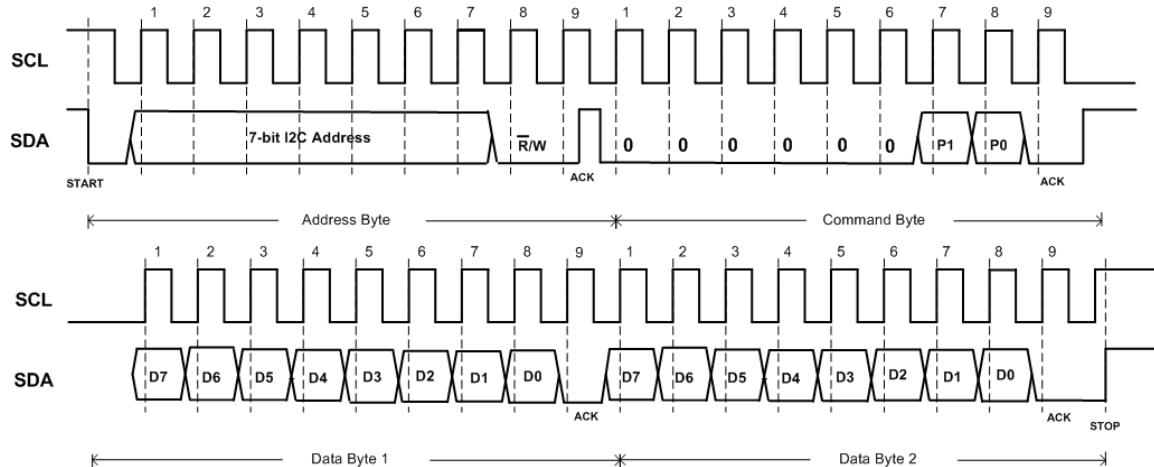

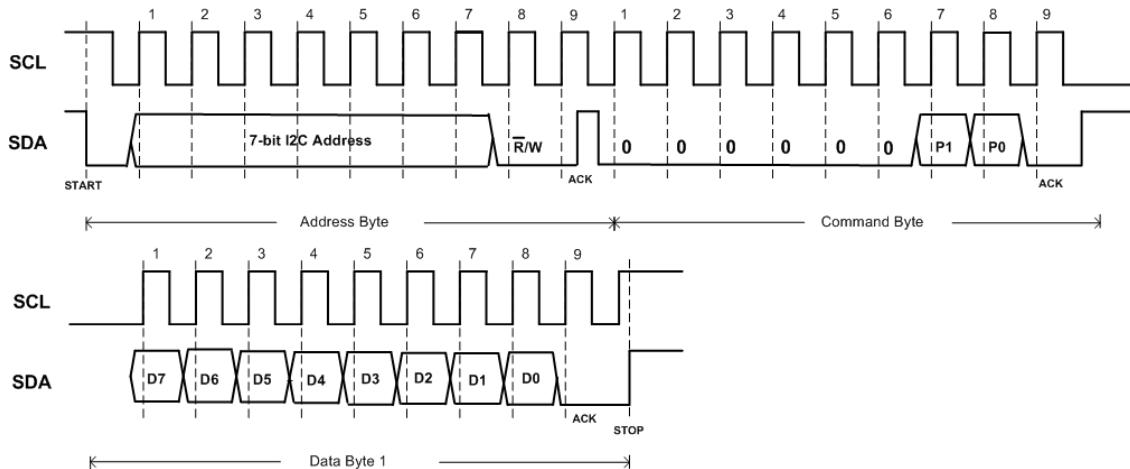

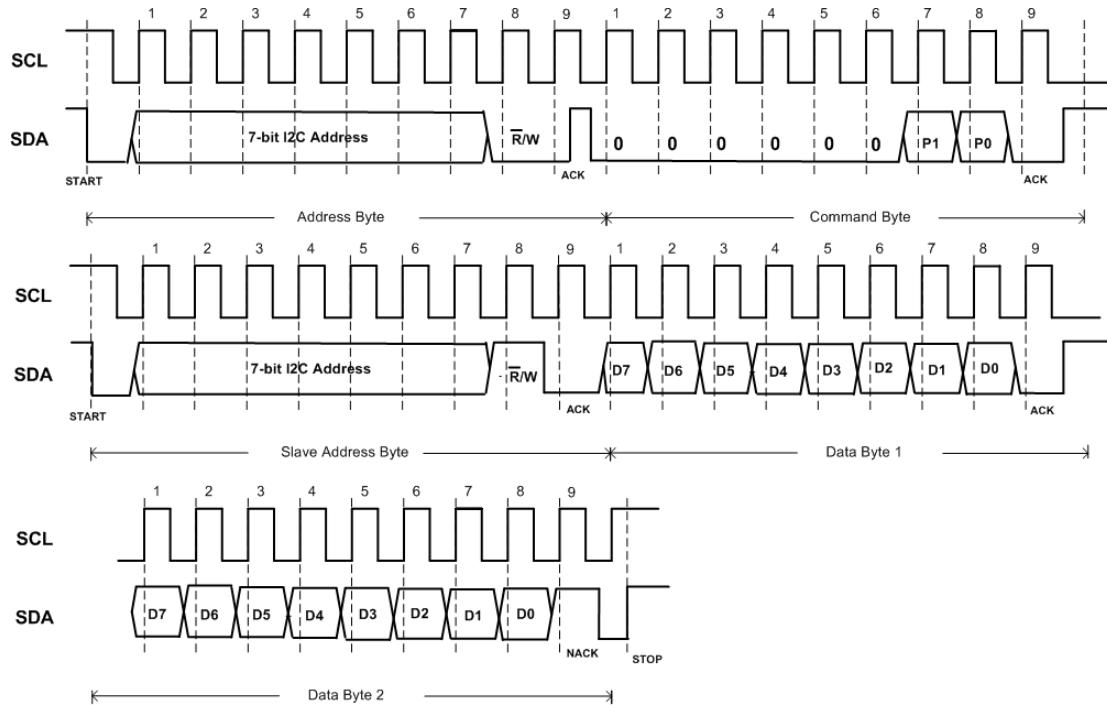

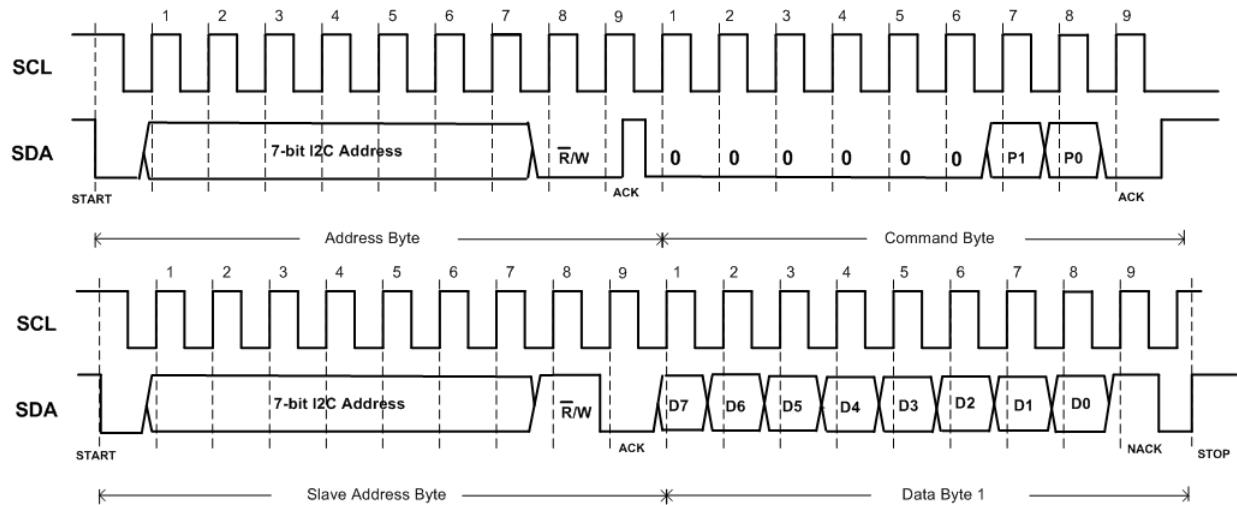

➤ I2C Digital Communication Timing Diagrams

| SYMBOL             | CONDITION                                 | MIN  | MAX | UNIT |

|--------------------|-------------------------------------------|------|-----|------|

| $f_{SCL}$          | SCL operating frequency                   | 2.5  | —   | us   |

| $t_{BUF}$          | Bus free time between STOP and START      | 1.3  | —   | us   |

| $t_{HDSTA}$        | Hold time after repeated START condition. | 600  | —   | ns   |

| $t_{SUSTA}$        | Repeated START condition setup time       | 600  | —   | ns   |

| $t_{SUSTO}$        | STOP condition setup time                 | 600  | —   | ns   |

| $t_{HDDAT}$        | Data hold time (*2)                       | 0    | —   | ns   |

| $t_{HSUDAT}$       | Data setup time                           | 100  | —   | ns   |

| $t_{LOW}$          | SCL clock low period                      | 1300 | —   | ns   |

| $t_{HIGH}$         | SCL clock high period                     | 600  | —   | ns   |

| $t_{VDAT}$         | Data valid time (*3)                      | —    | 900 | ns   |

| $t_{FDDA}$         | Data fall time                            | —    | 300 | ns   |

| $t_R$              | Clock rise time                           | —    | 300 | ns   |

| $t_F$              | Clock fall time                           | —    | 300 | ns   |

| Time out           | Clock fall time                           | 100  | —   | ms   |

| $t_{RCClock/data}$ | rise time for SCL=100KHz                  | —    | 1   | us   |

(\*1) The host and device have the same VDD voltage. The voltages are based on statistical analysis of samples tested during initial release.

(\*2) The maximum  $t_{HDDAT}$  can be 0.9us for fast mode, and is less than the maximum  $t_{VDAT}$  by a transition time.

(\*3)  $t_{VDAT}$ =time for data signal from SCL LOW to SDA output (HIGH to LOW, depending on which is worst).  $=$ time for data signal from SCL LOW to SDA output (HIGH to LOW, depending on which is worse).

Figure 8. I2C Timing

## ➤ Slave Address

To communicate with the AFE, the master device must first address devices through a 7-bit device address, a direction bit indicating the intent of executing a read or write operation.

## Timing Diagram

Figure 9. Two-wire timing diagram for Write Two Bytes format

Figure 10. Two-wire timing diagram for Write Single Byte format

Figure 11. Two-wire timing diagram for Read Two Bytes format

Figure 12. Two-wire timing diagram for Read Single Byte format

### ➤ **Register File**

The AFE build-in register files which can be configured to control the functions of analog front end. After powering up, the internal power on reset circuit will clear the registerdata into default value.

### ➤ **Channel Multiplexer Configuration**

AFE is 3 channels multiplexed data acquisition system utilized in industrial process control, portable medical devices, and automated test equipment need increased channel density where the user can measure the signals from multipole sensors, monitor and scan many input channels into a single sigma-delta ADC. The input multiplexer selects the signalfor measurement which could save PCB space, power and total system cost. The sigma-delta data converter is conventionally monotonic and uses integrated modulator for oversampling and digital decimation filtering that requires a internal clock source to synchronize all the functionality circuit blocks, resulting in a nonzero cycle latency. The multiplexer input faces limited bandwidth, settling time and input range which will degradethe system performance requiring to be designed carefully.

Since sigma-delta data converter is an oversampling analog input, the transition band ofanti-aliasing filter could be greatly simplified rather than brick-wall stop band filter in Nyquist-rate data converters. In most applications, aa simple single-pole RC filter is required for easy implementation.

The AFE has 3 differential analog input channels. The analog input signals are connected to internal programmable gain amplifier when the devices are operated in buffered mode. The unbuffered mode could be configured by register, the input channels connect to 2<sup>nd</sup> gain stage and feed through the sigma-delta modulator directly. By unknownor higher source impedance, the input channel should set to using buffer mode where the input signals acquires by a high impedance input stage. Therefore, the AFE can tolerate any signal source impedances which connect to external resistive-type sensors directly. User could enable buffered mode to set the INBUF=1. It should be noted that the input common mode range of buffer mode between AVSS+100mV to AVDD-1V.

When INBUF=0, the devices operate in unbuffered mode. User can configure the ADCGN to setup the 2<sup>nd</sup> gain stage to amplify the input signals without buffer. If the input source impedance is low enough compared to input impedance of sigma-delta modulator, it will notresult in much gain error on data converter output.

The AFE can be configured with gain equals to 1, 2, 4, 8 or 16 when it is operated inunbuffered mode. The absolute input voltage in unbuffered mode is restricted between AVSS-30mV to AVDD+30mV.Because no buffer circuits enabled during unbuffered mode, the power consumption could be minimized in data conversion.

### ➤ **Instrumentation Amplifier**

There is a programmable gain amplifier in front of sigma-delta modulator which could be used as an input analog buffer. User could configure the INBUF bit in register to enable the PGA amplifier. If the INBUF=1, the amplifier will active, and the amplifier will dis-active when INBUF=0. The PGA amplifier will be active automatically as the gain setting greater than 1. If the gain setting is equal to 1, user could configure to enable the buffer or not to adapt the input source connections. Although its wide input dynamic range of PGA and analog-to-digital converter, it is necessary to ensure that the headroom required for correct operation is met with gain configuration.

When the PGA amplifier is enabled, the input channel multiplexer will apply to input of the instrumentation amplifier. The low-noise programmable gain amplifier can amplify small amplitude signals to be gained while still maintaining excellent noise performance. The input gain in buffered mode could be set by 1, 2, 4, 8, 16, 32, 64 and up to 128 in the configuration register. For example, with an internal 1.2V reference voltage, the unipolar input range is from 1.2V and the bipolar range is from  $\pm 1.2V$ .

If the AFE is operated with external reference that has a value equal to AVDD, the analog input signal must be limited to 90% of VREF/PGAGN[2:0] when the programmable gain amplifier is enabled.

### ➤ **ADC Configuration**

The AFE are low noise, low power analog-to-digital data converter that incorporate a sigma-delta modulator, programmable instrumentation amplifier, and on-chip digital decimation filter intended for the measurement of low-frequency signals such as those in RTD, thermocouple, thermopile, pressure transducer and scales.

AFE allocates 3 input channels that can be buffered or unbuffered. User could adapt to different application from input source impedance to configure the buffer on/off. The input buffer incorporates with programmable gain stage to amplify low-level sensor input signals. In addition to the input gain stage configuration, the reference voltage of sigma-delta data converter could be configured also. If the full-scale of input signal after PGA amplifier stage is far below the default reference voltage, user could setup the gain of reference by x1, x3/4, x1/2 and x1/4 referred to analog input voltage.

There is programmable input DC offset voltage setup if the analog input voltage is not equally equipped in full-scale input dynamic range. Designer could configure the DCSET[2:0] which could adjust the input DC level by 1/12VREF to 7/12VREF from analog input voltage.

Upon the input offset voltage from sensors, the input of the sigma-delta modulator has a system chopper switch to remove the system offset effect. User could average output data from toggling input chopper switch to have an offset-free output.

The output data rate of the AFE is user programmable. The allowable update rates along with different settling times could be configured by oversampling ratio register.

Normal mode signal bandwidth noise rejection is the major function of the digital filter. If user would like to immune 50Hz/60Hz power buzz, it could be implemented by placing the frequency response of the digital filter with output notches at 50Hz or 60Hz.

### ➤ **Calibration**

The AFE will go through factory calibrated flow during manufacturing and circuit testing, user could implement the measurements without user calibration. If some the measurement system suffers from higher input impedance mismatch or system offset from temperature drift or environment changing, the AFE reserves a user-calibrated registers to remove systematic dc errors. It means that the devices have internal zero-scale calibration, internal gain error calibration, system zero-scale calibration and system gain error calibration, which effectively reduce the offset error and gain error to the optimized measurement performance.

During an internal offset error and gain error calibration, the input multiplexer and are connected internally to the ADC input pins. However, a system calibration should apply the input voltages on the analog input pins before systematic calibration is initiated.

A calibration should be treated as a data converter operation. After each data conversion, the output data of

---

digital filtering is scaled using the ADC calibration registers before beingwritten to the data register. The offset calibration coefficient is subtracted from the result prior to multiplication by the full-scale coefficient. The EOC pin determine the end of calibration via a polling sequence or an interrupt-driven routine.

#### ➤ **IDAC Excitation Current Sources for Sensor Stimulation**

The devices build in dual matched excitation current output, it expresses as the current DAC output (IDAC) in datasheet. The IDAC constant current sources that can be programmed to equal 10uA, 50uA and up to 1.5mA with 7 steps by register setting. Both excited source currents from the AVDD are directed topins which are combo-function pin configuration with analog input (AIN2+ and AIN2-) and reference voltage input pins (RIN1+and RIN1-). The IDAC current sources can be used to stimulate external resistive bridge, thermistor or RTD sensors.

#### ➤ **Reference Signal Configuration**

The AFE has embedded a 1.2V reference supply. The reference voltage of sigma-delta modulator can be applied from internal bandgap reference or external reference input. For external references, the sigma-delta modulator has a fully differential input capability for the channel. The RIN0 is a dedicated differential external reference inputchannel and another reference input channel, RIN1, is a combo function with analog input channel AIN2. The reference sources of the AFE can be configured by internal register. User can select any external voltage reference source by configuring the referenceinput buffer to get the optimizing performance. When the internal reference voltage is selected, it is preferred to connect the external reference pins to analog ground to protect from noise coupling on multiplexer.

The reference inputs can be configured in buffered or unbuffered by VRBUF bit in register. When VRBUF=0, the reference input voltage will bypass the internal buffer and connect to switched-capacitor circuits in data modulator. If VRBUF=1, the reference input will buffer byinternal amplifier to immune the gain error result from the excessive RC source impedancemismatch. The common-mode range for the differential inputs is from AVSS to AVDD-1V.

In application where the excitation current for the external sensor on the analog inputs alsodrive the reference voltage by ratio-metric. The steering current error will be cancelled by such connection architecture.

Using external reference resistor of reference voltage generation, it is important to considerusing a lower temperature coefficient external resistor with higher accuracy and a better temperature drift performance.

#### ➤ **Clock Oscillator**

The internal oscillator runs at 1MHz which provides the master clock source of digital circuitand ADC. The AD6110A default clock source is specified with n factory-trimmed accuracy for  $\pm 3\%$ .

There are options for the internal oscillator to divide into different clock sources through clock generator. The output frequency of configurable clock generator could dynamicallyprogram the digital operation clock and ADC data rate.