November 2014

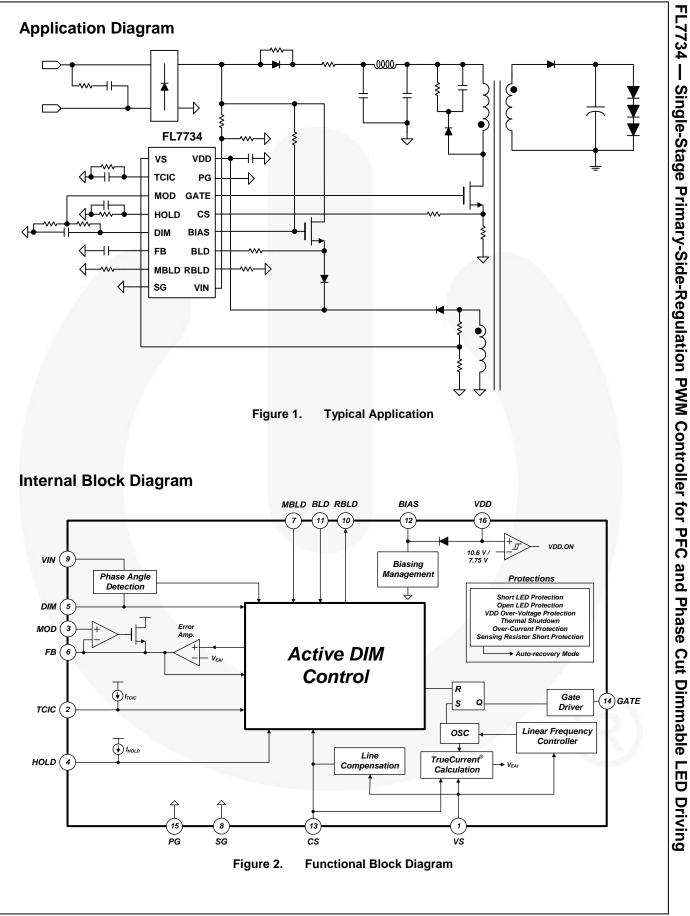

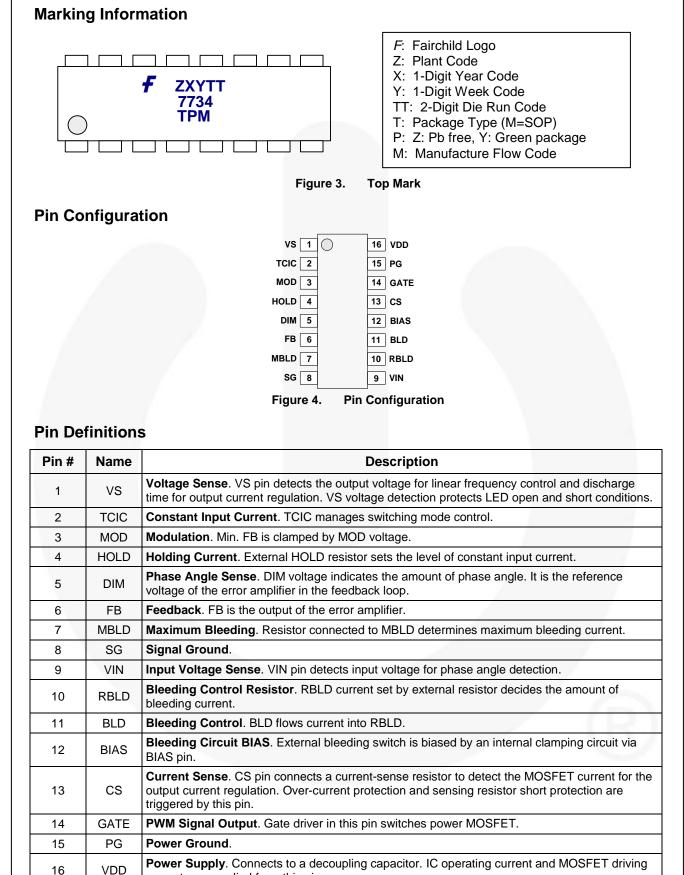

# FL7734 Single-Stage Primary-Side-Regulation PWM Controller for PFC and Phase Cut Dimmable LED Driving

#### Features

- Excellent Dimmer Compatibility by Active Dimming Control

- Programmable Dimming Curve and Input Current Management

- Constant LED Current Regulation in Large Phase Angle Range

- Cost-Effective Solution without Input Bulk Capacitor and Feedback Circuitry

- Accurate Constant-Current (CC) Control, Independent on Line Voltage, Output Voltage, Magnetizing Inductance Variation

- Power Factor Correction (PFC)

- Fast Startup utilizing Bleeding Circuit

- Open-LED Protection

- Short-LED Protection

- Sensing Resistor Short Protection

- Cycle-by-Cycle Current Limiting

- Over-Temperature Protection with Auto Restart

#### **Applications**

LED Lighting System

#### Description

The FL7734 is a highly integrated PWM controller with advanced Primary-Side-Regulation (PSR) technique to minimize components for low power LED lighting solutions. Using the innovative TRUECURRENT<sup>®</sup> technology for tight constant-current control, it enables designs with constant-current (CC) tolerance of less than ±1% in the wide line voltage range to meet stringent LED brightness requirements.

FL7734 can operate with all types of phase cut dimmers. Phase cut dimming is managed smoothly by Fairchild's proprietary constant input current control and bleeding current control to achieve excellent dimmer compatibility without visible flicker.

The controller can automatically detect whether there is a dimmer connection. In non dimming mode, the operating mode is set to optimize power factor and THD by enabling linear frequency control and voltage mode based on DCM.

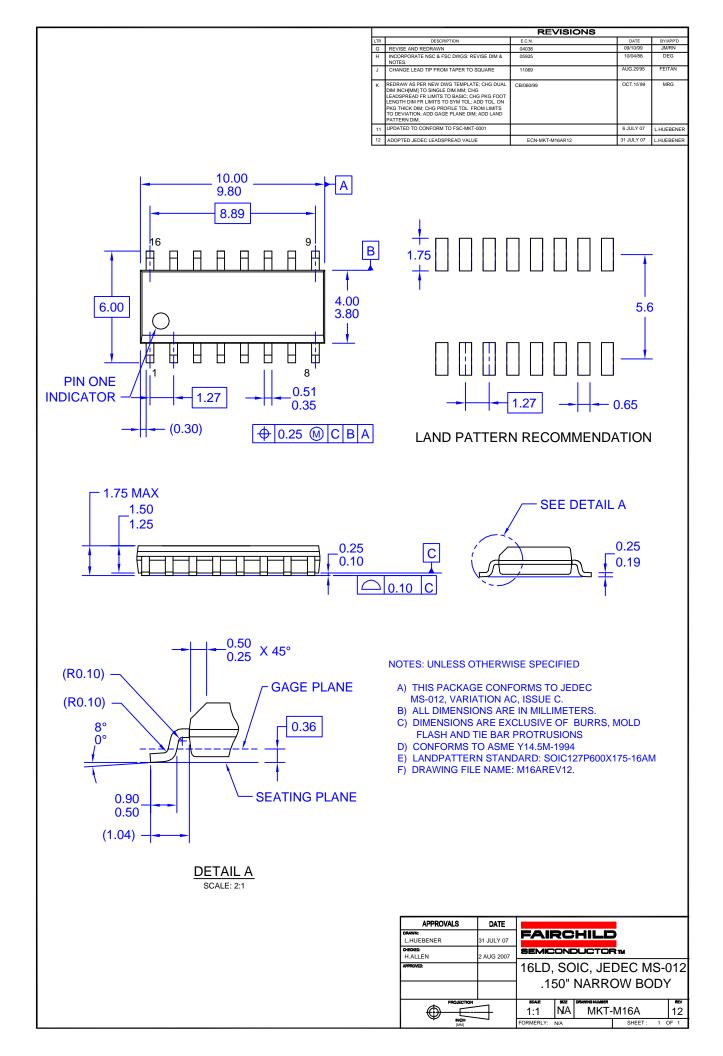

An external high-voltage bleeding circuit is utilized to implement fast startup and high system efficiency. The FL7734 also provides powerful protections, such as LED open / short, sensing resistor shorted, and overtemperature for high system reliability. The FL7734 is available in 16-pin Small-Outline Package (SOP).

#### **Related Resources**

FL7734 Product Folder

| Ordering Information |                             |                                         |                   |  |  |  |

|----------------------|-----------------------------|-----------------------------------------|-------------------|--|--|--|

| Part Number          | Operating Temperature Range | Package                                 | Packing<br>Method |  |  |  |

| FL7734MX             | -40°C to +125°C             | 16-Lead, Small Outline Package (SOP-16) | Tape & Reel       |  |  |  |

current are supplied from this pin.

## **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol            | Symbol Parameter                         |                                                  | Min. | Max. | Unit  |

|-------------------|------------------------------------------|--------------------------------------------------|------|------|-------|

| $V_{\text{VDD}}$  | DC Supply Voltage <sup>(1,2)</sup>       |                                                  | -0.3 | 30   | V     |

| V <sub>DIM</sub>  | DIM Pin Input Voltage                    |                                                  | -0.3 | 6.0  | V     |

| V <sub>MOD</sub>  | MOD Pin Input Voltage                    |                                                  | -0.3 | 6.0  | V     |

| V <sub>HOLD</sub> | HOLD Pin Input Voltage                   | )                                                | -0.3 | 6.0  | V     |

| V <sub>TCIC</sub> | TCIC Pin Input Voltage                   |                                                  | -0.3 | 6.0  | V     |

| $V_{FB}$          | FB Pin Input Voltage                     |                                                  | -0.3 | 6.0  | V     |

| $V_{RBLD}$        | RBLD Pin Input Voltage                   |                                                  | -0.3 | 6.0  | V     |

| V <sub>BIAS</sub> | BIAS Pin Input Voltage                   |                                                  | -0.3 | 30.0 | V     |

| V <sub>BLD</sub>  | BLD Pin Input Voltage                    |                                                  | -0.3 | 30.0 | V     |

| V <sub>MBLD</sub> | MBLD Pin Input Voltage                   |                                                  | -0.3 | 6.0  | V     |

| $V_{VS}$          | VS Pin Input Voltage                     |                                                  | -0.3 | 6.0  | V     |

| Vcs               | CS Pin Input Voltage                     |                                                  | -0.3 | 6.0  | V     |

| V <sub>GATE</sub> | GATE Pin Input Voltage                   |                                                  | -0.3 | 30.0 | V     |

| V <sub>VIN</sub>  | VIN Pin Input Voltage                    |                                                  | -0.3 | 30.0 | V     |

| PD                | Power Dissipation (T <sub>A</sub> <      | 50°C)                                            |      | 909  | mW    |

| heta ja           | Thermal Resistance (Ju                   | nction to Air)                                   |      | 110  | °C /W |

| TJ                | Maximum Junction Temperature             |                                                  |      | 150  | °C    |

| T <sub>STG</sub>  | Storage Temperature Range                |                                                  | -55  | 150  | °C    |

| TL                | Lead Temperature (Soldering, 10 Seconds) |                                                  |      | 260  | °C    |

| ESD               | Electrostatic Discharge                  | Human Body Model,<br>ANSI/ESDA/JEDEC JS-001-2012 |      | 5    | kV    |

|                   | Capability                               | Charged Device Model, JESD22-C101                |      | 2    |       |

Notes:

1. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.

2. All voltage values, except differential voltages, are given with respect to the GND pin.

## **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol | Parameter                       | Min. | Max. | Unit |

|--------|---------------------------------|------|------|------|

| TA     | A Operating Ambient Temperature |      | 125  | °C   |

## **Electrical Characteristics**

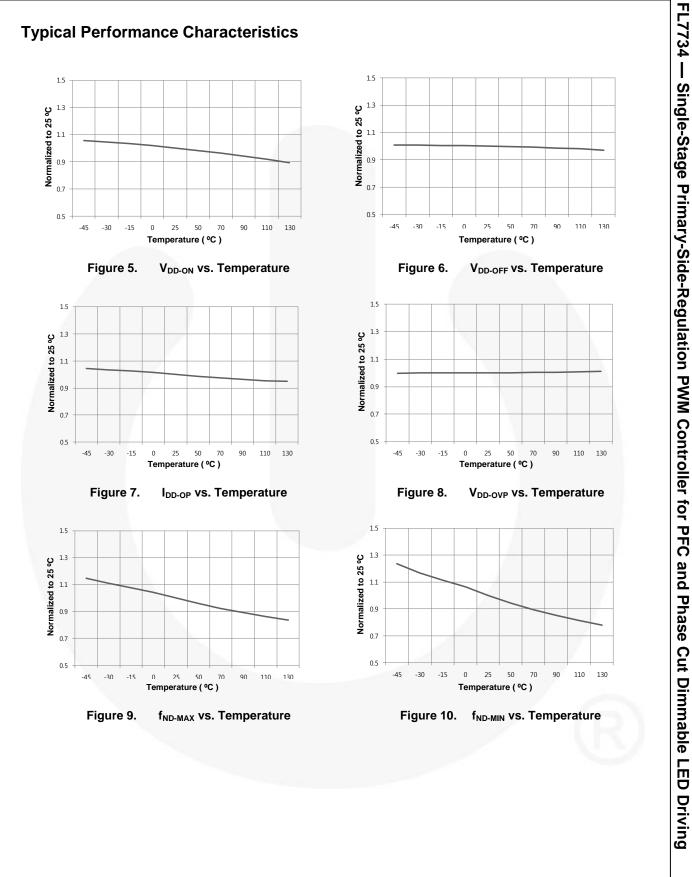

$V_{\text{DD}}\text{=}20$  V and  $T_{\text{J}}\text{=}\text{-}40$  ~ 125°C unless otherwise specified.

| Symbol                                                                  | Parameter                                                    | Condition                                                         | Min. | Тур. | Max. | Unit |

|-------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------|------|------|------|------|

| VDD Sectior                                                             | 1                                                            |                                                                   |      | 1    | 1    |      |

| V <sub>DD-ON</sub> Turn-On Threshold Voltage                            |                                                              |                                                                   | 9.1  | 10.6 | 12.1 | V    |

| V <sub>DD-OFF</sub>                                                     | Turn-Off Threshold Voltage                                   |                                                                   | 6.75 | 7.75 | 8.75 | V    |

| I <sub>DD-OP</sub>                                                      | Operating Current                                            | C <sub>LOAD</sub> =1 nF                                           | 4    | 5    | 6    | mA   |

| I <sub>DD-ST</sub>                                                      | Startup Current                                              | V <sub>DD</sub> =6 V                                              | -    | 2    | 10   | μA   |

| V <sub>DD-OVP</sub>                                                     | V <sub>DD</sub> Over-Voltage-Protection                      |                                                                   | 25   | 27   | 29   | V    |

| VBIAS-VDD-OFF                                                           | BIAS Clamp Voltage at VDD-OFF                                | V <sub>IN</sub> <sup>(3)</sup> =30 V,<br>R <sub>BIAS</sub> =20 kΩ | 21.3 | 24.4 | 27.5 | V    |

| V <sub>BIAS-VDD-ON</sub>                                                | BIAS Clamp Voltage at VDD-ON                                 | V <sub>IN</sub> <sup>(3)</sup> =30 V,<br>R <sub>BIAS</sub> =20 kΩ | 17.6 | 19.5 | 21.4 | V    |

| Gate Section                                                            | ı<br>ı                                                       |                                                                   |      |      |      |      |

| Vol                                                                     | Output Voltage Low                                           | I <sub>GATE</sub> =-1 mA                                          |      |      | 1.5  | V    |

| V <sub>OH</sub>                                                         | Output Voltage High                                          | I <sub>GATE</sub> =+1 mA,<br>V <sub>DD</sub> =10 V                | 5    |      |      | V    |

| Isource                                                                 | Peak Sourcing Current <sup>(4)</sup>                         |                                                                   |      | 60   |      | mA   |

| Isink                                                                   | Peak Sinking Current <sup>(4)</sup>                          |                                                                   |      | 180  |      | mA   |

| tr                                                                      | Rising Time                                                  | C <sub>LOAD</sub> =1 nF                                           | 100  | 150  | 200  | ns   |

| t <sub>f</sub>                                                          | Falling Time                                                 | C <sub>LOAD</sub> =1 nF                                           | 20   | 60   | 100  | ns   |

| VGATE-CLAMP GATE Clamp Voltage                                          |                                                              | V <sub>DD</sub> =20 V                                             | 12   | 15   | 18   | V    |

| Oscillator Se                                                           | ection                                                       |                                                                   |      |      |      |      |

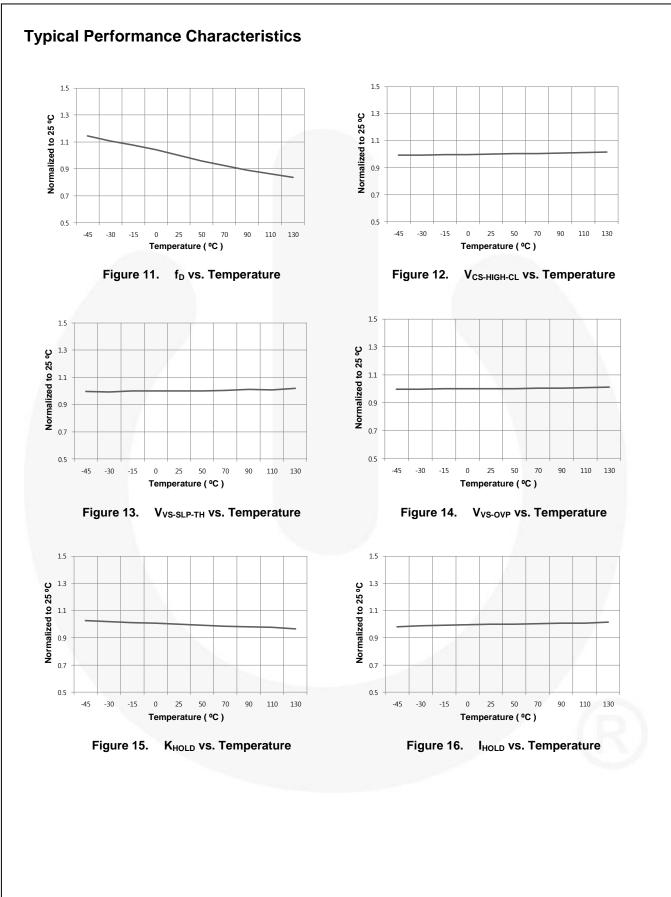

| f <sub>D</sub>                                                          | Operating Frequency at D.Mode                                | TJ=25°C                                                           | 65   | 70   | 75   | kHz  |

| f <sub>ND-MAX</sub>                                                     | Max. Frequency at ND.Mode                                    | T <sub>J</sub> =25°C                                              | 65   | 70   | 75   | kHz  |

| f <sub>ND-MIN</sub>                                                     | Min. Frequency at ND.Mode                                    | T <sub>J</sub> =25°C                                              | 26   | 29.5 | 33   | kHz  |

| t <sub>ON-MAX</sub>                                                     | Maximum Turn-On Time                                         | T <sub>J</sub> =25°C                                              | 10.4 | 12.4 | 14.4 | μS   |

| t <sub>ON-MIN</sub>                                                     | Minimum Turn-On Time <sup>(4)</sup>                          | V <sub>FB</sub> =0 V                                              |      | 600  |      | ns   |

| Current Sen                                                             | se Section                                                   |                                                                   |      | A    |      |      |

| t <sub>LEB</sub>                                                        | Leading-Edge Blanking Time <sup>(4)</sup>                    |                                                                   |      | 300  |      | ns   |

| t <sub>PD</sub> Propagation Delay to GATE                               |                                                              |                                                                   | 50   | 100  | 150  | ns   |

| V <sub>CS</sub> /I <sub>VS</sub> Line Compensation Ratio <sup>(4)</sup> |                                                              |                                                                   |      | 21.5 |      | V/A  |

| Voltage Sen                                                             | se Section                                                   |                                                                   |      |      |      |      |

| t <sub>DIS-BNK</sub>                                                    | t <sub>DIS</sub> Blanking Time at VS Sampling <sup>(4)</sup> |                                                                   |      | 1.5  | 1    | μs   |

| I <sub>VS-BNK</sub>                                                     | VS Current for VS Blanking                                   |                                                                   | 67   | 80   | 93   | μA   |

| M                                                                       | VC Clemping Voltors                                          | I <sub>VS</sub> =1 mA                                             | -0.1 |      | 1    | V    |

| $V_{VS-CLAMP}$                                                          | VS Clamping Voltage                                          | I <sub>VS</sub> =10 μΑ                                            |      |      | 0.35 | V    |

Notes:

3.  $V_{IN}$  is external voltage source and  $R_{BIAS}$  is connected between  $V_{IN}$  and BIAS pin.

4. This parameter, although design-guaranteed, is not tested in production.

| _ |                                                                        |

|---|------------------------------------------------------------------------|

|   | Ш                                                                      |

|   | FL7                                                                    |

|   | 7                                                                      |

| ļ | FL7734                                                                 |

| ļ | 34 — Single-Stage Primary-Side-Regulation PWM Controller for PFC and F |

|   |                                                                        |

| ļ | Ś                                                                      |

|   | Ť                                                                      |

|   | ğ                                                                      |

|   | e                                                                      |

|   | n.                                                                     |

|   | ž                                                                      |

| ļ | <u> 0</u> E                                                            |

|   | e                                                                      |

|   | σ                                                                      |

|   | Ξ.                                                                     |

| ļ | В                                                                      |

|   | ar                                                                     |

|   | Ś                                                                      |

| ļ | പ്പ                                                                    |

| ļ | ō                                                                      |

|   | e                                                                      |

| ļ | +                                                                      |

| ļ | e                                                                      |

| ļ | g                                                                      |

| ļ | L<br>L                                                                 |

| ļ | at                                                                     |

|   | ō                                                                      |

|   | ž                                                                      |

|   | σ                                                                      |

|   | Š                                                                      |

|   | S                                                                      |

| ļ |                                                                        |

|   | 2                                                                      |

|   | ň                                                                      |

| ļ | 4                                                                      |

|   | <u>o</u>                                                               |

|   | e                                                                      |

|   | 1                                                                      |

| ļ | ō                                                                      |

| ļ | Ť                                                                      |

|   | P                                                                      |

|   |                                                                        |

|   |                                                                        |

|   | ne                                                                     |

| ļ | d                                                                      |

| ļ | Π                                                                      |

|   | Ľ                                                                      |

|   | as                                                                     |

|   | ë                                                                      |

| ļ | Ô                                                                      |

| ļ | È                                                                      |

| ļ | <b>_</b>                                                               |

|   | G                                                                      |

|   | З                                                                      |

|   | Ā                                                                      |

|   | a                                                                      |

| ļ | δ                                                                      |

|   | Ð                                                                      |

|   |                                                                        |

|   | Ш                                                                      |

| ļ | U                                                                      |

|   | ₫                                                                      |

|   | F                                                                      |

|   | Ì                                                                      |

|   | ິ                                                                      |

|   |                                                                        |

## **Electrical Characteristics**

$V_{\text{DD}}\text{=}20$  V and T\_J\text{=}-40 ~ 125°C unless otherwise specified.

| Symbol                    | Parameter                                         | Condition                                                                                                                        | Min. | Тур. | Max. | Unit |

|---------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Feedback Se               | ection                                            | I                                                                                                                                | 11   |      |      | 1    |

| gм                        | Transconductance                                  |                                                                                                                                  | 14   | 18   | 22   | µmho |

| I <sub>FB-SINK</sub>      | FB Sink Current                                   | T <sub>J</sub> =25°C, V <sub>EAI</sub> =2 V,<br>V <sub>FB</sub> =2.5 V                                                           | 14   | 18   | 22   | μA   |

| I <sub>FB-SOURCE</sub>    | FB Source Current                                 | V <sub>EAI</sub> =0 V, V <sub>FB</sub> =2.5 V                                                                                    | 14   | 18   | 22   | μA   |

| $V_{\text{FB-HGH}}$       | FB High Voltage <sup>(4)</sup>                    |                                                                                                                                  | 4.7  |      |      | V    |

| $V_{\text{FB-LOW}}$       | FB Low Voltage <sup>(4)</sup>                     |                                                                                                                                  |      |      | 0.1  | V    |

| Start Sequer              | nce Section                                       |                                                                                                                                  |      |      |      |      |

| tss1-MIN                  | Minimum Start Sequence Time 1                     |                                                                                                                                  | 10.8 | 12.0 | 13.2 | ms   |

| t <sub>SS3-MIN</sub>      | Minimum Start Sequence Time 3                     |                                                                                                                                  | 13.5 | 15.0 | 16.5 | ms   |

| V <sub>FB-ADJ-NDM</sub>   | FB Adjustment Voltage in ND.MODE                  |                                                                                                                                  | 1.26 | 1.40 | 1.54 | V    |

| Protection S              | ection                                            |                                                                                                                                  |      |      |      |      |

| V <sub>CS-HIGH-CL</sub>   | High Current Limit Threshold                      |                                                                                                                                  | 1.08 | 1.20 | 1.32 | V    |

| V <sub>CS-LOW-CL</sub>    | Low Current Limit Threshold                       |                                                                                                                                  | 0.15 | 0.20 | 0.25 | V    |

| V <sub>CS-OCP</sub>       | Over Current Protection Voltage                   |                                                                                                                                  |      | 1.8  |      | V    |

| V <sub>VS-LOW-CL-H</sub>  | Low Current Limit Hys. Voltage 'H' <sup>(4)</sup> |                                                                                                                                  | 0.45 | 0.50 | 0.55 | V    |

| V <sub>VS-LOW-CL-L</sub>  | Low Current Limit Hys. Voltage 'L' <sup>(4)</sup> |                                                                                                                                  | 0.35 | 0.40 | 0.45 | V    |

| V <sub>VS-SLP-TH</sub>    | VS Threshold Voltage for SLP                      |                                                                                                                                  | 0.35 | 0.40 | 0.45 | V    |

| V <sub>VS-OVP</sub>       | VS Threshold Voltage for OVP                      |                                                                                                                                  | 2.9  | 3.0  | 3.1  | V    |

| t <sub>AR-DELAY</sub>     | Auto Restart Delay Time <sup>(4)</sup>            |                                                                                                                                  |      | 4.0  |      | s    |

| V <sub>CS-SRSP</sub>      | CS Threshold Voltage for SRSP                     |                                                                                                                                  | 0.05 | 0.10 | 0.15 | V    |

| T <sub>OTP</sub>          | Threshold Temperature for OTP <sup>(4)(5)</sup>   |                                                                                                                                  |      | 150  |      | °C   |

| T <sub>OTP-HYS</sub>      | Junction Temperature Hysteresis <sup>(4)</sup>    |                                                                                                                                  |      | 10   |      | °C   |

| <b>Dimming Co</b>         | ntrol Section                                     |                                                                                                                                  |      |      | •    |      |

| I <sub>DIM</sub>          | DIM Sourcing Current                              | V <sub>DIM</sub> =3 V                                                                                                            | 36   | 40   | 44   | μA   |

| V <sub>VIN-DIM</sub>      | DIM Current On/Off Voltage <sup>(4)</sup>         |                                                                                                                                  |      | 3.00 |      | V    |

| V <sub>DIM-CLAMP</sub>    | DIM Clamping Voltage                              |                                                                                                                                  |      | 3.25 |      | V    |

| K <sub>HOLD</sub>         | HOLD Conversion Coefficient                       | $\begin{array}{c} T_{J} = 25^{\circ}\text{C}, \ V_{CS} = 0.5 \ \text{V}, \\ R_{\text{HOLD}} = 31.5 \ \text{k}\Omega \end{array}$ |      | 510  | 1    | /mA  |

| I <sub>HOLD</sub>         | HOLD Sourcing Current                             | V <sub>HOLD</sub> =3.5 V                                                                                                         | 36   | 40   | 44   | μA   |

| I <sub>TCIC</sub>         | TCIC Sourcing Current                             |                                                                                                                                  | 13.5 | 15.0 | 16.5 | μA   |

| V <sub>TCIC-MIN-DIS</sub> | Minimum TCIC Discharging Voltage                  |                                                                                                                                  | 0.9  | 1.0  | 1.1  | V    |

| V <sub>RBLD-CLAMP</sub>   | Clamped RBLD Voltage                              | $V_{VIN}$ =5 V,<br>R <sub>RBLD</sub> =40 Ω                                                                                       | 0.45 | 0.50 | 0.55 | V    |

| I <sub>MBLD</sub>         | MBLD Current                                      | V <sub>MBLD</sub> =3.5 V                                                                                                         | 36   | 40   | 44   | μA   |

Note:

5. If over-temperature protection is activated, the power system enters Auto Recovery Mode and output is disabled. Device operation above the maximum junction temperature is NOT guaranteed.

## **Functional Description**

FL7734 is a phase-cut dimmable PWM controller for LED lighting applications. Accurate LED current regulation independent of input voltage, output voltage and magnetizing inductance variations is implemented by TRUECURRENT<sup>®</sup> technique. The controller features programmable dimming curve which ensures that the constant maximum LED current can be met at the various maximum phase angle conditions of each dimmer and low LED current can be set at the minimum phase angle condition with wide dimming range. Fairchild's proprietary constant input current control provides excellent dimmer compatibility by maintaining input current higher than TRIAC holding current. The linear frequency control and DCM operation with minimized turn-on time ripple implements best power factor and THD in a single-stage topology. A variety of protections; such as short-LED protection, open-LED protection, sensing resistor open/short protection, overtemperature protection, and cvcle-by-cvcle current limitation stabilize system operation and protect external components.

#### Startup

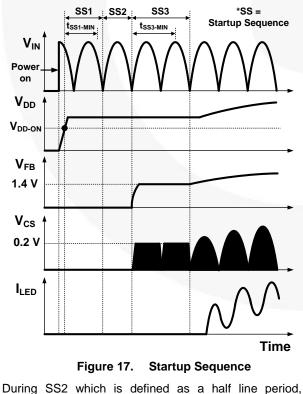

An external bleeding MOSFET is utilized for fast startup. Once power is on, BIAS voltage is quickly lifted to V<sub>BIAS</sub>. V<sub>DD-OFF</sub> (24.4 V) so the bleeding MOSFET can charge the VDD capacitor higher than V<sub>DD-ON</sub> voltage (10.6 V). Once V<sub>DD</sub> is higher than V<sub>DD-ON</sub>, Startup Sequence (SS1) begins with maximum bleeding current to stabilize dimmer operation. SS1 ends when V<sub>IN</sub> reaches the line voltage zero crossing after t<sub>SS1-MIN</sub> (12 ms).

During SS2 which is defined as a half line period, FL7734 determines whether phase-cut dimmer is connected in the line. From SS3, internal operation is

set as either dimming mode or non-dimming mode. SS3 time is set longer than  $t_{SS3-MIN}$  which is counted except for phase-cut time and finishes synchronized with  $V_{IN}$  zero crossing. 0.2 V current-mode is activated during SS3 so that output voltage reaches a level higher than threshold for short-LED protection, which is enabled after SS3. In the mean time, FB voltage is clamped to 1.4 V at non-dimming mode or a certain level proportional to phase angle at dimming mode to set the voltage closer to steady-state level. The maximum bleeding current is disabled after SS3 and voltage mode control is enabled at non-dimming mode and constant input current control is enabled at dimming mode.

#### **Constant-Current Regulation**

The output current is estimated using the peak drain current and inductor current discharge time because output current is same as the average of the diode current in steady-state. The peak value of the drain current is determined by the CS pin. The inductor discharge time ( $t_{dis}$ ) is sensed by a  $t_{dis}$  detector. Using three sources of information; peak drain current, inductor discharging time, and operating switching period, the TRUECURRENT<sup>®</sup> block calculates the estimated output current. The output of the calculation is compared with an internal precise reference to generate an error voltage ( $V_{FB}$ ). With Fairchild's innovative TRUECURRENT<sup>®</sup> technique, constant LED current can be precisely controlled.

### **Constant Input Current Control**

Fairchild's proprietary Constant Input Current (CIC) control generates switching duty to form input current proportional to the external resistor value at HOLD pin. Filtered switch current is the system input current and the system input current is adjusted by the calculation of CS average voltage. Input current is determined by equation (1) where  $K_{HOLD}$  is coefficient of internal calculation.

$$I_{\rm IN} = \frac{R_{\rm HOLD}}{R_{\rm CS} \cdot K_{\rm HOLD}} \tag{1}$$

Fairchild's CIC control offers superior accurate and stable current management than other input current control technologies.

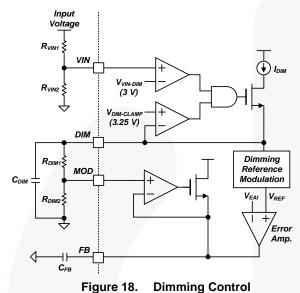

### **Dimming Control**

Phase angle is detected by comparing VIN voltage and 3 V threshold voltage ( $V_{VIN-DIM}$ ). When VIN voltage is higher than 3 V, DIM sourcing current ( $I_{DIM}$ ) is connected to the DIM pin and the current flows into external resistors ( $R_{DIM1}$  and  $R_{DIM2}$ ) and capacitor ( $C_{DIM}$ ). Therefore, the DIM voltage filtered by  $C_{DIM}$  indicates the amount of phase angle controlled by phase-cut dimmer.

$$V_{\text{DIM}} = I_{\text{DIM}} \cdot (R_{\text{DIM1}} + R_{\text{DIM2}}) \cdot \frac{PA}{180^{\circ}}$$

(2)

As a function of dimming reference modulation shown in Figure 18, output current is constantly regulated with constant  $V_{REF}$  when  $V_{DIM}$  is higher than 3 V and  $V_{REF}$  is set lower than  $V_{EAI}$  (TRUECURRENT<sup>®</sup> calculation result) when  $V_{DIM}$  is lower than 2.25 V. Once  $V_{DIM}$  is less than 2.25 V, the error amplifier always pulls down current in the output and FB voltage is clamped by MOD voltage so that open loop control starts for stable LED current control at low phase angle range.

High dimmer compatibility is implemented by bleeding current generated through BLD to RBLD and having the switching mode management by TCIC.

#### PFC and THD

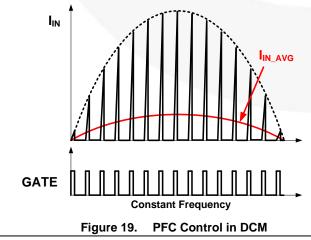

In a conventional boost converter, Boundary Conduction Mode (BCM) is generally used to keep input current in phase with input voltage for Power Factor (PF) and Total Harmonic Distortion (THD). However, BCM switching distorts input current in the single stage flyback / buck boost converter because power inductor current is not the same as input current. Moreover, it becomes more difficult to meet PF and THD once passive bleeder (resistor and capacitor in the driver input) is added for successful firing in the single stage TRIAC dimming system.

In order to optimize PF and THD in the single stage flyback topology, constant turn-on time and constant frequency in Discontinuous Conduction Mode (DCM) are the best method to make the input current proportional to the input voltage as shown in Figure 19. FL7734 basically adopts the DCM operation with constant turn-on and frequency in a half line cycle. Once dimmer absence is detected during startup sequence, FL7734 selects voltage mode in which constant turn-on time is maintained by an internal error amplifier and a large external capacitor (typically >1  $\mu$ F) at the FB pin. Constant frequency and DCM operation are managed by linear frequency control.

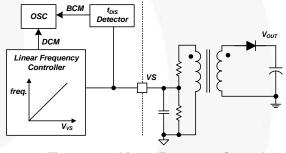

#### **Linear Frequency Control**

DCM should be guaranteed for high power factor in flyback topology. To maintain DCM in the wide range of output voltage, frequency is linearly adjusted by output voltage in linear frequency control. Output voltage is detected by auxiliary winding and resistive divider connected to the VS pin, as shown in Figure 20. When output voltage decreases, secondary diode conduction time is increased and the linear frequency control lengthens switching period, which retains DCM operation in the wide output voltage range. The frequency control lowers primary rms current for better power efficiency in full-load condition.

Figure 20. Linear Frequency Control

### **BCM Control**

The end of secondary diode conduction time ( $t_{DIS}$ ) can be over a switching period set by linear frequency control. In this case, FL7734 doesn't allow CCM and operation mode changes from DCM to BCM. Therefore, magnetizing inductance can be largely designed to add BCM for better efficiency if PF and THD meet specification with enough margin.

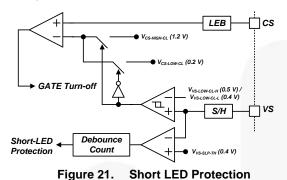

### **Short-LED Protection**

In a short-LED condition, the switching MOSFET and secondary diode are usually stressed by the high powering current.

FL7734 changes the current-limit level in a short-LED condition. When sampled VS voltage is lower than  $V_{VS-LOW-CL-L}$  (0.4 V), the current-limit level is reduced to 0.2 V from 1.2 V, as shown in Figure 21 so that powering is limited and external components' current stress is relieved. When the sampled VS voltage is continuously lower than  $V_{VS-SLP-TH}$  (0.4 V) for 3 consecutive switching cycles, short-LED protection is triggered with gate shutdown. After all types of protection including short-LED protection is triggered, FL7734 internally counts 4 seconds for auto restart and begins startup sequence again.

#### **Open-LED Protection**

When output load is open as high impedance, the output capacitor should be protected by limiting the capacitor voltage less than its maximum rating. FL7734 can detect the output over-voltage condition by sensing both VDD and VS voltages. When VDD voltage is higher than  $V_{DD-OVP}$  (27 V typical) or sampled VS voltage is higher than  $V_{VS-OVP}$  (3 V typical), protection is triggered. The protection mode is auto restart so normal operation resumes when the fault condition is removed.

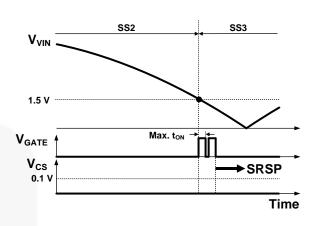

#### **Sensing Resistor Short Protection**

During SS3, the controller operates in current-mode control and the peak CS voltage is 0.2 V during switching mode. When a sensing resistor is short circuited, CS voltage cannot reach 0.2 V and turn on time is maximized with potential damage of switching MOSFET. In order to provide protection against the failure, FL7734 compares CS voltage with V<sub>CS-SRSP</sub> (0.1 V) during the initial two switching operation. When VCS doesn't reach 0.1 V for the two switching, Sensing Resistor Short Protection (SRSP) is triggered. In normal condition, input voltage corresponding to 1.5 V V<sub>VIN</sub> is high enough to make V<sub>CS</sub> higher than 0.1 V with turn-on time shorter than maximum turn-on time.

Figure 22. Sensing Resistor Short Protection

#### **Under-Voltage Lockout (UVLO)**

The turn-on and turn-off thresholds are fixed internally at 10.6 V and 7.75 V, respectively. During startup, the VDD capacitor must be charged higher than 10.6 V through the external bleeding MOSFET. The bleeding MOSFET supplies VDD operating current until power can be delivered from the auxiliary winding of the main transformer. Generally at small phase angle range, VDD supply time from auxiliary winding is short and V<sub>DD</sub> could reach to V<sub>DD-OFF</sub> (7.75 V). If V<sub>DD</sub> drops below V<sub>DD-OFF</sub>, VDD hiccup occurs with a certain hiccup frequency determined by VDD capacitor value and VDD supply current from auxiliary winding. This hiccup mode could cause LED flicker. In order to remove the unstable mode of operation, external bleeding circuit never allows V<sub>DD</sub> voltage to fall down less than V<sub>DD-OFF</sub> (7.75 V) once input power is supplied.

#### **Over-Temperature Protection (OTP)**

The built-in temperature-sensing circuit shuts down PWM output if the junction temperature exceeds 150°C. After Over-Temperature Protection (OTP) is triggered, FL7734 repeats auto-restart time counting until the junction temperature is lowered less than 140°C. Different from Short/Open-LED protection and SRSP, startup sequence doesn't appear every 4 seconds of auto-restart delay time because the temperature is detected by monitoring internally, not by checking external pin information. Normal startup sequence is started again when the junction temperature is out of the hysteresis temperature (140°C).

\* Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. TO OBTAIN THE LATEST, MOST UP-TO-DATE DATASHEET AND PRODUCT INFORMATION, VISIT OUR WEBSITE AT <u>HTTP://WWW.FAIRCHILDSEMI.COM</u>, FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### AUTHORIZED USE

Unless otherwise specified in this data sheet, this product is a standard commercial product and is not intended for use in applications that require extraordinary levels of quality and reliability. This product may not be used in the following applications, unless specifically approved in writing by a Fairchild officer: (1) automotive or other transportation, (2) military/aerospace, (3) any safety critical application – including life critical medical equipment – where the failure of the Fairchild product reasonably would be expected to result in personal injury, death or property damage. Customer's use of this product is subject to agreement of this Authorized Use policy. In the event of an unauthorized use of Fairchild's product, Fairchild accepts no liability in the event of product failure. In other respects, this product shall be subject to Fairchild's Worldwide Terms and Conditions of Sale, unless a separate agreement has been signed by both Parties.

#### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Terms of Use

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

| Definition of Terms                                                     |                       |                                                                                                                                                                                                     |  |  |  |

|-------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Datasheet Identification                                                | Product Status        | Definition                                                                                                                                                                                          |  |  |  |

| Advance Information                                                     | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |  |  |  |

| Preliminary First Production   No Identification Needed Full Production |                       | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |  |  |  |

|                                                                         |                       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |  |  |  |

| Obsolete                                                                | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor.<br>The datasheet is for reference information only.                                                 |  |  |  |

Rev. 175