## FM8P756

## OTP-Based 8-Bit Microcontroller with LCD Driver

#### **Devices Included in this Data Sheet:**

FM8P756A: 24-pin OTP deviceFM8P756B: 20-pin OTP device

• FM8P756C: 16-pin OTP device

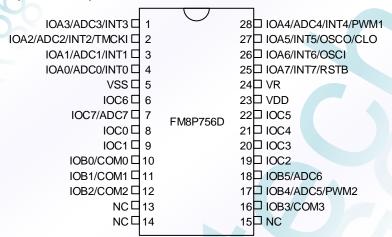

• FM8P756D: 28-pin OTP device with VR pin

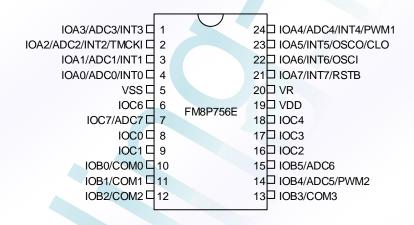

• FM8P756E: 24-pin OTP device with VR pin

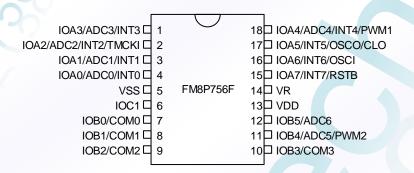

• FM8P756F: 18-pin OTP device with VR pin

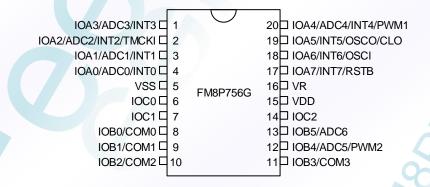

• FM8P756G: 20-pin OTP device with VR pin

#### **FEATURES**

- Total 8 channel 10bit AD converter with ±2LSB resolution

- · All instructions are single cycle except for program branches which are two-cycles

- All OTP area GOTO instruction

- All OTP area subroutine CALL instruction

- · 8-bit wide data path

- 8-level deep hardware stack

- 2K x 16 bits on chip OTP

- 36x8 bits on chip special purpose registers and 96 x 8 bits on chip general purpose registers (SRAM)

- Operating speed: DC-20 MHz clock input, or DC-100 ns instruction cycle

- · Direct, indirect addressing modes for data accessing

- · Three real time down-count Timer/Counter with 3-bit programmable prescaler

- TMR1: 8-bit, PWM1 & Timer

- TMR2: 8-bit, PWM2 & Timer

- TMR3: 8-bit, Timer

- Software controlled 4-COM lines LCD driver with 1/2bias

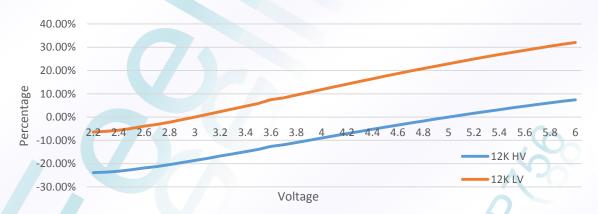

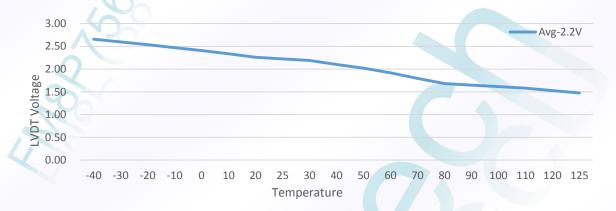

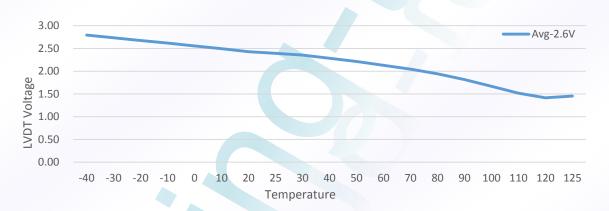

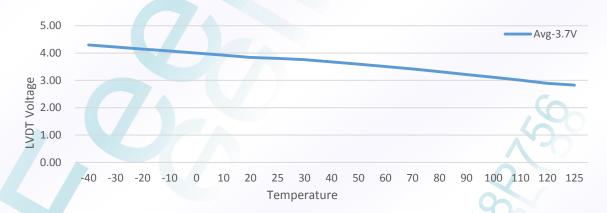

- Built-in 3 levels Low Voltage Detector (LVDT) (2.2V/2.6V/3.7V) for Brown-out Reset (BOR)

- Power-up Reset Timer (PWRT)

- On chip Watchdog Timer (WDT) with internal oscillator for reliable operation and soft-ware watch-dog enable/disable control

- Three I/O ports Port A, Port B and Port C with independent direction control

- 21 Bi-direction I/O port (Programmable Pull-up enable in Input mode)

- One Input only port (IOA7/RSTB)

- Four kinds of interrupt source: 3 Timers/Counters, 8 external interrupt sources: IOA0~IOA7, Internal watchdog timer (i\_WDT) wakeup, and A/D end of conversion

- · Wake-up from SLEEP:

- Port A (IOA0~IOA7) pin change wakeup

- WDT overflow

- i\_WDT overflow

- · Power saving SLEEP mode

- Programmable Code Protection

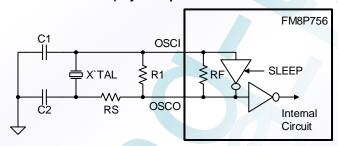

- Selectable oscillator options:

- ERC: External Resistor/ Voltage Controlled Oscillator

- XT: Crystal/Resonator Oscillator

- LF: Low Frequency Crystal Oscillator

- HIRC: Internal Resistor/Capacitor High speed Oscillator

- LIRC: Internal Resistor/Capacitor Low speed Oscillator

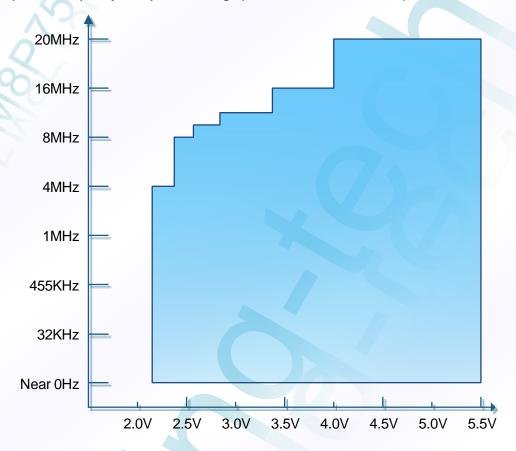

- Operating voltage range:

- ≤4MHz: 2.2V to 5.5V

- ≤8MHz: 2.4V to 5.5V, see 6.1 for more information.

This datasheet contains new product information. Feeling Technology reserves the rights to modify the product specification without notice. No liability is assumed as a result of the use of this product. No rights under any patent accompany the sales of the product.

## **GENERAL DESCRIPTION**

The FM8P756 is a low-cost, high speed, high noise immunity, OTP-based 8-bit CMOS microcontrollers. It employs a RISC architecture with 54 instructions. All instructions are single cycle except for program branches which take two cycles. The easy to use and easy to remember instruction set reduces development time significantly.

The FM8P756 consists of Power-on Reset (POR), Brown-out Reset (BOR), Power-up Reset Timer (PWRT), Watchdog Timer, OTP, SRAM, tri-state I/O port, I/O pull-high control, Power saving SLEEP mode, 3 real time programmable clock/counter, Interrupt, Wake-up from SLEEP mode, and Code Protection for OTP products. There are eight oscillator configurations to be chosen from, including the power-saving LF (Low Frequency) oscillator and cost saving internal RC oscillator.

The FM8P756 address 2K×16 of program memory.

The FM8P756 can directly or indirectly address its register files and data memory. All special function registers including the program counter are mapped in the data memory.

The FM8P756 provides total 8 channel 10bit AD converter with ±2LSB resolution.

The FM8P756 provides total 4 COM LCD pins, drive waveform is controlled by Software.

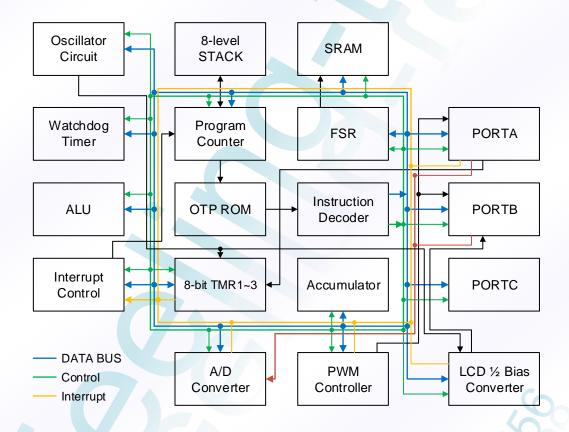

#### **BLOCK DIAGRAM**

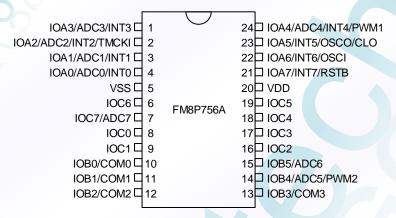

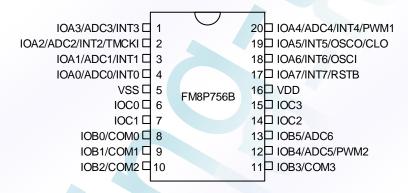

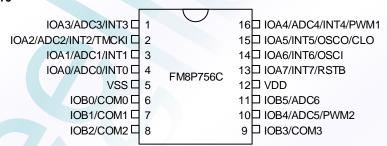

#### **PIN CONNECTION**

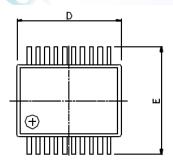

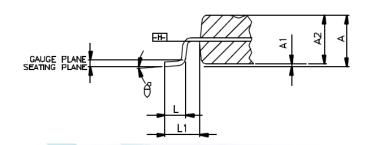

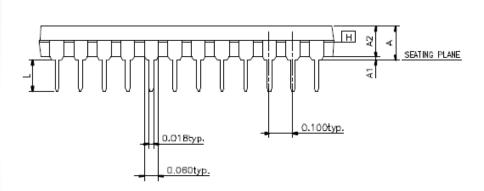

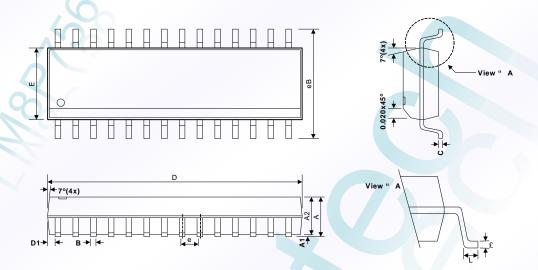

## PDIP24, SOP24

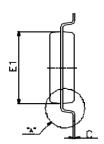

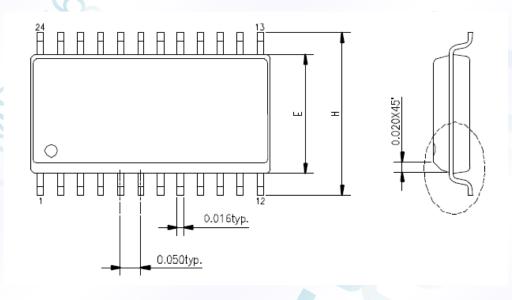

#### PDIP20, SOP20

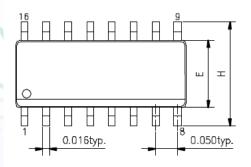

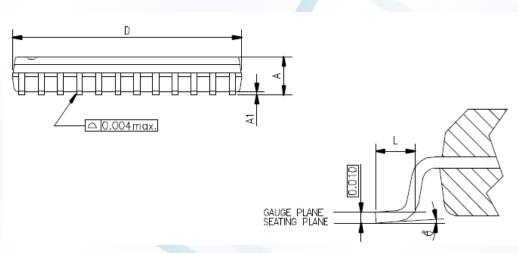

#### PDIP16, SOP16

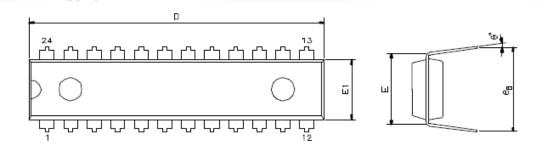

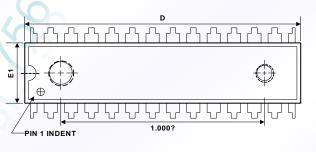

#### PDIP28, SOP28 (With VR PIN)

#### PDIP24, SOP24 (With VR PIN)

## PDIP20, SOP20 (With VR PIN)

## PDIP18, SOP18 (With VR PIN)

## **PIN DESCRIPTIONS**

| FIN DESCRIP                         | 110113 |                                                                                                                                                                                                                                        |

|-------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                                | I/O    | Description                                                                                                                                                                                                                            |

| IOA0/AD0/INT0<br> <br>IOA4/AD4/INT4 | I/O    | Bi-direction I/O port (programmable Pull-high in Input mode) Wake-up on pin change External interrupt input A/D converter input IOA4 is PWM1 output                                                                                    |

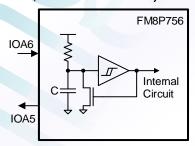

| IOA5/INT5<br>/OSCO                  | I/O    | <ul> <li>Bi-direction I/O port (programmable Pull-high in Input mode)</li> <li>Wake-up on pin change</li> <li>External interrupt input</li> <li>Clock output shared with IOA5</li> <li>Oscillator output (XT, LF, ERC mode)</li> </ul> |

| IOA6/INT6<br>/OSCI                  | I/O    | <ul> <li>Bi-direction I/O port (programmable Pull-high in Input mode)</li> <li>Wake-up on pin change</li> <li>External interrupt input</li> <li>Oscillator input (XT, LF, ERC mode)</li> </ul>                                         |

| IOA7/INT7<br>/RSTB                  | 1      | <ul> <li>Input port</li> <li>Wake-up on pin change</li> <li>External interrupt input</li> <li>System clear (RESET) input. This pin is an active low RESET to the device.<br/>The voltage on this pin must not exceed VDD.</li> </ul>   |

| IOB0/COM0<br> <br>IOB3/COM3         | I/O    | Bi-direction I/O port (programmable Pull-high in Input mode) Software controlled 1/2bias LCD COM0 ~ COM3 output                                                                                                                        |

| IOB4/AD5<br> <br>IOB5/AD6           | I/O    | <ul> <li>Bi-direction I/O port (programmable Pull-high in Input mode)</li> <li>IOB4 is PWM2 output</li> <li>A/D converter input</li> </ul>                                                                                             |

| IOC0<br> <br>IOC6                   | I/O    | Bi-direction I/O port (programmable Pull-high in Input mode)     LCD segment output                                                                                                                                                    |

| IOC7/ADC7                           | I/O    | <ul> <li>Bi-direction I/O port (programmable Pull-high in Input mode)</li> <li>LCD segment output</li> <li>A/D converter input</li> </ul>                                                                                              |

| VR                                  | -      | ADC module reference input. The voltage on this pin must not exceed VDD.                                                                                                                                                               |

| VDD                                 | -      | Positive supply                                                                                                                                                                                                                        |

| VSS                                 | -      | Ground                                                                                                                                                                                                                                 |

Legend: I=input, O=output, I/O=input/output

Note: Please refer to 2.2 for detail IO type description

#### 1.0 MEMORY ORGANIZATION

FM8P756 memory is organized into program memory and data memory.

## 1.1 Program Memory Organization

The FM8P756 has a 11-bit Program Counter capable of addressing a 2Kx16 program memory space.

The RESET vector for the FM8P756 is at 000h.

The H/W interrupt vector is at 004h.

FM8P756 supports all OTP area CALL/GOTO instructions without page.

Figure 1.1: Program Memory Map and STACK

## 1.2 Data Memory Organization

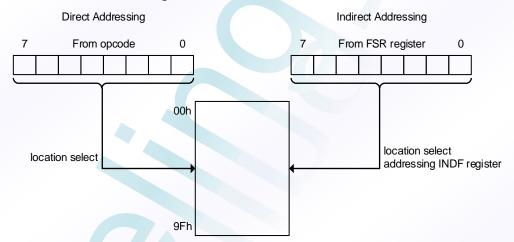

Data memory is composed of 36 bytes Special Function Registers and 96 bytes General Purpose Registers. The data memory can be accessed either directly or indirectly through the FSR register.

Table 1.1: Registers File Map for FM8P756

| Address | Description     |

|---------|-----------------|

| 00h     |                 |

| :       | Special Purpose |

| :       | Register        |

| 2Ch     |                 |

| 40h     |                 |

|         |                 |

|         |                 |

| :       | General Purpose |

| :       | Register        |

|         |                 |

|         |                 |

| 9Fh     |                 |

**Table 1.2: Special Purpose Registers Map**

|               | e itegiete.                                                                                                                                                                     |                        |           |              |             |              |              |        |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------|--------------|-------------|--------------|--------------|--------|

| Name          | В7                                                                                                                                                                              | В6                     | B5        | B4           | В3          | B2           | B1           | B0     |

|               |                                                                                                                                                                                 |                        |           |              |             |              |              |        |

| INDF          | Us                                                                                                                                                                              | es contents            | of FSR to | address da   | ata memory  | y (not a phy | sical regis  | ter)   |

| PCL           |                                                                                                                                                                                 | Low order 8 bits of PC |           |              |             |              |              |        |

| PCHBUF        | -                                                                                                                                                                               | -                      |           | - /          | -           | High o       | order 3 bits | of PC  |

| STATUS        | -                                                                                                                                                                               | -                      | 1         | TO           | PD          | Z            | DC           | С      |

| FSR           |                                                                                                                                                                                 |                        | Indirect  | data memo    | ory address | s pointer    |              |        |

| ONTROL        |                                                                                                                                                                                 |                        |           |              |             |              |              |        |

| IOSTA         | 4                                                                                                                                                                               | IOSTA6                 | IOSTA5    | IOSTA4       | IOSTA3      | IOSTA2       | IOSTA1       | IOSTA0 |

| PORTA         | IOA7                                                                                                                                                                            | IOA6                   | IOA5      | IOA4         | IOA3        | IOA2         | IOA1         | IOA0   |

| IOSTB         | -                                                                                                                                                                               | -                      | IOSTB5    | IOSTB4       | IOSTB3      | IOSTB2       | IOSTB1       | IOSTB0 |

| PORTB         | -                                                                                                                                                                               | -                      | IOB5      | IOB4         | IOB3        | IOB2         | IOB1         | IOB0   |

| IOSTC         | IOSTC7                                                                                                                                                                          | IOSTC6                 | IOSTC5    | IOSTC4       | IOSTC3      | IOSTC2       | IOSTC1       | IOSTC0 |

| PORTC         | IOC7                                                                                                                                                                            | IOC6                   | IOC5      | IOC4         | IOC3        | IOC2         | IOC1         | IOC0   |

| it Timer & PW | M1 Duty                                                                                                                                                                         |                        |           |              |             |              |              |        |

| T1CON         | T1EN                                                                                                                                                                            | -                      | T1SO1     | T1SO0        | T1EDG       | T1PS2        | T1PS1        | T1PS0  |

| PWM1CON       | T1MOD                                                                                                                                                                           | PWM1S                  | EPWM1     | -            | PIR13       | PIR12        | PIR11        | PIR10  |

| T1LA          |                                                                                                                                                                                 |                        | 8-bit r   | eal-time tir | ner/counte  | r latch      |              |        |

| T1CNT         |                                                                                                                                                                                 |                        | 8-bit re  | eal time tim | er/counter  | Count        |              |        |

| it Timer & PW | M2 Duty                                                                                                                                                                         |                        |           |              |             |              |              |        |

| T2CON         | T2EN                                                                                                                                                                            | -                      | T2SO1     | T2SO0        | T2EDG       | T2PS2        | T2PS1        | T2PS0  |

| PWM2CON       | T2MOD                                                                                                                                                                           | PWM2S                  | EPWM2     | -            | PIR23       | PIR22        | PIR21        | PIR20  |

| T2LA          |                                                                                                                                                                                 |                        | 8-bit r   | eal-time tir | ner/counte  | r latch      |              | 12     |

| T2CNT         |                                                                                                                                                                                 | 39                     | 8-bit re  | eal time tim | er/counter  | Count        |              |        |

| t Timer       |                                                                                                                                                                                 |                        |           |              |             |              |              |        |

| T3CON         | T3EN                                                                                                                                                                            | T3LOAD                 | T3SO1     | T3SO0        | T3EDG       | T3PS2        | T3PS1        | T3PS0  |

| T3LA          | 8-bit real-time timer/counter latch                                                                                                                                             |                        |           |              |             |              |              |        |

| T3CNT         | 8-bit real-time timer/counter Count                                                                                                                                             |                        |           |              |             |              |              |        |

| RQ            |                                                                                                                                                                                 |                        |           |              |             |              |              |        |

| INTEN         | GIE                                                                                                                                                                             | ADCIE                  | PAIE      | COMIE        | -           | T3IE         | T2P2IE       | T1P1IE |

| INTFLAG       | -                                                                                                                                                                               | ADCIF                  | PAIF      | COMIF        | -           | T3IF         | T2P2IF       | T1P1IF |

|               | INDF PCL PCHBUF STATUS FSR ONTROL IOSTA PORTA IOSTB PORTB IOSTC PORTC ITIMER & PW T1CON PWM1CON T1LA T1CNT ITTIMER & PW T2CON PWM2CON T2LA T2CNT ITTIMER T3CON T3LA T3CNT INTEN | INDF                   | INDF      | INDF         | INDF        | INDF         | INDF         | INDF   |

# FM8P756

| Address     | Name         | B7     | B6     | B5     | B4     | В3     | B2     | B1     | В0     |  |

|-------------|--------------|--------|--------|--------|--------|--------|--------|--------|--------|--|

| ADC Contro  | ADC Control  |        |        |        |        |        |        |        |        |  |

| 1Bh (r/w)   | ADCON1       | ADCEN  | -      | -      | -      | -      | CHSL2  | CHSL1  | CHSL0  |  |

| 1Ch (r/w)   | ADCON2       | -      | •      | -      | -      | -      | -      | CLKSL1 | CLKSL0 |  |

| 1Dh (r/w)   | ADCON3       | -      | •      | 1      | -      | ANISL3 | ANISL2 | ANISL1 | ANISL0 |  |

| 1Eh (r)     | ADDATL       | D1     | D0     | -      | -      | -      | -      | -      | -      |  |

| 1Fh (r)     | ADDATH       | D9     | D8     | D7     | D6     | D5     | D4     | D3     | D2     |  |

| Software LC | Software LCD |        |        |        |        |        |        |        |        |  |

| 20h (r/w)   | COMCON1      | -      | •      | -      | -      | COM3E  | COM2E  | COM1E  | COM0E  |  |

| 21h (r/w)   | COMCON2      | COMEN  | •      | •      | COMIS1 | COMIS0 | COMCK2 | COMCK1 | COMCK0 |  |

| Others      |              |        |        |        |        |        |        | 4      |        |  |

| 22h (r/w)   | SYSCLK       | CLKS   | •      | -      | -      | •      | -      | IRCPD  | ECLKPD |  |

| 23h (r/w)   | CLOCON       | CLOEN  | •      | EXCLK  | DINV   | DUTY   | CLOPS2 | CLOPS1 | CLOPS0 |  |

| 25h (r/w)   | APHCON       | •      | PHA6   | PHA5   | PHA4   | PHA3   | PHA2   | PHA1   | PHA0   |  |

| 26h (r/w)   | BPHCON       | •      | •      | PHB5   | PHB4   | PHB3   | PHB2   | PHB1   | PHB0   |  |

| 27h (r/w)   | CPHCON       | PHC7   | PHC6   | PHC5   | PHC4   | PHC3   | PHC2   | PHC1   | PHC0   |  |

| 28h (r/w)   | INTPA        | PA7IEN | PA6IEN | PA5IEN | PA4IEN | PA3IEN | PA2IEN | PA1IEN | PA0IEN |  |

| 29h (r/w)   | WDTCON       | WDTEN  | I_WDT  | I_TWDT | -      | -      | WDTPS2 | WDTPS1 | WDTPS0 |  |

| 2Ah (r/w)   | TAB_BNK      | -      | -      | -      | -      | -//    | BNK2   | BNK1   | BNK0   |  |

Legend: - = unimplemented, read as '0'.

#### 2.0 FUNCTIONAL DESCRIPTIONS

## 2.1 Operational Registers

#### 2.1.1 INDF (Indirect Addressing Register)

| Address   | Name | В7 | B6                                                                    | B5 | B4 | В3 | B2 | B1   | В0 |

|-----------|------|----|-----------------------------------------------------------------------|----|----|----|----|------|----|

| 00h (r/w) | INDF | Us | Uses contents of FSR to address data memory (not a physical register) |    |    |    |    | ter) |    |

The INDF Register is not a physical register. Any instruction accessing the INDF register can actually access the register pointed by FSR Register. Reading the INDF register itself indirectly (FSR="0") will read 00h. Writing to the INDF register indirectly results in a no-operation (although status bits may be affected).

#### **Example 2.1: INDIRECT ADDRESSING**

Register file 48 contains the value 10h

Register file 49 contains the value 0Ah

Load the value 48 into the FSR Register

A read of the INDF Register will return the value of 10h

Increment the value of the FSR Register by one (@FSR=49h)

A read of the INDF register now will return the value of 0Ah.

Figure 2.1: Direct/Indirect Addressing for FM8P756

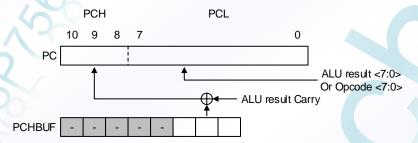

## 2.1.2 PCL / PCHBUF (Low / High Bytes of Program Counter) & Stack

| Address   | Name   | B7                     | В6 | B5 | B4 | В3 | B2     | B1          | В0    |

|-----------|--------|------------------------|----|----|----|----|--------|-------------|-------|

| 01h (r/w) | PCL    | Low order 8 bits of PC |    |    |    |    |        |             |       |

| 02h (r/w) | PCHBUF | -                      | -  | -  | -  | -  | High o | rder 3 bits | of PC |

Legend: - = unimplemented, read as '0'.

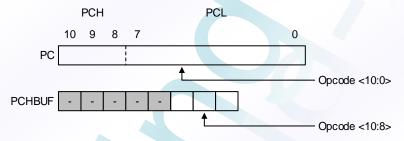

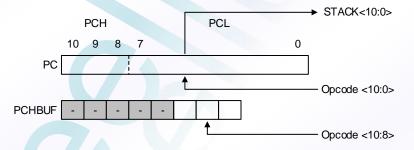

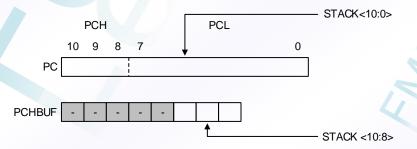

FM8P756 devices have an 11-bits wide Program Counter (PC) and eight-level deep 11-bit hardware push/pop stack. This 11-bits Program Counter can be accessed and controlled by two registers, PCHBUF and PCL. The low byte of PC control register is called the PCL. This register is readable and writable. The high byte of PC control register is called the PCHBUF. This register contains the PC<10:8> bits also readable or writable. The PCL and PCHBUF registers normally indicate the value of Program Counter. But when interrupt occurrence and execution of RETF and RETFIE, the PCHBUF data would not be update.

Any address within the program memory can be written into PCL and PCHBUF registers. If the PCHBUF register been changed and different from Program Counter., the value of PCHBUF register updated only when execute GOTO, CALL, RETURN, or PCL value changed or increases from 0xff to 0x00. Once the value of PCL register changed, the program and Program Counter will jump to the location indicated by PCL and PCHBUF register.

Figure 2.2: Loading of PC in Different Situations

Situation 1: GOTO Instruction

Situation 2: CALL Instruction

Situation 3: RETURN, RETF, RETIA or RETFIE Instruction

#### Situation 4: Instruction with PCL as destination

## 2.1.3 STATUS (Status Register)

| Address   | Name   | B7 | B6 | B5 | B4 | В3 | B2 | B1 | B0 |

|-----------|--------|----|----|----|----|----|----|----|----|

| 03h (r/w) | STATUS | -  | -  | -  | TO | PD | Z  | DC | С  |

Legend: - = unimplemented, read as '0'.

This register contains the arithmetic status of the ALU, the RESET status.

If the STATUS Register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are not writable. Therefore, the result of an instruction with the STATUS Register as destination may be different than intended. For example, CLRR STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS Register as 000u u1uu (where u = unchanged).

#### C: Carry/borrow bit.

ADDAR

- = 1, Carry occurred.

- = 0, No Carry occurred.

SUBAR

- = 1, No borrow occurred.

- = 0, Borrow occurred.

Note: A subtraction is executed by adding the two's complement of the second operand. For rotate (RRR, RLR) instructions, this bit is loaded with either the high or low order bit of the source register.

## DC: Half carry/half borrow bit

**ADDAR**

- = 1, Carry from the 4th low order bit of the result occurred.

- = 0, No Carry from the 4th low order bit of the result occurred.

SUBAR

- = 1, No Borrow from the 4th low order bit of the result occurred.

- = 0, Borrow from the 4th low order bit of the result occurred.

#### Z: Zero bit.

- = 1, The result of a logic operation is zero.

- = 0, The result of a logic operation is not zero.

**PD**: Power down flag bit.

= 1, after power-up or by the CLRWDT instruction.

= 0, by the SLEEP instruction.

**TO**: Watch-dog timer overflow flag bit.

= 1, after power-up or by the CLRWDT or SLEEP instruction

= 0, a watch-dog time overflow occurred

## 2.1.4 FSR (Indirect Data Memory Address Pointer)

| Address   | Name | В7 | В6 | B5       | B4        | В3          | B2      | B1 | B0 |

|-----------|------|----|----|----------|-----------|-------------|---------|----|----|

| 04h (r/w) | FSR  |    |    | Indirect | data memo | ory address | pointer |    |    |

Bit7:Bit0: Select registers address in the indirect addressing mode. See 2.1.1 for detail description.

# 2.1.5 PORTA, PORTB, PORTC, IOSTA, IOSTB and IOSTC (Port Data Registers and Port Direction Control Registers)

| Address   | Name  | В7     | В6     | B5     | B4     | В3     | B2     | B1     | B0     |

|-----------|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| 05h (r/w) | IOSTA | -      | IOSTA6 | IOSTA5 | IOSTA4 | IOSTA3 | IOSTA2 | IOSTA1 | IOSTA0 |

| 06h (r/w) | PORTA | IOA7*  | IOA6   | IOA5   | IOA4   | IOA3   | IOA2   | IOA1   | IOA0   |

| 07h (r/w) | IOSTB | -      | -      | IOSTB5 | IOSTB4 | IOSTB3 | IOSTB2 | IOSTB1 | IOSTB0 |

| 08h (r/w) | PORTB | -      | •      | IOB5   | IOB4   | IOB3   | IOB2   | IOB1   | IOB0   |

| 09h (r/w) | IOSTC | IOSTC7 | IOSTC6 | IOSTC5 | IOSTC4 | IOSTC3 | IOSTC2 | IOSTC1 | IOSTC0 |

| 0Ah (r/w) | PORTC | IOC7   | IOC6   | IOC5   | IOC4   | IOC3   | IOC2   | IOC1   | IOC0   |

Legend: - = unimplemented, read as '0'.

The registers (IOSTA, IOSTB and IOSTC) are used to define the input or output of each port.

- = 1, Input.

- = 0, Output.

Reading the port (PORTA, PORTB and PORTC register) reads the status of the pins independent of the pin's input/output modes. Writing to these ports will write to the port data latch. Please refer to 2.2 for detail I/O Port description.

Note: IOA7 is read only.

## 2.1.6 TMR1: 8-bit Timer & PWM1 Duty

The Timer1 is an 8-bit down count timer/counter which includes counter register (T1CNT), and latch register (T1LA). Please refer to 2.3 for detail Timer description.

The Timer1 can also be PWM1 and controlled by the register PWM1CON. Please refer to 2.4 for detail PWM description.

## 2.1.6.1 T1CON (Timer1 Control Register)

| Address   | Name  | В7   | В6 | B5    | B4    | В3    | B2    | B1    | B0    |

|-----------|-------|------|----|-------|-------|-------|-------|-------|-------|

| 10h (r/w) | T1CON | T1EN | -  | T1SO1 | T1SO0 | T1EDG | T1PS2 | T1PS1 | T1PS0 |

Legend: - = unimplemented, read as '0'.

T1EN: TMR1 Enable/Disable

= 1, TMR1 (PWM1) Enable. = 0, TMR1 (PWM1) Disable.

T1SO1:T1SO0: TMR1 clock source selection

| T1SO1 | T1SO0 | TMR1 clock source         |

|-------|-------|---------------------------|

| 0     | 0     | TMCKI(IOA2)               |

| 0     | 1     | Crystal mode OSCI or LIRC |

| 1     | 0     | Internal 8MHz RC or ERC   |

| 1     | 1     | 8 MHz IRCx2               |

Note: Please refer 2.3 for detail description.

T1EDG: TMR1 clock edge selection. This bit works only when external clock source TMCKI (IOA2) selected.

= 1, TMR1 decreased while external clock H→L (Falling edge).

= 0, TMR1 decreased while external clock L→H (Rising edge).

T1PS2:T1PS0: TMR1 Prescaler selection

| T1PS2: | T1PS0 | TMR1 Prescal rate |

|--------|-------|-------------------|

| 0 0    | 0     | 1:1               |

| 0 0    | 1     | 1:2               |

| 0 1    | 0     | 1:4               |

| 0 1    | 1     | 1:8               |

| 1 0    | 0     | 1:16              |

| 1 0    | 1     | 1:32              |

| 1 1    | 0     | 1:64              |

| 1 1    | 1     | 1:128             |

## 2.1.6.2 PWM1CON (PWM1 Control Register)

| Address   | Name    | B7    | B6    | B5    | B4 | В3    | B2    | B1    | В0    |

|-----------|---------|-------|-------|-------|----|-------|-------|-------|-------|

| 11h (r/w) | PWM1CON | T1MOD | PWM1S | EPWM1 | -  | PIR13 | PIR12 | PIR11 | PIR10 |

Legend: - = unimplemented, read as '0'.

T1MOD: TMR1 operation mode select bit.

= 1, The TMR1 in PWM mode operation.

= 0, The TMR1 in Timer mode operation.

PWM1S: Initial State of PWM1 output duty.

= 1, Set the initial state to L, change to H when TMR1 duty underflow.

= 0, Set the initial state to H, change to L when TMR1 duty underflow.

**EPWM1**: Extension PWM mode selection

= 1, PWM1 is Extension PWM mode.

= 0, PWM1 is normal PWM mode.

Note: Please refer to 2.4 for detail PWM description.

PIR13:PIR10: Interrupt Event Rate of PWM1.

"1:N" means interrupt occurred after "N" PWM1 pulses.

| Р | IR13 | : PIR1 | 0 | PWM1 Interrupt rate |

|---|------|--------|---|---------------------|

| 0 | 0    | 0      | 0 | 1:1                 |

| 0 | 0    | 0      | 1 | 1:2                 |

| 0 | 0    | 1      | 0 | 1:3                 |

| 0 | 0    | 1      | 1 | 1:4                 |

|   |      |        |   |                     |

| 1 | 1    | 0      | 1 | 1:14                |

| 1 | 1    | 1      | 0 | 1:15                |

| 1 | 1    | 1      | 1 | 1:16                |

## 2.1.6.3 T1LA (Timer1 Latch Register)

| Address   | Name | B7 | В6 | B5      | B4           | В3          | B2      | B1 | В0 |

|-----------|------|----|----|---------|--------------|-------------|---------|----|----|

| 12h (r/w) | T1LA |    |    | 8-bit r | eal-time tin | ner/counter | r latch |    |    |

T1LA is a Timer1 pre-set latch buffer, see 2.3 for detail description.

#### 2.1.6.4 T1CNT (Timer1 Counter Register)

|         |       |    | 4000 |          |              |            |       |    |    |

|---------|-------|----|------|----------|--------------|------------|-------|----|----|

| Address | Name  | B7 | B6   | B5       | B4           | В3         | B2    | B1 | B0 |

| 2Bh (r) | T1CNT |    |      | 8-bit re | eal-time tim | er/counter | Count |    | 7  |

T1CNT is a Timer1 real-time counter, this register is only read, see 2.3 for detail description.

## 2.1.7 TMR2: 8-bit Timer & PWM2 Duty

The Timer2 is an 8-bit down count timer/counter which includes counter register (T2CNT), and latch register (T2LA). Please refer to 2.3 for detail Timer description.

The Timer2 can also be PWM2 and controlled by the register PWM2CON. Please refer to 2.4 for detail PWM description.

## 2.1.7.1 T2CON (Timer2 Control Register)

| Address   | Name  | В7   | В6 | B5    | B4    | В3    | B2    | B1    | B0    |

|-----------|-------|------|----|-------|-------|-------|-------|-------|-------|

| 13h (r/w) | T2CON | T2EN | -  | T2SO1 | T2SO0 | T2EDG | T2PS2 | T2PS1 | T2PS0 |

Legend: - = unimplemented, read as '0'.

T2EN: TMR2 Enable/Disable

= 1, TMR2 (PWM2) Enable. = 0, TMR2 (PWM2) Disable.

T2SO1:T2SO0: TMR2 clock source selection

| T2SO1 | T2SO0 | TMR2 clock source         |

|-------|-------|---------------------------|

| 0     | 0     | TMCKI(IOA2)               |

| 0     | 1     | Crystal mode OSCI or LIRC |

| 1     | 0     | Internal 8MHz RC or ERC   |

| 1     | 1     | 8MHz IRCx2                |

Note: Please refer 2.3 for detail description.

**T2EDG**: TMR2 clock edge selection. This bit works only when external clock source TMCKI (IOA2) selected.

- = 1, TMR2 decreased while external clock H→L (Falling edge).

- = 0, TMR2 decreased while external clock L→H (Rising edge).

T2PS2:T2PS0: TMR2 Prescaler selection

|   | T2P | S2 : T2 | PS0 | TMR2 Prescal rate |

|---|-----|---------|-----|-------------------|

|   | 0   | 0       | 0   | 1:1               |

|   | 0   | 0       | 1   | 1:2               |

|   | 0   | 1       | 0   | 1:4               |

|   | 0   | 1       | 1   | 1:8               |

|   | 1   | 0       | 0   | 1:16              |

|   | 1   | 0       | 1   | 1:32              |

| 1 | 1   | 1       | 0   | 1:64              |

|   | 1   | 1       | 1   | 1:128             |

## 2.1.7.2 PWM2CON (PWM2 Control Register)

| Address   | Name    | B7    | B6    | B5    | B4 | В3    | B2    | B1    | B0    |

|-----------|---------|-------|-------|-------|----|-------|-------|-------|-------|

| 14h (r/w) | PWM2CON | T2MOD | PWM2S | EPWM2 | -  | PIR23 | PIR22 | PIR21 | PIR20 |

Legend: - = unimplemented, read as '0'.

**T2MOD**: TMR2 operation mode select bit.

= 1, The TMR2 in PWM mode operation.

= 0, The TMR2 in Timer mode operation.

PWM2S: Initial State of PWM2 output duty.

= 1, Set the initial state to L, change to H when TMR2 duty underflow.

= 0, Set the initial state to H, change to L when TMR2 duty underflow.

**EPWM2**: Extension PWM mode selection

= 1, PWM2 is Extension PWM mode.

= 0, PWM2 is normal PWM mode.

Note: Please refer to 2.4 for detail PWM description.

PIR23:PIR20: Interrupt Event Rate of PWM2.

"1:N" means interrupt occurred after "N" PWM2 pulses.

| Р | IR23 | : PIR2 | 20 | PWM2 Interrupt rate |

|---|------|--------|----|---------------------|

| 0 | 0    | 0      | 0  | 1:1                 |

| 0 | 0    | 0      | 1  | 1:2                 |

| 0 | 0    | 1      | 0  | 1:3                 |

| 0 | 0    | 1      | 1  | 1:4                 |

|   |      |        |    |                     |

| 1 | 1    | 0      | 1  | 1:14                |

| 1 | 1    | 1      | 0  | 1:15                |

| 1 | 1    | 1      | 1  | 1:16                |

## 2.1.7.3 T2LA (Timer2 Latch Register)

| Address   | Name | B7 | В6 | B5      | B4           | В3          | B2    | B1 | В0 |

|-----------|------|----|----|---------|--------------|-------------|-------|----|----|

| 15h (r/w) | T2LA |    |    | 8-bit r | eal-time tir | ner/counter | latch |    |    |

T2LA is a Timer2 pre-set latch buffer, see 2.3 for detail description.

#### 2.1.7.4 T2CNT (Timer2 Counter Register)

| Address | Name  | B7 | B6 | B5       | B4           | В3         | B2    | B1 | В0 |

|---------|-------|----|----|----------|--------------|------------|-------|----|----|

| 2Ch (r) | T2CNT |    |    | 8-bit re | eal-time tim | er/counter | Count |    |    |

T2CNT is a Timer2 real-time counter, this register is only read, see 2.3 for detail description.

#### 2.1.8 TMR3: 8-bit Timer

The Timer3 is an 8-bit down count timer/counter which includes counter register (T3CNT), and latch register (T3LA). Please refer to 2.3 for detail Timer description.

#### 2.1.8.1 T3CON (Timer3 Control Register)

| Address   | Name  | В7   | B6     | B5    | B4    | В3    | B2    | B1    | B0    |

|-----------|-------|------|--------|-------|-------|-------|-------|-------|-------|

| 16h (r/w) | T3CON | T3EN | T3LOAD | T3SO1 | T3SO0 | T3EDG | T3PS2 | T3PS1 | T3PS0 |

**T3EN**: TMR3 Enable/Disable = 1, TMR3 Enable. = 0, TMR3 Disable.

T3LOAD: Enable/Disable Latch Buffer automatically load to counter register while writing to latch register

- = 1, Enable TMR3 latch buffer automatically load to counter register while writing to latch register.

- = 0, Disable TMR3 latch buffer automatically load to counter register while writing to latch register.

Note: This bit is only affected after latch register written. When the timer underflows, the latch register data will automatically load into counter register.

T3SO1:T3SO0: TMR3 clock source selection

| T3SO1 | T3SO0 | TMR3 clock source         |

|-------|-------|---------------------------|

| 0     | 0     | TMCKI(IOA2)               |

| 0     | 1     | Crystal mode OSCI or LIRC |

| 1     | 0     | Internal 8MHz RC or ERC   |

| 1     | 1     | Not function, don't use.  |

Note: Please refer 2.3 for detail description.

T3EDG: TMR3 clock edge selection. This bit works only when external clock source TMCKI (IOA2) selected.

- = 1, TMR3 decreased while external clock H→L (Falling edge).

- = 0, TMR3 decreased while external clock L→H (Rising edge).

## 2.1.8.2 T3LA (Timer3 Latch Register)

| Address   | Name | B7 | B6 | B5      | B4           | В3          | B2    | B1 | B0 |

|-----------|------|----|----|---------|--------------|-------------|-------|----|----|

| 17h (r/w) | T3LA |    |    | 8-bit r | eal-time tin | ner/counter | latch |    |    |

T3LA is a Timer3 pre-set latch buffer, see 2.3 for detail description.

#### 2.1.8.3 T3CNT (Timer3 Counter Register)

| Address | Name  | B7 | B6 | B5       | B4           | В3          | B2    | B1 | B0 |

|---------|-------|----|----|----------|--------------|-------------|-------|----|----|

| 18h (r) | T3CNT |    |    | 8-bit re | eal-time tim | ner/counter | Count |    |    |

T3CNT is a Timer3 real-time counter, this register is only read, see 2.3 for detail description.

T3PS2:T3PS0: TMR3 Prescaler selection

| T3P | S2 : T3 | PS0 | TMR3 Prescal rate |

|-----|---------|-----|-------------------|

| 0   | 0       | 0   | 1:1               |

| 0   | 0       | 1   | 1:2               |

| 0   | 1       | 0   | 1:4               |

| 0   | 1       | 1   | 1:8               |

| 1   | 0       | 0   | 1:16              |

| 1   | 0       | 1   | 1:32              |

| 1   | 1       | 0   | 1:64              |

| 1   | 1       | 1   | 1:128             |

#### 2.1.9 INTEN (Interrupt Mask Register)

| Address   | Name  | В7  | В6    | B5   | B4    | B3 | B2   | B1     | B0     |

|-----------|-------|-----|-------|------|-------|----|------|--------|--------|

| 19h (r/w) | INTEN | GIE | ADCIE | PAIE | COMIE | 1  | T3IE | T2P2IE | T1P1IE |

Legend: - = unimplemented, read as '0'.

GIE: Global interrupt enable bit.

= 1, Enable all un-masked interrupts.

= 0, Disable all interrupts.

Note: When an interrupt event occurred with the GIE bit and its corresponding interrupt enable bits are set, the GIE bit will be cleared by hardware to disable any further interrupts. The RETFIE instruction will exit the interrupt routine and set the GIE bit to re-enable interrupt.

ADCIE: ADC conversion completed interrupt enable bit.

= 1, Enable interrupt.

= 0, Disable interrupt.

PAIE: PORTA interrupt enable

= 1, Enable interrupt.

= 0, Disable interrupt.

**COMIE**: LCD COM interrupt enable bit.

= 1, Enable interrupt.

= 0, Disable interrupt.

T3IE: Timer3 underflow interrupt enable bit.

= 1, Enable interrupt.

= 0, Disable interrupt.

**T2P2IE**: Timer2 / PWM2 underflow interrupt enable bit.

= 1, Enable interrupt.

= 0, Disable interrupt.

T1P1IE: Timer1 / PWM1 underflow interrupt enable bit.

= 1, Enable interrupt.

= 0, Disable interrupt.

#### 2.1.10 INTFLAG (Interrupt Status Register)

| Address   | Name    | B7 | В6    | B5   | B4    | В3 | B2   | B1     | B0     |

|-----------|---------|----|-------|------|-------|----|------|--------|--------|

| 1Ah (r/w) | INTFLAG | -  | ADCIF | PAIF | COMIF | -  | T3IF | T2P2IF | T1P1IF |

Legend: - = unimplemented, read as '0'.

ADCIF: ADC Interrupt flag. Set when ADC conversion is completed, reset by software.

PAIF: Port A <7:0> Interrupt flag. Set when pin changed on selected I/O by register INTPA, reset by software.

**COMIF**: LCD COM interrupt flag. Set when LCD clock overflows, and reset by software.

T3IF: TMR3 interrupt flag. Set when TMR3 underflows, and reset by software.

**T2P2IF**: TMR2 or PWM2 interrupt flag. Set when TMR2 underflows or PWM2 pulse counts to selected

interrupt rate, and reset by software.

T1P1IF: TMR1 or PWM1 interrupt flag. Set when TMR1 underflows or PWM1 pulse counts to selected

interrupt rate, and reset by software.

Note: BCR instruction is not recommended for Clear interrupt flag (INTFLAG register).

## 2.1.11 ADCON1 (AD converter Control Register1)

| Address   | Name   | В7    | В6 | B5 | B4 | B3 | B2    | B1    | B0    |

|-----------|--------|-------|----|----|----|----|-------|-------|-------|

| 1Bh (r/w) | ADCON1 | ADCEN | -  | -  |    | -  | CHSL2 | CHSL1 | CHSL0 |

Legend: - = unimplemented, read as '0'.

ADCEN: ADC enable/disable setting

= 1, Enable.= 0, Disable.

Note: This bit should be set by software and would be reset by hardware after the ADC end of

conversion.

CHSL2:CHSL0: ADC input channel select

| CHSL2 | CHSL1 | CHSL0 | Input channel       |

|-------|-------|-------|---------------------|

| 0     | 0     | 0     | Channel 0, IOA0 pin |

| 0     | 0     | 1     | Channel 1, IOA1 pin |

| 0     | 1     | 0     | Channel 2, IOA2 pin |

| 0     | 1     | 1     | Channel 3, IOA3 pin |

| 1     | 0     | 0     | Channel 4, IOA4 pin |

| 1     | 0     | 1     | Channel 5, IOB4 pin |

| 1     | 1     | 0     | Channel 6, IOB5 pin |

| 1     | 1     | 1     | Channel 7, IOC7 pin |

#### 2.1.12 ADCON2 (AD converter Control Register2)

| Address   | Name   | B7 | B6 | B5 | B4 | В3 | B2 | B1     | B0     |

|-----------|--------|----|----|----|----|----|----|--------|--------|

| 1Ch (r/w) | ADCON2 | -  | -  | -  | -  | -  | -  | CLKSL1 | CLKSL0 |

Legend: - = unimplemented, read as '0'.

CLKSL1:CLKSL0: ADC Conversion clock source select bits.

| CKSL1 | CKSL0 | Conversion clock                                  |

|-------|-------|---------------------------------------------------|

| 0     | 0     | System clock / 2 (fastest result, lowest quality) |

| 0     | 1     | System clock / 8                                  |

| 1     | 0     | System clock / 32                                 |

| 1     | 1     | System clock / 128 (slowest result, best quality) |

Note: This clock is used to control the conversion precision and speed. The precision will be dropped off if faster conversion rate been used. The lowest conversion rate would be recommended in order to acquire most accurate data.

#### 2.1.13 ADCON3 (AD converter Control Register3)

| Add | ress  | Name   | В7 | В6 | B5 | B4 | В3     | B2     | B1     | В0     |

|-----|-------|--------|----|----|----|----|--------|--------|--------|--------|

| 1Dh | (r/w) | ADCON3 | -  | -  | -  | -  | ANISL3 | ANISL2 | ANISL1 | ANISL0 |

Legend: - = unimplemented, read as '0'.

ANISL3:ANISL0: Analog input select bits.

| ANISL3 | ANISL2 | ANISL1 | ANISL0                  | Analog input selection          |

|--------|--------|--------|-------------------------|---------------------------------|

| 0      | 0      | 0      | 0                       | All the ports are digital input |

| 0      | 0      | 0      | 1                       | AN0                             |

| 0      | 0      | 1      | 0                       | AN1                             |

| 0      | 0      | 1      | 1                       | AN2                             |

| 0      | 1      | 0      | 0                       | AN3                             |

| 0      | 1      | 0      | 1                       | AN4                             |

| 0      | 1      | 1      | 0                       | AN5                             |

| 0      | 7      | 1      | 1                       | AN6                             |

| 1      | 0      | 0      | 0                       | AN7                             |

|        | Otl    | ner    | No function, don't use. |                                 |

Note: To minimize power consumption, all the I/O pins should be carefully managed before entering sleep mode.

## 2.1.14 ADDATL, ADDATH (AD conversion data high-byte and low-byte Register)

| Address | Name   | B7 | B6 | B5 | B4 | В3 | B2 | B1  | B0 |

|---------|--------|----|----|----|----|----|----|-----|----|

| 1Eh (r) | ADDATL | D1 | D0 | -  | -  | -  | -  | - , |    |

| 1Fh (r) | ADDATH | D9 | D8 | D7 | D6 | D5 | D4 | D3  | D2 |

Legend: - = unimplemented, read as '0'.

The ADDATL and ADDATH registers is ADC conversion result. When ADC conversion is completed, the result is loaded into ADDATL and ADDATH, the ADCEN bit will be cleared, and the ADCIF bit will be set (if ADCIE are set).

#### 2.1.15 Software Controlled LCD Module

| Address   | Name    | B7    | В6 | B5 | B4     | В3     | B2     | B1     | В0     |

|-----------|---------|-------|----|----|--------|--------|--------|--------|--------|

| 20h (r/w) | COMCON1 | -     | -  | -  | -      | СОМЗЕ  | COM2E  | COM1E  | COM0E  |

| 21h (r/w) | COMCON2 | COMEN | -  | -  | COMIS1 | COMIS0 | COMCK2 | COMCK1 | COMCK0 |

Legend: - = unimplemented, read as '0'.

The pins IOB0~IOB3 on port B can be used as COM lines to drive an external LCD panels. To implement this function, the COMCON1 and COMCON2 registers used to setup the correct bias voltage on these pins.

## 2.1.15.1 COMCON1 (Software LCD COM Control Register1)

COM0E: IOB0 / COM0 Selection bit.

= 1. IOB0 is normal I/O.

= 0, IOB0 is COM0, 1/2 VDD output (in LCD mode).

COM1E: IOB1 / COM1 Selection bit.

= 1, IOB1 is normal I/O.

= 0, IOB1 is COM1, 1/2 VDD output (in LCD mode).

COM2E: IOB2 / COM2 Selection bit.

= 1, IOB2 is normal I/O.

= 0, IOB2 is COM2, 1/2 VDD output (in LCD mode).

COM3E: IOB3 / COM3 Selection bit.

= 1, IOB3 is normal I/O.

= 0, IOB3 is COM3, 1/2 VDD output (in LCD mode).

#### 2.1.15.2 COMCON2 (Software LCD COM Control Register2)

| Address   | Name    | B7    | B6 | B5 | B4     | В3     | B2     | B1     | B0     |

|-----------|---------|-------|----|----|--------|--------|--------|--------|--------|

| 21h (r/w) | COMCON2 | COMEN | -  | -  | COMIS1 | COMIS0 | COMCK2 | COMCK1 | COMCK0 |

Legend: - = unimplemented, read as '0'.

**COMEN**: COM module enable/disable bit.

= 1, Enable COM module.

= 0, Disable COM module.

**COMIS1:COMIS0**: COMn operating current selection (VDD = 5V).

|   | COMIS1 | COMIS0 | COMn operating current |

|---|--------|--------|------------------------|

|   | 0      | 0      | 25uA                   |

| 1 | 0      | 1      | 50uA                   |

|   | 1      | 0      | 100uA                  |

|   | 1      | 1      | 200uA                  |

**COMCK2:COMCK0**: COMn turn-on time selection (interrupt).

|     |           | , , , , , | 1 -7                 |

|-----|-----------|-----------|----------------------|

| COM | CK2 : CON | /ICK0     | COMn Clock prescaler |

| 0   | 0         | 0         | System clock / 1024  |

| 0   | 0         | 1         | System clock / 2048  |

| 0   | 1         | 0         | System clock / 4096  |

| 0   | 1         | 1         | System clock / 8192  |

| 1   | 0         | 0         | System clock / 4     |

| 1   | 0         | 1         | System clock / 8     |

| 1   | 1         | 0         | System clock / 16    |

| 1   | 1         | 1         | System clock / 32    |

#### 2.1.16 SYSCLK (System Clock Control Register)

| Address   | Name   | B7   | В6 | B5 | B4 | B3 | B2    | B1    | В0     |

|-----------|--------|------|----|----|----|----|-------|-------|--------|

| 22h (r/w) | SYSCLK | CLKS | -  | -  | -  | 1  | A - A | IRCPD | ECLKPD |

Legend: - = unimplemented, read as '0'.

The FM8P756 could be operated either dual or single clock system selected by configuration words. Please refer to 2.14 for detail configuration selection description. This register is used to control the switch between different system clocks and power-down function of those clocks.

**CLKS**: System Clock Selection (only valid in dual clock mode)

- = 1, System Clock is External OSC/LIRC.

- = 0, System Clock is Internal 8MHz or 4MHz RC.

IRCPD: Internal RC Power down Control (only valid in dual clock mode)

- = 1, Internal 8MHz or 4MHz RC Power Down.

- = 0, Internal 8MHz or 4MHz RC Power ON.

Note: Make sure the system clock been switch to external OSC/RC before power down internal 8MHz or 4MHz RC.

ECLKPD: External clock (OSC/LIRC) Power down Control (only valid in dual clock mode)

- = 1, External OSC/LIRC Power Down.

- = 0, External OSC/LIRC Power ON.

Note: Make sure the system clock been switch to internal 8MHz or 4MHz RC before power down external OSC/LIRC.

#### 2.1.17 CLOCON (Clock output Control Register)

| Address   | Name   | B7    | B6   | B5    | B4   | В3   | B2     | B1     | B0     |

|-----------|--------|-------|------|-------|------|------|--------|--------|--------|

| 23h (r/w) | CLOCON | CLOEN | 1.47 | EXCLK | DINV | DUTY | CLOPS2 | CLOPS1 | CLOPS0 |

Legend: - = unimplemented, read as '0'.

The FM8P756 provides one system clock output with prescaler function.

**CLOEN**: System Clock output function selection

- = 1, IOA5 is Clock Output.

- = 0, IOA5 is normal I/O.

**EXCLK**: External clock (IOA2/TMCKI) function selection

- = 1, IOA2 is external clock input of timer.

- = 0, IOA2 is normal I/O.

**DINV**: System Clock output Duty invert selection bit.

If DUTY bit = 1:

= 1, 1/4 duty output

= 0, keep 3/4 duty output

else: Ignore.

**DUTY**: System Clock output duty selection bit.

= 1, 3/4 duty output.

= 0, 1/2 duty output.

CLOPS2:CLOPS0: Clock Output prescaler setting

| 22 . CL | ODCO                  | Clock Output prescaler ratio                    |              |  |  |  |  |

|---------|-----------------------|-------------------------------------------------|--------------|--|--|--|--|

| 52 . CL | UP30                  | DUTY = 0                                        | DUTY = 1     |  |  |  |  |

| 0       | 0                     | 1:1                                             | 1:2          |  |  |  |  |

| 0       | 1                     | 1:2                                             | 1:4          |  |  |  |  |

| 1       | 0                     | 1:4                                             | 1:8          |  |  |  |  |

| 1       | 1                     | 1:8                                             | 1:16         |  |  |  |  |

| 0       | 0                     | 1:16                                            | 1:32         |  |  |  |  |

| 0       | 1                     | 1:32                                            | 1:64         |  |  |  |  |

| Other   |                       | No function                                     | , don't use. |  |  |  |  |

|         | 0<br>0<br>1<br>1<br>0 | 0 0<br>0 1<br>1 0<br>1 1<br>0 0<br>0 1<br>Other | DUTY = 0  0  |  |  |  |  |

#### 2.1.18 APHCON, BPHCON, CPHCON (Port A, Port B, Port C Pull-high Control Register)

| Address   | Name   | В7   | В6   | B5   | B4   | В3   | B2   | B1   | B0   |

|-----------|--------|------|------|------|------|------|------|------|------|

| 25h (r/w) | APHCON | 1    | PHA6 | PHA5 | PHA4 | PHA3 | PHA2 | PHA1 | PHA0 |

| 26h (r/w) | BPHCON | -    | -    | PHB5 | PHB4 | PHB3 | PHB2 | PHB1 | PHB0 |

| 27h (r/w) | CPHCON | PHC7 | PHC6 | PHC5 | PHC4 | PHC3 | PHC2 | PHC1 | PHC0 |

Legend: - = unimplemented, read as '0'.

Those registers are used to setup pull-high resistor enable/disable of each IO pins.

- = 1, Pull-high resistor enable.

- = 0, Pull-high resistor disable.

### 2.1.19 INTPA (Port A Interrupt / Wakeup control Register)

| Address   | Name  | B7     | B6     | B5     | B4     | B3     | B2     | B1     | B0     |

|-----------|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| 28h (r/w) | INTPA | PA7IEN | PA6IEN | PA5IEN | PA4IEN | PA3IEN | PA2IEN | PA1IEN | PA0IEN |

This register is used to enable/disable the interrupt/wakeup function of Port A. Please refer to 2.8.1 for detail description of External Interrupt and Wake up function.

- = 1, Selected IO interrupt/wakeup enable.

- = 0, Selected IO interrupt/wakeup disable.

## 2.1.20 WDTCON (Watchdog Timer Control Register)

| Address   | Name   | B7    | В6    | B5     | B4 | В3 | B2     | B1     | В0     |

|-----------|--------|-------|-------|--------|----|----|--------|--------|--------|

| 29h (r/w) | WDTCON | WDTEN | I_WDT | I_TWDT | -  | -  | WDTPS2 | WDTPS1 | WDTPS0 |

Legend: - = unimplemented, read as '0'.

The FM8P756 builds in a watchdog timer with two different modes, normal watchdog reset and internal watchdog wakeup. The watchdog timer is controlled by this register (WDTCON). Please refer to 2.6 for detail Watchdog Timer description.

**WDTEN**: Watchdog Timer Enable/ Disable.

= 1, WDT Enable.

= 0, WDT disable.

I\_WDT: Internal Watchdog Wakeup mode selection.

= 1, Internal Watchdog Wakeup Enable.

= 0, Internal Watchdog Wakeup Disable.

**I\_TWDT**: Watchdog Timer Stable time required when operating in I\_WDT mode (I\_WDT bit = 1).

= 1, 1.25ms.

= 0, 5ms (default).

WDTPS2:WDTPS0: Watchdog timer prescaler setting

| WDT | PS2 : WD | TPS0 | WDT prescaler rate |

|-----|----------|------|--------------------|

| 0   | 0        | 0    | 1:1 (20mS)         |

| 0   | 0        | 1    | 1:2 (40mS)         |

| 0   | 1        | 0    | 1:4 (80mS)         |

| 0   | 1        | 1    | 1:8 (160mS)        |

| 1   | 0        | 0    | 1:16 (320mS)       |

| 1   | 0        | 1    | 1:32 (640mS)       |

| 1   | 1        | 0    | 1:64 (1.28S)       |

| 1   | 1        | 1    | 1:128 (2.56S)      |

## 2.1.21 TAB\_BNK (Table Look-up function Bank select Register)

| Address   | Name   | B7 | B6 | B5 | B4 | В3 | B2   | B1   | B0   |

|-----------|--------|----|----|----|----|----|------|------|------|

| 2Ah (r/w) | TB_BNK | -  | -  | -  | -  | -  | BNK2 | BNK1 | BNK0 |

Legend: - = unimplemented, read as '0'.

The FM8P756 provides a table look-up function and the bank selection of ROM data is controlled by this register. Please refer to 2.10 for detail operation of look-up table function.

BNK2:BNK0: Page selection of Look-up table

| BNK2 : BNK0 |   |   | BANK select                  |

|-------------|---|---|------------------------------|

| 0           | 0 | 0 | 000 XXXX XXXX Table location |

| 0           | 0 | 1 | 001 XXXX XXXX Table location |

| 0           | 1 | 0 | 010 XXXX XXXX Table location |

|             |   |   |                              |

| 1           | 1 | 1 | 111 XXXX XXXX Table location |

## 2.1.22 ACC (Accumulator)

| Address   | Name | B7 | B6          | B5 | B4 | В3 | B2 | B1 | B0 |

|-----------|------|----|-------------|----|----|----|----|----|----|

| N/A (r/w) | ACC  |    | Accumulator |    |    |    |    |    |    |

Accumulator is an internal data transfer, or instruction operand holding. It cannot be addressed.

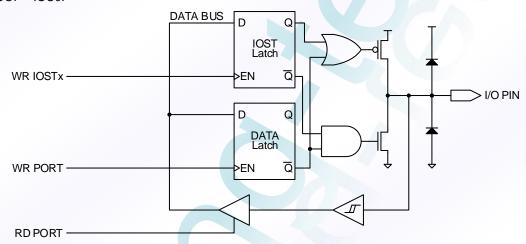

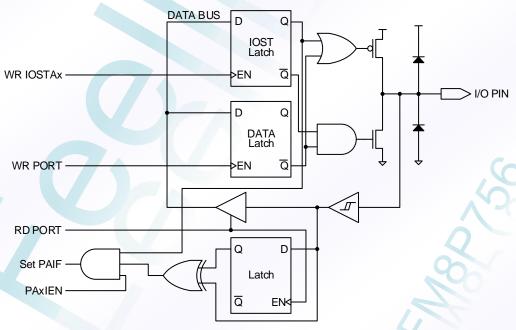

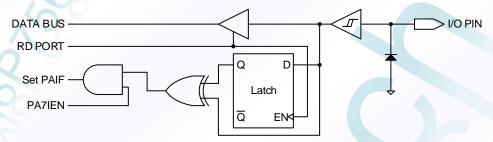

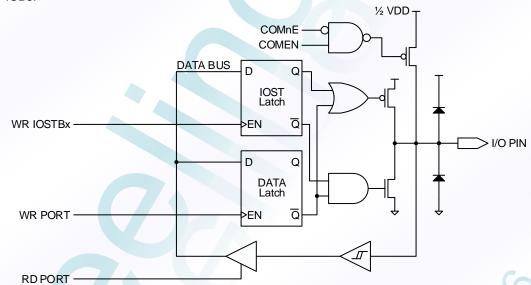

#### 2.2 I/O Ports

There are totally 21 bi-directional tri-state I/O ports and one (IOA7) input only. All I/O pins (IOA<6:0>, IOB<5:0> and IOC<7:0>) have specified data direction control registers (IOSTA, IOSTB and IOSTC) which can configure these pins as output or input.

All the IO pins can also enable or disable a weak internal pull-high by setting APHCON, BPHCON and CPHCON. This weak pull-high will be automatically turned off when the pin is configured as an output pin.

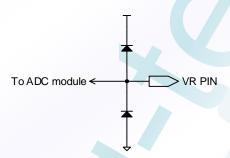

VR pin is reference voltage input pin of the ADC module, this pin does not have I/O function.

The Configuration Words can set IOA7 to Reset functions. When acting as Reset functions the pins will read as "0" during port read.

Please note, IOB2 and VR voltage on these pins must not exceed VDD, otherwise it will cause the pin breakdown.

#### Figure 2.3: Block Diagram of I/O Pins

IOB5, IOC7 ~ IOC0:

Pull-high / ADC / LCD are not shown in this figure

IOA6 ~ IOA0:

Pull-high/ADC/OSC are not shown in this figure

IOA7:

Voltage on this pin must not exceed VDD.

VR:

Voltage on this pin must not exceed VDD.

Pull-high is not shown in this figure

## 2.3 Timer/Event Counter (TMR1, TMR2, TMR3)

The FM8P756 contains three 8-bit down-counts Timers/Counters. All these timers have auto reload function, TMR1 and TMR2 can be to perform PWM function.

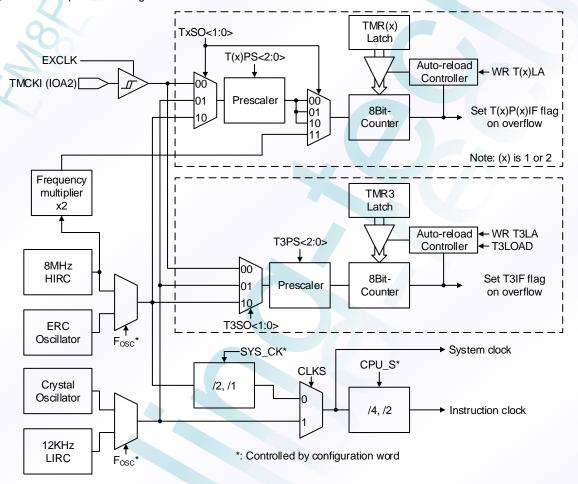

Figure 2.4: Simple Block Diagram of the Timer 1 ~ 3

#### 2.3.1 Clock Source

Timer1 and Timer2 has four clock sources can be selected, Timer3 has three clock sources can be selected.

#### 2.3.1.1 TMCKI (IOA2)

The event counter mode would be activated when the source of TMCKI (IOA2) used. At this mode, the rising/falling edge of the event could also be selected separately.

## 2.3.1.2 Crystal or External RC Oscillator

In this mode, the timer clock source from Crystal / ERC oscillator module. Oscillator module operating modes are defined by the Fosc bit in the configuration word.

Please note that, in this case, the clock input to the timer in two paths, and therefore will have the following composition:

Table 2.1: Selection of Timer 1 ~ 3 Clock source

| Fosc mode of Configuration word | Timer 1 ~ 3 Clock                       |

|---------------------------------|-----------------------------------------|

| HIRC                            | Only HIRC 8 MHz                         |

| HIRC & LIRC                     | HIRC 8 MHz or LIRC 12 KHz               |

| HIRC & XT or HIRC & LF          | HIRC 8 MHz or Crystal oscillator source |

| ERC                             | Only External RC oscillator source      |

| LIRC                            | Only LIRC 12 KHz                        |

| XT or LF                        | Only Crystal oscillator source          |

Since the oscillator module is controlled by the Fosc bit, if need a combination of multiple clock sources, the need to carefully choose the configuration word Fosc operating mode.

#### 2.3.1.3 Internal 8MHz RC Oscillator

In this mode, timer clock source from internal 8MHz RC oscillator. Please note that this clock source can only be used in the following modes:

Table 2.2: Selection of 8 MHz HIRC clock source

| Fosc mode of Configuration word | Timer 1 ~ 3 Clock          |

|---------------------------------|----------------------------|

| HIRC                            |                            |

| HIRC & LIRC                     | HIRC 8 MHz can be selected |

| HIRC & XT or HIRC & LF          |                            |

| ERC or LIRC or XT or LF         | HIRC 8 MHz are shutdown    |

#### 2.3.1.4 Internal 8MHz RC Oscillator \*2

In this mode, the IRC frequency is multiplied by 2, as the timer clock source, this clock source using the same Opportunity and Table 2.2.

Note: This mode only for Timer1 and Timer2.

## 2.3.2 Prescaler

Each timer contains a 3-bits prescaler which can scale the timer or counter from 1:1 to 1:128.

| TxF | S2 : Tx  | PS0 | TMRx Prescal rate |

|-----|----------|-----|-------------------|

| 0   | 0        | 0   | 1:1               |

| 0   | 0        | 1   | 1:2               |

| 0   | 1        | 0   | 1:4               |

| 0   | <b>1</b> | 1   | 1:8               |

| 1   | 0        | 0   | 1:16              |

| 1   | 0        | 1   | 1:32              |

| 1   | 1        | 0   | 1:64              |

| 1   | 1        | 1   | 1:128             |

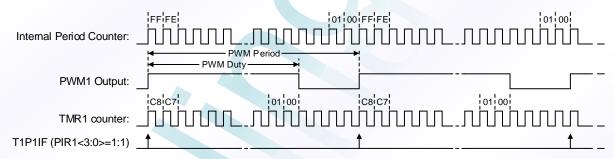

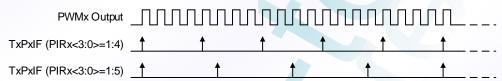

#### 2.4 Pulse Width Modulation (PWM)

FM8P756 provides two PWM output shared with TMR1 and TMR2. When PWM1 or PWM2 selected, TMR1/TMR2 will be the duty of PWM1/PWM2.

PWM1 and PWM2 period is fixed resolution of 8-bits; duty time output a maximum resolution of 8-bits (normal mode) or 6-bits (extended mode).

The PWM outputs are on the IOA4/ADC4/INT4/PWM1, and IOB4/ADC5/PWM2 pins.

The user needs to set the T1MOD bit (PWM1CON<7>) to enable the PWM1 output. When T1MOD bit is set, the IOA4/ADC4/INT4/PWM1 pin is configured as PWM1 output and forced as an output, irrespective of the data direct bit (IOSTA<6>). When the T1MOD is clear, the pin behaves as a I/O pin.

Similarly, the T2MOD bit (PWM2CON<7>) controls the configuration of the IOB4/ADC5/PWM2 pin.

The FM8P756 PWM has two modes of operation; PWM1 and PWM2 have normal mode, and the extension mode, detailed description as follows:

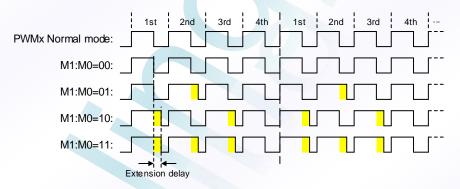

#### 2.4.1 Normal PWM mode

In the Normal PWM mode, it is a general purpose PWM mode; this mode can be used in the PWM1 and PWM2.

The PWM1 period time is fixed; period time can be calculated as follows:

The duty cycle of PWM1 is determined by the 8-bit value T1LA, PWM1 duty time is as follows:

Duty time of PWM1 =

$$(T1LA+1) * TMR1$$

Prescal rate \*  $\frac{1}{Clock}$  source frequency or

$T1LA = \frac{Duty \ time * Clock \ source \ frequency}{TMR1 \ Prescal \ rate}$

PWM1 and PWM2 structure is the same. Therefore, these formulas can be used directly in PWM2.

## **Example 2.2: PWM1 Setting (Normal mode)**

| Address | Code     |                  |                   |                                                 |

|---------|----------|------------------|-------------------|-------------------------------------------------|

| NA      | #include | <8P756.ASH>      |                   |                                                 |

|         |          |                  |                   |                                                 |

|         |          | //Set PWM1 D     | outy              |                                                 |

| n       |          | MOVIA            | 0x32              |                                                 |

| n+1     |          | MOVAR            | T1CON             | ;CLK source is Crystal, Prescaler 1:4           |

|         |          |                  |                   | ;Period time = $256*4*(1/16MHz) = 64uS$         |

| n+2     |          | MOVIA            | 0x80              |                                                 |

| n+3     |          | MOVAR            | PWM1CON           | ;Set to Normal PWM, interrupt rate 1:1          |

| n+4     |          | MOVIA            | 0xC8              |                                                 |

| n+5     |          | MOVAR            | T1LA              | ;Set Duty (0xC8 down count to 0x00)             |

|         |          |                  |                   | ;Duty time = $(0xC8+1)^44^*(1/16MHz) = 50.25uS$ |

| n+6     |          | BSR              | T1CON,T1EN_B      | ;Start PWM1                                     |

|         |          | //Interrupt sett | ing, not required |                                                 |

| n+7     |          | MOVIA            | 0x81              |                                                 |

| n+8     |          | MOVAR            | INTEN             | ;Enable global & PWM1 interrupt                 |

| n+9     |          | MOVIA            | 0x76              | ;Clear interrupt flag                           |

| n+10    |          | MOVAR            | INTFLAG           | ;Clear T1P1IF(PWM1) flag                        |

- Note: 1. The PWM duty (Fosc/255 max) must be smaller than PWM period (Fosc/256). In this example, the frequency of external OSC is approximately 16MHz.

- 2. The PWM duty has built-in controller circuit, user can directly change, and the new value will be automatically loaded to the next cycle.

Figure 2.5: Normal PWM Output Waveform

#### 2.4.2 Extension PWM mode

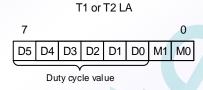

In the extension PWM mode, PWM module will increase the delay to Duty cycle. This mode has three modes, can be select by T1LA <1:0> (PWM1) or T2LA <1:0> (PWM2). Therefore, in the extension mode, duty cycle maximum resolution is 6-bits.

The PWM1 or PWM2 duty cycle is set by T1LA <7:2> or T2LA <7:2>.

This mode can be used in the PWM1 and PWM2.

Figure 2.6: T1 or T2 LA bits allocation in the Extension PWM mode

| M1  | : M0 | Stretched cycle number     |

|-----|------|----------------------------|

| 0 0 |      | None (Same as Normal mode) |

| 0   | 1    | Only 2nd                   |

| 1   | 0    | 1st and 3rd                |

| 1   | 1    | 1st, 2nd and 3rd           |

Figure 2.7: Extension PWM Output Waveform

Extension mode duty time can be calculated as follows:

Duty time of PWM1 =

$$(T1LA+1) * TMR1$$

Prescal rate \*  $\frac{1}{Clock}$  source frequency or

$$T1LA = \frac{Duty time * Clock source frequency}{TMR1 Prescal rate}$$

Extension delay time is as follows:

Extension delay time = TMR1 Prescal rate \*

$$\frac{1}{\text{Clock source frequency}}$$

PWM1 and PWM2 structure is the same. Therefore, these formulas can be used directly in PWM2.

## **Example 2.3: PWM1 Setting (Extension mode)**

| Address | Code     |                  |                   |                                               |

|---------|----------|------------------|-------------------|-----------------------------------------------|

| NA      | #include | <8P756.ASH>      | •                 |                                               |

|         |          |                  |                   |                                               |

|         |          | //Set PWM1 D     | uty               |                                               |

| n       |          | MOVIA            | 0x32              |                                               |

| n+1     |          | MOVAR            | T1CON             | ;CLK source is Crystal, Prescaler 1:4         |

|         |          |                  |                   | ;Period time = $256*4*(1/16MHz) = 64uS$       |

| n+2     |          | MOVIA            | 0xA0              |                                               |

| n+3     |          | MOVAR            | PWM1CON           | ;Set to Extension PWM, interrupt rate 1:1     |

| n+4     |          | MOVIA            | 0xC9              |                                               |

| n+5     |          | MOVAR            | T1LA              | ;Set Duty (0x32 down count to 0x00)           |

|         |          |                  |                   | ;Duty time = $(0x32+1)*4*(1/16MHz) = 12.75uS$ |

| n+6     |          | BSR              | T1CON,T1EN_B      | ;Start PWM1                                   |

|         |          | //Interrupt sett | ing, not required |                                               |

| n+7     |          | MOVIA            | 0x81              |                                               |

| n+8     |          | MOVAR            | INTEN             | ;Enable global & PWM1 interrupt               |

| n+9     |          | MOVIA            | 0x76              | ;Clear interrupt flag                         |

| n+10    |          | MOVAR            | INTFLAG           | ;Clear T1P1IF(PWM1) flag                      |

- Note: 1. The PWM duty (Fosc/255 max) must be smaller than PWM period (Fosc/256). In this example, the frequency of external OSC is approximately 16MHz.

- 2. The PWM duty has built-in controller circuit, user can directly change, and the new value will be automatically loaded to the next cycle.

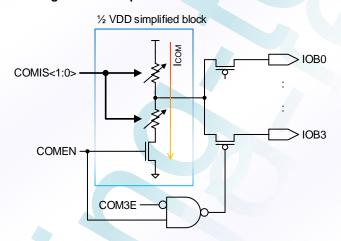

## 2.5 Software controlled LCD

The FM8P756 have the software controlled LCD driving external LCD panels. The common pins for LCD driving, COM0~COM3, are pin shared with certain pin on IOB0~IOB3 port. The LCD signals (COM and SEG) are generated using the application program.

The LCD driver function is controlled using the COMCON1 and COMCON2 to controlling the overall on/off function, Also controls the bias voltage setup function. This enables the LCD COM driver to generate the necessary VDD/2 voltage levels for LCD 1/2 bias operations.

#### 2.5.1 1/2 VDD Bias

The chip provides 1/2 VDD bias in IOB0  $\sim$  IOB3. User needs to set the COMIS<1:0> bits set I<sub>COM</sub> current. To make the I/O Output 1/2 VDD bias, must be setting COMEN bit to "1".

When COMEN bit is "1", COM0E direct control IOB0 pin, users only need to control IOB0 and COM0E two bits, IOSTB0 does not affect the status of IOB0.

Similarly, COM3E ~ COM1E bits control the corresponding IOB3 ~ IOB1 pin.

Figure 2.8: Simplified Block Diagram of COM pins

IOB0~IOB2 some circuit are not shown in this figure

Table 2.3: COM 3~0 Pin Function

| COMEN | COMnE | Pin Function | IOB3 ~ 0 |  |  |

|-------|-------|--------------|----------|--|--|

| 0     | X     | I/O          | 0 or 1   |  |  |

| 1     | 0     | COMn         | 1/2 VDD  |  |  |

| 1     | 1     | I/O          | 0 or 1   |  |  |

Note: In the case of unused, the user must turn-off 1/2 VDD bias (setting COMEN bit to "0"), reducing current consumption.

#### 2.5.2 COMCK

The chip provides one set of dividers can be set, the user can use this divider to generate an interrupt triggers signal to generate LCD waveform by software program. If this interrupt source used in another application, COMEN bit must be set to "1".

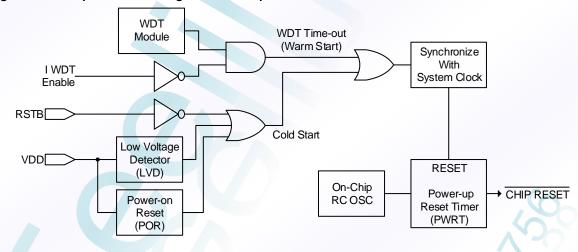

## 2.6 Watch Dog Timer (WDT)

The Watchdog Timer (WDT) is a free running on-chip RC oscillator which does not require any external components. So the WDT will still run even if the clock on the OSCI and OSCO pins is turned off, such as in SLEEP mode.

The WDT can be disabled by clearing the control bit WDTEN (WDTCON <7>) to "0".

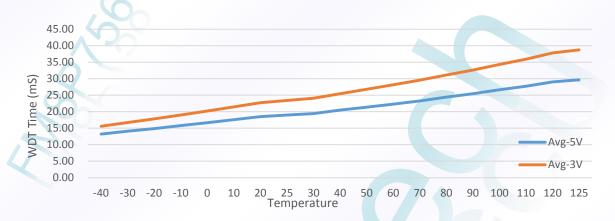

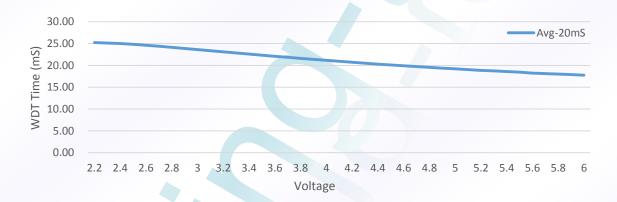

The WDT has a typical time-out period of 20 mS (without prescaler). This period of this timer may be variant slightly because of temperature, voltage, and process variation. If a longer time-out period is desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT controlled by the WDTCON register <2:0>. Thus, the longest time-out period is approximately 2.56 seconds.

The CLRWDT instruction clears the WDT and prevents it from timing out and generating a device reset.

The SLEEP instruction also resets the WDT. This gives the maximum SLEEP time before a WDT Wake-up Reset.

There are two type of watchdog timer mode could be selected by I\_WDT (WDTCON <6>). When I\_WDT bit disable, normal watchdog timer reset is selected. During normal operation or in SLEEP mode, a WDT time-out will cause the device reset and the  $\overline{\text{TO}}$  bit (STATUS<4>) will be cleared.

If I\_WDT bit enabled, the internal watchdog timer wakeup will be used. The system wakeups from sleep, then jumps into interrupt vector with external interrupt request PAIF (INTFLAG<5>) and continues from next instruction instead of triggering a reset event. There is a stabilization time required for internal watchdog wakeup could be selected by I\_TWDT (WDTCON<5>). The default value of this stabilization timer is 5ms.

**Example 2.4: Internal Watchdog Wakeup**

| Address | Code                                                |  |

|---------|-----------------------------------------------------|--|

| NA      | #include <8P756.ASH>                                |  |

| 0x003   | A MOT Melicine                                      |  |

| 0x004   | (Backup status code) 1. WDT Wakeup                  |  |

|         | ;User WDT Wakeup ISR code                           |  |

|         | MOVIA 0x57                                          |  |

|         | MOVAR INTFLAG \ ;Clear PAIF flag <sup>(Note1)</sup> |  |

|         | (Restore status code)                               |  |

|         | / RETFIE                                            |  |

|         | 2. Return from ISR                                  |  |

| n       | MOVIA 0xA0                                          |  |

| n+1     | MOVAR INTEN ;Enable global & Port A interrupt       |  |

| n+2     | CLRWDT                                              |  |

| n+3     | MOVIA 0xE7                                          |  |

| n+4     | MOVAR WDTCON / ;Sleep: 2.56S + Wakeup: 5mS          |  |

| n+5     |                                                     |  |

| n+6     | /                                                   |  |

| n+7     | SLEEP                                               |  |

| n+8     | NOP                                                 |  |

|         |                                                     |  |

Note: 1. BCR instruction is not recommended for Clear interrupt flag (INTFLAG register).

2. Interrupt backup / restore status code are not shown in this example.

**Example 2.5: Typical Watchdog Reset**

| Address | Code     |            |                |              |          |         |  |  |

|---------|----------|------------|----------------|--------------|----------|---------|--|--|

| NA      | #include | <8P756.ASH | <del> </del> > |              |          |         |  |  |

| 0x000   |          | 🔨          |                |              |          |         |  |  |

|         |          |            | WDT Reset      |              |          |         |  |  |

| n       |          | CLRWDT \   | WDI Kesel      |              |          |         |  |  |

| n+1     |          | MOVIA      | 0x87           |              |          |         |  |  |

| n+2     |          | MOVAR      | WDTCON         | ;Sleep: 2.56 | S + Wake | up:20mS |  |  |

| n+3     |          |            | 1              |              |          |         |  |  |

| n+4     |          | /          |                |              |          |         |  |  |

| n+5     |          | SLEEP /    |                |              |          |         |  |  |

| n+6     |          | NOP /      |                |              |          |         |  |  |

| n+7     |          |            |                |              |          |         |  |  |

| n+8     |          |            |                |              |          |         |  |  |

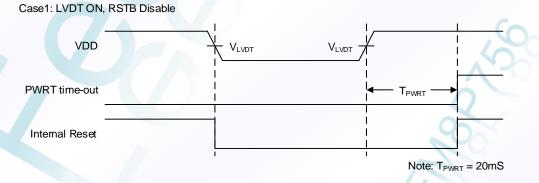

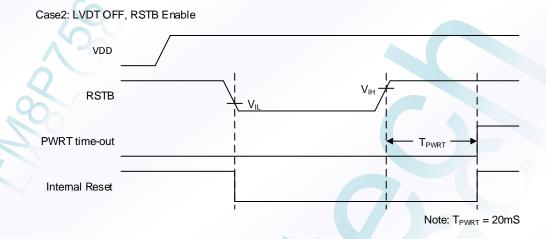

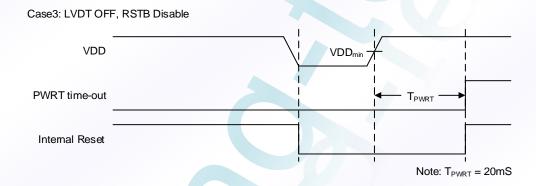

#### 2.7 Reset

FM8P756 device may be RESET in one of the following ways:

- 1. Power-on Reset (POR)

- 2. Brown-out Reset (BOR)

- 3. RSTB Pin Reset

- 4. WDT time-out Reset

Some registers are not affected in any RESET condition. Their status is unknown on Power-on Reset and unchanged in any other RESET. Most other registers are reset to a "reset state" on Power-on Reset, RSTB or WDT Reset.

A Power-on RESET pulse is generated on-chip when Vdd rise is detected. To use this feature, the user merely ties the RSTB pin to Vdd.

On-chip Low Voltage Detector (LVDT) places the device into reset when Vdd is below a fixed voltage. This ensures that the device does not continue program execution outside the valid operation Vdd range. Brown-out RESET is typically used in AC line or heavy loads switched applications.