# 1MHz, 3A Synchronous Step-Down Regulator

## **General Description**

The FP6173 is a high efficiency current mode synchronous buck PWM DC-DC regulator. The internal generated 0.8V precision feedback reference voltage is designed for low output voltage. Low  $R_{DS\ (ON)}$  synchronous switch dramatically reduces conduction loss. To extend battery life for portable application, 100% duty cycle is supported for low-dropout operation. Shutdown mode also helps saving the current consumption. The FP6173 is packaged in SOP-8L(EP) to reduce PCB space.

### **Features**

> Input Voltage Range: 2.5 to 5.5V

Adjustable Output Voltage From 0.8V to V<sub>CC</sub>

➤ Precision Feedback Reference Voltage: 0.8V (±2%)

Output Current: 3A (Max.)

➤ Duty Cycle: 0~100%

> Internal Fixed PWM Frequency: 1MHz

Low Quiescent Current: 100μA

> No Schottky Diode Required

> Built-in Soft Start

> Current Mode Operation

> Over Temperature Protection

Package: SOP-8L (EP)

## **Applications**

- > Cellular Telephone

- Wireless and DSL Modems

- > Digital Still Cameras

- Portable Products

- ➤ MP3 Players

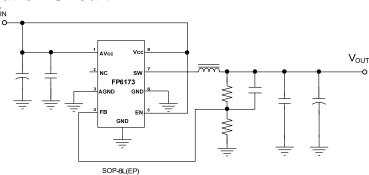

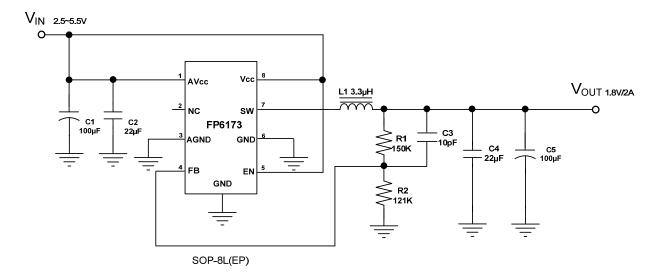

# **Typical Application Circuit**

This datasheet contains new product information. Feeling Technology reserves the rights to modify the product specification without notice. No liability is assumed as a result of the use of this product. No rights under any patent accompany the sales of the product.

Website: http://www.feeling-tech.com.tw

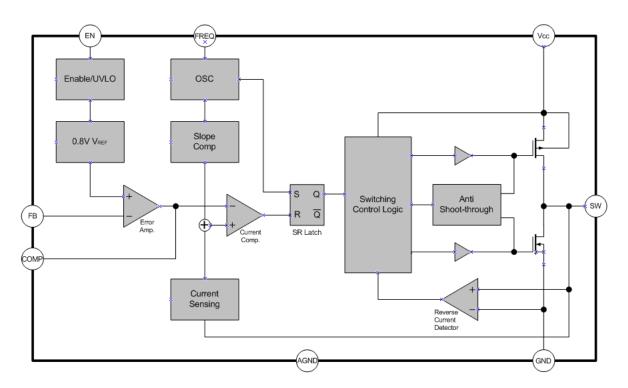

# **Function Block Diagram**

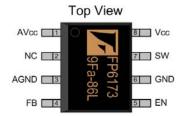

# **Pin Descriptions**

## SOP-8L (EP)

| Name            | No. | 1/0 | Description                               |

|-----------------|-----|-----|-------------------------------------------|

| $AV_{CC}$       | 1   | Р   | Analog Supply Voltage                     |

| NC              | 2   | NA  | Not Connected                             |

| AGND            | 3   | Р   | Analog Ground                             |

| FB              | 4   | I   | Feedback                                  |

| EN              | 5   | I   | Enable                                    |

| GND             | 6   | Р   | Ground                                    |

| SW              | 7   | 0   | Switch                                    |

| V <sub>CC</sub> | 8   | Р   | Supply Voltage                            |

| EP              | 9   | Р   | Exposed PAD - Must be connected to Ground |

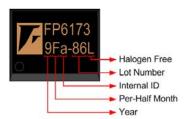

## **Marking Information**

### SOP-8L (EP)

**Halogen Free**: Halogen free product indicator **Lot Number**: Wafer lot number's last two digits

For Example: 132386TB → 86

Internal ID: Internal Identification Code

Per-Half Month: Production period indicated in half month time unit

For Example:  $A \rightarrow First Half Month of January$

B → Last Half Month of January

$C \rightarrow First Half Month of February$

D → Last Half Month of February

Year: Production year's last digit

**Ordering Information**

| Part Number | Operating<br>Temperature | Package     | MOQ    | Description |

|-------------|--------------------------|-------------|--------|-------------|

| FP6173XR-G1 | -40°C ~ +85°C            | SOP-8L (EP) | 2500EA | Tape & Reel |

**Absolute Maximum Ratings**

| Parameter                                | Symbol                            | Conditions | Min. | Тур. | Max.            | Unit   |

|------------------------------------------|-----------------------------------|------------|------|------|-----------------|--------|

| Input Supply Voltage                     | V <sub>CC</sub> /AV <sub>CC</sub> |            | -0.3 |      | 6               | V      |

| EN, V <sub>FB</sub> , SW Voltage         |                                   |            | -0.3 |      | V <sub>CC</sub> | V      |

| P-Channel Switch Source Current (DC)     |                                   |            |      |      | 3.9             | Α      |

| N-Channel Switch Sink Current (DC)       |                                   |            |      |      | 3.9             | Α      |

| Peak SW Pin Sink and Source Current (AC) |                                   |            |      |      | 6               | Α      |

| Thermal Resistance                       | $\theta_{JA}$                     | SOP-8L(EP) |      |      | +60             | °C / W |

| mermai Resistance                        | θ <sub>JC</sub>                   |            |      |      | +10             | °C/W   |

| Junction Temperature                     | T <sub>J</sub>                    |            |      |      | +150            | °C     |

| Storage Temperature                      | T <sub>ST</sub>                   |            | -65  |      | +150            | °C     |

| Lead Temperature (soldering, 10 sec)     |                                   |            |      |      | +260            | °C     |

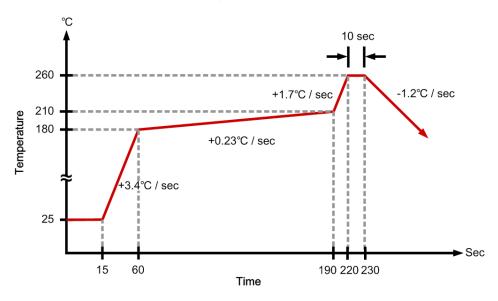

# **Suggested IR Re-flow Soldering Curve**

This datasheet contains new product information. Feeling Technology reserves the rights to modify the product specification without notice. No liability is assumed as a result of the use of this product. No rights under any patent accompany the sales of the product.

**Recommended Operating Conditions**

| Parameter             | Symbol   | Conditions | Min. | Тур. | Max. | Unit |

|-----------------------|----------|------------|------|------|------|------|

| Supply Voltage        | $V_{CC}$ |            | 2.5  |      | 5.5  | V    |

| Operating Temperature |          |            | -40  |      | +85  | °C   |

# DC Electrical Characteristics ( $V_{\text{CC}}$ =3.6V , $T_{\text{A}}$ = 25°C , unless otherwise noted)

| Parameter                             | Symbol                 | Conditions                                                      | Min.  | Тур.  | Max.  | Unit  |

|---------------------------------------|------------------------|-----------------------------------------------------------------|-------|-------|-------|-------|

| Degulated Foodback Valtage            | \ <u>/</u>             | T <sub>A</sub> =25°C                                            | 0.784 | 0.8   | 0.816 | V     |

| Regulated Feedback Voltage            | $V_{FB}$               | -40°C~+85°C                                                     | 0.776 | 0.8   | 0.824 | V     |

| Line Regulation with V <sub>REF</sub> | $\Delta V_{FB}$        | V <sub>CC</sub> =2.5V to 5.5V                                   |       | 0.04  | 0.4   | % / V |

| Output Voltage Line Regulation        | $\Delta V_{OUT}$       | V <sub>CC</sub> =2.5 to 5.5V                                    |       | 0.04  | 0.4   | % / V |

| RDS (ON) of P-Channel FET             | R <sub>DS (ON)</sub> P | I <sub>SW</sub> =100mA                                          |       | 60    | 90    | mΩ    |

| RDS (ON) of N-Channel FET             | R <sub>DS(ON)</sub> N  | I <sub>SW</sub> =-100mA                                         |       | 60    | 90    | mΩ    |

| SW Leakage                            | I <sub>LSW</sub>       | V <sub>EN</sub> =0V, V <sub>CC</sub> =5V                        |       | ±0.01 | ±1    | μΑ    |

| Over Current Limit                    | I <sub>OCP</sub>       | V <sub>FB</sub> =0.7V                                           | 3.75  | 5     | 6     | Α     |

| Quiescent Current                     | I <sub>IN</sub>        | Shutdown, V <sub>EN</sub> =0V                                   |       | 0.1   | 1     | μΑ    |

| Quiescent Current                     |                        | Active, V <sub>FB</sub> =0.7V, V <sub>EN</sub> =V <sub>CC</sub> |       | 100   |       | μΑ    |

| EN Threshold                          | V <sub>EN</sub>        | -40°C~ +85°C                                                    | 0.3   | 1     | 1.5   | V     |

| EN Leakage Current                    | I <sub>EN</sub>        | -40°C ~+85°C                                                    |       | ±0.01 | ±1    | μΑ    |

| Oscillator Frequency                  | Fosc                   | V <sub>FB</sub> =0.8V                                           | 0.8   | 1.0   | 1.2   | MHz   |

## **Function Description**

### **Control Loop**

The FP6173 is a high efficiency current mode synchronous buck regulator. Both the main (P-channel MOSFET) and synchronous (N-channel MOSFET) switches are built internally. With current mode operation, the PWM duty is controlled both by the error amplifier output and the peak inductor current. At the beginning of each cycle, the oscillator turn on the P-MOSFET switch to source current from  $V_{CC}$  to SW output. Then, the chip starts to compare the inductor current with the error amplifier output. Once the inductor current is larger than the error amplifier output, the P-MOSFET switch is turned off. When the load current increases, the feedback voltage FB will slightly drop. This causes the error amplifier to output a higher current level until the prior mentioned peak inductor current reach the same level. The output voltage then can be sustained at the same.

When the top P-MOSFET switch is off, the bottom synchronous N-MOSFET switch is turned on. Once the inductor current reverses, both top and bottom MOSFET will be turn off to leave the SW pin into high impedance state.

The FP6173's current mode control loop also includes slope compensation to suppress sub-harmonic oscillations at high duty cycles. This slope compensation is achieved by adding a compensation ramp to the inductor current signal.

#### **LDO Mode**

The FP6173's maximum duty cycle can reach 100%. That means the driver's main switch is turn on through out whole clock cycle. Once the duty reaches 100%, the feedback path no longer controls the output voltage. The output voltage will be the input voltage minus the main switch voltage drop.

#### **Over Current Protection**

FP6173 limits the peak main switch current cycle by cycle. When over current occurs, chip will turn off the main switch and turn the synchronous switch on until next cycle.

#### **Short Circuit Protection**

When the FB pin is drop below 0.4V, the chip will tri-state the output pin SW automatically. After 300us rest to avoid over heating, chip will re-initiate PWM operation with soft start.

#### **Thermal Protection**

FP6173 will shutdown automatically when the internal junction temperature reaches 150°C to protect both the part and the system.

## **Application Information**

### Input capacitor Selection

The input capacitor must be connected between the  $V_{CC}$  pin and GND pin of FP6173 to maintain steady input voltage and filter out the pulsing input current. The voltage rating of input capacitor must be greater than maximum input voltage plus ripple voltage.

In switch mode, the input current is discontinuous in a buck converter. The source current waveform of the high-side MOSFET is a square wave. To prevent large voltage transients, a low ESR input capacitor sized for the maximum RMS current must be used. The RMS value of input capacitor current can be calculated by:

$$I_{RMS} = I_{O\_MAX} \sqrt{\frac{V_O}{V_{IN}} \left(1 - \frac{V_O}{V_{IN}}\right)}$$

It can be seen that when  $V_O$  is half of  $V_{CC}$ ,  $C_{IN}$  is under the worst current stress. The worst current stress on  $C_{IN}$  is  $I_{O\ MAX}/2$ .

#### **Inductor Selection**

The value of the inductor is selected based on the desired ripple current. Large inductance gives low inductor ripple current and small inductance result in high ripple current. However, the larger value inductor has a larger physical size, higher series resistance, and/or lower saturation current. In experience, the value is to allow the peak-to-peak ripple current in the inductor to be 10%~20% maximum load current. The inductance value can be calculated by:

$$L = \frac{(V_{IN} - V_{O})}{f \times \Delta I_{L}} \frac{V_{O}}{V_{IN}} = \frac{(V_{IN} - V_{O})}{f \times \left[2 \times (10\% \sim 20\%)I_{O}\right]} \frac{V_{O}}{V_{IN}}$$

The inductor ripple current can be calculated by:

$$\Delta I_{L} = \frac{V_{O}}{f \times L} \times \left[ 1 - \frac{V_{O}}{V_{IN}} \right]$$

Choose an inductor that does not saturate under the worst-case load conditions, which is the load current plus half the peak-to-peak inductor ripple current, even at the highest operating temperature. The peak inductor current is:

$$I_{L_{-PEAK}} = I_{O} + \frac{\Delta I_{L}}{2}$$

The inductors in different shape and style are available from manufacturers. Shielded inductors are small and radiate less EMI issue. But they cost more than unshielded inductors. The choice depends on EMI requirement, price and size.

This datasheet contains new product information. Feeling Technology reserves the rights to modify the product specification without notice. No liability is assumed as a result of the use of this product. No rights under any patent accompany the sales of the product.

Website: http://www.feeling-tech.com.tw

| Inductor Value (µH) | Dimensions (mm) | Component Supplier | Model          |

|---------------------|-----------------|--------------------|----------------|

| 1                   | 8.3×8.3×4.5     | FENG-JUI           | TPRH8D43-1R0M  |

| 1                   | 10.3×10.3×4.0   | FENG-JUI           | TPRH10D40-1R0M |

| 2.2                 | 8.3×8.3×4.5     | FENG-JUI           | TPRH8D43-2R2M  |

| 2.2                 | 10.3×10.3×4.0   | FENG-JUI           | TPRH10D40-2R2M |

## **Output Capacitor Selection**

The output capacitor is required to maintain the DC output voltage. Low ESR capacitors are preferred to keep the output voltage ripple low. In a buck converter circuit, output ripple voltage is determined by inductor value, switching frequency, output capacitor value and ESR. The output ripple is determined by:

$$\Delta V_{O} = \Delta I_{L} \times \left( \text{ESR}_{COUT} + \frac{1}{8 \times f \times C_{OUT}} \right)$$

Where f = operating frequency,  $C_{OUT}$ = output capacitance and  $\Delta I_L$  = ripple current in the inductor. For a fixed output voltage, the output ripple is highest at maximum input voltage since  $\Delta I_L$  increases with input voltage.

| Capacitor Value | Case Size | Component Supplier | Model           |

|-----------------|-----------|--------------------|-----------------|

| 10µF            | 0805      | Taiyo Yuden        | JMK212BJ106MG   |

| 10µF            | 0805      | TDK                | C12012X5ROJ106K |

| 22µF            | 0805/1206 | TDK                | C2012JB0J226M   |

### **Using Ceramic Input and Output Capacitors**

Care must be taken when ceramic capacitors are used at the input and the output. When a ceramic capacitor is used at the input and the power is supplied by a wall adapter through long wires, a load step at the output can induce voltage ringing at the input,  $V_{CC}$ . At best condition, this ringing may couple to the output and be mistaken as loop instability. At worst condition, a sudden inrush current through the long wires can potentially cause a voltage spike at  $V_{CC}$ , which may large enough to damage the part. When choosing the input and output ceramic capacitors, choose the X5R or X7R dielectric material. These dielectrics have the best temperature and voltage characteristics of all the ceramic capacitors for a given value and size.

#### **Output Voltage Programming**

The output voltage is set using a resistive voltage divider from the output to FB pin. The output voltage is determined by:

$$V_O = 0.8V \left(1 + \frac{R_1}{R_2}\right)$$

This datasheet contains new product information. Feeling Technology reserves the rights to modify the product specification without notice. No liability is assumed as a result of the use of this product. No rights under any patent accompany the sales of the product.

Website: http://www.feeling-tech.com.tw Rev. 0.62

#### The recommended resistor value is summarized below:

| V <sub>OUT</sub> (V) | R <sub>1</sub> (Ω) | R <sub>2</sub> (Ω) | C <sub>3</sub> (F) |

|----------------------|--------------------|--------------------|--------------------|

| 0.8                  | 100k               | Not Used           | Not Used           |

| 1.2                  | 150k               | 301k               | 10p                |

| 1.5                  | 221k               | 255k               | 10p                |

| 1.8                  | 150k               | 121k               | 10p                |

| 2.5                  | 200k               | 93.1k              | 10p                |

| 3.3                  | 232k               | 73.2k              | 10p                |

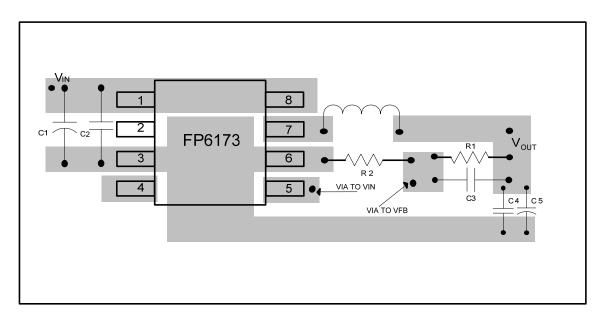

### **PC Board Layout Checklist**

- The power traces, consisting of the GND, SW and V<sub>CC</sub> trace should be kept short, direct and wide.

- 2. Place C<sub>IN</sub> near V<sub>CC</sub> pin as closely as possible to maintain input voltage steady and filter out the pulsing input current.

- 3. The resistive divider R<sub>1</sub> and R<sub>2</sub> must be connected to FB pin directly and as closely as possible.

- 4. FB is a sensitive node. Please keep it away from switching node, SW. A good approach is to route the feedback trace on another PCB layer and have a ground plane between the top and feedback trace routing layer. This reduces EMI radiation on to the DC-DC converter its own voltage feedback trace.

- 5. Keep the GND plates of C<sub>IN</sub> and C<sub>OUT</sub> as close as possible. Then connect this to the ground plane (if one is used) with several vias. This reduces ground plane noise by preventing the switching currents from circulating through the ground plane. It also reduces ground bounce at FP6173 by giving it a low impedance ground connection.

Suggested Layout for SOP-8L(EP)

# **Typical Application**

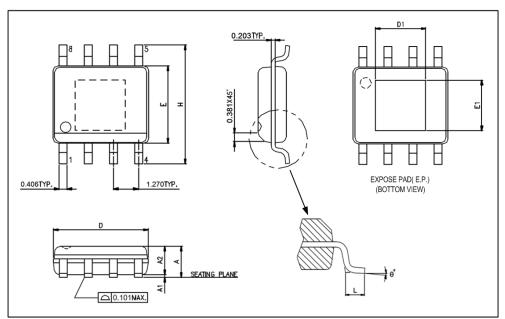

## **Package Outline**

## SOP-8L (EP)

UNIT: mm

| Symbols | Min. (mm) | Max. (mm) |

|---------|-----------|-----------|

| Α       | 1.346     | 1.752     |

| A1      | 0.050     | 0.152     |

| A2      |           | 1.498     |

| D       | 4.800     | 4.978     |

| Е       | 3.810     | 3.987     |

| Н       | 5.791     | 6.197     |

| L       | 0.406     | 1.270     |

| θ°      | 0°        | 8°        |

## **Exposed PAD Dimensions:**

| Symbols | Min. (mm) | Max. (mm) |  |  |

|---------|-----------|-----------|--|--|

| E1      | 2.184 REF |           |  |  |

| D1      | 2.971 REF |           |  |  |

### Note:

- 1. Package dimensions are in compliance with JEDEC outline: MS-012 AA.

- 2. Dimension "D" does not include molding flash, protrusions or gate burrs.

- 3. Dimension "E" does not include inter-lead flash or protrusions

This datasheet contains new product information. Feeling Technology reserves the rights to modify the product specification without notice. No liability is assumed as a result of the use of this product. No rights under any patent accompany the sales of the product.

Website: <a href="http://www.feeling-tech.com.tw">http://www.feeling-tech.com.tw</a>