## USB Type-C Power Delivery and USB HVDCP Controller

## **Description**

FP6606 is a USB PD PHY that enables a USB Type-C port with the Configuration Channel (CC) logic needed for USB Type-C ecosystems. It integrates the physical layer of the USB BMC power delivery (PD) protocol to allow up to 100W of power and support for alternate mode interfaces. An external microprocessor, containing USB Type-C Port Manager (TCPM), communicates with the FP6606 through an I2C interface.

Under control of the TCPM, FP6606 uses the CC pins to determine port attach/detach, cable orientation, role detection, and port control for USB Type-C current mode. The FP6606 can be configured as DFP, UFP, or DRP, depending on the application. The FP6606 implements VBUS detection and discharge for the implementation of a compliant USB Type-C port.

The FP6606 integrates 100mW switch to provide VCONN power for E-mark cable and provides VCONN discharge function. The FP6606 also supports USB Type-C optional features such as audio and debug accessory mode.

Additionally, the FP6606 integrates HiSilicon Fast Charging Protocol (FCP) and Qualcomm<sup>®</sup> Quick Charge<sup>TM</sup> 2.0/3.0 (QC 2.0/3.0) USB interface. The FP6606 monitors USB D+/D- data line and automatically adjusts the output voltage depending on different powered device. If the powered device doesn't support USB PD protocol, the FP6606 can support other protocol as mentioned above.

The FP6606 is available in TQFN-24 and TQFN-16 packages.

### **Features**

### **USB Type-C:**

- Supports USB Type-C<sup>™</sup> 1.2 and TCPCI 1.2

- 5V-24 V Power Sourcing and Sinking

- 100mW VCONN Power (20mA)

- Optimized for Portable Applications with Autonomous Dual Role Port (DRP) Support

- TCPM Configures as :

- Source, Sink and DRP mode

- Attach/Detach of USB port

- Cable Orientation Detection

- Current Mode Advertisement and Detection

- Debug and Audio Accessory Support

- Dead Battery Support (Optional)

- VBUS and VCONN Discharge Function

- Support Type-C DRP Try.SRC or Try.SNK

#### **USB PD:**

- USB Power Delivery 2.0/ 3.0 Specifications

- Fast Role Swap Support

- Data Chunked and PPS Support

### D+/D- Data lines (Source Role Only):

- Support Qualcomm<sup>®</sup> Quick Charge<sup>TM</sup> 2.0/3.0

- Voltage Range from 3.6V to 12V for Class A and 20V for Class B

- Support HiSilicon Fast Charging Protocol (FCP) & Super Charge Protocol (SCP)

- Automatically Selects FCP and QC2.0/3.0 Protocols

- Supports USB DCP Applying 2.7V on D+ Line and 2.7V on D- Line

- Supports USB DCP Shorting D+ Line to D- Line per USB Battery Charging Specification, Revision 1.2

#### Others:

- Control of External N-CH MOSFETs for Source and Sink Power Path

- Fault pin Alarm for VBUS OVP, CC or D+/D- Short to VBUS

- User Defined I/O x 3 pins

- Low Current Consumption( < 30 uA)

## **Applications**

- Adapter, Car Charger

- Wall Charger, Power Banks

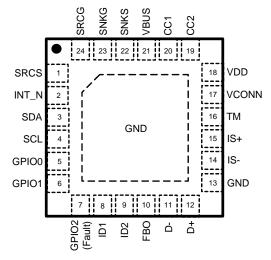

## **Pin Assignments**

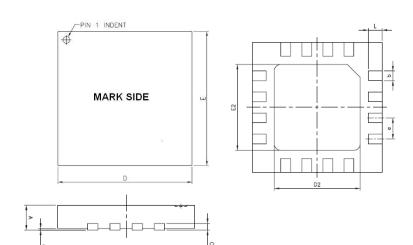

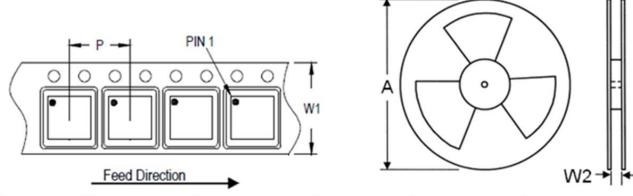

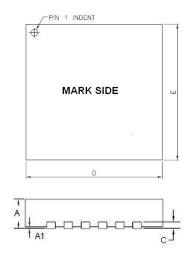

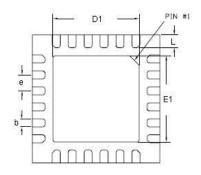

W8 Package TQFN-24(Exposed Pad, 4mmx4mm)

W5 Package TQFN-16(Exposed Pad, 4mmx4mm)

Figure 1. Pin Assignment of FP6606

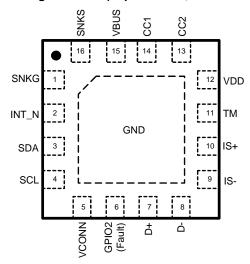

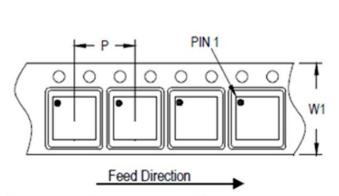

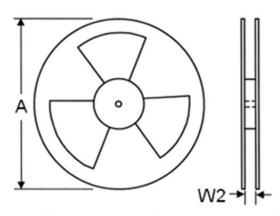

## **Ordering Information**

# **Typical Application Circuit**

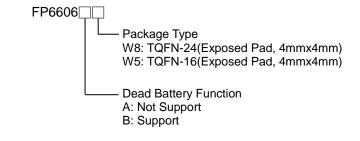

### 1. Sink/Source - Boost Converter with FBO control

Figure 2. Boost Converter with FBO control circuit

# **Typical Application Circuit (Continued)**

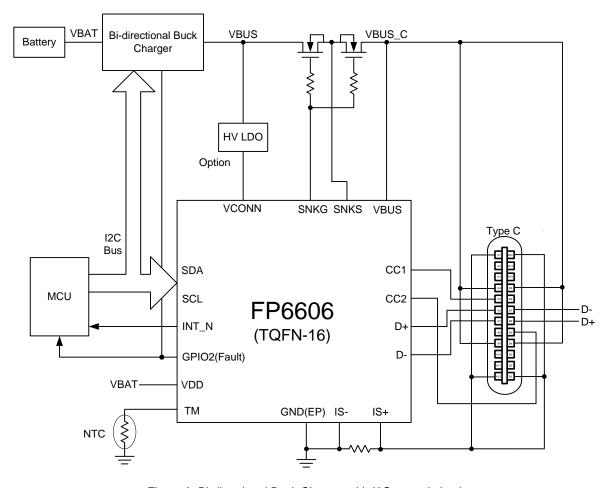

## 2. Sink/Source - Bi-directional Buck Charger with I2C control

Figure 3. Bi-directional Buck Charger with I2C control circuit

# **Typical Application Circuit (Continued)**

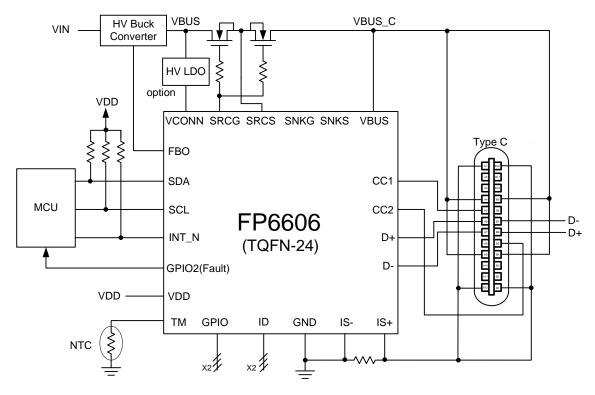

## 3. Source Only - HV Buck Converter with FBO control

Figure 4. HV Buck Converter with FBO control Circuit

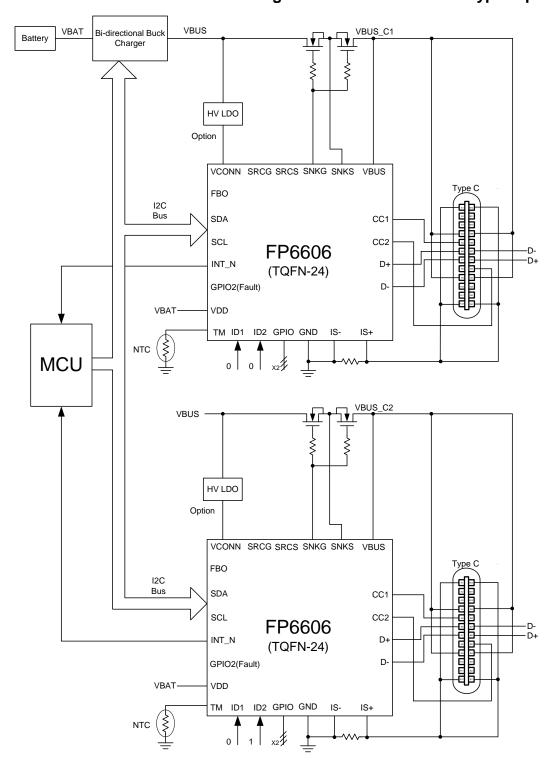

## **Typical Application Circuit (Continued)**

4. Sink/Source - Bi-directional Buck Charger with I2C control - two Type-C ports

Figure 5. Bi-directional Buck Charger with I2C control - two Type-C ports Circuit

# **Functional Pin Description**

| Pin Name | Pin No.<br>(TQFN-24) | Pin No.<br>(TQFN-16) | Pin Function                                                                                                                                                                                                       |

|----------|----------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SRCS     | 1                    | -                    | NMOS source note control(as source).                                                                                                                                                                               |

| INT_N    | 2                    | 2                    | Open drain output. Asserted low to indicate status change occurred. Requires an external pull-up resistor.                                                                                                         |

| SDA      | 3                    | 3                    | I <sup>2</sup> C communication data signal. Requires an external pull-up resistor.                                                                                                                                 |

| SCL      | 4                    | 4                    | I <sup>2</sup> C communication clock signal. Requires an external pull-up resistor.                                                                                                                                |

| GPIO 0~2 | 5,6,7                | 6                    | Programable digital input/ouput pin. The GPIO 2 also can be configued as fault pin.                                                                                                                                |

| ID1 & 2  | 8,9                  | -                    | The I <sup>2</sup> C slave address selection pins.                                                                                                                                                                 |

| FBO      | 10                   | •                    | Feedback output pin. Current sink/source FB node.                                                                                                                                                                  |

| D-       | 11                   | 8                    | USB D- data line for USB interface.                                                                                                                                                                                |

| D+       | 12                   | 7                    | USB D+ data line for USB interface.                                                                                                                                                                                |

| GND      | 13                   | -                    | Ground.                                                                                                                                                                                                            |

| IS-      | 14                   | 9                    | Negative input of a current sense amplifier. Connect to the current sense resistor on the VBUS power path.                                                                                                         |

| IS+      | 15                   | 10                   | Positive input of a current sense amplifier. Connect to the current sense resistor on the VBUS power path. This pin could be opened or connected to ground if user want to neglect the current of VBUS power path. |

| тм       | 16                   | 11                   | External thermal sensor connection node (NTC).                                                                                                                                                                     |

| VCONN    | 17                   | 5                    | 4.75V to 5.5V VCONN. VCONN voltage should be at a valid stable value before TCPM turns on the VCONN switch.                                                                                                        |

| VDD      | 18                   | 12                   | 2.7V to 5.5V positive supply voltage.                                                                                                                                                                              |

| CC2      | 19                   | 13                   | Type-C configuration channel signal 2.                                                                                                                                                                             |

| CC1      | 20                   | 14                   | Type-C configuration channel signal 1.                                                                                                                                                                             |

| VBUS     | 21                   | 15                   | VBUS voltage detection.                                                                                                                                                                                            |

| SNKS     | 22                   | 16                   | NMOS source note control(as sink).                                                                                                                                                                                 |

| SNKG     | 23                   | 1                    | NMOS gate note control(as sink).                                                                                                                                                                                   |

| SRCG     | 24                   | -                    | NMOS gate note control(as source).                                                                                                                                                                                 |

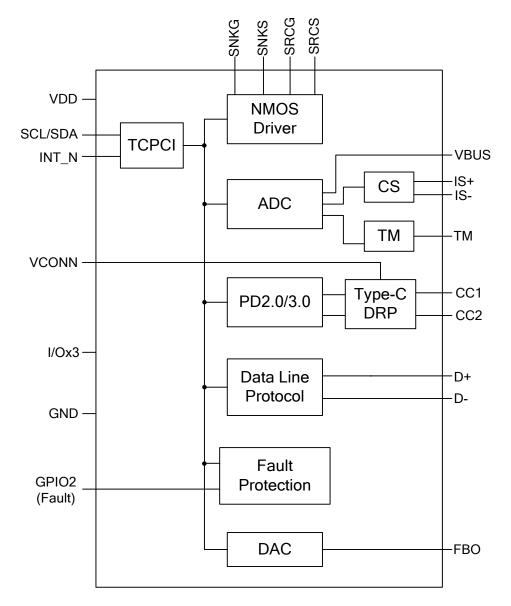

# **Functional Block Diagram**

Figure 6. Block Diagram of FP6606

## **Function Description**

#### **Slave Address Selection**

FP6606 supports four kinds of slave addresses, which is selected by TCPM. The default slave address of FP6606 is 0x60 and it could be changed by ID1 and ID2 pins through pull-high/low. Please refer to the table as blew.

| Slave address | ID1 | ID2 |

|---------------|-----|-----|

| 0x60          | 0   | 0   |

| 0x62          | 0   | 1   |

| 0x64          | 1   | 0   |

| 0x66          | 1   | 1   |

#### Dead Battery Function (FP6606B only)

FP6606 could be applied to the power bank system due to the input voltage of FP6606 ranges from 2.7V to 5.5V. Moreover, when the battery is dead, FP6606 will automatically change the supplied power from input pin to VBUS pin and enable the NMOS\_SNK driver. Please refer to the register 0xAC for setting the dead battery function.

#### **Overvoltage Protection**

FP6606 supports overvoltage protection of VBUS, CC1, CC2, D+ and D- pin. The GPIO 2 (fault pin) will be pulled high when one of these pins is suffered from the high voltage. TCPM monitors the GPIO 2 (fault pin) and the abnormal information is therefore catched immetiatively. Additionally, the setting of OVP protection is assigned to the vendor define registers.

### **Temperature Measurement**

FP6606 provides the TM pin connected to the NTC thermistor. The TM pin could source current and return the voltage on NTC thermistor to the register of FP6606. Therefore, TCPM could access the voltage on NTC thermistor from the register of FP6606 and the temperature could be obatained by simple calculation. Please refer to the register 0xC0[6:5] and 0xC4.

#### **VBUS Control**

The FP6606 is a controller so that it must be combined with power stage. The FBO pin of FP6606 must be connected to the feedback node of power stage. The VBUS control of FP6606 is implemented by sourcing/sinking current from FBO pin. Please refer to the register 0xD0~0xD2 for detail information.

#### **Current Measurement**

FP6606 could monitor the current flowing from IS+ pin to ISpin. The current information is returned to register 0xC3. However, FP6606 do not support the over current protection. If the over current protection is needed, it must be implemented by power stage or other protection circuit.

### **VCONN Over Temperature Protection**

VCONN switch is the only probably heating point in FP6606 due to the current limit of the VCONN switch is up to 40mA. When the temperature of the VCONN switch is higher than the 160°C the VCONN switch will be automatically turned off until the temperature decreases to 130°C.

#### Data Line Interface (D+/D-)

FP6606 supports QC 2.0/3.0/FCP and SCP protocol on the D+/D- data line. The related registers are assigned to the vendor define registers. These registers are public for user and could be managed by TCPM.

When the FP6606 is configured as QC 2.0/3.0/FCP mode, both D+ and D- pin are applied to 2.7V. If sink device has the function of QC 2.0/3.0/FCP, D+ pin will be forced between 0.325V and 2V. In the meanwhile, D+ pin will be automatically connected to D- pin by FP6606 and this process is called the short mode for USB BC1.2 specification. If D+ is continuously applied to the voltage between 0.325V and 2V for 1.25 seconds, the FP6606 will enter QC 2.0/3.0/FCP operation mode. The QC 2.0/3.0 could be classed as the following table.

| D+   | D-     | Output Voltage  |

|------|--------|-----------------|

| 0.6V | 0.6V   | 12V             |

| 3.3V | 0.6V   | 9V              |

| 0.6V | 3.3V   | Continuous mode |

| 0.6V | High-Z | 5V (Default)    |

When the voltage of D+ pin and D- pin simultaneously satisfy these two inequalities VDAT(REF)< D+ <VSEL\_REF and D- > VSEL\_REF, the FP6606 would enter continuous mode.

In the continuous mode, each voltage pulse on D+ pin generated by sink device is between 1V and 3V. In the meanwhile, the high level of pulse should be keep at least 200us (default). If the specified conditions are satisfied, the FBO pin will sink 2uA (default) per pulse. The maximum sink current is 150uA for output voltage 20V.

In the continuous mode, each voltage pulse on D- pin generated by sink device is between 3V and 1V. At the same time, the low level of pulse should be keep at least 200us (default). If the specified conditions are satisfied, the FBO pin will source 2uA (default) per pulse. The maximum source current is 14uA for output voltage 3.6V.

If the sink device doesn't support QC 2.0/3.0, the FP6601Q will remain default output voltage 5V for safe operation. On the other hand, when USB cable is removed, the voltage of D+ pin is therefore lower than VDAT(REF) and the output default voltage 5V is also applied.

# **Function Description (Continued)**

### MTP Register table

MTP function in FP6606 indicates thirty-two registers. Each page consists of four registers. Then, each chip includes eight pages. The Reg.0x98~Reg.0x9A are used to operate the MTP registers. The definition of MTP register could be refer to following table. However, both page 0 and page 1 are reserved by vendor.

| Chip | Page     | Register Name                  | Register<br>Address | MTP<br>Address |

|------|----------|--------------------------------|---------------------|----------------|

|      |          | Reserved                       | 0xA0                | 0x00           |

|      | 0        | Reserved                       | 0xA1                | 0x01           |

|      | Reserved | 0xA2                           | 0x02                |                |

|      |          | Reserved                       | 0xA3                | 0x03           |

|      |          | QC_PROTOCOL_CONTROL_BYTE_0     | 0x9C                | 0x04           |

|      | 4        | QC_PROTOCOL_CONTROL_BYTE_1     | 0x9D                | 0x05           |

|      | I        | Reserved                       | 0x9E                | 0x06           |

|      |          | Reserved                       | 0x9F                | 0x07           |

|      |          | Reserved                       | 0xA4                | 80x0           |

|      | 0        | Reserved                       | 0xA5                | 0x09           |

|      | 2        | Reserved                       | 0xA6                | 0x0A           |

|      |          | Reserved                       | 0xA7                | 0x0B           |

|      |          | Reserved                       | 0xA8                | 0x0C           |

|      | 3        | Reserved                       | 0xA9                | 0x0D           |

|      | 3        | Reserved                       | 0xAA                | 0x0E           |

| 0    |          | Reserved                       | 0xAB                | 0x0F           |

| U    |          | DEAD_BATTERY_VOLTAGE_SELECTION | 0xAC                | 0x10           |

|      | 4        | Reserved                       | 0xAD                | 0x11           |

|      | 4        | Reserved                       | 0xAE                | 0x12           |

|      |          | FACTORY_ID                     | 0xAF                | 0x13           |

|      |          | VENDOR_ID_L                    | 0x00                | 0x14           |

|      | E        |                                | 0x01                | 0x15           |

|      | 5        | USBTYPEC_REV_L                 | 0x06                | 0x16           |

|      |          | USBTYPEC_REV_H                 | 0x07                | 0x17           |

|      |          | DEVICE_ID_L                    | 0x04                | 0x18           |

|      | 6        | DEVICE_ID_H                    | 0x05                | 0x19           |

|      | U        | DEVICE_CAPABILITIES_1_L        | 0x24                | 0x1A           |

|      |          | DEVICE_CAPABILITIES_1_H        | 0x25                | 0x1B           |

|      |          | DEVICE_CAPABILITIES_2_L        | 0x26                | 0x1C           |

|      | 7        | DEVICE_CAPABILITIES_2_H        | 0x27                | 0x1D           |

|      | ,        | STANDARD_INPUT_CAPABILITIES    | 0x28                | 0x1E           |

|      |          | STANDARD_OUTPUT_CAPABILITIES   | 0x29                | 0x1F           |

# Absolute Maximum Ratings (Note 1)

| Supply voltage VDD                                                         | -0.3V to +6.5V  |

|----------------------------------------------------------------------------|-----------------|

| • VCONN                                                                    | -0.3V to +6.5V  |

| • INT_N, SDA, SCL                                                          | -0.3V to +24V   |

| • CC1, CC2, VBUS                                                           | -0.3V to +24V   |

| • VBUS                                                                     | -0.3V to +28V   |

| • D+, D                                                                    | -0.3V to +12V   |

| • SRCS, SNKS, SRCG, SNKG                                                   | -0.3V to +35V   |

| • GPIO 0~4                                                                 | -0.3V to +6.5V  |

| • IS+, IS-, FBO, TM                                                        | -0.3V to +6.5V  |

| Maximum junction temperature (T <sub>J</sub> )                             | +150°C          |

| •Storage temperature (T <sub>Stg</sub> )                                   | -65°C to +150°C |

| • Lead temperature (Soldering, 10sec.)                                     | +260°C          |

| <ul> <li>Power dissipation @T<sub>A</sub>=25°C, (P<sub>D</sub>)</li> </ul> |                 |

| TQFN-16                                                                    | 2 W             |

| TQFN-24                                                                    | 2 W             |

| <ul> <li>Package thermal resistance, (θ<sub>JA</sub>) (Note 2)</li> </ul>  |                 |

| TQFN-16                                                                    | 51 °C/W         |

| TQFN-24                                                                    | 50 °C/W         |

| $ullet$ Package thermal resistance, $(\theta_{JC})$                        |                 |

| TQFN-16                                                                    | 25 °C/W         |

| TQFN-24                                                                    | 19 °C/W         |

|                                                                            |                 |

Note 1: Stresses beyond this listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Note 2:  $\theta_{JA}$  is measured at 25°C ambient with the component mounted on a high effective thermal conductivity test board of JEDEC-51-7.

# **Recommended Operating Conditions**

| Input supply voltage (VDD)                                                | +2.7V to +5.5V  |

|---------------------------------------------------------------------------|-----------------|

| VCONN voltage range                                                       | +2.7V to +5.5V  |

| • VBUS voltage                                                            | 0V to +24V      |

| • System I <sup>2</sup> C voltage range that SDA and SCL are pulled up to | +1.65V to +5.5V |

| Operating temperature range (T <sub>A</sub> )                             | -40°C to +85°C  |

| Junction temperature (T <sub>J</sub> )                                    | -40°C to +125°C |

## **Electrical Characteristics**

| General-Electrical Characteristics                                                                      |                                |                                             |     |     |          |      |  |  |  |

|---------------------------------------------------------------------------------------------------------|--------------------------------|---------------------------------------------|-----|-----|----------|------|--|--|--|

| Parameter                                                                                               | Symbol                         | Conditions                                  | Min | Тур | Max      | Unit |  |  |  |

| Input Power                                                                                             |                                |                                             | •   | •   |          |      |  |  |  |

| VDD input voltage range                                                                                 | $V_{VDD}$                      |                                             | 2.7 |     | 5.5      | V    |  |  |  |

| VDD voltage rising release voltage                                                                      | V <sub>BAT_UVLOR_LK(VTH)</sub> | DEAD_BAT_SEL,<br>Reg.0xAC=0x01              |     | 2.9 |          | V    |  |  |  |

| VDD voltage falling lockout voltage                                                                     | V <sub>BAT_UVLOF_LK(VTH)</sub> | DEAD_BAT_SEL,<br>Reg.0xAC=0x01              |     | 2.7 |          | V    |  |  |  |

| VDD voltage lockout hysteresis voltage                                                                  | V <sub>BAT_UVLOF_LK(HYS)</sub> |                                             |     | 200 |          | mV   |  |  |  |

| In dead battery mode, VBUS turn on voltage                                                              | V <sub>BUS_NMOS_ON</sub>       |                                             | 4   |     | 6.5      | V    |  |  |  |

| N Channel MOSFET Gate Driver                                                                            |                                |                                             |     |     |          |      |  |  |  |

| Sourcing current of SNKG (Note 3)                                                                       |                                |                                             |     | TBD |          | μΑ   |  |  |  |

| Sourcing voltage (ON) between SNKG and SNKS (Note 3)                                                    |                                |                                             | 5   |     | 15       | V    |  |  |  |

| Sourcing current of SRCG (Note 3)                                                                       |                                |                                             |     | TBD |          | μΑ   |  |  |  |

| Sourcing voltage (ON) between SRCG and SRCS (Note 3)                                                    |                                |                                             | 5   |     | 15       | V    |  |  |  |

| Current Sense (IS+ and IS-)                                                                             |                                |                                             |     |     |          |      |  |  |  |

| Current sense range                                                                                     |                                |                                             | 0   |     | 6.4      | Α    |  |  |  |

| Resolution                                                                                              |                                |                                             |     | TBD |          |      |  |  |  |

| Accuracy                                                                                                |                                |                                             |     | TBD |          |      |  |  |  |

| GPIO0~GPIO2                                                                                             | •                              |                                             |     | •   |          |      |  |  |  |

| Logic-low threshold voltage for inputs                                                                  | V <sub>IL_GPIO</sub>           |                                             |     |     | 1.97     | V    |  |  |  |

| Logic-high threshold voltage for inputs                                                                 | V <sub>IH_GPIO</sub>           |                                             | 2.6 |     |          | V    |  |  |  |

| Logic-low threshold voltage for outputs                                                                 | V <sub>OL_GPIO</sub>           |                                             |     |     |          | V    |  |  |  |

| Logic-high threshold voltage for outputs                                                                | V <sub>OH_GPIO</sub>           |                                             |     |     |          | V    |  |  |  |

| Power Consumption                                                                                       |                                | 1                                           | I.  | u l | <u>I</u> |      |  |  |  |

| UFP current consumption in unattached.SNK                                                               | I <sub>(UNATTACHED_UFP)</sub>  | VDD=3.7V                                    |     | TBD |          | μΑ   |  |  |  |

| DRP current consumption while toggling between unattached.SNK and unattached                            | I <sub>(UNATTACHED_DRP)</sub>  | VDD=3.7V                                    |     | TBD |          | μΑ   |  |  |  |

| DFP current consumption in unattached                                                                   | I <sub>(UNATTACHED_DFP)</sub>  | VDD=3.7V                                    |     | TBD |          | μΑ   |  |  |  |

| UFP current consumption in attached.SNK active mode. PD disabled                                        | I <sub>(ACTIVE_UFP)</sub>      | VDD=3.7V                                    |     | TBD |          | μA   |  |  |  |

| UFP current consumption in attached.SNK with PD enabled and transmitting continuous BIST carrier mode 2 | I(ACTIVE_UFP_PD)               | VDD = 3.7V;<br>TX_CARRIER_MODE2_SEL =<br>1; |     | 5.2 |          | mA   |  |  |  |

| Control Pins: INT_N                                                                                     |                                |                                             |     |     |          |      |  |  |  |

| INT_N leakage                                                                                           | I <sub>(INTN_LEAK)</sub>       | VDD = 0V; 0 < INT_N < 3.3V                  | -1  |     | 1        | μA   |  |  |  |

| Low-level signal output voltage                                                                         | V <sub>OL</sub>                | IOL = -2mA                                  |     |     | 0.4      | V    |  |  |  |

# **Electrical Characteristics (Continued)**

| Parameter                                                                              | Symbol                        | Conditions                                           | Min | Тур  | Max  | Unit |

|----------------------------------------------------------------------------------------|-------------------------------|------------------------------------------------------|-----|------|------|------|

| I2C (SDA and SCL). VDD must be above 3                                                 | V to operate at 3.3\          | / I2C levels                                         |     | •    |      |      |

| High-level input signal voltage                                                        | V <sub>IH(I2C)</sub>          |                                                      | 1.2 |      |      | V    |

| Low-level input signal voltage                                                         | V <sub>IL(I2C)</sub>          |                                                      |     |      | 0.4  | V    |

| Low-level signal output voltage (open-drain)                                           | V <sub>OL(I2C)</sub>          |                                                      |     |      | 0.4  | V    |

| Low level output current                                                               | I <sub>OL(I2C)</sub>          |                                                      | 6   |      |      | mA   |

| Leakage through SDA and SCL pins                                                       | I <sub>(I2C_LKG)</sub>        | VDD = 0V; pin pulled up to 3.6V                      | -1  |      | 1    | μΑ   |

| Capacitance for SDA and SCL pins                                                       | C <sub>(I2C)</sub>            |                                                      |     |      | 10   | pF   |

| I2C bus capacitance for FM+ (1MHz)                                                     | C <sub>(I2C_FM+_BUS)</sub>    |                                                      |     |      | 150  | pF   |

| I2C bus capacitance for FM (400KHz)                                                    | C <sub>(I2C_FM_BUS)</sub>     |                                                      |     |      | 150  | pF   |

| External resistors on both SDA and SCL when operating at FM+ (1MHz)                    | R <sub>(EXT_I2C_FM+)</sub>    | C(I2C_FM+_BUS) = 150pF                               | 620 | 820  | 910  | Ω    |

| External resistors on both SDA and SCL when operating at FM (400KHz)                   | R <sub>(EXT_I2C_FM)</sub>     | C(I2C_FM_BUS) = 150pF                                | 620 | 1500 | 2200 | Ω    |

| VBUS                                                                                   |                               |                                                      |     |      |      |      |

| Bleed discharge is a low current discharge to provide a minimum load current if needed | R <sub>(Bleed)</sub>          |                                                      | 8   | 10   | 12.5 | kΩ   |

| Force discharge resistance                                                             | R <sub>(FA_Discharge)</sub>   |                                                      |     | 400  |      | Ω    |

| VBUS_voltage register measurement accuracy                                             | V <sub>(VBUS_MEASURE_AC</sub> |                                                      | -2  |      | 2    | %    |

| OTSD                                                                                   |                               |                                                      |     |      |      |      |

| TJ over temperature trip threshold resulting in VCONN turn off and flag set            | T <sub>(OTSD1)</sub>          |                                                      |     | 150  |      | °C   |

| FBO Pin-QC mode                                                                        |                               |                                                      |     |      |      |      |

| Up/down current step (QC 2.0/3.0)                                                      | I <sub>UP, IDOWN</sub>        | IUP = 40μA (9V), 70μA (12V),<br>IDOWN = 14μA (3.6V). |     | 2    |      | μΑ   |

# **Electrical Characteristics (Continued)**

| USB Power Delivery- Electrical Characteristics                                                                                         |                              |                                        |       |     |       |          |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------------------------------|-------|-----|-------|----------|--|--|--|

| Parameter                                                                                                                              | Symbol                       | Conditions                             | Min   | Тур | Max   | Unit     |  |  |  |

| CC Pins (CC1 and CC2)                                                                                                                  |                              |                                        |       |     |       |          |  |  |  |

| Voltage on both CC pins when in dead battery and the attached DFP is presenting default current advertisement                          | V <sub>CC(USB_DB)</sub>      | VDD = 0V                               | 0.25  |     | 1.5   | <b>V</b> |  |  |  |

| Voltage on both CC pins when in dead battery and the attached DFP is presenting medium current (1.5A) advertisement                    | V <sub>CC(MED_DB)</sub>      | VDD = 0V                               | 0.45  |     | 1.5   | ٧        |  |  |  |

| Voltage on both CC pins when in dead battery and the attached DFP is presenting high current (3.0A) advertisement                      | V <sub>CC(HIGH_DB)</sub>     | VDD = 0V                               | 0.85  |     | 2.45  | ٧        |  |  |  |

| Pull-down resistor when in UFP or DRP mode                                                                                             | R <sub>(CC_RD)</sub>         | VDD = 2.7V to 5.5V                     | 4.59  | 5.1 | 5.61  | kΩ       |  |  |  |

| Pull-down resistor for active cable                                                                                                    | R <sub>(CC_RA)</sub>         | VDD = 2.7V to 5.5V                     | 0.8   | 1   | 1.2   | kΩ       |  |  |  |

| Leakage current through CC pins                                                                                                        | I <sub>CC(LKG)</sub>         | VDD = 0V; VCONN = 0V;<br>CC pin = 5.5V |       |     | 1.36  | mA       |  |  |  |

| Voltage level range for detecting a DFP attach when configured as a UFP and DFP is advertising default current source capability       | V <sub>(UFP_CC_USB)</sub>    | ·                                      | 0.25  |     | 0.61  | V        |  |  |  |

| Voltage level range for detecting a DFP attach when configured as a UFP and DFP is advertising medium (1.5A) current source capability | V(UFP_CC_MED)                |                                        | 0.7   |     | 1.16  | V        |  |  |  |

| Voltage level range for detecting a DFP attach when configured as a UFP and DFP is advertising high (3.0A) current source capability   | V <sub>(UFP_CC_HIGH)</sub>   |                                        | 1.31  |     | 2.04  | V        |  |  |  |

| Voltage threshold for detecting a UFP attach when FP6606 is advertising default current source capability                              | V <sub>TH(DFP_CC_USB)</sub>  |                                        | 1.51  | 1.6 | 1.64  | >        |  |  |  |

| Voltage threshold for detecting a UFP attach when FP6606 is advertising medium current (1.5A) source capability                        | V <sub>TH(DFP_CC_MED)</sub>  |                                        | 1.51  | 1.6 | 1.64  | V        |  |  |  |

| Voltage threshold for detecting a UFP attach when FP6606 is advertising high current (3.0A) source capability                          | V <sub>TH(DFP_CC_HIGH)</sub> |                                        | 2.46  | 2.6 | 2.74  | ٧        |  |  |  |

| Voltage threshold for detecting a active cable attach when advertising default current                                                 | V <sub>TH(AC_CC_USB)</sub>   |                                        | 0.15  | 0.2 | 0.25  | ٧        |  |  |  |

| Voltage threshold for detecting a active cable attach when advertising medium current                                                  | V <sub>TH(AC_CC_MED)</sub>   |                                        | 0.35  | 0.4 | 0.45  | >        |  |  |  |

| Voltage threshold for detecting a active cable attach when advertising high current                                                    | V <sub>TH(AC_CC_HIGH)</sub>  |                                        | 0.76  | 0.8 | 0.84  | V        |  |  |  |

| Default mode pull-up current source when advertising default current                                                                   | I <sub>CC(DEFAULT_P)</sub>   |                                        | 64    | 80  | 96    | μΑ       |  |  |  |

| Medium (1.5A) mode pull-up current source when advertising medium current                                                              | I <sub>CC(MED_P)</sub>       |                                        | 165.6 | 180 | 194.4 | μA       |  |  |  |

| High (3.0A) mode pull-up current source when advertising high current                                                                  | I <sub>CC(HIGH_P)</sub>      | VDD > 3.0V                             | 303.6 | 330 | 356.4 | μA       |  |  |  |

# **Electrical Characteristics (Continued)**

| Parameter                                                                                        | Symbol                    | Conditions                                      | Min     | Тур   | Max    | Unit |

|--------------------------------------------------------------------------------------------------|---------------------------|-------------------------------------------------|---------|-------|--------|------|

| Output impedance of CC1/CC2 during TX when operating in PD mode and driving the CC line (Note 3) | R <sub>TX(PD)</sub>       | At 750KHz                                       | 33      | 48    | 75     | Ω    |

| Fast role swap request transmit driver resistance (excluding cable resistance)                   | R <sub>TX(FRS_PD)</sub>   |                                                 |         |       | 5      | Ω    |

| Transmit high voltage when operating in PD mode                                                  | V <sub>OH(PD)</sub>       |                                                 | 1.05    | 1.125 | 1.2    | V    |

| Transmit low voltage when operating in PD mode                                                   | V <sub>OL(PD)</sub>       |                                                 |         |       | 0.07   | V    |

| Receiver input impedance. Does not include pull-up or pull-down resistance from cable detect     | R <sub>RX(PD)</sub>       | TX is Hi-Z                                      | 1       |       |        | ΜΩ   |

| Fast role swap request voltage detection threshold                                               | V <sub>RX(FRS_PD)</sub>   |                                                 | 0.49    | 0.52  | 0.55   | V    |

| Input high voltage when sourcing power. Selected when POWER_ROLE = 1                             | V <sub>IH(PD_SRC)</sub>   |                                                 | 0.8925  |       | 1.5325 | V    |

| Input high voltage when sinking power. Selected when POWER_ROLE = 0                              | V <sub>IH(PD_SNK)</sub>   |                                                 | 0.6425  |       | 1.5325 | V    |

| Input low voltage when sourcing power. Selected when POWER_ROLE = 1                              | V <sub>IL(PD_SRC)</sub>   |                                                 | -0.3325 |       | 0.4825 | V    |

| Input low voltage when sinking power. Selected when POWER_ROLE = 0                               | V <sub>IL(PD_SNK)</sub>   |                                                 | -0.3325 |       | 0.2325 | V    |

| External shunt capacitance on both CC1 and CC2                                                   | C <sub>RX(SHUNT)</sub>    |                                                 | 200     |       | 450    | pF   |

| VCONN                                                                                            |                           |                                                 |         |       |        |      |

| RON for VCONN power FET                                                                          | R <sub>DS(ON)</sub>       |                                                 |         | 6     | 15     | Ω    |

| Voltage to pass through VCONN power FET                                                          | V <sub>(PASS)</sub>       |                                                 |         | 5     |        | V    |

| VCONN current limit; VCONN is connected above this voltage                                       | I <sub>(VCONN)</sub>      |                                                 | 30      | 40    | 50     | mA   |

| Threshold for detecting VCONN present                                                            | V <sub>(VCONN_PRES)</sub> |                                                 |         |       | 2.4    | V    |

| Resistance to GND when VCONN discharge is enabled                                                | R <sub>(VCONN_DIS)</sub>  |                                                 | 4.59    | 5.1   | 5.61   | kΩ   |

| QC-EC                                                                                            |                           |                                                 |         |       |        |      |

| High Voltage Dedicated Charging Port (HV                                                         | /DCP)                     |                                                 |         |       |        |      |

| Data detect voltage                                                                              | V <sub>DAT(REF)</sub>     |                                                 | 0.25    | 0.325 | 0.4    | V    |

| Output voltage selection reference                                                               | V <sub>SEL_REF</sub>      |                                                 | 1.8     | 2.0   | 2.2    | ٧    |

| D- pull-down resistance                                                                          | R <sub>D-(DWN)</sub>      |                                                 |         | 20    |        | kΩ   |

| D+ leakage resistance                                                                            | R <sub>DAT-LKG</sub>      | VDD<br>=3.2-6.4V,VD+=0.6-3.6V<br>Switch SW1=Off | 300     | 500   | 800    | kΩ   |

| Switch SW1 on-resistance                                                                         | R <sub>DS_ON_N1</sub>     | VDD =5V,SW1=200μA                               |         |       | 40     | Ω    |

| Apple 2.4A Mode                                                                                  | •                         |                                                 | •       | •     | •      |      |

| D+_2.7V/D2.7V line output voltage                                                                |                           | VDD > 3V                                        | 2.57    | 2.7   | 2.84   | V    |

| D+_2.7V/D2.7V line output impedance                                                              |                           | VDD > 3V                                        |         | 33.6  |        | kΩ   |

|                                                                                                  | 1                         | 1                                               | 1       |       | 1      |      |

Note 3: Not production tested.

# **Timing Requirements**

| General-Timing Requirements                                                                              |                            |                                                  |       |     |      |      |  |  |  |

|----------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------|-------|-----|------|------|--|--|--|

| Parameter                                                                                                | Symbol                     | Conditions                                       | Min   | Тур | Max  | Unit |  |  |  |

| I2C(SDA and SCL)                                                                                         |                            |                                                  |       | I   |      |      |  |  |  |

| SCL clock frequency                                                                                      | F <sub>SCL</sub>           |                                                  | 0.001 |     | 1    | MHz  |  |  |  |

| Hold time (repeated) start condition                                                                     | t <sub>HD;STA</sub>        |                                                  | 0.26  |     |      | μs   |  |  |  |

| Low period of SCL                                                                                        | t <sub>LOW</sub>           |                                                  | 0.5   |     |      | μs   |  |  |  |

| High period of SCL                                                                                       | t <sub>HIGH</sub>          |                                                  | 0.26  |     |      | μs   |  |  |  |

| Setup time for a repeated start condition                                                                | t <sub>SU;STA</sub>        |                                                  | 0.26  |     |      | μs   |  |  |  |

| Data hold time                                                                                           | t <sub>HD;DAT</sub>        |                                                  | 0     |     |      | μs   |  |  |  |

| Data setup time                                                                                          | t <sub>SU;DAT</sub>        |                                                  | 50    |     |      | μs   |  |  |  |

| Setup time for STOP condition                                                                            | t <sub>SU;STOP</sub>       |                                                  | 0.26  |     |      | μs   |  |  |  |

| Bus free time between STOP and START condition                                                           | t <sub>BUF</sub>           |                                                  | 0.5   |     |      | μs   |  |  |  |

| Data valid time                                                                                          | t <sub>VD;DAT</sub>        |                                                  |       |     | 0.45 | μs   |  |  |  |

| Data valid acknowledge time                                                                              | t <sub>VD;ACK</sub>        |                                                  |       |     | 0.45 | μs   |  |  |  |

| Rise time of both SDA and SCL                                                                            | t <sub>R_I2C</sub>         | 30% to 70%                                       |       |     | 120  | Ns   |  |  |  |

| Fall time of both SDA and SCL                                                                            | t <sub>F_I2C</sub>         | 70% to 30%                                       | 14    |     | 120  | ns   |  |  |  |

| Power-Up Requirements                                                                                    |                            |                                                  | 1     |     |      |      |  |  |  |

| Time from VDD (min) to FP6606 asserts INT_N low                                                          | t <sub>INT_N_LOW</sub>     | Measured from VDD(min) to INT_N pin at VOL(min). |       |     | 4    | ms   |  |  |  |

| VDD rise time                                                                                            | t <sub>VDD_RISE</sub>      | Measured from 0V to VDD(min)                     |       |     | 40   | ms   |  |  |  |

| USB PD-Timing                                                                                            |                            |                                                  |       |     |      |      |  |  |  |

| CC Pins (CC1 and CC2)                                                                                    |                            |                                                  |       |     |      |      |  |  |  |

| Bit rate                                                                                                 | F <sub>br_PD</sub>         |                                                  | 270   | 300 | 330  | Kbps |  |  |  |

| Unit interval                                                                                            | t <sub>UI_PD</sub>         |                                                  | 3.03  | 3.3 | 3.7  | μs   |  |  |  |

| Rise time                                                                                                | t <sub>RISE_PD</sub>       | 10% to 90%; CRX(SHUNT) = 200pF                   | 300   |     |      | ns   |  |  |  |

| Fall time                                                                                                | t <sub>FALL_PD</sub>       | 90% to 10%; CRX(SHUNT) = 200pF                   | 300   |     |      | ns   |  |  |  |

| Rx Bandwidth limiting filter                                                                             | t <sub>RxFilter</sub>      |                                                  | 100   |     |      | ns   |  |  |  |

| Time from the end of last bit of a frame until the state of the first bit of the next pre-amble          | t <sub>InterFrameCap</sub> |                                                  | 25    |     | 50   | Ms   |  |  |  |

| Time before the start of the first bit of the preamble when the transmitter shall start driving the line | t <sub>StartDrive</sub>    |                                                  | -1    |     | 1    | Ms   |  |  |  |

| Time to cease driving the line after the end of the last bit of a frame                                  | t <sub>EndDriveBMC</sub>   |                                                  |       |     | 23   | Ms   |  |  |  |

| Time to cease driving the line after the final                                                           | t <sub>HoldLowBMC</sub>    |                                                  | 1     |     | 23   | μs   |  |  |  |

# **Timing Requirements (Continued)**

| General-Timing Requirements                                    |                               |                                                              |     |     |     |      |  |  |

|----------------------------------------------------------------|-------------------------------|--------------------------------------------------------------|-----|-----|-----|------|--|--|

| Parameter                                                      | Symbol                        | Conditions                                                   | Min | Тур | Max | Unit |  |  |

| Transitions for signal detect                                  | n <sub>Transition</sub> Count | Number of transitions to be detected to declare bus non-idle | 3   |     |     |      |  |  |

| Fast role swap request transmit duration                       | t <sub>FRSWAPTX</sub>         |                                                              | 60  |     | 120 | μs   |  |  |

| Fast role swap detection time                                  | t <sub>FRSWAPRX</sub>         |                                                              | 30  |     | 50  | μs   |  |  |

| VCONN Fault                                                    |                               |                                                              |     |     |     |      |  |  |

| Delay from VCONN fault detected to VCONN fault status flag set | tvconn_fault_dly              |                                                              |     |     | 20  | μs   |  |  |

| Delay from VCONN fault detected to VCONN switch opened         | t <sub>VCONN_OPEN</sub>       |                                                              |     |     | 50  | ns   |  |  |

| Sampling Timings                                               |                               | <u> </u>                                                     |     |     |     |      |  |  |

| Delay from VCONN fault detected to VCONN fault status flag set | t <sub>CC_SAMPLE_RATE</sub>   | CC_SAMPLE_RATE = 2'b01                                       |     | 2   |     | ms   |  |  |

| The sampling interval of VBUS voltage                          | t <sub>VBUSINRATE</sub>       | CC_SAMPLE_RATE = 2'b01                                       |     | 2   |     | ms   |  |  |

| Qu                                                                                                          | Qualcomm <sup>®</sup> Quick Charge-Timing Requirements |                             |      |      |      |    |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------|------|------|------|----|--|--|--|--|--|

| Parameter                                                                                                   | Symbol                                                 | Min                         | Тур  | Max  | Unit |    |  |  |  |  |  |

| TCPC Timing Constraints                                                                                     |                                                        |                             |      |      |      |    |  |  |  |  |  |

| Time between I2C STOP and first bit SOP                                                                     | t <sub>Buffer2Cc</sub>                                 |                             |      |      | 195  | μs |  |  |  |  |  |

| Time between last bit of EOP and Rx buffer ready                                                            | t <sub>Cc2Buffer</sub>                                 |                             |      |      | 50   | μs |  |  |  |  |  |

| Time between status change occurs and status register(s) updated                                            | t <sub>SetReg</sub>                                    |                             |      |      | 50   | μs |  |  |  |  |  |

| Time between status change occurs and status register(s) updated                                            | t <sub>CcStatusDelay</sub>                             | t <sub>CcStatus</sub> Delay |      |      |      | μs |  |  |  |  |  |

| Time from last I2C transaction or ALERT#<br>pin assertion to entering Error Recovery<br>(Watchdog function) | t <sub>HVWatchdog</sub>                                |                             | 650  |      | 5000 | ms |  |  |  |  |  |

| High Voltage Dedicated Charging Port (HV                                                                    | (DCP)                                                  |                             | ı    |      |      |    |  |  |  |  |  |

| D+ high glitch filter time                                                                                  | T <sub>GLITCH(BC)-D+_H</sub>                           |                             | 1000 | 1250 | 1500 | ms |  |  |  |  |  |

| D- low glitch filter time                                                                                   | T <sub>GLITCH(BC)-DL</sub>                             |                             |      | 1    |      | ms |  |  |  |  |  |

| Output voltage glitch filter time                                                                           | T <sub>GLITCH(V)</sub> change 20 40 60                 |                             |      |      | 60   | ms |  |  |  |  |  |

| Continuous mode glitch filter time                                                                          | T <sub>GLITCH-CONT-CHANGE</sub>                        |                             | 100  |      | 200  | μs |  |  |  |  |  |

# **Register Maps**

| Address      | Pagistar Nama                         | Pocot | Definition                                                                      |

|--------------|---------------------------------------|-------|---------------------------------------------------------------------------------|

| Address      | Register Name                         | Reset | Definition                                                                      |

| 0x00         | VENDOR_ID_L                           | 0x5B  |                                                                                 |

| 0x01         | VENDOR_ID_H                           | 0x2E  |                                                                                 |

| 0x02         | PRODUCT_ID_L                          | 0x06  |                                                                                 |

| 0x03         | PRODUCT_ID_H                          | 0x66  |                                                                                 |

| 0x04         | DEVICE_ID_L                           | 0x00  |                                                                                 |

| 0x05         | DEVICE_ID_H                           | 0x00  |                                                                                 |

| 0x06         | USBTYPEC_REV_L                        | 0x00  |                                                                                 |

| 0x07         | USBTYPEC_REV_H                        | 0x00  |                                                                                 |

| 0x08         | USBPD_REV_VER_L                       | 0x11  |                                                                                 |

| 0x09         | USBPD_REV_VER_H                       | 0x30  |                                                                                 |

| 0x0A         | PD_INTERFACE_REV_L                    | 0x12  |                                                                                 |

| 0x0B         | PD_INTERFACE_REV_H                    | 0x10  |                                                                                 |

| 0x0C ~ 0x0F  | Reserved                              | 0x00  | Reserved                                                                        |

| 0x10         | ALERT_L                               | 0x02  |                                                                                 |

| 0x11         | ALERT_H                               | 0x02  |                                                                                 |

| 0x12         | ALERT_MASK_L                          | 0xFF  |                                                                                 |

| 0x13         | ALERT_MASK_H                          | 0x0F  |                                                                                 |

| 0x14         | POWER_STATUS_MASK                     | 0xFF  |                                                                                 |

| 0x15         | FAULT_STATUS_MASK                     | 0xFF  |                                                                                 |

| 0x16 ~ 0x18  | Reserved                              | 0x00  | Reserved                                                                        |

| 0x19         | TCPC_CONTROL                          | 0x00  |                                                                                 |

| 0x1A         | ROLE_CONTROL                          | 0x0A  |                                                                                 |

| 0x1B         | FAULT_CONTROL                         | 0x00  |                                                                                 |

| 0x1C         | POWER_CONTROL                         | 0x60  |                                                                                 |

| 0x1D         | CC_STATUS                             | 0x10  |                                                                                 |

| 0x1E         | POWER_STATUS                          | 0x00  |                                                                                 |

| 0x1F         | FAULT_STATUS                          | 0x80  |                                                                                 |

| 0x20 ~ 0x22  | Reserved                              | 0x00  | Reserved                                                                        |

| 0x23         | COMMAND                               | 0x00  |                                                                                 |

| 0x24         | DEVICE_CAPABILITIES_1_L               | 0xD8  |                                                                                 |

| 0x25         | DEVICE_CAPABILITIES_1_H               | 0x1E  |                                                                                 |

| 0x26         | DEVICE_CAPABILITIES_2_L               | 0xC1  |                                                                                 |

| 0x27         | DEVICE_CAPABILITIES_2_H               | 0x01  |                                                                                 |

| 0x28         | STANDARD_INPUT_CAPABILITIES           | 0x00  |                                                                                 |

| 0x29         | STANDARD_OUTPUT_CAPABILITIES          | 0x00  |                                                                                 |

| 0x2A ~ 0x2D  | Reserved                              | 0x00  | Reserved                                                                        |

| 0x2E         | MESSAGE_HEADER_INFO                   | 0x02  |                                                                                 |

| 0x2F         | RECEIVE_DETECT                        | 0x00  |                                                                                 |

| 0x30         | RECEIVE_BYTE_COUNT                    | 0x00  | Number of Bytes in the RECEIVE_BUFFER that are not stale.                       |

| 0x31         | RX_BUF_FRAME_TYPE                     | 0x00  | Type of received frame (with a reference to a description of the register)      |

| 0x32         | RX_BUF_HEADER_BYTE_0                  | 0x00  | Byte 0 (bits 70) of RX message header                                           |

| 0x32<br>0x33 | RX_BUF_HEADER_BYTE_1                  | 0x00  | Byte 1 (bits 158) of RX message header                                          |

| 0x34         | RX_BUF_OBJ1_BYTE_0                    | 0x00  | RX Byte 0 (bits 70) of 1st data object                                          |

| 0x35         | RX_BUF_OBJ1_BYTE_1                    | 0x00  | RX Byte 1 (bits 158) of 1st data object                                         |

| 0x36         | RX_BUF_OBJ1_BYTE_2                    | 0x00  | RX Byte 1 (bits 136) of 1st data object                                         |

| 0x37         | RX_BUF_OBJ1_BYTE_3                    | 0x00  | RX Byte 3 (bits 3124) of 1st data object                                        |

| 0x37<br>0x38 | RX_BUF_OBJ2_BYTE_0                    | 0x00  | RX Byte 0 (bits 70) of 2nd data object                                          |

| 0x39         | RX_BUF_OBJ2_BYTE_1                    | 0x00  | RX Byte 0 (bits 70) of 2nd data object  RX Byte 1 (bits 158) of 2nd data object |

| 0x39<br>0x3A | RX_BUF_OBJ2_BYTE_1 RX_BUF_OBJ2_BYTE_2 | 0x00  | RX Byte 1 (bits 156) of 2nd data object                                         |

|              |                                       |       | , , , , ,                                                                       |

| 0x3B         | RX_BUF_OBJ2_BYTE_3                    | 0x00  | RX Byte 3 (bits 3124) of 2nd data object                                        |

| 0x3C         | RX_BUF_OBJ3_BYTE_0                    | 0x00  | RX Byte 0 (bits 70) of 3rd data object                                          |

| 0x3D         | RX_BUF_OBJ3_BYTE_1                    | 0x00  | RX Byte 1 (bits 158) of 3rd data object                                         |

| 0x3E         | RX_BUF_OBJ3_BYTE_2                    | 0x00  | RX Byte 2 (bits 2316) of 3rd data object                                        |

| 0x3F         | RX_BUF_OBJ3_BYTE_3                    | 0x00  | RX Byte 3 (bits 3124) of 3rd data object                                        |

# **Register Maps (Continued)**

| Address | Register Name                             | Reset | Definition                               |

|---------|-------------------------------------------|-------|------------------------------------------|

| 0x40    | RX_BUF_OBJ4_BYTE_0                        | 0x00  | RX Byte 0 (bits 70) of 4th data object   |

| 0x41    | RX_BUF_OBJ4_BYTE_1                        | 0x00  | RX Byte 1 (bits 158) of 4th data object  |

| 0x42    | RX_BUF_OBJ4_BYTE_2                        | 0x00  | RX Byte 2 (bits 2316) of 4th data object |

| 0x43    | RX_BUF_OBJ4_BYTE_3                        | 0x00  | RX Byte 3 (bits 3124) of 4th data object |

| 0x44    | RX_BUF_OBJ5_BYTE_0                        | 0x00  | RX Byte 0 (bits 70) of 5th data object   |

| 0x45    | RX_BUF_OBJ5_BYTE_1                        | 0x00  | RX Byte 1 (bits 158) of 5th data object  |

| 0x46    | RX_BUF_OBJ5_BYTE_2                        | 0x00  | RX Byte 2 (bits 2316) of 5th data object |

| 0x47    | RX_BUF_OBJ5_BYTE_3                        | 0x00  | RX Byte 3 (bits 3124) of 5th data object |

| 0x48    | RX_BUF_0BJ6_BYTE_0                        | 0x00  | RX Byte 0 (bits 70) of 6th data object   |

| 0x49    | RX_BUF_OBJ6_BYTE_1                        | 0x00  | RX Byte 1 (bits 158) of 6th data object  |

| 0x4A    | RX_BUF_OBJ6_BYTE_2                        | 0x00  | RX Byte 2 (bits 2316) of 6th data object |

| 0x4B    | RX_BUF_OBJ6_BYTE_3                        | 0x00  | RX Byte 3 (bits 3124) of 6th data object |

| 0x4C    | RX_BUF_OBJ7_BYTE_0                        | 0x00  | RX Byte 0 (bits 70) of 7th data object   |

| 0x4D    | RX_BUF_OBJ7_BYTE_1                        | 0x00  | RX Byte 1 (bits 158) of 7th data object  |

| 0x4E    | RX_BUF_OBJ7_BYTE_2                        | 0x00  | RX Byte 2 (bits 2316) of 7th data object |

| 0x4F    | RX_BUF_OBJ7_BYTE_3                        | 0x00  | RX byte 3 (bits 3124) of 7th data object |

| 0x50    | TRANSMIT                                  | 0x00  | Retry count and SOP* TX type             |

| 0x51    | TRANSMIT_BYTE_COUNT                       | 0x00  | The number of bytes the TCPM will write  |

| 0x52    | TX_BUF_HEADER_BYTE_0                      | 0x00  | Byte 0 (bits 70) of TX message header    |

| 0x53    | TX_BUF_HEADER_BYTE_1                      | 0x00  | Byte 1 (bits 158) of TX message header   |

| 0x54    | TX_BUF_OBJ1_BYTE_0 / Extend header byte 0 | 0x00  | TX Byte 0 (bits 70) of 1st data object   |

| 0x55    | TX_BUF_OBJ1_BYTE_1 / Extend header byte 1 | 0x00  | TX Byte 1 (bits 158) of 1st data object  |

| 0x56    | TX_BUF_OBJ1_BYTE_2                        | 0x00  | TX Byte 2 (bits 2316) of 1st data object |

| 0x57    | TX_BUF_OBJ1_BYTE_3                        | 0x00  | TX Byte 3 (bits 3124) of 1st data object |

| 0x58    | TX_BUF_OBJ2_BYTE_0                        | 0x00  | TX Byte 0 (bits 70) of 2nd data object   |

| 0x59    | TX_BUF_OBJ2_BYTE_1                        | 0x00  | TX Byte 1 (bits 158) of 2nd data object  |

| 0x5A    | TX_BUF_OBJ2_BYTE_2                        | 0x00  | TX Byte 2 (bits 2316) of 2nd data object |

| 0x5B    | TX_BUF_OBJ2_BYTE_3                        | 0x00  | TX Byte 3 (bits 3124) of 2nd data object |

| 0x5C    | TX_BUF_OBJ3_BYTE_0                        | 0x00  | TX Byte 0 (bits 70) of 3rd data object   |

| 0x5D    | TX_BUF_OBJ3_BYTE_1                        | 0x00  | TX Byte 1 (bits 158) of 3rd data object  |

| 0x5E    | TX_BUF_OBJ3_BYTE_2                        | 0x00  | TX Byte 2 (bits 2316) of 3rd data object |

| 0x5F    | TX_BUF_OBJ3_BYTE_3                        | 0x00  | TX Byte 3 (bits 3124) of 3rd data object |

| 0x60    | TX_BUF_OBJ4_BYTE_0                        | 0x00  | TX Byte 0 (bits 70) of 4th data object   |

| 0x61    | TX_BUF_OBJ4_BYTE_1                        | 0x00  | TX Byte 1 (bits 158) of 4th data object  |

| 0x62    | TX_BUF_OBJ4_BYTE_2                        | 0x00  | TX Byte 2 (bits 2316) of 4th data object |

| 0x63    | TX_BUF_OBJ4_BYTE_3                        | 0x00  | TX Byte 3 (bits 3124) of 4th data object |

| 0x64    | TX_BUF_OBJ5_BYTE_0                        | 0x00  | TX Byte 0 (bits 70) of 5th data object   |

| 0x65    | TX_BUF_OBJ5_BYTE_1                        | 0x00  | TX Byte 1 (bits 158) of 5th data object  |

| 0x66    | TX_BUF_OBJ5_BYTE_2                        | 0x00  | TX Byte 2 (bits 2316) of 5th data object |

| 0x67    | TX_BUF_OBJ5_BYTE_3                        | 0x00  | TX Byte 3 (bits 3124) of 5th data object |

| 0x68    | TX_BUF_OBJ6_BYTE_0                        | 0x00  | TX Byte 0 (bits 70) of 6th data object   |

| 0x69    | TX_BUF_OBJ6_BYTE_1                        | 0x00  | TX Byte 1 (bits 158) of 6th data object  |

| 0x6A    | TX_BUF_OBJ6_BYTE_2                        | 0x00  | TX Byte 2 (bits 2316) of 6th data object |

| 0x6B    | TX_BUF_OBJ6_BYTE_3                        | 0x00  | TX Byte 3 (bits 3124) of 6th data object |

| 0x6C    | TX_BUF_OBJ7_BYTE_0                        | 0x00  | TX Byte 0 (bits 70) of 7th data object   |

| 0x6D    | TX_BUF_OBJ7_BYTE_1                        | 0x00  | TX Byte 1 (bits 158) of 7th data object  |

| 0x6E    | TX_BUF_OBJ7_BYTE_2                        | 0x00  | TX Byte 2 (bits 2316) of 7th data object |

| 0x6F    | TX_BUF_OBJ7_BYTE_3                        | 0x00  | TX Byte 3 (bits 3124) of 7th data object |

# **Register Maps (Continued)**

| Address     | Register Name                        | Reset       | Definition                                    |

|-------------|--------------------------------------|-------------|-----------------------------------------------|

| 0x70        | VBUS_VOLTAGE_L                       | 0x00        | LSB of VBUSIN measured voltage in 25mV steps. |

| 0x71        | VBUS_VOLTAGE_H                       | 0x00        | MSB of VBUSIN measured voltage in 25mV steps. |

| 0x72        | VBUS_SINK_DISCONNECT_THRESHOLD _L    | 0xC8        |                                               |

| 0x73        | VBUS_SINK_DISCONNECT_THRESHOLD<br>_H | 0x00        |                                               |

| 0x74        | VBUS_STOP_DISCHARGE_THRESHOLD_       |             |                                               |

| 0x75        | VBUS_STOP_DISCHARGE_THRESHOLD_<br>H  | 0x00        |                                               |

| 0x76        | VBUS_VOLTAGE_ALARM_HI_CFG_L          | 0x00        |                                               |

| 0x77        | VBUS_VOLTAGE_ALARM_HI_CFG_H          | 0x00        |                                               |

| 0x78        | VBUS_VOLTAGE_ALARM_LO_CFG_L          | 0x00        |                                               |

| 0x79        | VBUS_VOLTAGE_ALARM_LO_CFG_H          | 0x00        |                                               |

| 0x7A ~ 0x7F | Reserved                             | 0x00        | Reserved                                      |

|             | Vendor Define                        | d Space (0x | (80 ~ 0xDF)                                   |

| 0x80        | SYSTEM_CONTROL_BYTE_0                | 0x10        | ,                                             |

| 0x81        | SYSTEM_CONTROL_BYTE_1                | 0x00        |                                               |

| 0x82        | Reserved                             | 0x00        | Reserved                                      |

| 0x83        | MODE_STATUS_BYTE_0                   | 0x01        |                                               |

| 0x84        | MODE_STATUS_BYTE_1                   | 0x10        | Reserved                                      |

| 0x85        | EXTERNAL_NMOS_CONTROL                | 0x00        |                                               |

| 0x86        | SYSTEM_CONTROL_BYTE_2                | 0x00        |                                               |

| 0x87 ~ 0x8F | Reserved                             | 0x00        | Reserved                                      |

| 0x90        | VENDOR_INTERRUPTS_BYTE_0             | 0x00        |                                               |

| 0x91        | VENDOR_INTERRUPTS_BYTE_1             | 0x00        |                                               |

| 0x92        | VENDOR_INTERRUPTS_MASK_BYTE_0        | 0x00        |                                               |

| 0x93        | VENDOR_INTERRUPTS_MASK_BYTE_1        | 0x00        |                                               |

| 0x94        | CC_GENERAL_CONTROL                   | 0x04        |                                               |

| 0x95 ~ 0x97 | Reserved                             | 0x00        | Reserved                                      |

| 0x98        | MTP_CONTROL_BYTE_0                   | 0x00        | 110001100                                     |

| 0x99        | MTP_CONTROL_BYTE_1                   | 0x00        |                                               |

| 0x9A        | MTP_PASSWORD                         | 0x00        |                                               |

| 0x9B        | Reserved                             | 0x00        | Reserved                                      |

| 0x9C        | QC_PROTOCOL_CONTROL_BYTE_0           | 0x83        |                                               |

| 0x9D        | QC_PROTOCOL_CONTROL_BYTE_1           | 0x00        |                                               |

| 0x9E ~ 0x9F | Reserved                             | 0x00        | Reserved                                      |

| 0xA0 ~ 0xAB | Reserved                             | 0x00        | Reserved                                      |

| 0xAC        | DEAD_BATTERY_VOLTAGE_SELECTION       | 0x01        |                                               |

| 0xAD ~ 0xAF | Reserved                             | 0x30        | Reserved                                      |

| 0xB0 ~ 0xBF | Reserved                             | 0x00        | Reserved                                      |

| 0xC0        | ADC_CONTROL                          | 0x81        |                                               |

| 0xC1 ~ 0xC2 | Reserved                             | 0x00        | Reserved                                      |

| 0xC3        | ADC_IBUS_DATA                        | 0x00        |                                               |

| 0xC4        | ADC_TEMPERATURE_DATA                 | 0x00        |                                               |

| 0xC5 ~ 0xC7 | Reserved                             | 0x00        | Reserved                                      |