# Integrated Multi-Channel DC-DC Converters for TFT LCD Panels

### **Description**

The FP6783 is an integrated power supply solution optimized for medium to large size thin-film transistor (TFT) liquid crystal displays (LCD's).

The boost converter operates at a frequency of 1.2MHz. The integrated N-channel FET has a typical current limit of 4.5A and can support output voltage up to 18V.

A positive charge pump with an integrated driver can produce up to 36V of positive gate drive.

The GPM is a flicker compensation circuit to reduce the coupling effect of gate lines; the gate-shaping timing is controlled by the timing-controller to modulate the Gate-On voltage, VGHM. It also can delay the Gate-On voltage during power-on to achieve a correct power-on delay time and the falling time of the Gate-On voltage are programmable by external capacitor and resistor.

The FP6783 is available in a thin 20-pin 5x5 mm TQFN green package.

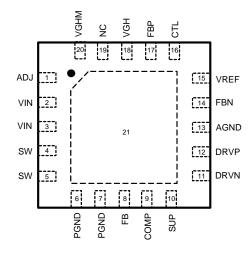

# **Pin Assignments**

WQ Package (TQFN-20)(5mm x 5mm)

Figure 1. Pin Assignment of FP6783

#### **Features**

- 2.5V to 5.5V Input Supply

- 1.2MHz Switching Frequency

- Current-Mode Boost Regulator

- Integrated 18V/4.5A FET

- Fast Transient Response to Pulsed Load

- High Efficiency

- GPM Controller with Adjustable Falling Time

- Flicker Compensator

- Power-on Sequence Control

- Over-Temperature Protection

- Over-Current Protection

- Over-Voltage Protection

- Under-Voltage Protection

- Charge Pump for VGH Regulation

- Charge Pump for VGL Regulation

- TQFN-20 Exposed Pad Package

- ROHS Compliant

## **Applications**

- TFT LCD for Notebook

- TFT LCD for Monitor

- TFT LCD for TV

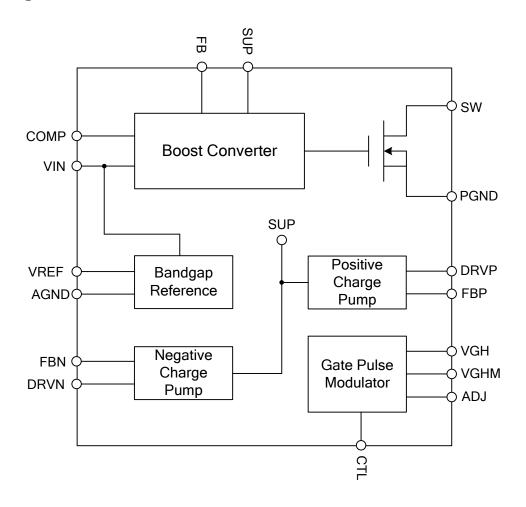

## **Ordering Information**

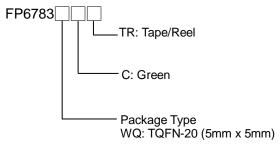

# **Typical Application Circuit**

Figure 2. Typical Application Circuit of FP6783

# **Functional Pin Description**

| Pin No. | Pin Name | I/O | Pin Function                            |  |

|---------|----------|-----|-----------------------------------------|--|

| 1       | ADJ      | 0   | Gate High voltage fall time setting pin |  |

| 2       | VIN      | I   | Power supply input pin                  |  |

| 3       | VIN      | I   | Power supply input pin                  |  |

| 4       | sw       | -   | Main PWM switching pin                  |  |

| 5       | sw       | -   | Main PWM switching pin                  |  |

| 6       | PGND     | -   | SW MOS GND                              |  |

| 7       | PGND     | -   | SW MOS GND                              |  |

| 8       | FB       | I   | Main PWM Feedback pin                   |  |

| 9       | COMP     | 0   | Main PWM Error amplifier output         |  |

| 10      | SUP      | -   | High voltage power supply input         |  |

| 11      | DRVN     | 0   | Negative charge pump output pin         |  |

| 12      | DRVP     | 0   | Positive charge pump output pin         |  |

| 13      | AGND     | -   | Analog Ground                           |  |

| 14      | FBN      | I   | Negative charge pump feedback pin       |  |

| 15      | VREF     | 0   | Internal Reference voltage output       |  |

| 16      | CTL      | I   | High voltage switch control pin         |  |

| 17      | FBP      | I   | Positive charge pump feedback pin       |  |

| 18      | VGH      | -   | Gate high voltage input                 |  |

| 19      | NC       | -   | No connect                              |  |

| 20      | VGHM     | 0   | Switch gate high voltage for TFT        |  |

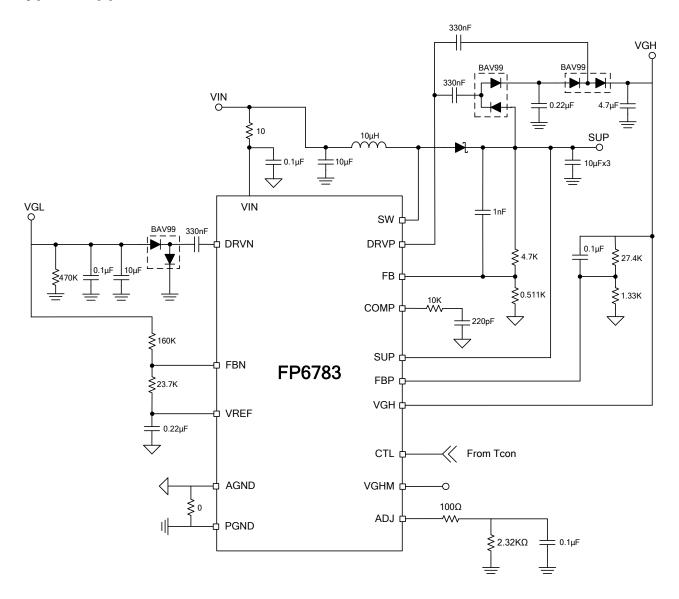

# **Block Diagram**

Figure 3. Block Diagram of FP6783

# **Absolute Maximum Ratings**

| • VIN to AGND                                                                      | 7V                                |

|------------------------------------------------------------------------------------|-----------------------------------|

| • SUP,SW to PGND                                                                   | 20V                               |

| • VGH to PGND                                                                      | 40V                               |

| Input Voltage (FB, FBN, FBP, CTL)                                                  | VIN + 0.3V                        |

| Output Voltage (COMP, VREF)                                                        | VIN + 0.3V                        |

| Output voltage 2 (ADJ, VGHM)                                                       | VGH + 0.3V                        |

| Output voltage 3 (DRVP, DRVN)                                                      | SUP + 0.3V                        |

| <ul> <li>Continuous Power Dissipation (T<sub>A</sub>=+25°C)</li> </ul>             |                                   |

| TQFN-20 (5mmx5mm)                                                                  | 2.5W                              |

| <ul> <li>Package Thermal Resistance, TQFN-20 (5mmx5mm) (θ<sub>JA</sub>)</li> </ul> |                                   |

| TQFN-20 (5mmx5mm)                                                                  | 40°C/W                            |

| Operating Junction Temperature Range (T <sub>J</sub> )                             |                                   |

| Storage Temperature Range                                                          |                                   |

| Note1: Stresses beyond those listed under "Absolute Maximum Ratings" may cause     | se permanent damage to the device |

| Recommended Operating Conditions                                                   |                                   |

| Supply Voltage V <sub>IN</sub>                                                     | +2.5V to +5.5V                    |

| Operation Temperature Range                                                        |                                   |

## **Electrical Characteristics**

$(V_{IN}=2.5V \text{ to } 5.5V, TA=-40 \text{ to } 85^{\circ}\text{C}, \text{ unless otherwise specified.}$  Typical values are tested at 25°C ambient temperature,  $V_{IN}=3.3V, V_{SUP}=12V)$

| Parameter                                       | Symbol             | Conditions                                                                     | Min   | Тур   | Max   | Unit |

|-------------------------------------------------|--------------------|--------------------------------------------------------------------------------|-------|-------|-------|------|

| Input Voltage Range                             | V <sub>IN</sub>    |                                                                                | 2.5   | -     | 5.5   | V    |

| SUP Input Voltage Range                         | $V_{SUP}$          |                                                                                | 6     | -     | 18    | V    |

| \(\lambda\)   1   1   1   1   1   1   1   1   1 | V <sub>UVLO</sub>  | Falling                                                                        | 2.05  | 2.15  | 2.25  | V    |

| VIN Under Voltage Lockout                       |                    | Rising                                                                         | 2.15  | 2.25  | 2.35  | V    |

| VIN Operating Current                           | IV <sub>IN</sub>   | V <sub>FB</sub> =1.5V, Not Switching                                           | -     | 0.56  | 0.8   | mA   |

| VIN Operating Current                           |                    | V <sub>FB</sub> =1.1V, Switching                                               | -     | 5.6   | 10.0  | mA   |

| Thermal Shutdown                                | T <sub>SHDN</sub>  |                                                                                | -     | 150   | -     | °C   |

| Reference Voltage                               |                    |                                                                                | •     |       |       |      |

| Reference Voltage                               | $V_{REF}$          | I <sub>VREF</sub> =100μA                                                       | 1.238 | 1.250 | 1.262 | V    |

| Line Regulation                                 |                    | V <sub>IN</sub> =2.5V to 5.5V,<br>I <sub>VREF</sub> =100μA                     | -     | 2     | 5     | %/V  |

| Load Regulation                                 |                    | I <sub>VREF</sub> =0~100μA                                                     | -     | 1     | 5     | %/mA |

| Oscillator                                      | •                  |                                                                                | 1     |       |       |      |

| Oscillation Frequency                           | Fosc               |                                                                                | 1.0   | 1.2   | 1.4   | MHz  |

| Maximum Duty Cycle                              | D <sub>MAX</sub>   |                                                                                | 86    | 90    | 94    | %    |

| Error Amplifier (Channel 1)                     |                    |                                                                                |       |       |       |      |

| Feedback Voltage                                | $V_{FB}$           |                                                                                | 1.238 | 1.250 | 1.262 | V    |

| Input Bias Current                              | I <sub>FB</sub>    | V <sub>FB</sub> =1V to 1.5V                                                    | -40   | 0     | 40    | nA   |

| Feedback-Voltage Line Regulation                | $V_{RI}$           | Level to produce<br>V <sub>COMP</sub> =1.25V<br>2.5V <v<sub>IN&lt;5.5V</v<sub> | -     | 0.05  | 0.15  | %/V  |

| Transconductance                                | G <sub>M</sub>     | Δ I=5μA                                                                        | -     | 105   | -     | μA/V |

| Voltage Gain                                    | A <sub>V</sub>     |                                                                                | -     | 1500  | -     | V/V  |

| N-MOS Switch (Channel 1)                        |                    |                                                                                |       |       |       |      |

| Current Limit                                   | I <sub>LIM</sub>   |                                                                                | 4.0   | 4.5   | -     | Α    |

| On-Resistance                                   | Ron                | I <sub>SW</sub> =1.0A                                                          | -     | 0.15  | 0.20  | Ω    |

| Leakage Current                                 | I <sub>SWOFF</sub> | V <sub>SW</sub> =12V                                                           | -     | 1     | 20    | μΑ   |

| Charge Pump (Channel 2 and Channel 3)           |                    |                                                                                |       |       |       |      |

| SUP Input Supply Range                          | VH                 |                                                                                | 6     | -     | 18    | V    |

| SUP Over Voltage Protect                        | V <sub>OVP</sub>   |                                                                                | -     | 18    | 20    | V    |

| Charge Pump Frequency                           | F <sub>OSCP</sub>  |                                                                                | 500   | 600   | 700   | KHz  |

| FBN Threshold Voltage                           | $V_{FBN}$          |                                                                                | 235   | 250   | 265   | mV   |

| FBN Input Bias Current                          | I <sub>FBN</sub>   | V <sub>FBN</sub> =-0.25V to 0.25V                                              | -40   | 0     | 40    | nA   |

# **Electrical Characteristics (Continued)**

$(V_{IN}=2.5V \text{ to } 5.5V, TA=-40 \text{ to } 85^{\circ}\text{C}, \text{ unless otherwise specified. Typical values are tested at } 25^{\circ}\text{C} \text{ ambient temperature, } V_{IN}=3.3V, V_{SUP}=12V)$

| V <sub>IN</sub> =3.3V, V <sub>SUP</sub> =12V)  Parameter | Symbol            | Conditions                       | Min   | Тур  | Max   | Unit |

|----------------------------------------------------------|-------------------|----------------------------------|-------|------|-------|------|

| FBP Threshold Voltage                                    | V <sub>FBP</sub>  |                                  | 1.238 | 1.25 | 1.262 | V    |

| FBP Input Bias Current                                   | I <sub>FBP</sub>  | V <sub>FBP</sub> =1V to 1.5V     | -40   | 0    | 40    | nA   |

| DRVN Leakage Current                                     | I <sub>OFF1</sub> | V <sub>FBN</sub> =0V, DRVN=SUP   | -     | 0.1  | 10    | μA   |

| DRVP Leakage Current                                     | I <sub>OFF2</sub> | V <sub>FBP</sub> =1.4V, DRVP=SUP | _     | 0.1  | 10    | μA   |

|                                                          | RONP1             | , , , ,                          | _     | 3    | 20    | Ω    |

| DRVN Switch R-ON                                         | RONP1             |                                  | _     | 3    | 20    | Ω    |

|                                                          | RONP2             |                                  | _     | 3    | 20    | Ω    |

| DRVP Switch R-ON                                         | RONP2             |                                  | _     | 3    | 20    | Ω    |

| Soft Start and Fault Detect                              |                   |                                  |       |      |       |      |

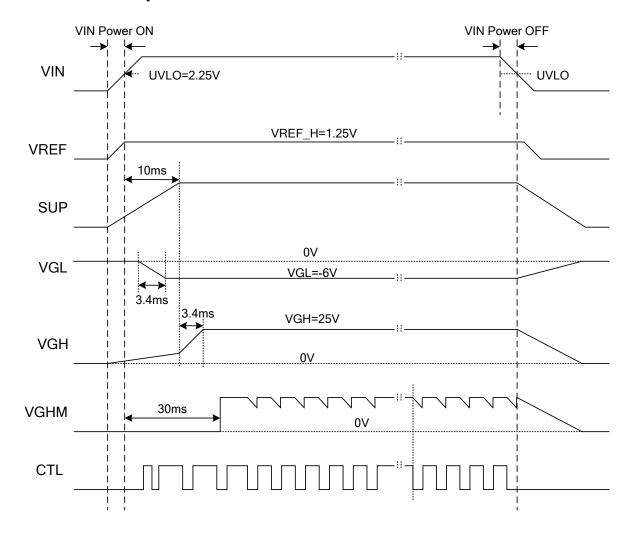

| PWM Soft Start Time                                      | t <sub>SS1</sub>  |                                  | -     | 10   | -     | ms   |

| VGH Soft Start Time                                      | t <sub>SS2</sub>  |                                  | -     | 3.4  | -     | ms   |

| VGL Soft Start Time                                      | t <sub>SS3</sub>  |                                  | -     | 3.4  | -     | ms   |

| During Fault Protect Trigger Time                        | t <sub>FP</sub>   |                                  | -     | 160  | -     | ms   |

| High Voltage Switch Start Delay Time                     | T <sub>DLY</sub>  |                                  | 24    | 30   | 36    | ms   |

| FB Fault Protection Voltage                              | V <sub>F1</sub>   |                                  | 0.95  | 1.00 | 1.05  | V    |

| FBN Fault Protection Voltage                             | V <sub>F2</sub>   |                                  | 0.4   | 0.45 | 0.5   | V    |

| FBP Fault Protection Voltage                             | V <sub>F3</sub>   |                                  | 0.95  | 1.00 | 1.05  | V    |

| FB Under Voltage Protect                                 |                   |                                  | -     | 0.1  | -     | V    |

| High Voltage Switch Controller                           |                   |                                  |       |      |       |      |

| CTL Input Low Voltage                                    | V <sub>IL</sub>   |                                  | -     | -    | 0.5   | V    |

| CTL Input High Voltage                                   | V <sub>IH</sub>   |                                  | 2     | -    | -     | V    |

| CTL Input Bias Current                                   | I <sub>B4</sub>   | V <sub>CTL</sub> =0 to VIN       | -40   | 0    | 40    | nA   |

| VGH Input Voltage Range                                  | $V_{GH}$          |                                  | -     | -    | 36    | V    |

| VGHM Output Voltage Range                                | $V_{GHM}$         |                                  | 2     | -    | -     | V    |

| Propagation Delay CTL to VGH                             | t <sub>PP</sub>   | VGH=25V                          | -     | 100  | 200   | ns   |

| VGH to VGHM Switch R-ON                                  | R <sub>ONSC</sub> |                                  | -     | 15   | 30    | Ω    |

| VGHM to ADJ Switch R-ON                                  | R <sub>ONDC</sub> |                                  | -     | 30   | 60    | Ω    |

| VGHM to GND Switch R-ON                                  | RONCG             |                                  | 1.5   | 2.5  | 3.5   | ΚΩ   |

# **Power On/Off Sequence**

Figure 4. Power on/off Sequence

#### **Application Information**

The FP6783 offers an all-in-one solution for TFT LCD. The chip includes a high-efficiency boost converter with a 18V/4.5A on-chip N-channel transistor for biasing of the LCD, a regulated positive charge pump, a regulated negative charge pump and a gate pulse modulation circuit. A voltage detector circuit generates a reset signal when the input voltage falls below the preset threshold.

#### **TFT LCD Boost Converter (SUP)**

The LCD panel SUP supply is generated from a high-efficiency PWM boost converter operating with control. Switching frequency is current mode 1.2MHz. on-period, During the TON, synchronous FET connects one end of the inductor to ground, therefore increasing the inductor current. After the FET turns off, the inductor switching node, SW, is charged to a positive voltage by the inductor current. The freewheeling diode turns on and the inductor current flows to the output capacitor.

The converter operates in continuous conduction mode (CCM) when the load current  $I_{LOAD}$  is at least one-half of the inductor ripple current  $\Delta_{ILPP}$ .

$$I_{LOAD} \ge \frac{\Delta I_{LPP}}{2} \times \frac{V_{IN}}{V_{BOOST}}$$

$$\Delta I_{LPP} = \frac{(V_{BOOST} - V_{IN}) \times V_{IN}}{F_{OSC} \times V_{BOOST}}$$

The output voltage VBOOST is determined by the duty cycle, D, and input voltage, VIN, as given by the following equation.

$$V_{BOOST} = \frac{V_{IN}}{1-D}$$

For smaller load current, the inductor current would decay to zero during the free-wheeling period and the output node would be disconnected from the inductor for a portion of the switching period. The converter is then operating in discontinuous mode (DCM).

Current mode control is well known for its robustness and fast transient response. An inner current feedback loop sets the on time and the duty cycle such that the current through the inductor equals to the current computed by the compensator. This loop acts within one switching cycle. A slope compensation ramp is added to suppress sub-harmonic oscillations.

An outer voltage feedback loop subtracts the voltage on the FB pin from the internal reference voltage and feeds the difference to the compensator operational transconductance (Gm) amplifier. This amplifier is compensated by an external R-C network to allow the user to optimize the transient response and loop stability for the specific application conditions.

#### **Positive Charge Pump (VGH)**

The positive charge pump is used to generate the TFT LCD gate on voltage. The output voltage, VGH, can be set by an external resistive divider. Voltage VFBP is typically 1.25V. A single stage charge pump can produce an output voltage less than approximately twice the charge pump input voltage SUP. The charge pump can deliver up to 20mA of current. The maximum voltage VGH should not exceed 36V if it is used to supply the GPM circuit.

#### **Negative Charge Pump (VGL)**

The negative charge pump is used to generate the TFT LCD gate off voltage. The output voltage, VGL, can be set by an external resistive divider. Voltage VFBN is typically 0.25V. A single stage charge pump can produce an output voltage less than approximately once the charge pump input voltage SUP. The charge pump can deliver up to 20mA of current.

#### Gate-pulse modulator (GPM)

The GPM is a flicker compensation circuit to reduce the coupling effect of gate lines, and is controlled by timing controller to modulate VGHM, the Gate-On voltage. This block is not activated until the below 2 conditions are satisfied: 1) The input voltage exceeds its UVLO, 2) No fault condition is detected. Once GPM activates and CTL is low, the internal switch between VGH and VGHM turns on and the switch between VGHM and ADJ turns off. If CTL is high, the internal switch between VGHM and VGHM turns off and the switch between VGHM and ADJ turns on. At that time, the falling time of the Gate-On voltage are programmable by an external resistor connected between ADJ and GND.

## **Application Information (Continued)**

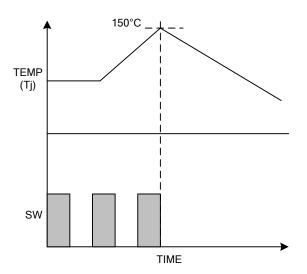

#### **Thermal-Overload Protection**

The FP6783 boost converter provides Thermal-overload Protection to prevent excessive power dissipation from overheating the IC. When the junction temperature exceeds Tj=150°C, a thermal sensor activates the fault protection, which shuts down (latches) all outputs. The thermal sensor turns internal circuitry on again after IC cycle the input voltage to clear the thermal shutdown latch.

#### **Output Fault Protection**

During steady-state operation, if feedback voltage of the main regulator falls below 1.0V, positive linear regulator falls below 1.0V or negative linear regulator falls below 450mV, the FP6783 activates an internal fault timer. If any condition indicates a continuous fault for the fault timer duration (160ms typ.) the IC sets the fault latch to shut down all its output. Once the fault condition is removed, cycle the VIN (below the UVLO falling threshold) to clear the fault latch and reactivate the device. The fault-detection circuit is disabled during the soft-start ramp.

#### **Over Current Protection**

The FP6783 has Over-Current Protection (OCP) that limits the peak inductor current in every switching cycle. It prevents large current from damaging the inductor and diode. Once the inductor current exceeds the current limit, the internal switch turns off immediately and shortens the duty cycle. The output voltage drops if the over-current condition occurs. Current limit is affected by the input voltage, duty cycle, and inductor value.

FP6783-Preliminary 0.3-NOV-2012 **10**

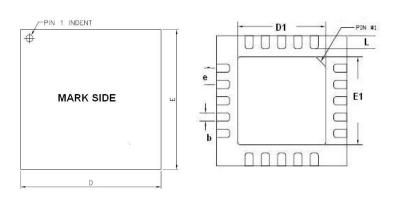

## **Outline Information**

TQFN-20 5mm×5mm (pitch 0.65mm) Package (Unit: mm)

| SYMBOLS | DIMENSION IN MILLIMETER |      |  |  |  |

|---------|-------------------------|------|--|--|--|

| UNIT    | MIN                     | MAX  |  |  |  |

| А       | 0.70                    | 0.80 |  |  |  |

| A1      | 0.00                    | 0.05 |  |  |  |

| С       | 0.18                    | 0.25 |  |  |  |

| E       | 4.95                    | 5.05 |  |  |  |

| E1      | 1.25                    | 3.25 |  |  |  |

| D       | 4.95                    | 5.05 |  |  |  |

| D1      | 1.25                    | 3.25 |  |  |  |

| Ĺ       | 0.35                    | 0.75 |  |  |  |

| b       | 0.25                    | 0.35 |  |  |  |

| е       | 0.60                    | 0.70 |  |  |  |

Note: Followed From JEDEC MO-220.

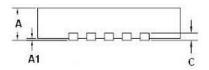

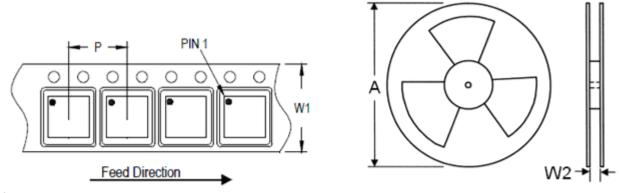

## **Carrier Dimensions**

| Tape Size | Pocket Pitch | Reel Size (A) |     | Reel Size (A) |           | Reel Width | Empty Cavity | Units per Reel |

|-----------|--------------|---------------|-----|---------------|-----------|------------|--------------|----------------|

| (W1) mm   | (P) mm       | in            | mm  | (W2) mm       | Length mm |            |              |                |

| 12        | 8            | 13            | 330 | 12.4          | 400~1000  | 3,000      |              |                |