**Product Specification**

RoHS Compliant

LEAD FREE

- Fingerprint area sensor

- NEW hard and scratch resistant protective surface coating

- Superior image quality

- 3D image with 256 true gray scale values

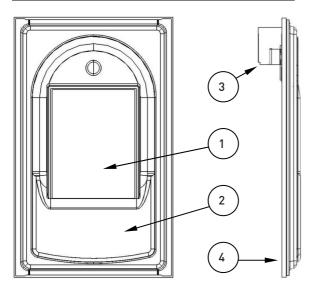

- Ergonomic frame for optimized finger guidance

- High speed SPI interface or Parallel interface

- Flex connector or BGA

- 3.3 and 2.5 volt operation

- >15kV ESD protection

- >1 million wear cycles

- Computer peripheral

- Physical access control

- Time and attendance

- Wireless devices

- Security application

- Medical equipment & storage

### General description

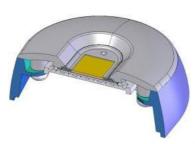

FPC1011F is a new compact CMOS fingerprint sensor with several significant advantages. FPC1011F deliveries superior image quality, with 256 gray scale values in every single pixel. The reflective measurement method sends an electrical signal via the frame directly into the finger. This technique enables the use of an unbeatably hard and thick protective surface coating. The sensor with its 3D pixel sensing technology can read virtually any finger; dry or wet.

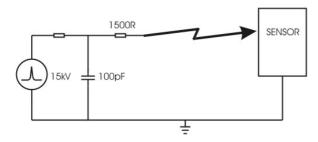

Thanks to the new extremely hard and durable surface coating, FPC1011F is protected against ESD well above 15 kV, as well as scratches, impact and everyday wear-and-tear. FPC1011F is delivered with a designed micro-ergonomic guidance frame, simplifying proper fingerprint guidance and hence improving algorithm performance.

FPC1011F is available in two configurations; either a versatile flex connector version, FPC1011F1, with a serial SPI interface or a standard BGA component, FPC1011F2, with both serial and parallel interface. In higher volumes, the micro-ergonomic frame can be made available in different colors and textures.

### Quick reference data

| PARAMETER DESCRIPTION     |                                      | VALUE             | UNIT     |

|---------------------------|--------------------------------------|-------------------|----------|

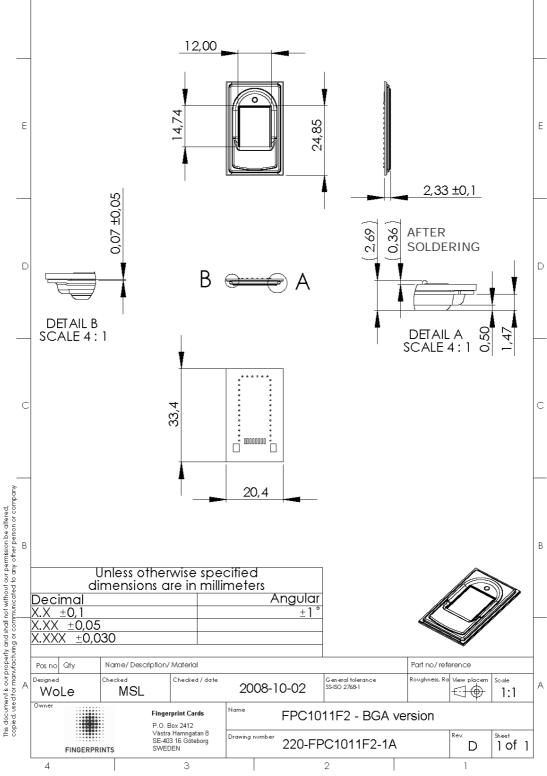

| Dimension                 | Sensor body (W x L x T)              | 20.4 x 33.4 x 2.3 | mm       |

| Interface                 | Serial SPI or Parallel               | 8/32              | pin      |

| Supply voltage            | VDC                                  | 2.5 - 3.3         | ٧        |

| Supply current            | Typical at 3.3V, 4MHz and RT         | 7                 | mA       |

| Supply current sleep mode | Power down                           | 10                | μА       |

| Clock frequency           | Serial SPI or Parallel               | 32                | MHz      |

| Read out speed            | Serial SPI or Parallel               | 4                 | Mpixel/s |

| Active sensing area       | Pixel matrix                         | 10.64 x 14.00     | mm       |

| Size sensing array        | Pixel matrix (363 dpi)               | 152 x 200         | pixel    |

| Pixel resolution          | 256 gray scale values                | 8                 | bit      |

| ESD protection            | IEC61000-4-2, level 4, air discharge | > 15              | kV       |

| Wear-and-tear             | No of wear cycles at 6N > 1 million  |                   | cycle    |

710-FPC1011F\_D\_Product-specification.doc

### Product Specification

### Table of contents

| 1           | Functional description               |    |

|-------------|--------------------------------------|----|

| 1.1         | Introduction                         |    |

| 1.2         | Block diagram                        |    |

| 1.3         | Technical features                   |    |

| 1.4         | Sensor surface robustness            |    |

| 1.5         | Application limits                   |    |

| 1.6         | Absolute maximum ratings             | 4  |

| 2           | Electrical characteristics           | 5  |

| _           |                                      |    |

| 3           | Operation                            |    |

| 3.1         | Introduction                         |    |

| 3.2         | Sensor technology                    |    |

| 3.3         | Image properties                     |    |

| 3.4         | Interface                            |    |

| 3.5         | Sensor readout                       | 8  |

| 4           | Serial mode                          | 10 |

| 4.1         | Instruction summary                  |    |

| 4.2         | Sensor setup                         |    |

| 4.3         | Serial mode instructions             |    |

| 4.4         | Sample Implementation                |    |

| _           | ·                                    |    |

| 5           | Parallel mode                        |    |

| 5.1         | Instruction summary                  |    |

| 5.2         | Sensor setup                         |    |

| 5.3         | Parallel mode instructions           |    |

| 5.4         | Sample Implementation                | 26 |

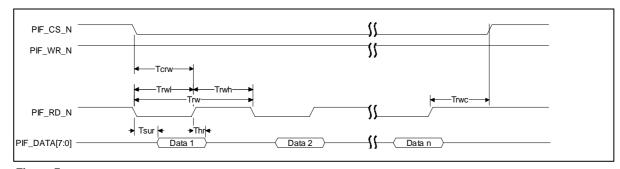

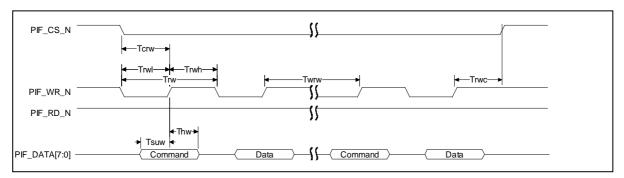

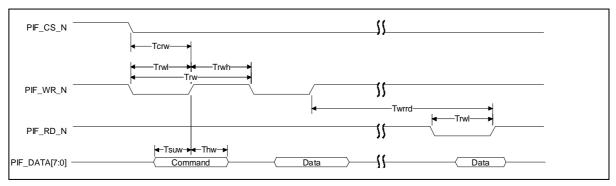

| 6           | Timing requirements                  | 27 |

| 6.1         | General timing                       | 27 |

| 6.2         | Serial mode timing                   |    |

| 6.3         | Parallel mode timing                 | 29 |

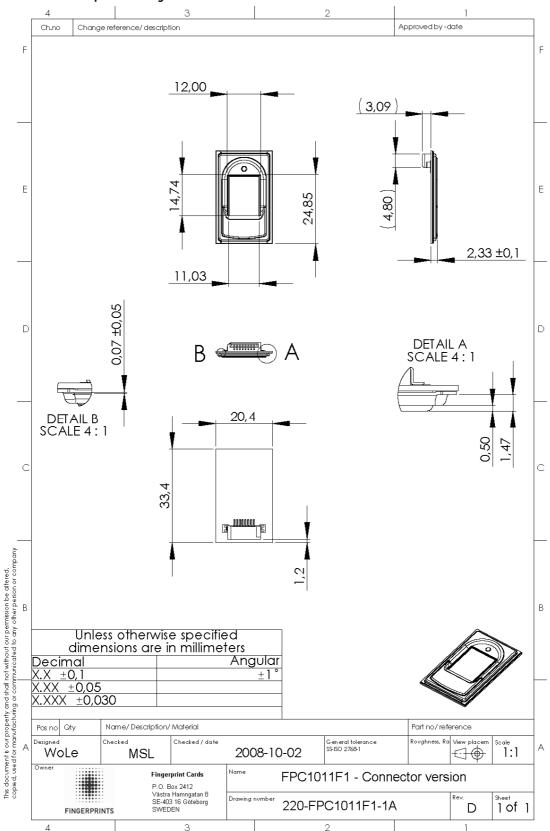

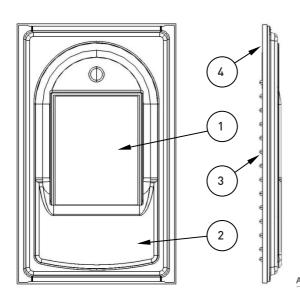

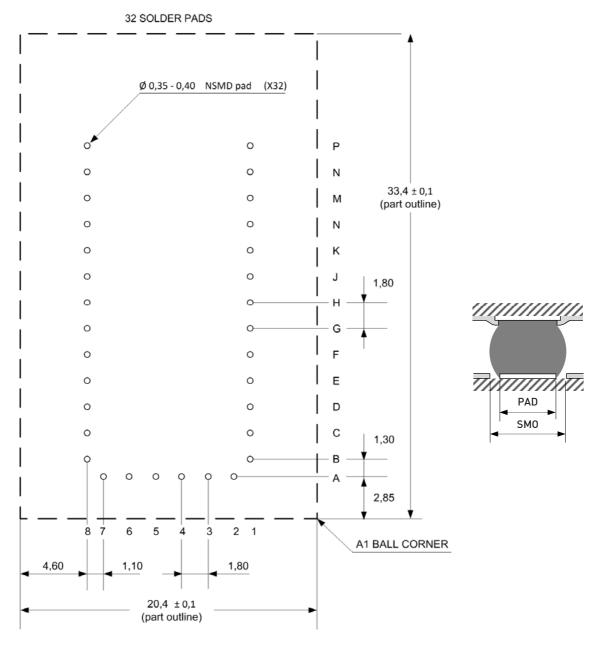

| 7           | Mechanical properties                | 21 |

| <b>7</b> .1 | FPC1011F1 - part drawing             |    |

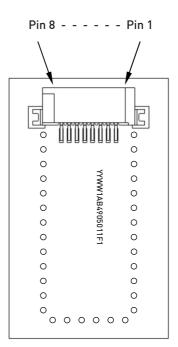

| 7.1         | FPC1011F1 - pin configuration        |    |

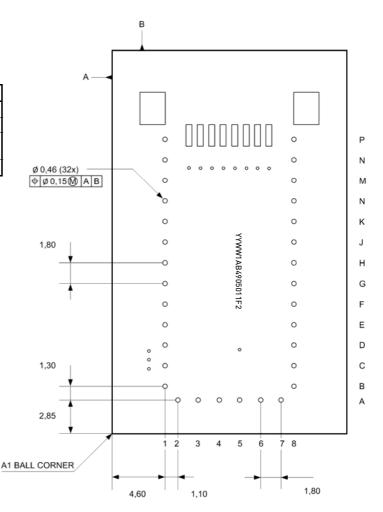

| 7.2         | FPC1011F2 - part drawing             |    |

| 7.3<br>7.4  | FPC1011F2 - pin configuration        |    |

| 7.4         |                                      |    |

| 8           | Cosmetic properties                  |    |

| 8.1         | Sensor surface quality               |    |

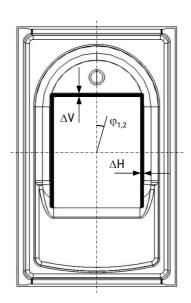

| 8.2         | Assembly accuracy                    | 35 |

| 9           | Application information              | 36 |

| 9.1         | Sensor integration                   |    |

| 9.2         | Sensor shut down mode                |    |

| 9.3         | ESD protection                       |    |

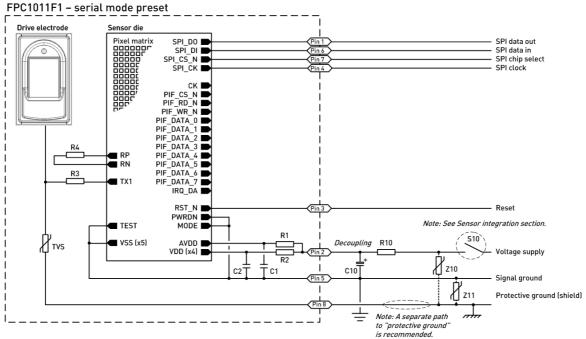

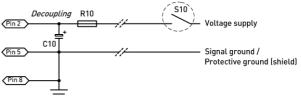

| 9.4         | FPC1011F1 - reference layout         |    |

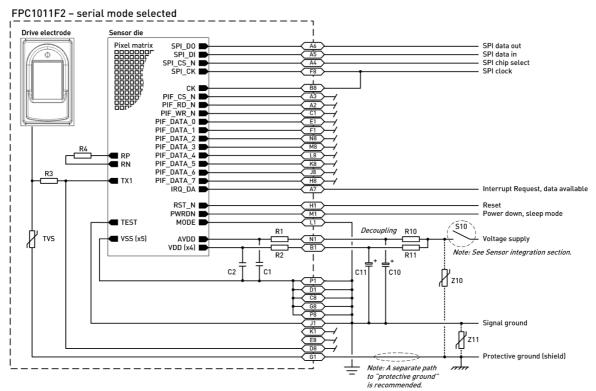

| 9.5         | FPC1011F2 - reference layout         |    |

| 9.6         | FPC1011F1 - mating flex strip        |    |

| 9.7         | FPC1011F2 - PCB layout pattern       |    |

| 9.8         | FPC1011F2 - reflow soldering profile |    |

| 10          |                                      |    |

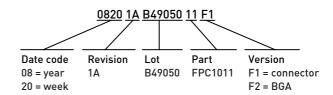

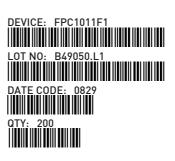

| 10          | Order information                    |    |

| 10.1        | Part numbers                         |    |

| 10.2        | Production codes                     |    |

| 10.3        | Package information                  |    |

| 10.4        | ESD sensitivity                      | 45 |

| 11          | Document revision history            | 46 |

| 40          | ·                                    |    |

| 12          | Contact information                  | 46 |

**Product Specification**

### 1 Functional description

#### 1.1 Introduction

The FPC1011F sensor component is suitable for numerous types of authentication systems. These systems may be based on highly integrated low power solutions utilizing Fingerprint Cards' (*Fingerprints*) companion chip, or a large variety of standard microcontrollers or high performance DSPs.

The sensor package is built around Fingerprint Cards' sophisticated 3rd generation CMOS implementation FPC1011. The FPC1011 offers both a serial SPI interface and a parallel asynchronous interface. The communication interface is easily selected by means of a separate interface selection pin (MODE).

Two package configurations are available; an 8 pin flex connector (FPC1011F1) or a 32 ball BGA (FPC1011F2).

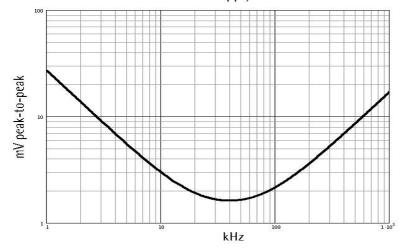

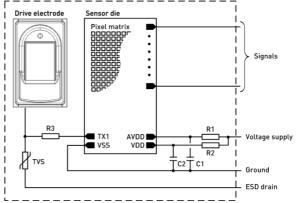

### 1.2 Block diagram

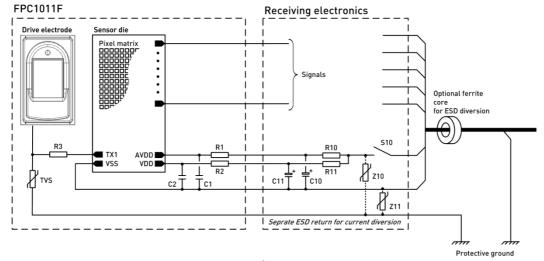

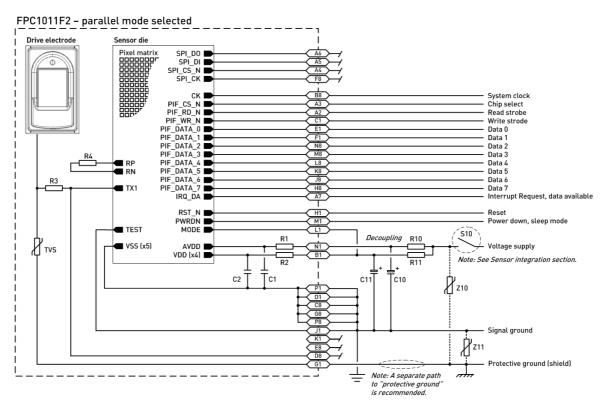

Depending on selected package configuration; two separate hardware interfaces are available. Both interfaces are indicated in the figure below. Signals marked "only BGA" are only available in FPC1011F2, the 32 ball BGA version. In FPC1011F1 these signals are preset or re-routed to obtain an 8 pin serial interface.

### FPC1011F1 preset configuration:

- Analog and digital power supply are combined

- System clock and SPI clock are combined

- Power down is disabled

- Mode pin is preset to serial interface

- Parallel interface cannot be accessed

#### **FPC1011F** Drive electrode SPI interface SPI (x3) SPI CK I SPI clock System clock (only BGA) Parallel interface (only BGA) RST N ■ Power down (only BGA) PWRDN MODE Interface select (only BGA) R3 AVDD Analog voltage supply (only BGA) VDD Voltage supply TVS Ground ESD drain

Block diagram - Overview

**Product Specification**

#### 1.3 Technical features

| PARAMETER             | DESCRIPTION                                          | VALUE             | UNIT  |

|-----------------------|------------------------------------------------------|-------------------|-------|

| Dimension             | Sensor body                                          | 20.4 x 33.4 x 2.3 | mm    |

|                       | Flex connector type, sensor body plus connector      | 20.4 x 33.4 x 5.4 | mm    |

|                       | BGA type, sensor body plus solder balls              | 20.4 x 33.4 x 2.7 | mm    |

| Active sensing area   |                                                      | 10.64 x 14.00     | mm    |

| Size sensing array    |                                                      | 152 x 200         | pixel |

| Spatial resolution    |                                                      | 363               | dpi   |

| Pixel resolution      | 256 gray scale levels                                | 8                 | bit   |

| Operating temperature |                                                      | - 20 + 60         | °C    |

| Storage temperature   |                                                      | - 40 + 85         | °C    |

| ESD                   | IEC61000-4-2 level 4, air discharge                  | > ±15             | kV    |

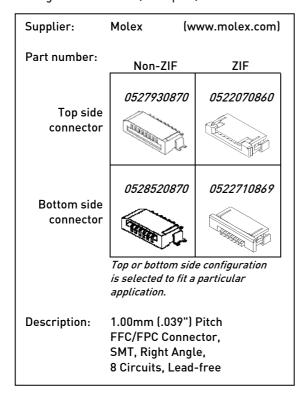

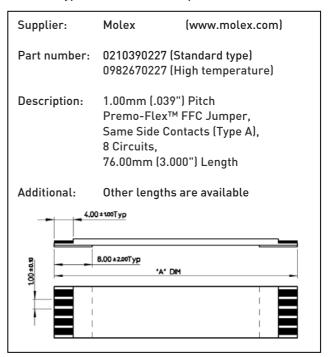

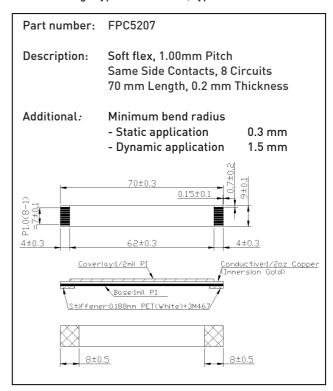

| Package type          | FPC1011F1 - 8 pin flex connector, 1mm pitch, Non-ZIF | 8                 | pin   |

|                       | FPC1011F2 - 32 ball BGA                              | 32                | pin   |

#### 1.4 Sensor surface robustness

| PARAMETER                | DESCRIPTION                                                                                                         | CONDITION               | RESULT |

|--------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------|--------|

| Mechanical wear-and-tear | Repetitive wear-and-tear cycles                                                                                     | > 1 000 000 cycles @ 6N | PASS   |

| Foreign substances       | Repetitive strokes with:                                                                                            | 200 cycles @ 6N         | PASS   |

|                          | Acetone, Artificial sweat, Coca cola, Coffee, Isopropyl,<br>Ethanol, Ketchup, Mosquito repellent, Oil, Petrol, Soap |                         |        |

### 1.5 Application limits

The FPC1011F package is designed for indoor, non-condensing, applications. Do not subject the sensor component to direct sunlight for extended periods. The sensor surface is hard and extremely robust, and will withstand years of normal wear-and-tear. However, do not subject the sensor surface to sharp or hard objects since this might cause permanent damage.

Cleaning should be done with a soft cotton textile. Do not subject the sensor surface to excessive mechanical force. The fingerprint sensor is a high-performing SMD device and should be handled accordingly. Additional information on proper product integration is offered in the section *Sensor integration*.

### 1.6 Absolute maximum ratings

| Pressure on sensor <sup>1</sup> | 25 N                              | affect device reliability.                                                                                 |

|---------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------|

| ESD on IO's                     | ±2 kV                             | specification, is not implied. Exposure to absolute maximum rating conditions for extended periods, may    |

| Total power dissipation         | 50 mW                             | beyond those indicated as normal operation in this                                                         |

| Output voltage                  | -0.5 V to V <sub>DD</sub> + 0.5 V | the device. This is a stress rating only. Functional operation of the device, at these or other conditions |

| Input voltage                   | -0.5 V to V <sub>DD</sub> + 0.5 V | Stress beyond values listed under "Absolute<br>Maximum Ratings" may cause permanent damage to              |

| Supply voltage V <sub>DD</sub>  | -0.5 V to +7.0 V                  | Note:                                                                                                      |

Note 1: Additional information on proper product integration is offered in the section, Sensor integration.

s subject to change without prior notice 710-FPC1011F D Product-specification.doc

### 2 Electrical characteristics

Measured at room temperature (RT)

| SYMBOL           | PARAMETER                                | CONDITION                    | MIN                 | TYP                 | MAX                | UNIT |

|------------------|------------------------------------------|------------------------------|---------------------|---------------------|--------------------|------|

| FPC1011F1        | - serial mode is preset                  |                              |                     |                     |                    |      |

| $V_{DD}$         | Voltage supply (total)                   |                              | 2.35                | 2.5/3.3             | 3.45               | ٧    |

| I <sub>DD</sub>  | Current supply, total                    | V <sub>DD</sub> = 2.5V@4MHz  | -                   | 7                   | 14                 | mA   |

|                  |                                          | $V_{DD} = 2.5V@32MHz$        | -                   | 9                   | -                  | mA   |

|                  |                                          | $V_{DD} = 3.3V@4MHz$         | -                   | 7                   | 14                 | mA   |

|                  |                                          | $V_{DD} = 3.3V@32MHz$        | -                   | 12                  | -                  | mA   |

| FPC1011F2        | - serial mode                            |                              |                     |                     |                    |      |

| $V_{DD}$         | Voltage supply (digital)                 |                              | 2.35                | 2.5/3.3             | 3.45               | ٧    |

| $AV_{DD}$        | Analog voltage supply                    |                              | 2.35                | 2.5/3.3             | 3.45               | ٧    |

| I <sub>DD</sub>  | Current supply, total                    | $V_{DD} = 2.5V@4MHz$         | -                   | 7                   | -                  | mA   |

|                  |                                          | V <sub>DD</sub> = 2.5V@32MHz | -                   | 9                   | -                  | mA   |

|                  |                                          | $V_{DD} = 3.3V@4MHz$         | -                   | 7                   | -                  | mA   |

|                  |                                          | $V_{DD} = 3.3V@32MHz$        | -                   | 12                  | -                  | mA   |

| I <sub>DDS</sub> | Current supply, sleep mode               | PWRDN high                   | -                   | 10                  | -                  | uA   |

| FPC1011F2        | - parallell mode                         |                              |                     |                     |                    |      |

| $V_{DD}$         | Voltage supply (digital)                 |                              | 2.35                | 2.5/3.3             | 3.45               | ٧    |

| $AV_DD$          | Analog voltage supply                    |                              | 2.35                | 2.5/3.3             | 3.45               | ٧    |

| I <sub>DD</sub>  | Current supply, total                    | $V_{DD} = 3.3V@8MHz$         | -                   | TBD                 | -                  | mA   |

| $I_{DDS}$        | Current supply, sleep mode               | PWRDN high                   | -                   | 10                  | -                  | uA   |

| FPC1011F1/       | /F2 - digital inputs                     |                              |                     |                     |                    |      |

| V <sub>IL</sub>  | Logic '0' voltage                        |                              | N/A                 | N/A                 | 0.2V <sub>DD</sub> | ٧    |

| V <sub>IH</sub>  | Logic '1' voltage                        |                              | 0.8V <sub>DD</sub>  | N/A                 | N/A                | ٧    |

| I <sub>IL</sub>  | Logic '0' current (V <sub>I</sub> = GND) |                              | -                   | -                   | ±10                | uA   |

| I <sub>IH</sub>  | Logic '1' current $(V_I = V_{DD})$       |                              | -                   | -                   | ±10                | uA   |

| C <sub>IND</sub> | Input capacitance                        |                              | -                   | 6                   | -                  | pF   |

|                  | /F2 - digital outputs                    |                              |                     |                     |                    |      |

| V <sub>oL</sub>  | Logic '0' output voltage                 |                              | -                   | 0.2                 | 0.4                | ٧    |

| V <sub>OH</sub>  | Logic '1' output voltage                 |                              | 0.85V <sub>DD</sub> | 0.90V <sub>DD</sub> | -                  | ٧    |

Note: Details on clock frequency is available in the General Timing section.

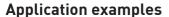

### Recommended 3.3V supply noise limit

Differential power supply disturbance

The graph shows the supply disturbance level (sinus rms), which will give less than one gray level rms disturbance in the fingerprint image readout. If the supply voltage is noisy, additional filtering may be required.

If separate (splitted) power supplies or long connection leads are used, it is important to maintain a synchronized power on voltage curve (equivalent ramp), for both  $V_{DD}$  and  $AV_{DD}$ . This care is necessary to avoid possible latch-up problems.

This specification is subject to change without prior notice

710-FPC1011F D Product-specification.doc

**Product Specification**

### 3 Operation

### 3.1 Introduction

If the sensor is used together with a companion chip from Fingerprint Cards, no detailed knowledge about the sensor circuit/matrix is required in order to operate the sensor component properly.

However, if the sensor component is used together with e.g. a standard micro-controller or a DSP, a detailed understanding of the sensor operation is recommended.

### 3.2 Sensor technology

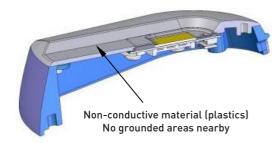

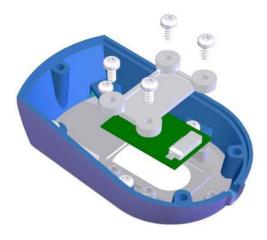

The sensor component uses an architecture where individual sensor elements sense a separate charge from the finger. A general block diagram for the sensor circuit is shown in the figure below.

The TX1-signal is used to supply a drive signal to the finger. Hence this signal is connected to an electrode (frame) directly surrounding the sensor area. This electrode (frame) is also part of the ESD protection.

Block diagram - Sensor circuit

**Product Specification**

### 3.3 Image properties

The FPC1011F sensor matrix contains 30400 pixels. On rare occasions some pixels may not be fully operational, called pixel errors (PE). A small number of imperfections do NOT degrade biometric performance. All sensors are thoroughly tested to ensure excellent image quality.

To verify the image quality and establish a proper signal-to-noise ratio (SNR), internal test functionality based on test patterns is implemented; Checkerboard and Inverted Checkerboard. To ensure conformity of the results, tests are always performed on these two internal test patterns, generated by the SENSEMODE parameter.

To meet image quality standards, test patterns must satisfy the following requirements:

| PARAMETER                      | VALUE            |

|--------------------------------|------------------|

| PE total                       | ≤60 pixels       |

| PE on any single row           | ≤30 pixels       |

| PE in any single column        | $\leq$ 40 pixels |

| PE within any 12x12 pixel area | ≤4 pixels        |

Note: Entire non-operational columns or rows are not accepted and hence scrapped.

A pixel error is defined as a pixel value that differs more than 20 grayscale levels from its local image median. The local image median is the median value over a sub-image consisting of 5 complete rows, where one of the rows contains the error pixel. (The sub-images are defined as rows 1-5, 6-10, 11-15, ..., 196-200).

A proper Checkerboard (CB) pattern and Inverted Checkerboard (ICB) pattern is generated with the following parameters:

| DRIVC | ADCREF | SENSEMODE |

|-------|--------|-----------|

| 70    | 3      | 1 (CB)    |

| 70    | 3      | 2 (ICB)   |

Note: Further details are available in the SENSEMODE register setup.

#### 3.4 Interface

The sensor circuit contains two separate interfaces; - a Serial Peripheral Interface (SPI) and - a fast parallel asynchronous interface.

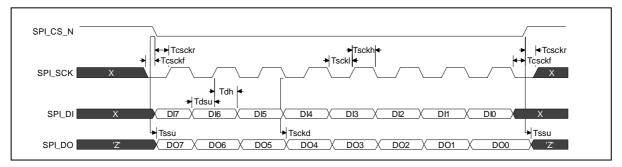

The SPI interface enables high-speed readout of data with a minimum of wires. The SPI interface supports a speed up to the current system clock speed. This feature makes the sensor usable for a wide range of control units. The SPI interface is a slave interface with CPHA = '0' and CPOL = '0'.

The parallel interface is included to enable even faster communication with a large variety of micro-controllers. The parallel interface is asynchronous and uses RD\_N and WR\_N as read and write strobes when accessing the sensor.

Through the communication interface, pixel data from the sensor circuit is entered into a FIFO, which in turn is read by applying read instructions. This FIFO enables a burst read out speed of up to 32 Mpixel/s in parallel mode. The maximum average readout speed in parallel mode is 4 Mpixel/s. The maximum readout speed in serial mode is 4 Mpixel/s.

A mode pin selects between the two interfaces (Interface select). Only one interface may be used at a time.

| MODE     | ENABLER    | DESCRIPTION                |

|----------|------------|----------------------------|

| Serial   | MODE = '0' | SPI interface enabled      |

| Parallel | MODE = '1' | Parallel interface enabled |

Interface selection using the mode pin

| TYPE      | SERIAL | PARALLEL            |

|-----------|--------|---------------------|

| FPC1011F1 | Yes    | No (mode is preset) |

| FPC1011F2 | Yes    | Yes                 |

Available interfaces - select with mode pin

**Product Specification**

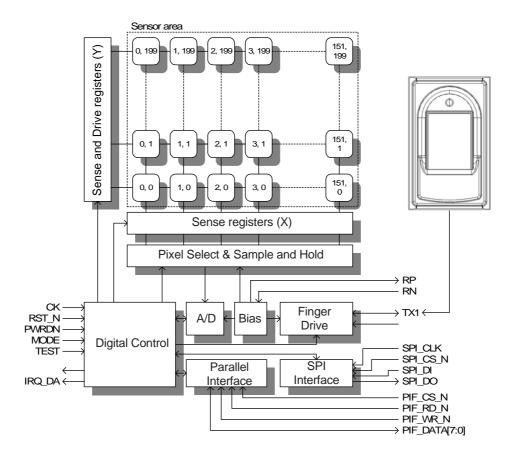

#### 3.5 Sensor readout

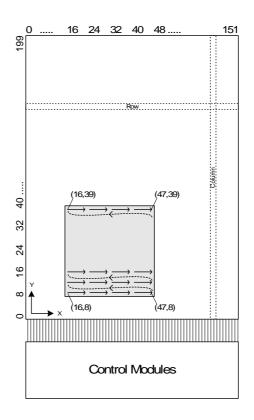

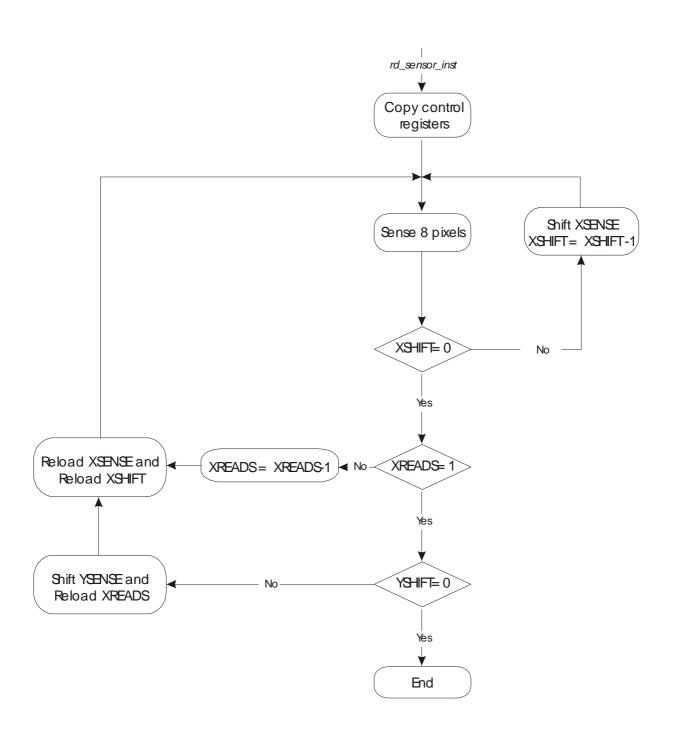

The sensor matrix consists of 152 x 200 sensor elements. The entire sensor, or a part of it, is read by applying a read sensor instruction. The size of the active area is set by the values of the XSHIFT and YSHIFT registers.

The default values for these registers select the complete sensor area to be read once. The readout sequence is illustrated in the figure below.

During all read operations, 8 pixels are captured simultaneously. By default the first 8 pixels being read are pixel (0,0) to (7,0), followed by pixels (8,0) to (15,0).

The readout area can be reduced by setting the XSHIFT and YSHIFT registers.

The sense area (a row of 8 pixels) is shifted in the x-direction XSHIFT times before it is shifted in the y-direction. The default start position can be changed by manually loading the SENSEX and SENSEY registers.

By setting XSENSE and YSENSE to start with pixels (16,8) to (23,8) and setting XSHIFT to 3 and YSHIFT to 31 the rectangle defined by the pixels (16,8) and (47,39) will be read, giving a total of 1024 pixels. Partial readout is illustrated in the figure above.

It is possible to read one row of pixels several times before shifting to the next row. This is done by setting the XREADS register.

The number of pixels being read is given by the following formula:

#pixels =

$$8 \cdot (XSHIFT+1) \cdot (YSHIFT+1)$$

Figure on next page shows the read sequence in detail.

Sensor read sequence

**Product Specification**

### 4 Serial mode

In serial mode all communication is done through the serial SPI interface. The available commands are described in this section.

#### 4.1 Instruction summary

| INSTRUCTION | INSTRUCTION CODE | DESCRIPTION                                                                                                                                     |  |

|-------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| rd_sensor   | 11 <sub>H</sub>  | Start sensing of finger. Data is placed in the FIFO.                                                                                            |  |

| rd_spidata  | 20 <sub>H</sub>  | Read from FIFO (only applicable when the SPI interface is used)                                                                                 |  |

| rd_spistat  | 21 <sub>H</sub>  | Read internal status registers in the SPI interface (only applicable when the SPI interface is used)                                            |  |

| rd_regs     | 50 <sub>H</sub>  | Read internal registers. All registers are read in one operation. The register content is placed in the FIFO.                                   |  |

| wr_drivc    | 75 <sub>H</sub>  | Write DRIVC register. Set finger drive amplitude.                                                                                               |  |

| wr_adcref   | 76 <sub>H</sub>  | Write ADCREF register. Set ADC sensitivity.                                                                                                     |  |

| wr_sensem   | 77 <sub>H</sub>  | Write SENSEMODE register. Set self-test mode.                                                                                                   |  |

| wr_fifo_th  | 7C <sub>H</sub>  | Write FIFO_TH register. Set the FIFO fill threshold for activation of data available signal, DA bit in SPI_STAT register or IRQ_DA (FPC1011F2). |  |

| wr_xsense   | 7F <sub>H</sub>  | Shift data into the XSENSE register.                                                                                                            |  |

| wr_ysense   | 81 <sub>H</sub>  | Shift data into the YSENSE register.                                                                                                            |  |

| wr_xshift   | 82 <sub>H</sub>  | Write XSHIFT register. Set number of shifts to be performed in the x-direction.                                                                 |  |

| wr_yshift   | 83 <sub>H</sub>  | Write YSHIFT register. Set number of shifts to be performed in the y-direction.                                                                 |  |

| wr_xreads   | 84 <sub>H</sub>  | Write XREADS register. Set number of times the same row should be read before shifting the YSENSE register.                                     |  |

### 4.2 Sensor setup

If the FPC1011F sensor is **NOT** used together with a companion chip from Fingerprint Cards, but instead with a standard micro-controller, a DSP or similar, an easy register setup is necessary.

The appropriate default parameters are indicated in table below. For detailed instructions on how to perform the actual register setup, please refer to the *Serial mode instructions* section in this document.

| DRIVC | ADCREF | SENSEMODE |

|-------|--------|-----------|

| 127   | 2      | 0         |

### 4.3 Serial mode instructions

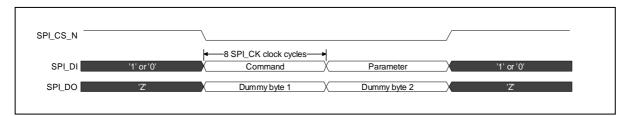

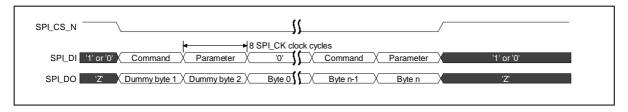

Below all instructions are described in detail. Relevant timing diagrams are showed in the section *Timing properties*.

In addition to the long shift-registers controlling the pixels in the sensor array, the sensor component contains one SPI status register and 13 control registers. All write instructions to registers operate in the same way. The FIFO-pointers are reset when any instruction except <rd\_spidata> and <rd\_spistat> is applied.

**Product Specification**

#### Read sensor instruction

| INSTRUCTION             | rd_sensor               | [ 11 <sub>H</sub> ] |

|-------------------------|-------------------------|---------------------|

| Mode                    | serial                  |                     |

| Input parameters        | 1 dummy byte            |                     |

| Data delay <sup>1</sup> | (363±2)t <sub>CLK</sub> |                     |

| Returned bytes          | 0                       |                     |

Note1: Data delay is the delay time from when the instruction is given, until data is available in the FIFO. The uncertainty, ±2 clock cycles, is only valid if separate SPI and system clocks are used (only possible in FPC1011F2 in serial model.

This instruction is used to read the entire sensor or a part of it. Timing for reading in serial mode is defined in the section *Timing properties*.

The read sensor instruction is only used to start the sense-sequence, and the instruction itself does not return any data. The first data from the sensor array will enter the FIFO after approximately 363 clock-cycles. After that, a new byte will enter the FIFO every 8th clock-cycle until the area defined by the XSENSE, YSENSE, XSHIFT and YSHIFT registers has been read.

When the FIFO is filled to a level equal to or greater than the value set by the FIFO\_TH register, the SPI\_STAT register will indicate that data is ready for fetching.

If the FIFO is filled up with data, overflow is avoided by stalling sensing until data is read from the FIFO. During this stall-period all analog modules are active, and the ASIC will draw current as during a regular sense operation.

Read SPI data instruction

| INSTRUCTION      | rd_spidata   | ( 20 <sub>H</sub> ) |

|------------------|--------------|---------------------|

| Mode             | serial       |                     |

| Input parameters | 1 dummy byte |                     |

| Data delay       | 0            |                     |

| Returned bytes   | n            |                     |

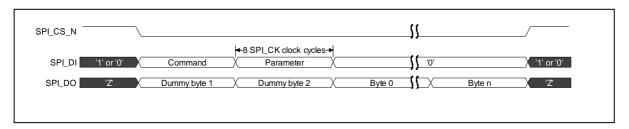

After the read SPI data instruction is sent, <rd\_spidata>, pixel data will be returned as shown in Figure 11. Data will continue to be returned as long as SPI\_CS\_N and SPI\_DI are kept low.

SPI\_DI should be kept low after the <rd\_spidata>, instruction is entered to avoid the subsequent byte to be interpreted as a new instruction.

The reading of data can be stopped at any time without data-loss by setting SPI\_CS\_N high, as long as SPI\_CS\_N is set high between the last bit of the current byte being read and the first bit in the next byte.

If SPI\_CS\_N is released at any other time (e.g. during a byte transfer) one or more bytes will be lost. To continue readout after a stop caused by setting SPI\_CS\_N high, the <rd\_spidata> instruction has to be applied again.

Product Specification

### Read SPI status instruction

| INSTRUCTION      | rd_spistat   | ( 21 <sub>H</sub> ) |

|------------------|--------------|---------------------|

| Mode             | serial       |                     |

| Input parameters | 1 dummy byte |                     |

| Data delay       | 0            |                     |

| Returned bytes   | 1            |                     |

The SPI status register holds status information for the SPI interface. When the read SPI status instruction is applied, the content of the SPI\_STAT register is returned. Applying this instruction does not interrupt sensor readout if sensor readout is in progress.

When the FIFO fill threshold is reached, the DA bit in the SPI\_STAT register and the IRQ\_DA signal will be set. The IRQ\_DA signal pin is not available in FPC1011F1, only in FPC1011F2.

| REGIS   | STER     |     | SPI_STAT                                                |         |           |         |       |

|---------|----------|-----|---------------------------------------------------------|---------|-----------|---------|-------|

| Size (a | ctive bi | ts) | 3                                                       |         |           |         |       |

| 7       | 6        | 5   | 4                                                       | 3       | 2         | 1       | 0     |

| -       | -        | -   | -                                                       | -       | UFL       | STL     | DA    |

|         | Reset    |     | 00 <sub>H</sub> (default value)                         |         |           |         |       |

|         | 001      |     | Data a                                                  | vailabl | e in FIF  | 0.      |       |

|         | 010      |     | Stall. Bit is set if sensing is staldue to a full FIFO. |         |           | stalled |       |

| 100     |          |     | Under                                                   |         | it is set | if unde | rflow |

**Product Specification**

### Read registers instruction

| INSTRUCTION      | rd_regs      | ( 50 <sub>H</sub> ) |

|------------------|--------------|---------------------|

| Mode             | serial       |                     |

| Input parameters | 1 dummy byte |                     |

| Data delay       | 0            |                     |

| Returned bytes   | 0            |                     |

The read register instruction fills the FIFO with the value of all the internal control registers. The order in which the registers are entered into the FIFO is given in the table below.

This instruction does not return any data. Data has to be read with the <rd\_spidata> instruction The read SPI data instruction can directly follow this instruction for readout of register data.

| RETURN ORDER | REGISTER        |

|--------------|-----------------|

| 1            | STATUS          |

| 2            | NOT USED        |

| 3            | DRIVC           |

| 4            | ADCREF          |

| 5            | SENSEMODE       |

| 6            | FIFO_TH         |

| 7            | NOT USED        |

| 8            | XSHIFT          |

| 9            | YSHIFT          |

| 10           | XREADS          |

| 11           | NOT USED        |

| 12           | NOT USED        |

| 13           | NOT USED        |

| 14           | 00 <sub>H</sub> |

| 15           | 00 <sub>H</sub> |

| 16           | 00 <sub>H</sub> |

Return order for register values

The STATUS register is a read only register, which holds the status information for the FIFO.

| REGIS              | STER |                                         | STATUS                          |          |      |                     |     |  |  |

|--------------------|------|-----------------------------------------|---------------------------------|----------|------|---------------------|-----|--|--|

| Size (active bits) |      | 2                                       |                                 |          |      |                     |     |  |  |

| 7                  | 6    | 5                                       | 4                               | 3        | 2    | 1                   | 0   |  |  |

| -                  | -    | -                                       | -                               | -        | -    | STL                 | UFL |  |  |

| Reset              |      |                                         | 00 <sub>H</sub> (default value) |          |      |                     |     |  |  |

|                    | 01   |                                         | Underflow.                      |          |      |                     |     |  |  |

|                    | 0.   |                                         | Bit is set if underflow occurs  |          |      | s.                  |     |  |  |

| 10                 |      | Stall. Bit is set if sensing is stalled |                                 |          |      |                     |     |  |  |

|                    | 10   |                                         | due to                          | a full F | IFO. | due to a full FIFO. |     |  |  |

Remaining control registers (3-10) can be operated with both read and write instructions. Details on these registers are available together with the write instructions for each register.

All flag generation is based on comparing writepointer with read pointer synchronized to SPI clock.

This means that if a read instruction, resulting in an

underflow, occurs one clock period before new data

enters the FIFO, an undetected underflow will occur.

To avoid this, the procedure for reading from the

FIFO, which is outlined in FIFO\_TH register

description, should be followed.

The entire register is reset when a <rd\_regs> instruction is executed.

Product Specification

### Write to DRIVC register

| INSTRUCTION      | wr_drivc | ( 75 <sub>H</sub> ) |

|------------------|----------|---------------------|

| Mode             | serial   |                     |

| Input parameters | 1 byte   |                     |

| Data delay       | NA       |                     |

| Returned bytes   | NA       |                     |

The DRIVC register sets the amplitude for the drive signal, active on the drive electrode (frame).

The recommended DRIVC setting is listed in the Sensor setup section. With default value set, the drive signal is disabled.

| REGIS          | REGISTER            |                |                                     | DRIVC |   |     |   |

|----------------|---------------------|----------------|-------------------------------------|-------|---|-----|---|

| Size (a        | ctive bi            | ts)            | 8                                   |       |   |     |   |

| 7              | 6                   | 5              | 4                                   | 3     | 2 | 1   | 0 |

| Х              | Х                   | Х              | x x x x x                           |       |   |     | х |

| Res            | set                 |                | 00 <sub>H</sub> (default value)     |       |   |     |   |

| 0 <sub>D</sub> |                     |                | Min voltage, Electrode drive off    |       |   | off |   |

| 127            | 127 <sub>D</sub>    |                | Approximately V <sub>DD</sub> /2    |       |   |     |   |

| 128            | 8 <sub>D</sub> - 25 | 5 <sub>D</sub> | Max voltage, approx V <sub>DD</sub> |       |   |     |   |

### Write to ADCREF register

| INSTRUCTION      | wr_adcref | ( 76 <sub>H</sub> ) |

|------------------|-----------|---------------------|

| Mode             | serial    |                     |

| Input parameters | 1 byte    |                     |

| Data delay       | NA        |                     |

| Returned bytes   | NA        |                     |

The ADCREF register sets the dynamic range for the internal A/D converter. This register is set to '11' at reset.

The recommended ADCREF setting is listed in the *Sensor setup* section.

| REGIS   | STER     | ER ADCREF |                                 |   |   |   |   |

|---------|----------|-----------|---------------------------------|---|---|---|---|

| Size (a | ctive bi | ts)       | 2                               |   |   |   |   |

| 7       | 6        | 5         | 4                               | 3 | 2 | 1 | 0 |

| -       | -        | -         | -                               | - | - | Х | х |

| Reset   |          |           | 00 <sub>H</sub> (default value) |   |   |   |   |

| 00      |          |           | 0.125 x V <sub>DD</sub>         |   |   |   |   |

| 01      |          |           | 0.250 x V <sub>DD</sub>         |   |   |   |   |

|         | 10       |           | 0.375 x V <sub>DD</sub>         |   |   |   |   |

|         | 11       |           | 0.500 x V <sub>DD</sub>         |   |   |   |   |

**Product Specification**

### Write to SENSEMODE register

| INSTRUCTION      | wr_sensem | ( 77 <sub>H</sub> ) |

|------------------|-----------|---------------------|

| Mode             | serial    |                     |

| Input parameters | 1 byte    |                     |

| Data delay       | NA        |                     |

| Returned bytes   | NA        |                     |

The SENSEMODE register is a 2-bit register, which sets the test mode. In normal operation, this register should be cleared.

| REGIS              | STER  |   | SENS                                 | EMOD | E |   |   |  |

|--------------------|-------|---|--------------------------------------|------|---|---|---|--|

| Size (active bits) |       |   | 2                                    |      |   |   |   |  |

| 7                  | 6     | 5 | 4                                    | 3    | 2 | 1 | 0 |  |

| -                  |       |   |                                      | -    | 1 | х | Х |  |

|                    | Reset |   | 00 <sub>H</sub> (default value)      |      |   |   |   |  |

|                    | 00    |   | Regular image capture mode (default) |      |   |   |   |  |

|                    | 01    |   | Checker board test                   |      |   |   |   |  |

|                    | 10    |   | Inverted checker board test          |      |   |   |   |  |

|                    | 11    |   | Black test                           |      |   |   |   |  |

If the SENSEMODE register value is non-zero, different types of test patterns are generated internally in the sensor when an image is captured. The Checkerboard test pattern has high grayscale values for pixels on all even columns on even rows, and odd columns of odd rows. Subsequently, pixels on even columns on odd rows, and odd columns on even rows has a low grayscale value, creating a checkerboard pattern all over the image area.

Similarly, the Inverted checker board test pattern has high grayscale values where the regular checkerboard test pattern has low grayscale values, and vice versa.

Finally, the Black test pattern mode makes all grayscale values high. (The normal procedure when looking at a captured image is to first invert the image, since this makes an image of an actual finger look like an inked fingerprint. Therefore an image with all grayscale values high is considered to be an all black image.)

Write to FIFO\_TH register

| INSTRUCTION      | wr_fifo_th | ( 7C <sub>H</sub> ) |

|------------------|------------|---------------------|

| Mode             | serial     |                     |

| Input parameters | 1 byte     |                     |

| Data delay       | NA         |                     |

| Returned bytes   | NA         |                     |

The FIFO\_TH register holds the threshold value for the FIFO. When the fill level for the FIFO is higher than or equal to this value, the DA bit in the SPI\_STAT register is set.

The internal sensor data FIFO is 16 bytes deep and the threshold level can be set between 1 and 16. If this register is set to  $00_{\rm H}$  the DA bit will be set to indicate when all 16 bytes are holding valid data. The relation between the register value and the threshold level is shown below.

| REGIS              | STER |   | FIFO_                           | TH       |        |   |   |  |  |

|--------------------|------|---|---------------------------------|----------|--------|---|---|--|--|

| Size (active bits) |      |   | 4                               |          |        |   |   |  |  |

| 7                  | 6    | 5 | 4                               | 3        | 2      | 1 | 0 |  |  |

| -                  | -    | - | -                               | х        | х      | х | х |  |  |

| Reset              |      |   | 08 <sub>H</sub> (default value) |          |        |   |   |  |  |

| (                  | 0000 |   | Threshold level 16              |          |        |   |   |  |  |

| (                  | 0001 |   | Threshold level 1               |          |        |   |   |  |  |

| (                  | 0010 |   | Threshold level 2               |          |        |   |   |  |  |

|                    | :    |   | :                               |          |        |   |   |  |  |

| •                  | 1111 |   | Thres                           | hold lev | /el 15 |   |   |  |  |

**Product Specification**

#### Write to XSENSE/YSENSE register

| INSTRUCTION      | wr_xsense | (7F <sub>H</sub> ) |

|------------------|-----------|--------------------|

| Mode             | serial    |                    |

| Input parameters | 1 byte    |                    |

| Data delay       | NA        |                    |

| Returned bytes   | NA        |                    |

| INSTRUCTION      | wr_ysense | ( 81 <sub>H</sub> ) |

|------------------|-----------|---------------------|

| Mode             | serial    |                     |

| Input parameters | 1 byte    |                     |

| Data delay       | NA        |                     |

| Returned bytes   | NA        |                     |

These registers are used to select which pixels are active during sensing.

The values of these registers can be changed using the <wr\_xsense> and <wr\_ysense> instructions. When any of these instructions are applied, the XSENSE and YSENSE register, respectively, are shifted 8 bits towards the MSB and the 8 LSB's are replaced with the new byte.

The sensor circuit contains 8 sample-and-hold modules. Column  $n\cdot 8+m$ , where  $n=\{0..18\}$  and  $m=\{0..7\}$ , are connected to the sample-and-hold module number m, through pass gates.

These pass gates are controlled by the XSENSE register. It is important not to let two pixels drive the same sample-and-hold module when loading a non-default value to these registers.

It is also important that only one row is active at a time. The YSENSE register controls which row is active. Please make sure that only one bit in the YSENSE register is set to '1' at any time. If more that one bit in the YSENSE register is set to '1', the returned picture will be invalid, and current-consumption will increase.

To activate a pixel (sensing), the associated bits in both the XSENSE and the YSENSE registers have to be set.

During the fingerprint sensing period, the 8 sampleand-hold modules sample data simultaneously. This data is then digitized before a new sample-and-hold operation is performed. Data is always returned starting with sample-and-hold number 0 and ending with sample-and-hold number 7.

This means that if XSENSE is set to start sensing column 3 to 10 (instead of 0 to 7 which is default) and the shift mode is set to shift 8 positions, the pixels will be read out in the following order (by column number): 8, 9, 10, 3, 4, 5, 6, 7, 16, 17, 18, 11, 12, 13, 14, 15 and so on. This is illustrated in the table below.

| REGISTER         | XSENSE                               |

|------------------|--------------------------------------|

| Size (bit/bytes) | 152 / 19                             |

| Reset            | 00 00FF <sub>H</sub> (default value) |

| REGISTER         | YSENSE                               |

|------------------|--------------------------------------|

| Size (bit/bytes) | 200 / 25                             |

| Reset            | 00 0001 <sub>H</sub> (default value) |

| XSENSE START VALUE | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

|--------------------|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| COLUMN NO          | 0 | 1 | 2 | З | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 |

| CONNECTED TO SH NO | 0 | 1 | 2 | З | 4 | 5 | 6 | 7 | 0 | 1 | 2  | 3  | 4  | 5  | 6  | 7  | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  |

| SAMPLE CYCLE NO    |   |   |   |   |   |   |   | 1 |   |   |    |    |    |    |    | 2  |    |    |    |    |    | 3  |    |    |

Illustration of readout sequence with a non-standard start value for XSENSE

Product Specification

### Write to XSHIFT register

| INSTRUCTION      | wr_xshift | ( 82 <sub>H</sub> ) |

|------------------|-----------|---------------------|

| Mode             | serial    |                     |

| Input parameters | 1 byte    |                     |

| Data delay       | NA        |                     |

| Returned bytes   | NA        |                     |

The XSHIFT register holds the number of shifts performed in the x direction. The number of sense operations performed in one row exceeds the value stored in this register by one.

| REGISTER           |   |   | XSHII               | FT                   |          |      |   |  |  |

|--------------------|---|---|---------------------|----------------------|----------|------|---|--|--|

| Size (active bits) |   | 8 | 8                   |                      |          |      |   |  |  |

| 7                  | 6 | 5 | 4                   | 3                    | 2        | 1    | 0 |  |  |

| x x x              |   |   | x x x x x           |                      |          |      |   |  |  |

| Reset              |   |   | 12 <sub>H</sub> (18 | 8 <sub>D</sub> ) (de | fault va | lue) |   |  |  |

### Write to XREADS register

| INSTRUCTION      | wr_xreads | ( 84 <sub>H</sub> ) |

|------------------|-----------|---------------------|

| Mode             | serial    |                     |

| Input parameters | 1 byte    |                     |

| Data delay       | NA        |                     |

| Returned bytes   | NA        |                     |

The XREADS register holds the number of times the same row is read before shifting to the next.

| REGISTER           |   |   | XREA               | XREADS  |        |   |   |  |  |  |  |

|--------------------|---|---|--------------------|---------|--------|---|---|--|--|--|--|

| Size (active bits) |   | 8 | 8                  |         |        |   |   |  |  |  |  |

| 7                  | 6 | 5 | 4                  | 4 3 2 1 |        |   |   |  |  |  |  |

| х                  | Х | Х | х                  | х       | Х      | х | х |  |  |  |  |

| Reset              |   |   | 01 <sub>H</sub> (d | default | value) |   |   |  |  |  |  |

### Write to YSHIFT register

|                  | <del>-</del> |                     |

|------------------|--------------|---------------------|

| INSTRUCTION      | wr_yshift    | ( 83 <sub>H</sub> ) |

| Mode             | serial       |                     |

| Input parameters | 1 byte       |                     |

| Data delay       | NA           |                     |

| Returned bytes   | NA           |                     |

The YSHIFT register holds the number of shifts performed in the y-direction. The number of lines sensed exceeds the value stored in this register by one.

| REGISTER |          | YSHIF | -т                                                  |   |   |   |   |

|----------|----------|-------|-----------------------------------------------------|---|---|---|---|

| Size (a  | ctive bi | ts)   | 8                                                   |   |   |   |   |

| 7        | 6        | 5     | 4                                                   | 3 | 2 | 1 | 0 |

| Х        | х        | х     | х                                                   | х | х | х | х |

| Reset    | •        | •     | C7 <sub>H</sub> (199 <sub>D</sub> ) (default value) |   |   | • |   |

**Product Specification**

### 4.4 Sample Implementation

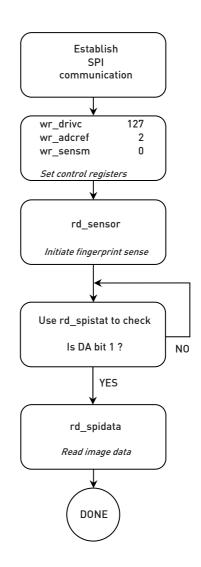

This section describes step-by-step how the SPI interface of FPC1011F can be used to perform a basic image readout process. We will outline in detail which commands the SPI host needs to transmit to receive the full sensor image.

- a) Establish a SPI connection between the SPI host and slave, using CPHA='0' and CPOL='0', at any clock speed <32MHz, and big endian bit order. Also, let the host enable the Chip Select signal in the SPI interface.

- b) Send the three instructions <wr\_drivc>,

<wr\_adcref>, and <wr\_sensemode> with

corresponding parameter values 127, 2, and

0 (recommended default values) to set the

sensor readout parameters.

| DRIVC | ADCREF | SENSEMODE |  |

|-------|--------|-----------|--|

| 127   | 2      | 0         |  |

If all other registers are left at their default values, the complete image area is read.

- c) Tell the sensor to capture an image by sending the instruction <rd\_sensor>, with a dummy parameter value.

- d) It will take some time before the first pixel data is available for reading in the FIFO. In SPI mode there are three ways to know when to start reading pixel data:

- Counting cycles, after 363 +/- 2 cycles the first pixel data will be available for reading. The FIFO gives a flexibility to safely start reading pixel data in cycle 365 489.

- IRQ\_DA signal (only FPC1011F2), when the FIFO threshold (FIFO\_TH register) is reached, the IRQ\_DA signal is set (high). The default value for the FIFO\_TH register is 8 (the FIFO is 16 bytes in total).

- Polling the SPI\_STATUS register, when the FIFO threshold (FIFO\_TH register) is reached, the DA bit (data available bit) is set (high).

Further details on how to operate the FIFO\_TH register is available in the section *Serial mode instruction*.

- e) Now, use the <rd\_spidata> instruction to read 30400 bytes of pixel data. The read pixel data is delivered row by row, with 1 byte per pixel, forming an image with dimensions 152 columns times 200 rows.

- f) Finally, let the host disable the Chip Select Signal, and (if applicable) shut down the connection to FPC1011F.

This specification is subject to change without prior notice

710-FPC1011F D Product-specification.doc

**Product Specification**

### 5 Parallel mode

In parallel mode all communication is done through the parallel asynchronous interface. The available commands are described in this section.

### 5.1 Instruction summary

| INSTRUCTION | INSTRUCTION CODE | DESCRIPTION                                                                                                   |

|-------------|------------------|---------------------------------------------------------------------------------------------------------------|

| rd_sensor   | 11 <sub>H</sub>  | Start sensing of finger. Data is placed in the FIFO.                                                          |

| rd_regs     | 50 <sub>H</sub>  | Read internal registers. All registers are read in one operation. The register content is placed in the FIFO. |

| wr_drivc    | 75 <sub>H</sub>  | Write DRIVC register. Set finger drive amplitude.                                                             |

| wr_adcref   | 76 <sub>H</sub>  | Write ADCREF register. Set ADC sensitivity.                                                                   |

| wr_sensem   | 77 <sub>H</sub>  | Write SENSEMODE register. Set self-test mode.                                                                 |

| wr_fifo_th  | 7C <sub>H</sub>  | Write FIFO_TH register. Set the FIFO fill threshold for activation of the data available signal, IRQ_DA.      |

| wr_xsense   | 7F <sub>H</sub>  | Shift data into the XSENSE register.                                                                          |

| wr_ysense   | 81 <sub>H</sub>  | Shift data into the YSENSE register.                                                                          |

| wr_xshift   | 82 <sub>H</sub>  | Write XSHIFT register. Set number of shifts to be performed in the x-direction.                               |

| wr_yshift   | 83 <sub>H</sub>  | Write YSHIFT register. Set number of shifts to be performed in the y-direction.                               |

| wr_xreads   | 84 <sub>H</sub>  | Write XREADS register. Set number of times the same row should be read before shifting the YSENSE register.   |

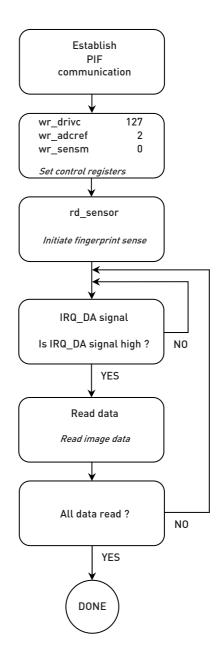

### 5.2 Sensor setup

When using the parallel interface, a register setup is always required.

The appropriate default parameters are indicated in the table below. For detailed instructions on how to perform the actual register setup, please refer to the *Parallel mode instructions* section in this document.

| DRIVC | ADCREF | SENSEMODE |

|-------|--------|-----------|

| 127   | 2      | 0         |

#### 5.3 Parallel mode instructions

Below all instructions are described in detail. Relevant timing diagrams are showed in the section *Timing properties*.

In addition to the long shift-registers controlling the pixels in the sensor array, the sensor component contains 13 control registers. All write instructions to registers operate in the same way. The FIFO-pointers are reset when any instruction is applied.

**Product Specification**

#### Read sensor instruction

| INSTRUCTION             | rd_sensor              | ( 11 <sub>H</sub> ) |

|-------------------------|------------------------|---------------------|

| Mode                    | parallel               |                     |

| Input parameters        | 1 dummy byte           |                     |

| Data delay <sup>1</sup> | (363±2)t <sub>CK</sub> |                     |

| Returned bytes          | 0                      |                     |

Note1: Data delay is the delay time from when the instruction is given, until data is available in the FIFO. The uncertainty, ±2 clock cycles, is due to the asynchronous nature of the interface (only valid for FPC1011F2).

This instruction is used to read the entire sensor or a part of it. Timing for reading in parallel mode is defined in the section *Timing properties*.

The read sensor instruction is only used to start the sense-sequence, and the instruction itself does not return any data. The first data from the sensor array will enter the FIFO after approximately 363 clock-cycles. After that, a new byte will enter the FIFO every 8th clock-cycle until the area defined by the XSENSE, YSENSE, XSHIFT and YSHIFT registers has been read.

When the FIFO is filled to a level equal to or greater than the value set by the FIFO\_TH register, the IRQ\_DA signal comes high to indicate that data is ready for fetching. Reading data from the FIFO in parallel mode is done using the PIF\_RD\_N signal. Details are available in the section *Parallel mode timing*.

If the FIFO is filled up with data, overflow is avoided by stalling sensing until data is read from the FIFO. During this stall-period all analog modules are active, and the ASIC will draw current as during a regular sense operation.

**Product Specification**

#### Read registers instruction

| INSTRUCTION      | rd_regs            | ( 50 <sub>H</sub> ) |

|------------------|--------------------|---------------------|

| Mode             | parallel           |                     |

| Input parameters | 1 dummy byte       |                     |

| Data delay       | 2±2t <sub>CK</sub> |                     |

| Returned bytes   | 0                  |                     |

The read register instruction fills the FIFO with the value of all the internal control registers. The order in which the registers are entered into the FIFO is given in the table below.

Reading data from the FIFO in parallel mode is done using the PIF\_RD\_N signal. Details are available in the section *Parallel mode timing*.

Contents of the registers are available no later than  $4 \cdot t_{\text{CK}}$  after the input parameter for this instruction is applied.

This instruction will completely fill the FIFO as shown in the table to the right. As a result of this, the IRQ\_DA signal will go high when data is available in the FIFO. Readout of the data in the FIFO can be stopped at any time.

| RETURN ORDER | REGISTER        |

|--------------|-----------------|

| 1            | STATUS          |

| 2            | NOT USED        |

| 3            | DRIVC           |

| 4            | ADCREF          |

| 5            | SENSEMODE       |

| 6            | FIFO_TH         |

| 7            | NOT USED        |

| 8            | XSHIFT          |

| 9            | YSHIFT          |

| 10           | XREADS          |

| 11           | NOT USED        |

| 12           | NOT USED        |

| 13           | NOT USED        |

| 14           | 00 <sub>H</sub> |

| 15           | 00 <sub>H</sub> |

| 16           | 00 <sub>H</sub> |

Return order for register values

The STATUS register is a read only register, which holds the status information for the FIFO.

| REGI     | STER      |                                         | STATUS              |                                 |   |     |     |  |

|----------|-----------|-----------------------------------------|---------------------|---------------------------------|---|-----|-----|--|

| Size (a  | active bi | ts)                                     | 2                   |                                 |   |     |     |  |

| 7        | 6         | 5                                       | 4                   | 3                               | 2 | 1   | 0   |  |

| -        | 1         | -                                       | 1                   | -                               | ı | STL | UFL |  |

|          | Reset 00  |                                         | 00 <sub>H</sub> (d  | 00 <sub>H</sub> (default value) |   |     |     |  |

|          | 01        |                                         | Underflow.          |                                 |   |     |     |  |

| <u> </u> |           | Bit is set if underflow occurs.         |                     |                                 |   |     |     |  |

| 10       |           | Stall. Bit is set if sensing is stalled |                     |                                 |   |     |     |  |

|          | 10        |                                         | due to a full FIFO. |                                 |   |     |     |  |

Remaining control registers (3-10) can be operated with both read and write instructions. Details on these registers are available together with the write instructions for each register.

All flag generation is based on comparing writepointer with read pointer synchronized to the system clock CK. This means that if a read instruction, resulting in an underflow, occurs one clock period before new data enters the FIFO, an undetected underflow will occur. To avoid this, the procedure for reading from the FIFO, which is outlined in FIFO\_TH register description, should be followed.

The entire register is reset when a <rd\_regs> instruction is executed.

Product Specification

### Write to DRIVC register

| INSTRUCTION      | wr_drivc | ( 75 <sub>H</sub> ) |

|------------------|----------|---------------------|

| Mode             | parallel |                     |

| Input parameters | 1 byte   |                     |

| Data delay       | NA       |                     |

| Returned bytes   | NA       |                     |

The DRIVC register sets the amplitude for the drive signal, active on the drive electrode (frame).

The recommended DRIVC setting is listed in the *Sensor setup* section. With default value set, the drive signal is disabled.

| REGIS            | STER                 |                | DRIVC                               |                                 |   |     |   |

|------------------|----------------------|----------------|-------------------------------------|---------------------------------|---|-----|---|

| Size (a          | ctive bi             | ts)            | 8                                   |                                 |   |     |   |

| 7                | 6                    | 5              | 4 3 2 1 0                           |                                 |   | 0   |   |

| х                | Х                    | х              | Х                                   | Х                               | х | х   | х |

| Res              | Reset                |                |                                     | 00 <sub>H</sub> (default value) |   |     |   |

| 0 <sub>D</sub>   |                      |                | Min voltage, Electrode drive off    |                                 |   | off |   |

| 127 <sub>D</sub> |                      |                | Approximately V <sub>DD</sub> /2    |                                 |   |     |   |

| 128              | B <sub>D</sub> - 255 | 5 <sub>D</sub> | Max voltage, approx V <sub>DD</sub> |                                 |   |     |   |

### Write to ADCREF register

| INSTRUCTION      | wr_adcref | ( 76 <sub>H</sub> ) |

|------------------|-----------|---------------------|

| Mode             | parallel  |                     |

| Input parameters | 1 byte    |                     |

| Data delay       | NA        |                     |

| Returned bytes   | NA        |                     |

The ADCREF register sets the dynamic range for the internal A/D converter. This register is set to '11' at reset.

The recommended ADCREF setting is listed in the *Sensor setup* section.

| REGIS   | STER     |     | ADCREF                          |                   |   |   |  |  |  |  |  |

|---------|----------|-----|---------------------------------|-------------------|---|---|--|--|--|--|--|

| Size (a | ctive bi | ts) | 2                               |                   |   |   |  |  |  |  |  |

| 7       | 6        | 5   | 4                               | 2                 | 1 | 0 |  |  |  |  |  |

| -       | -        | -   | x                               |                   |   |   |  |  |  |  |  |

|         | Reset    |     | 00 <sub>H</sub> (default value) |                   |   |   |  |  |  |  |  |

|         | 00       |     | 0.125 x V <sub>DD</sub>         |                   |   |   |  |  |  |  |  |

| (       | 01       |     | 0.250                           | x V <sub>DD</sub> |   |   |  |  |  |  |  |

|         | 10       |     | 0.375 x V <sub>DD</sub>         |                   |   |   |  |  |  |  |  |

|         | 11       |     | 0.500                           | x V <sub>DD</sub> |   |   |  |  |  |  |  |

**Product Specification**

#### Write to SENSEMODE register

| INSTRUCTION      | wr_sensem | ( 77 <sub>H</sub> ) |

|------------------|-----------|---------------------|

| Mode             | parallel  |                     |

| Input parameters | 1 byte    |                     |

| Data delay       | NA        |                     |

| Returned bytes   | NA        |                     |

The SENSEMODE register is a 2-bit register, which sets the test mode. In normal operation, this register should be cleared.

| REGIS   | STER     |     | SENS                                 | SENSEMODE |   |   |   |  |  |  |  |

|---------|----------|-----|--------------------------------------|-----------|---|---|---|--|--|--|--|

| Size (a | ctive bi | ts) | 2                                    |           |   |   |   |  |  |  |  |

| 7       | 6        | 5   | 4                                    | 3         | 2 | 1 | 0 |  |  |  |  |

| -       | -        | -   | -                                    | -         | 1 | х | х |  |  |  |  |

|         | Reset    |     | 00 <sub>H</sub> (default value)      |           |   |   |   |  |  |  |  |

|         | 00       |     | Regular image capture mode (default) |           |   |   |   |  |  |  |  |

|         | 01       |     | Checker board test                   |           |   |   |   |  |  |  |  |

|         | 10       |     | Inverted checker board test          |           |   |   |   |  |  |  |  |

|         | 11       |     | Black                                | test      |   |   |   |  |  |  |  |

If the SENSEMODE register value is non-zero, different types of test patterns are generated internally in the sensor when an image is captured. The Checkerboard test pattern has high grayscale values for pixels on all even columns on even rows, and odd columns of odd rows. Subsequently, pixels on even columns on odd rows, and odd columns on even rows has a low grayscale value, creating a checkerboard pattern all over the image area.

Similarly, the Inverted checker board test pattern has high grayscale values where the regular checkerboard test pattern has low grayscale values, and vice versa.

Finally, the Black test pattern mode makes all grayscale values high. (The normal procedure when looking at a captured image is to first invert the image, since this makes an image of an actual finger look like an inked fingerprint. Therefore an image with all grayscale values high is considered to be an all black image.)

Write to FIFO\_TH register

| INSTRUCTION      | wr_fifo_th | ( 7C <sub>H</sub> ) |

|------------------|------------|---------------------|

| Mode             | parallel   |                     |

| Input parameters | 1 byte     |                     |

| Data delay       | NA         |                     |

| Returned bytes   | NA         |                     |

The FIFO\_TH register holds the threshold value for the FIFO. When the fill level for the FIFO is higher than or equal to this value, the IRQ\_DA signal is comes high.

The internal sensor data FIFO is 16 bytes deep and the threshold level can be set between 1 and 16. If this register is set to  $00_{\rm H}$  the IRQ\_DA signal will come high to indicate when all 16 bytes are holding valid data. The relation between the register value and the threshold level is shown below.

| REGIS   | STER     |     | FIFO_                           | TH       |        |   |   |  |  |  |

|---------|----------|-----|---------------------------------|----------|--------|---|---|--|--|--|

| Size (a | ctive bi | ts) | 4                               |          |        |   |   |  |  |  |

| 7       | 6        | 5   | 4                               | 3        | 2      | 1 | 0 |  |  |  |

| -       | -        | -   | -                               | х        | х      | х | х |  |  |  |

| F       | Reset    |     | 08 <sub>H</sub> (default value) |          |        |   |   |  |  |  |

| (       | 0000     |     | Threshold level 16              |          |        |   |   |  |  |  |

| (       | 0001     |     | Threshold level 1               |          |        |   |   |  |  |  |

| (       | 0010     |     | Threshold level 2               |          |        |   |   |  |  |  |

|         | :        |     | :                               |          |        |   |   |  |  |  |

| •       | 1111     |     | Thres                           | hold lev | /el 15 |   |   |  |  |  |

**Product Specification**

### Write to XSENSE/YSENSE register

| INSTRUCTION      | wr_xsense | (7F <sub>H</sub> ) |

|------------------|-----------|--------------------|

| Mode             | parallel  |                    |

| Input parameters | 1 byte    |                    |

| Data delay       | NA        |                    |

| Returned bytes   | NA        |                    |

| INSTRUCTION      | wr_ysense | ( 81 <sub>H</sub> ) |

|------------------|-----------|---------------------|

| Mode             | parallel  |                     |

| Input parameters | 1 byte    |                     |

| Data delay       | NA        |                     |

| Returned bytes   | NA        |                     |

These registers are used to select which pixels are active during sensing.

The values of these registers can be changed using the <wr\_xsense> and <wr\_ysense> instructions. When any of these instructions are applied, the XSENSE and YSENSE register, respectively, are shifted 8 bits towards the MSB and the 8 LSB's are replaced with the new byte.

The sensor circuit contains 8 sample-and-hold modules. Column n·8+m, where n= $\{0..18\}$  and m= $\{0..7\}$ , are connected to the sample-and-hold module number m, through pass gates.

These pass gates are controlled by the XSENSE register. It is important not to let two pixels drive the same sample-and-hold module when loading a non-default value to these registers.

It is also important that only one row is active at a time. The YSENSE register controls which row is active. Please make sure that only one bit in the YSENSE register is set to '1' at any time. If more that one bit in the YSENSE register is set to '1', the returned picture will be invalid, and current-consumption will increase.

To activate a pixel (sensing), the associated bits in both the XSENSE and the YSENSE registers have to be set.

During the fingerprint sensing period, the 8 sampleand-hold modules sample data simultaneously. This data is then digitized before a new sample-and-hold operation is performed. Data is always returned starting with sample-and-hold number 0 and ending with sample-and-hold number 7.

This means that if XSENSE is set to start sensing column 3 to 10 (instead of 0 to 7 which is default) and the shift mode is set to shift 8 positions, the pixels will be read out in the following order (by column number): 8, 9, 10, 3, 4, 5, 6, 7, 16, 17, 18, 11, 12, 13, 14, 15 and so on. This is illustrated in the table below.

| REGISTER         | XSENSE                               |

|------------------|--------------------------------------|

| Size (bit/bytes) | 152 / 19                             |

| Reset            | 00 00FF <sub>H</sub> (default value) |

| REGISTER         | YSENSE                               |

|------------------|--------------------------------------|

| Size (bit/bytes) | 200 / 25                             |

| Reset            | 00 0001 <sub>H</sub> (default value) |

| XSENSE START VALUE | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

|--------------------|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| COLUMN NO          | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 |

| CONNECTED TO SH NO | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 0 | 1 | 2  | 3  | 4  | 5  | 6  | 7  | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  |

| SAMPLE CYCLE NO    |   |   |   |   |   |   |   | 1 |   |   |    |    |    |    |    | 2  |    |    |    |    |    | 3  |    |    |

Illustration of readout sequence with a non-standard start value for XSENSE

**Product Specification**

### Write to XSHIFT register

| wr_xshift | ( 82 <sub>H</sub> )      |

|-----------|--------------------------|

| parallel  |                          |

| 1 byte    |                          |

| NA        |                          |

| NA        |                          |

|           | parallel<br>1 byte<br>NA |

The XSHIFT register holds the number of shifts performed in the x direction. The number of sense operations performed in one row exceeds the value stored in this register by one.

| REGIS   | STER     |     | XSHIF               | -T                   |          |      |   |  |  |  |  |

|---------|----------|-----|---------------------|----------------------|----------|------|---|--|--|--|--|

| Size (a | ctive bi | ts) | 8                   |                      |          |      |   |  |  |  |  |

| 7       | 6        | 5   | 4                   | 4 3 2 1 0            |          |      |   |  |  |  |  |

| х       | х        | х   | х                   | х                    | х        | Х    | х |  |  |  |  |

| Reset   |          |     | 12 <sub>H</sub> (18 | 3 <sub>D</sub> ) (de | fault va | lue) |   |  |  |  |  |

### Write to XREADS register