# **FSC-BT981**

**5.2 Dual Mode Bluetooth Module Datasheet**

**Version 1.3**

### Copyright © 2013-2021 Feasycom Technology. All Rights Reserved.

Feasycom Technology reserves the right to make corrections, modifications, and other changes to its products, documentation and services at anytime. Customers should obtain the newest relevant information before placing orders. To minimize customer product risks, customers should provide adequate design and operating safeguards. Without written permission from Feasycom Technology, reproduction, transfer, distribution or storage of part or all of the contents in this document in any form is prohibited.

### **Revision History**

| Version | Data       | Notes                              |           |

|---------|------------|------------------------------------|-----------|

| 1.0     | 2021/05/08 | Initial Version                    | Fish      |

| 1.1     | 2021/06/08 | Update transmit power              | Fish      |

| 1.2     | 2021/08/25 | Update transmit power              | Devin Wan |

| 1.2.1   | 2021/10/19 | 1,change the Supply Voltage        | Devin Wan |

|         |            | 2, Storage: -20°C to +85°C         |           |

| 1.3     | 2021/10/27 | 1,change the Supply Voltage        | Devin Wan |

|         |            | 2,Bluetooth version changed to 5.2 |           |

|         |            |                                    |           |

|         |            |                                    |           |

|         |            | 7                                  |           |

|         |            | Chholosy Co.                       |           |

| Contact | : Us       |                                    |           |

### **Contact Us**

Shenzhen Feasycom Technology Co.,LTD

Email: sales@feasycom.com

Address: Rm 508, Building A, Fenghuang Zhigu, No.50, Tiezai Road, Xixiang, Baoan District, Shenzhen, 518102, China Tel: 86-755-27924639, 86-755-23062695

### **Contents**

| 1.  | INTRODUCTION                                        |              |

|-----|-----------------------------------------------------|--------------|

| 2.  | GENERAL SPECIFICATION                               |              |

|     | HARDWARE SPECIFICATION                              |              |

| 3.  |                                                     |              |

|     | 3.1 BLOCK DIAGRAM AND PIN DIAGRAM                   |              |

|     | 3.2 PIN Definition Descriptions                     |              |

| 4.  | PHYSICAL INTERFACE                                  | 7            |

|     | 4.1 Power Supply                                    | <del>.</del> |

|     | 4.2 RF Interface                                    |              |

|     | 4.3 SERIAL INTERFACES                               |              |

|     | 4.3.1 UART                                          |              |

|     | 4.3.2 I2C Interface                                 |              |

| _   |                                                     |              |

|     |                                                     |              |

|     | 5.1 ABSOLUTE MAXIMUM RATINGS                        |              |

|     | 5.2 RECOMMENDED OPERATING CONDITIONS                |              |

|     | 5.3 RF CHARACTERISTICS                              | 10           |

| 6.  |                                                     | 11           |

|     | RECOMMENDED TEMPERATURE REFLOW PROFILE              |              |

| 7.  | RECOMMENDED TEMPERATURE REFLOW PROFILE              |              |

| 8.  |                                                     |              |

|     | 8.1 Mechanical Details                              | 12           |

| _   | HARDWARE INTEGRATION SUGGESTIONS                    | 4.           |

| 9.  | 9.1 Soldering Recommendations                       | 13           |

| !   | 9.1 Soldering Recommendations                       | 13           |

| !   | 9.2 LAYOUT GUIDELINES(INTERNAL ANTENNA)             | 13           |

| !   | 9.3 LAYOUT GUIDELINES (EXTERNAL ANTENNA)            | 14           |

|     | 9.3.1 Antenna Connection and Grounding Plane Design |              |

| 10. | PRODUCT PACKAGING INFORMATION                       | 16           |

|     | 10.1 DEFAULT PACKING                                | 17           |

|     | 10.1 DEFAULI PACKING                                |              |

|     | 10.2 FACKING BOX (OPTIONAL)                         | 17           |

| 11  | APPLICATION SCHEMATIC                               | 15           |

#### 1. INTRODUCTION

### **Overview**

FSC-BT981 is a high-performance, highly integrated Bluetooth 5.2 BR/EDR/BLE, designed to operate on the 2400MHz to 2480Mhz ISM frequency band.

Abundant peripherals, power-on reset (POR) and I2C, arithmetic accelerators further reduce the cost and size of the entire system.

By default, Feasycom standard firmware is built-in, and customized firmware is also available.FSC-BT981 is a suitable product for designers who want to add wireless functions to their products.

### **Features**

- Bluetooth 5.2 Classical/BLE Proprietary double-mode **RF SOC**

- UART programming and data interface (baudrate can up to 921600bps)

- 12C interfaces

- **Digital Peripherals**

- Two-wire Master (I2C compatible), up to 400kbps

- LED drive capability

- AES256 HW encryption

- **Dual Core Digital Architecture**

- ARM Cortex-M0 Core for application

- CPU clock speed up to 192Mhz

- 2.4GHz Transceiver

- Single-end RFIO

- -95dBm in BLE mode

- Support 250kbps, 1/2/3 Mbps data rates

- Tx Power 0dBm

- Postage stamp sized form factor

- Working current is 5mA

- Support External Antenna

- **RoHS** compliant

### **Application**

- **Health Thermometer**

- **Heart Rate**

- **Blood Pressure**

- **Proximity**

### Module picture as below showing

Figure 1: FSC-BT981 Picture

# 2. General Specification

**Table 1:** General Specifications

| Categories         | Features             | Implementation                                       |

|--------------------|----------------------|------------------------------------------------------|

|                    | Bluetooth Version    | Bluetooth v5.2 Dual mode                             |

|                    | Frequency            | 2.400 - 2.480 GHz                                    |

| Wireless           | Transmit Power       | 5dBm (Maximum)                                       |

| Specification      | Receive Sensitivity  | -95 dBm@0.1%BER (BLE mode)                           |

|                    | Modulation           | GFSK, π/4 DQPSK, 8DPSK                               |

|                    | Raw Data Rates (Air) | 3 Mbps                                               |

|                    |                      | TX, RX,                                              |

|                    |                      | Supports Automatic Flow Control (CTS and RTS lines). |

|                    | UART Interface       | General Purpose I/O                                  |

| Host Interface and | OAKI IIILEITACE      | Default 115200,N,8,1                                 |

| Peripherals        |                      | Baudrate support from 1200 to 921600                 |

|                    | 2,                   | 5, 6, 7, 8 data bit character                        |

|                    | GPIO                 | 6 (maximum – configurable) lines                     |

|                    | I2C Interface        | 1 (configurable from GPIO total). Up to 400 kbps     |

| Profiles           | Classic Bluetooth    | Support                                              |

| Profiles           | Bluetooth Low Energy | Support                                              |

| Maximum            | Classic Bluetooth    | 1 Clients                                            |

| Connections        | Bluetooth Low Energy | 1 Clients                                            |

| FW upgrade         | 9                    | llink                                                |

| Supply Voltage     | Supply               | 3.3V 3.6V                                            |

| Power Consumption  |                      | Working current 5mA                                  |

| Physical           | Dimensions           | 12mm X 15mm X 2mm; Pad Pitch 1.1mm                   |

| Environmental      | Operating            | -20°C to +85°C                                       |

| Environmental      | Storage              | -20°C to +85°C                                       |

| Missellaneous      | Lead Free            | Lead-free and RoHS compliant                         |

| Miscellaneous      | Warranty             | One Year                                             |

| Humidity           |                      | 10% ~ 90% non-condensing                             |

| MSL grade:         |                      | MSL 3                                                |

| ESD grade:         |                      | Human Body Model: Class-2                            |

| LJD glaue.         |                      | Machine Model: Class-B                               |

|                    |                      |                                                      |

### 3. HARDWARE SPECIFICATION

### 3.1 Block Diagram and PIN Diagram

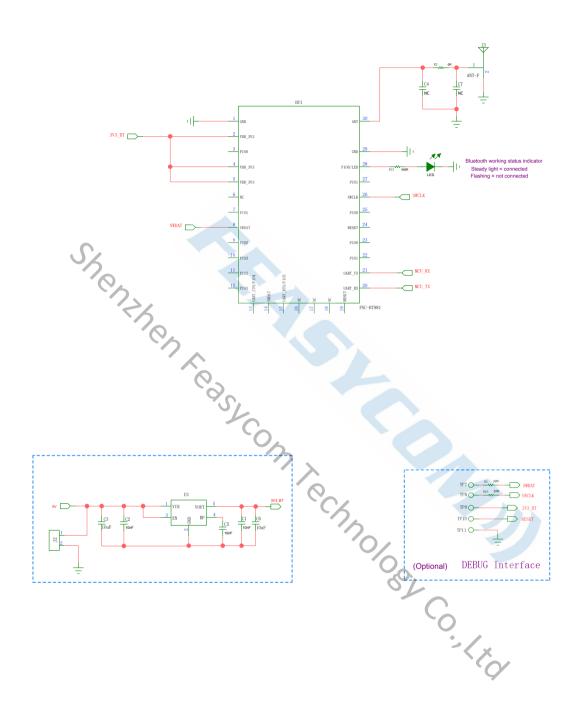

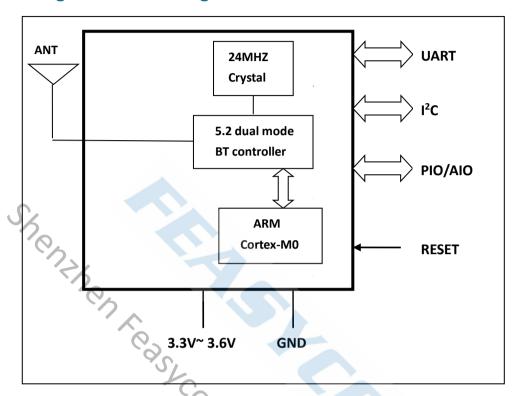

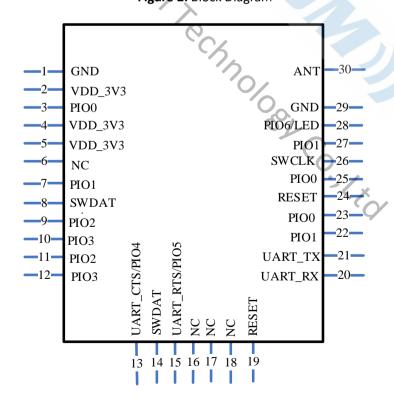

Figure 2: Block Diagram

Figure 3: FSC-BT981 PIN Diagram(Top View)

-6-

#### **PIN Definition Descriptions** 3.2

Table 2: Pin definition

| TUDIC Z. I | in definition     |      |                                                                         |

|------------|-------------------|------|-------------------------------------------------------------------------|

| Pin        | Pin Name          | Туре | Pin Descriptions                                                        |

| 1          | GND               | Vss  | Power Ground                                                            |

| 2          | VDD_3V3           | Vdd  | Power supply voltage 3.3V ~ 3.6V                                        |

| 3,23,25    | PIO0              | I/O  | Programmable input/output line                                          |

| 4          | VDD_3V3           | Vdd  | Power supply voltage 3.3V ~ 3.6V                                        |

| 5          | VDD_3V3           | Vdd  | Power supply voltage 3.3V ~ 3.6V                                        |

| 6          | NC                | NC   | NC                                                                      |

| 7,22,27    | PIO1              | 1/0  | Programmable input/output line                                          |

| 8,14       | SWDAT             | 1/0  | Update Interface(SWDAT)                                                 |

| 9,11       | PIO2              | 1/0  | Programmable input/output line                                          |

| 10,12      | PIO3              | 1/0  | Alternative Function: Programmable input/output line                    |

| 13         | UART_CTS/PIO4     | 1/0  | Programmable input/output line                                          |

|            | ٧,                |      | Or UART Clear To Send Active Low                                        |

| 15         | UART_RTS/PIO5     | I/O  | Programmable input/output line                                          |

|            | - 6               |      | Or UART Request To Send Active Low                                      |

| 16         | NC                | NC   | NC                                                                      |

| 17         | NC NC             | NC   | NC NC                                                                   |

| 18         | NC                | NC/  | NC NC                                                                   |

| 19,24      | RESET             | 110  | Reset if low. Input debounced so must be low for >5ms to cause a reset. |

| 20         | UART_RX           | i    | UART data input                                                         |

| 21         | UART_TX           | 0    | UART data output                                                        |

| 26         | SWCLK             | 1/0  | Update Interface(SWCLK)                                                 |

| 28         | PIO6/LED          | I/O  | Programmable input/output line                                          |

| 29         | GND               | Vss  | Power Ground                                                            |

| 30         | EXT_ANT           | 0    | Bluetooth 50ohm transmitter output/ receiver input                      |

|            | <del>-</del>      |      | 50,                                                                     |

|            |                   |      |                                                                         |

| 4 D        | IIVCICAL INTEREAC | _    |                                                                         |

| 4. PI      | HYSICAL INTERFAC  | E    |                                                                         |

|            |                   |      | Z Z                                                                     |

| 4.1        | Power Supply      |      | Bluetooth 50ohm transmitter output/ receiver input                      |

|            |                   |      |                                                                         |

#### 4. PHYSICAL INTERFACE

#### 4.1 **Power Supply**

The transient response of the regulator is important. If the power rails of the module are supplied from an external voltage source, the transient response of any regulator used should be 20µs or less. It is essential that the power rail recovers quickly.

#### 4.2 **RF Interface**

For this module, the default mode of the antenna is internal antenna.

The user can connect the 50 ohm antenna directly to the RF port.

- 2402–2480 MHz

- TX output power of +5dBm.

- Receiver to achieve maximum sensitivity -95dBm @ 0.1% BLE

### 4.3 Serial Interfaces

### 4.3.1 **UART**

FSC-BT981 provides one channels of Universal Asynchronous Receiver/Transmitters(UART)(Full-duplex asynchronous communications). The UART Controller performs a serial-to-parallel conversion on data received from the peripheral and a parallel-to-serial conversion on data transmitted from the CPU. Each UART Controller channel supports ten types of interrupts.

This is a standard UART interface for communicating with other serial devices. The UART interface provides a simple mechanism for communicating with other serial devices using the RS232 protocol.

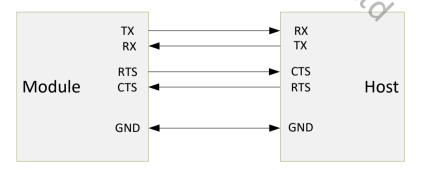

When the module is connected to another digital device, UART\_RX and UART\_TX transfer data between the two devices.

This module output is at 3.3V~ 3.6V CMOS logic levels (tracks VCC). Level conversion must be added to interface with an RS-232 level compliant interface.

Table 3: Possible UART Settings

| Parameter           | CO. |        | Possible Values                          |

|---------------------|-----|--------|------------------------------------------|

|                     | M   | inimum | 1200 baud (≤2%Error)                     |

| Baudrate            | Sta | andard | 115200bps(≤1%Error)                      |

|                     | М   | aximum | 921600bps(≤1%Error)                      |

| Flow control        |     | 70     | Supports Automatic Flow Control (CTS and |

|                     |     | 10/    | RTS lines)                               |

| Parity              | ·   |        | None, Odd or Even                        |

| Number of stop bits | ,   |        | 1 /1.5/2                                 |

| Bits per channel    | ,   |        | 5/6/7/8                                  |

When connecting the module to a host, please make sure to follow.

Figure 4: UART Connection

### 4.3.2 I2C Interface

I2C is a two-wire, bi-directional serial bus that provides a simple and efficient method of data exchange between devices. The I2C standard is a true multi-master bus including collision detection and arbitration that prevents data corruption if two or more masters attempt to control the bus simultaneously.

FSC-BT981 has I2C master which supports 100Kbps and 400Kbps.

Data is transferred between a Master and a Slave synchronously to SCL on the SDA line on a byte-by-byte basis. Each data byte is 8-bit long. There is one SCL clock pulse for each data bit with the MSB being transmitted first. An acknowledge bit follows each transferred byte. Each bit is sampled during the high period of SCL; therefore, the SDA line may be changed only during the low period of SCL and must be held stable during the high period of SCL. A transition on the SDA line while SCL is high is interpreted as a command (START or STOP). Please refer to the following figure for more details about I2C Bus Timing.

Figure 5: I2C Bus Timing

The device on-chip I2C logic provides the serial interface that meets the I2C bus standard mode specification. The I2C port handles byte transfers autonomously. The I2C H/W interfaces to the I2C bus via two pins: SDA and SCL. Pull up resistor is needed for I2C operation as these are open drain pins. When the I/O pins are used as I2C port, user must set the pins function to I2C in advance.

### 5. ELECTRICAL CHARACTERISTICS

### 5.1 Absolute Maximum Ratings

Absolute maximum ratings for supply voltage and voltages on digital and analogue pins of the module are listed below. Exceeding these values causes permanent damage.

The average PIO pin output current is defined as the average current value flowing through any one of the corresponding pins for a 100mS period. The total average PIO pin output current is defined as the average current value flowing through all of the corresponding pins for a 100mS period. The maximum output current is defined as the value of the peak current flowing through any one of the corresponding pins.

Table 4: Absolute Maximum Rating

| Parameter                              | Min  | Max  | Unit |

|----------------------------------------|------|------|------|

| VDD_3V3 DC Power Supply                | -0.3 | +3.6 | V    |

| T <sub>A</sub> - Operating Temperature | -20  | +85  | °C   |

| T <sub>ST</sub> - Storage Temperature  | -20  | +85  | °C   |

## **5.2** Recommended Operating Conditions

**Table 5:** Recommended Operating Conditions

| Parameter                              | Min         | Туре | Max         | Unit |

|----------------------------------------|-------------|------|-------------|------|

| VDD_3V3 DC Power Supply                | 3.3         | -    | 3.6         | V    |

| T <sub>A</sub> - Operating Temperature | -20         | 25   | +85         | °C   |

| T <sub>ST</sub> - Storage Temperature  | -20         | 25   | +85         | °C   |

| VIH High Level                         | VDD_3V3-0.3 |      | VDD_3V3+0.3 | V    |

| VIL Low Level                          | VSS         |      | VSS+0.3     | V    |

| VOH High Level                         | VDD_3V3-0.3 |      | VDD_3V3+0.3 | V    |

| VOL Low Level                          | VSS         |      | VSS+0.3     | V    |

### **5.3** RF characteristics

**Table 6:** Transmitter Characteristics

| Parameter                         | Min  | Туре | Max  | Unit |

|-----------------------------------|------|------|------|------|

| Operating Frequency               | 2400 |      | 2480 | MHz  |

| RF output power                   | -20  | 0    | 5    | dBm  |

| Out of band emission 2 MHz (GFSK) |      | -40  |      | dBm  |

| Out of band emission 3 MHz(GFSK)  |      | -48  |      | dBm  |

| 20dB bandwidth                    |      | 0.9  |      | MHz  |

**Table 7:** BLE Receiver Characteristics

| Parameter                                           | Min      | Туре | Max | Unit |

|-----------------------------------------------------|----------|------|-----|------|

| High Gain mode, Sensitivity @0.1%                   | <b>/</b> | -95  |     | dBm  |

| Standard Gain mode, Sensitivity @0.1%               | .60      | -92  |     | dBm  |

| Maximum Input Power                                 | 7        | 0    |     | dBm  |

| Co-channel C/I, Basic Rate, GFSK                    | 70.      | 7    |     | dB   |

| ACS C/I 1MHz, Basic Rate, GFSK                      |          | 5.5  | 7   | dB   |

| ACS C/I 2MHz, Basic Rate, GFSK                      | 601      | -36  | -34 | dB   |

| ACS C/I 3MHz, Basic Rate, GFSK                      |          | -43  |     | dB   |

| ACS C/I Image channel, Basic Rate, GFSK             |          | -34  |     | dB   |

| C/I 1 MHz adjacent to image channel, Basic Rate, GF | SK       | -28  |     | dB   |

Table 8: BT Receiver Characteristics

| Parameter                               | Min  | Туре | Max | Unit |

|-----------------------------------------|------|------|-----|------|

| Basic Rate, GFSK, BER<0.1%, Dirty Tx on | -92  |      |     | dBm  |

| EDR, π /4 DQPSK, BER<0.01%, Dirty Tx on | -93  |      |     | dBm  |

| EDR, 8PSK, BER<0.01%, Dirty Tx on       | -83  |      |     | dBm  |

| Maximum Input Power                     | 0    |      |     | dBm  |

| Co-channel C/I, EDR, π/4 DQPSK          | 10.5 |      |     | dB   |

| ACS C/I 1MHz, EDR, π/4 DQPSK            |      | -8   |     | dB   |

| ACS C/I 2MHz, EDR, π/4 DQPSK            |      |      |     | dB   |

| ACS C/I 3MHz, EDR, π/4 DQPSK            |      | -54  |     | dB   |

| ACS C/I Image channel, EDR, π/4 DQPSK               | -27 | dB |

|-----------------------------------------------------|-----|----|

| C/I 1 MHz adjacent to image channel, EDR, π/4 DQPSK | -43 | dB |

| Co-channel C/I, EDR, 8PSK                           | 20  | dB |

| ACS C/I 1MHz, EDR, 8PSK                             | 0   | dB |

| ACS C/I 2MHz, EDR, 8PSK                             | -20 | dB |

| ACS C/I 3MHz, EDR, 8PSK                             | -45 | dB |

| ACS C/I Image channel, EDR, 8PSK                    | -18 | dB |

| C/I 1 MHz adjacent to image channel, EDR, 8PSK      | -33 | dB |

|                                                     |     |    |

### 6. MSL & ESD

Table 9: MSL and ESD

| Parameter  | Value                     |

|------------|---------------------------|

| MSL grade: | MSL 3                     |

| ESD grado: | Human Body Model: Class-2 |

| ESD grade: | Machine Model: Class-B    |

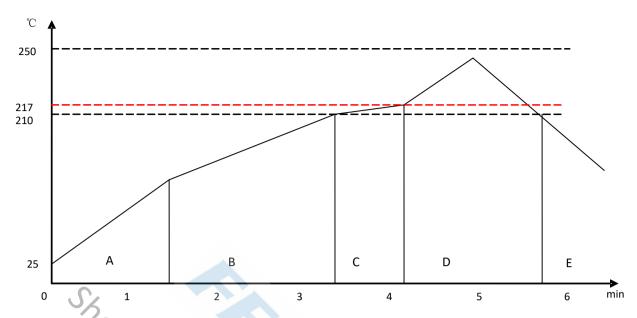

### 7. RECOMMENDED TEMPERATURE REFLOW PROFILE

Prior to any reflow, it is important to ensure the modules were packaged to prevent moisture absorption. New packages contain desiccate (to absorb moisture) and a humidity indicator card to display the level maintained during storage and shipment. If directed to bake units on the card, please check the below **next table** and follow instructions specified by IPC/JEDEC J-STD-033.

**Note:** The shipping tray cannot be heated above 65°C. If baking is required at the higher temperatures displayed in the below **next table**, the modules must be removed from the shipping tray.

Any modules not manufactured before exceeding their floor life should be re-packaged with fresh desiccate and a new humidity indicator card. Floor life for MSL (Moisture Sensitivity Level) 3 devices is 168 hours in ambient environment 30°C/60%RH.

Table 10: Recommended baking times and temperatures

| MSL | 125°C Baking Temp. |                  | 90°C/≤ 5%RH Baking Temp. |                  | 40°C/ ≤ 5%RH Baking Temp. |                  |

|-----|--------------------|------------------|--------------------------|------------------|---------------------------|------------------|

|     | Saturated @        | Floor Life Limit | Saturated @              | Floor Life Limit | Saturated @               | Floor Life Limit |

|     | 30°C/85%           | + 72 hours @     | 30°C/85%                 | + 72 hours @     | 30°C/85%                  | + 72 hours @     |

|     |                    | 30°C/60%         |                          | 30°C/60%         | 9                         | 30°C/60%         |

| 3   | 9 hours            | 7 hours          | 33 hours                 | 23 hours         | 13 days                   | 9 days           |

Feasycom surface mount modules are designed to be easily manufactured, including reflow soldering to a PCB. Ultimately it is the responsibility of the customer to choose the appropriate solder paste and to ensure oven temperatures during reflow meet the requirements of the solder paste. Feasycom surface mount modules conform to J-STD-020D1 standards for reflow temperatures.

The soldering profile depends on various parameters necessitating a set up for each application. The data here is given only for guidance on solder reflow.

Figure 6: Typical Lead-free Re-flow

**Pre-heat zone (A)** — This zone raises the temperature at a controlled rate, **typically 0.5** – 2 °C/s. The purpose of this zone is to preheat the PCB board and components to 120  $^{\circ}$  150  $^{\circ}$ C. This stage is required to distribute the heat uniformly to the PCB board and completely remove solvent to reduce the heat shock to components.

Equilibrium Zone 1 (B) — In this stage the flux becomes soft and uniformly encapsulates solder particles and spread over PCB board, preventing them from being re-oxidized. Also with elevation of temperature and liquefaction of flux, each activator and rosin get activated and start eliminating oxide film formed on the surface of each solder particle and PCB board. The temperature is recommended to be 150° to 210° for 60 to 120 second for this zone.

Equilibrium Zone 2 (C) (optional) — In order to resolve the upright component issue, it is recommended to keep the temperature in 210 – 217  $^{\circ}$  for about 20 to 30 second.

**Reflow Zone (D)** — The profile in the figure is designed for Sn/Ag3.0/Cu0.5. It can be a reference for other lead-free solder. The peak temperature should be high enough to achieve good wetting but not so high as to cause component discoloration or damage. Excessive soldering time can lead to intermetallic growth which can result in a brittle joint. The recommended peak temperature (Tp) is 230 ~ 250 °C. The soldering time should be 30 to 90 second when the temperature is above 217 °C.

Cooling Zone (E) — The cooling ate should be fast, to keep the solder grains small which will give a longer-lasting joint. 0,1% Typical cooling rate should be 4 °C.

#### **MECHANICAL DETAILS** 8.

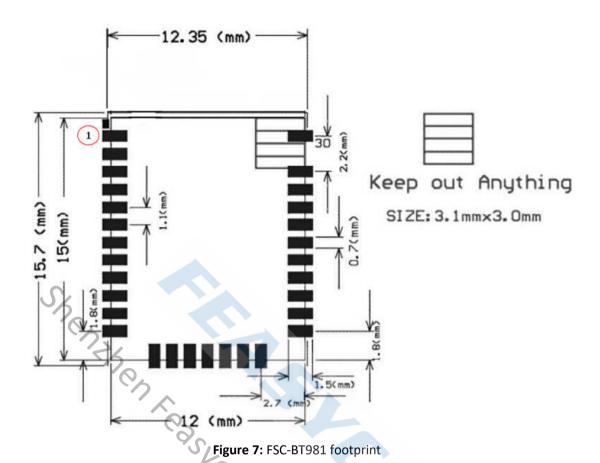

#### **Mechanical Details** 8.1

Dimension: 12mm(W) x 15mm(L) x 2.0mm(H) Tolerance: ±0.3mm

Pad size: 1.5mm x 0.7mm Tolerance: ±0.2mm

Pad pitch: 1.1mm Tolerance: ±0.1mm

### 9. HARDWARE INTEGRATION SUGGESTIONS

### 9.1 Soldering Recommendations

FSC-BT981 is compatible with industrial standard reflow profile for Pb-free solders. The reflow profile used is dependent on the thermal mass of the entire populated PCB, heat transfer efficiency of the oven and particular type of solder paste used. Consult the datasheet of particular solder paste for profile configurations.

Feasycom will give following recommendations for soldering the module to ensure reliable solder joint and operation of the module after soldering. Since the profile used is process and layout dependent, the optimum profile should be studied case by case. Thus following recommendation should be taken as a starting point guide.

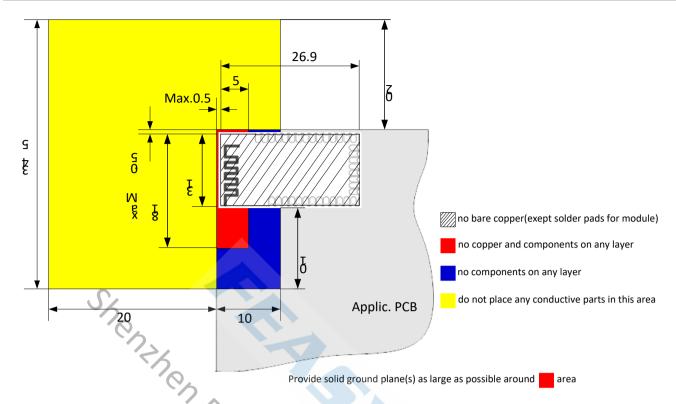

### 9.2 Layout Guidelines(Internal Antenna)

It is strongly recommended to use good layout practices to ensure proper operation of the module. Placing copper or any metal near antenna deteriorates its operation by having effect on the matching properties. Metal shield around the antenna will prevent the radiation and thus metal case should not be used with the module. Use grounding vias separated max 3 mm apart at the edge of grounding areas to prevent RF penetrating inside the PCB and causing an unintentional resonator. Use GND vias all around the PCB edges.

The mother board should have no bare conductors or vias in this restricted area, because it is not covered by stop mask print. Also no copper (planes, traces or vias) are allowed in this area, because of mismatching the on-board antenna.

Figure 8: FSC-BT981 Restricted Area(Unit: mm)

Following recommendations helps to avoid EMC problems arising in the design. Note that each design is unique and the following list do not consider all basic design rules such as avoiding capacitive coupling between signal lines. Following list is aimed to avoid EMC problems caused by RF part of the module. Use good consideration to avoid problems arising from digital signals in the design.

Ensure that signal lines have return paths as short as possible. For example if a signal goes to an inner layer through a via, always use ground vias around it. Locate them tightly and symmetrically around the signal vias. Routing of any sensitive signals should be done in the inner layers of the PCB. Sensitive traces should have a ground area above and under the line. If this is not possible, make sure that the return path is short by other means (for example using a ground line next to the signal line).

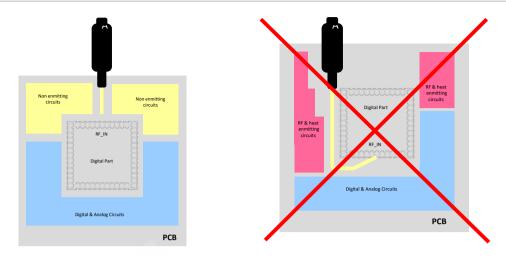

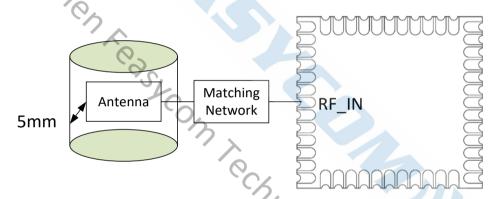

### 9.3 Layout Guidelines(External Antenna)

Placement and PCB layout are critical to optimize the performances of a module without on-board antenna designs. The trace from the antenna port of the module to an external antenna should be  $50\Omega$  and must be as short as possible to avoid any interference into the transceiver of the module. The location of the external antenna and RF-IN port of the module should be kept away from any noise sources and digital traces. A matching network might be needed in between the external antenna and RF-IN port to better match the impedance to minimize the return loss.

As indicated in below, RF critical circuits of the module should be clearly separated from any digital circuits on the system board. All RF circuits in the module are close to the antenna port. The module, then, should be placed in this way that module digital part towards your digital section of the system PCB.

Figure 9: Placement the Module on a System Board

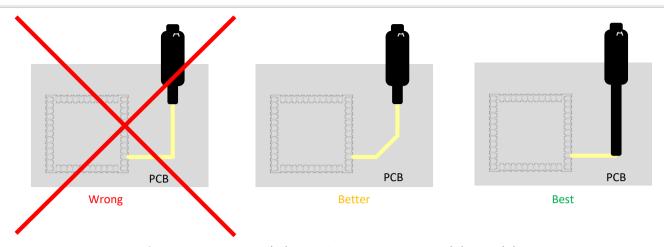

### 9.3.1 Antenna Connection and Grounding Plane Design

Figure 10: Leave 5mm Clearance Space from the Antenna

### General design recommendations are:

- The length of the trace or connection line should be kept as short as possible.

- Distance between connection and ground area on the top layer should at least be as large as the dielectric thickness.

- Routing the RF close to digital sections of the system board should be avoided.

- To reduce signal reflections, sharp angles in the routing of the micro strip line should be avoided. Chamfers or fillets are preferred for rectangular routing; 45-degree routing is preferred over Manhattan style 90-degree routing.

Figure 11: Recommended Trace Connects Antenna and the Module

- Routing of the RF-connection underneath the module should be avoided. The distance of the micro strip line to the ground plane on the bottom side of the receiver is very small and has huge tolerances. Therefore, the impedance of this part of the trace cannot be controlled.

- Use as many vias as possible to connect the ground planes.

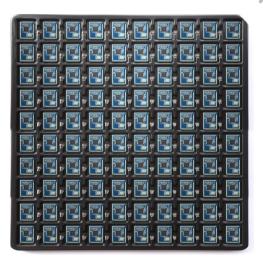

### 10. PRODUCT PACKAGING INFORMATION

### 10.1 Default Packing

- a, Tray vacuum

- b, Tray Dimension: 180mm \* 195mm

Figure 12: Tray vacuum

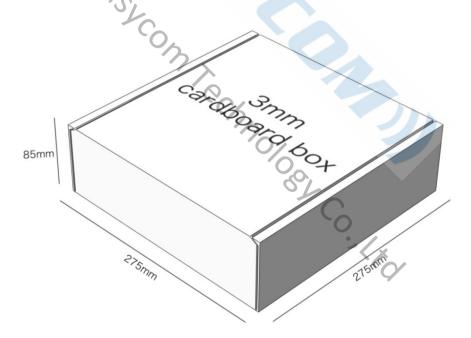

# 10.2 Packing box(Optional)

<sup>\*</sup> If require any other packing, must be confirmed with customer

Figure 13: Packing Box

<sup>\*</sup> Package: 1000PCS Per Carton (Min Carton Package)

### 11. APPLICATION SCHEMATIC