April 2012

# FSL106MR Green Mode Fairchild Power Switch (FPS™)

### **Features**

- Internal Avalanche-Rugged SenseFET: 650V

- Under 50mW Standby Power Consumption at 265V<sub>AC</sub>, No-Load Condition with Burst Mode

- Precision Fixed Operating Frequency with Frequency Modulation for Attenuating EMI

- Internal Startup Circuit

- Built-in Soft-Start: 15ms

- Pulse-by-Pulse Current Limiting

- Various Protections: Over-Voltage Protection (OVP), Overload Protection (OLP), Output-Short Protection (OSP), Abnormal Over-Current Protection (AOCP), Internal Thermal Shutdown Function with Hysteresis (TSD)

- Auto-Restart Mode

- Under-Voltage Lockout (UVLO)

- Low Operating Current: 1.8mA

- Adjustable Peak Current Limit

# **Applications**

- SMPS for VCR, STB, DVD, & DVCD Players

- SMPS for Home Appliance

- Adapter

#### Related Resources

- AN-4137 Design Guidelines for Offline Flyback

Converters Using FPS™

- AN-4141 Troubleshooting and Design Tips for Fairchild Power Switch (FPS™) Flyback Converter Applications

- AN-4147 Design Guidelines for RCD Snubber of Flyback Converters

- Fairchild Power Supply WebDesigner Flyback Design & Simulation - In Minutes at No Expense

## **Description**

The FSL106MR integrated Pulse Width Modulator (PWM) and SenseFET is specifically designed for high-performance offline Switch-Mode Power Supplies (SMPS) with minimal external components. FSL106MR includes integrated high-voltage power switching regulators that combine an avalanche-rugged SenseFET with a current-mode PWM control block.

The integrated PWM controller features include: Under-Voltage Lockout (UVLO) protection, Leading-Edge Blanking (LEB), a frequency generator for EMI attenuation, an optimized gate turn-on/turn-off driver, Thermal Shutdown (TSD) protection, and temperature-compensated precision current sources for loop compensation and fault protection circuitry. The FSL106MR offers good soft-start performance. When compared to a discrete MOSFET and controller or RCC switching converter solution, the FSL106MR reduces total component count, design size, and weight; while increasing efficiency, productivity, and system reliability. This device provides a basic platform that is well suited for the design of cost-effective flyback converters.

| Maximum Output Power <sup>(1)</sup> |                      |                        |                   |  |

|-------------------------------------|----------------------|------------------------|-------------------|--|

| 230V <sub>AC</sub>                  | ± 15% <sup>(2)</sup> | 85-26                  | 55V <sub>AC</sub> |  |

| Adapter <sup>(3)</sup>              | Open<br>Frame        | Adapter <sup>(3)</sup> | Open<br>Frame     |  |

| 7W                                  | 10W                  | 6W                     | 8W                |  |

#### Notes:

- The junction temperature can limit the maximum output power.

- 2. 230V<sub>AC</sub> or 100/115V<sub>AC</sub> with doubler.

- Typical continuous power in a non-ventilated enclosed adapter measured at 50°C ambient.

# **Ordering Information**

| Part<br>Number | Operating<br>Temperature Range | Top Mark | Package                           | Packing<br>Method |

|----------------|--------------------------------|----------|-----------------------------------|-------------------|

| FSL106MR       | -40 to +105°C                  | FSL106MR | 8-Lead, Dual Inline Package (DIP) | Rail              |

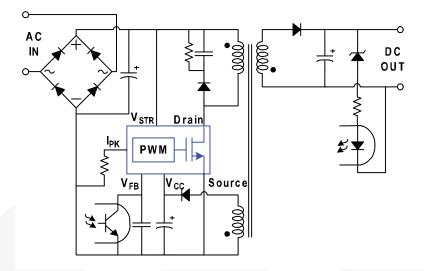

# **Typical Application Diagram**

Figure 1. Typical Application

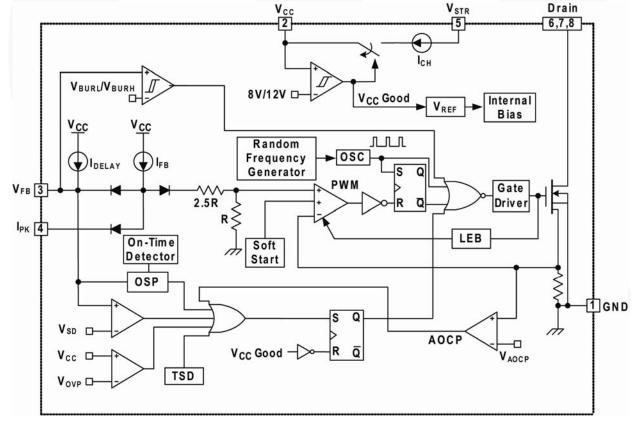

# **Internal Block Diagram**

Figure 2. Internal Block Diagram

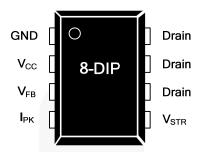

# **Pin Configuration**

Figure 3. Pin Configuration

# **Pin Definitions**

| Pin #   | Name            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|---------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1       | GND             | Ground. SenseFET source terminal on the primary side and internal control ground.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

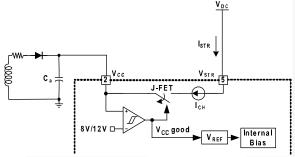

| 2       | V <sub>CC</sub> | Positive Supply Voltage Input. Although connected to an auxiliary transformer winding, current is supplied from pin 5 ( $V_{STR}$ ) via an internal switch during startup (see Figure 2). Once $V_{CC}$ reaches the UVLO upper threshold (12V), the internal startup switch opens and device power is supplied via the auxiliary transformer winding.                                                                                                                                  |  |  |

| 3       | $V_{FB}$        | <b>Feedback Voltage</b> . The non-inverting input to the PWM comparator, it has a 0.4mA current source connected internally, while a capacitor and opto-coupler are typically connected externally. There is a delay while charging the external capacitor C <sub>FB</sub> from 2.4V to 6V using an internal 5µA current source. This delay prevents false triggering under transient conditions, but still allows the protection mechanism to operate under true overload conditions. |  |  |

| 4       | I <sub>PK</sub> | <b>Peak Current Limit</b> . Adjusts the peak current limit of the SenseFET. The feedback 0.4mA current source is diverted to the parallel combination of an internal $6k\Omega$ resistor and any external resistor to GND on this pin to determine the peak current limit.                                                                                                                                                                                                             |  |  |

| 5       | $V_{STR}$       | <b>Startup</b> . Connected to the rectified AC line voltage source. At startup, the internal switch supplies internal bias and charges an external storage capacitor placed between the $V_{CC}$ pin and ground. Once $V_{CC}$ reaches 12V, the internal switch is opened.                                                                                                                                                                                                             |  |  |

| 6, 7, 8 | Drain           | <b>Drain</b> . Designed to connect directly to the primary lead of the transformer and capable of switching a maximum of 650V. Minimizing the length of the trace connecting these pins to the transformer decreases leakage inductance.                                                                                                                                                                                                                                               |  |  |

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.  $T_J = 25^{\circ}$ C unless otherwise specified.

| Symbol            | Parameter                                               | Min.     | Max.               | Unit |

|-------------------|---------------------------------------------------------|----------|--------------------|------|

| V <sub>STR</sub>  | V <sub>STR</sub> Pin Voltage                            | -0.3     | 650.0              | V    |

| V <sub>DS</sub>   | Drain Pin Voltage                                       | -0.3     | 650.0              | V    |

| V <sub>CC</sub>   | Supply Voltage                                          |          | 26                 | V    |

| $V_{FB}$          | Feedback Voltage Range                                  | -0.3     | 12.0               | V    |

| I <sub>D</sub>    | Continuous Drain Current                                |          | 0.5                | Α    |

| I <sub>DM</sub>   | Drain Current Pulsed <sup>(4)</sup>                     |          | 2                  | Α    |

| E <sub>AS</sub>   | Single Pulsed Avalanche Energy <sup>(5)</sup>           |          | 15                 | mJ   |

| P <sub>D</sub>    | Total Power Dissipation                                 |          | 1.5                | W    |

| T <sub>J</sub>    | Operating Junction Temperature                          | Internal | Internally Limited |      |

| T <sub>A</sub>    | Operating Ambient Temperature                           | -40      | +105               | °C   |

| T <sub>STG</sub>  | Storage Temperature                                     | -55      | +150               | °C   |

| ESD               | Human Body Model, JESD22-A114 <sup>(6)</sup>            | 3        |                    | KV   |

| E2D               | Charged Device Model, JESD22-C101 <sup>(6)</sup>        | 2        |                    | ΝV   |

| $\Theta_{JA}$     | Junction-to-Ambient Thermal Resistance <sup>(7,8)</sup> |          | 80                 | °C/W |

| $\Theta_{\sf JC}$ | Junction-to-Case Thermal Resistance <sup>(7,9)</sup>    |          | 19                 | °C/W |

| $\Theta_{JT}$     | Junction-to-Top Thermal Resistance <sup>(7,10)</sup>    |          | 33.7               | °C/W |

#### Notes:

- 4. Repetitive rating: pulse-width limited by maximum junction temperature.

- 5. L=30mH, starting T<sub>1</sub>=25°C.

- 6. Meets JEDEC standards JESD 22-A114 and JESD 22-C101.

- 7. All items are tested with the standards JESD 51-2 and JESD 51-10.

- 8.  $\Theta_{JA}$  free-standing, with no heat-sink, under natural convection.

- 9.  $\Theta_{JC}$  junction-to-lead thermal characteristics under  $\Theta_{JA}$  test condition.  $T_C$  is measured on the source #7 pin closed to plastic interface for  $\Theta_{JA}$  thermo-couple mounted on soldering.

- 10.  $\Theta_{JT}$  junction-to-top of thermal characteristic under  $\Theta_{JA}$  test condition.  $T_t$  is measured on top of package. Thermocouple is mounted in epoxy glue.

## **Electrical Characteristics**

$T_A$  = 25°C unless otherwise specified.

| Symbol                | Parameter                                                                | Conditions                                                                                                         | Min. | Тур. | Max. | Units |

|-----------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| SenseFE1              | Γ Section                                                                | •                                                                                                                  | ı    |      | 1    | ı     |

| BV <sub>DSS</sub>     | Drain-Source Breakdown Voltage                                           | $V_{CC} = 0V, I_D = 250\mu A$                                                                                      | 650  |      |      | V     |

| I <sub>DSS</sub>      | Zero Gate Voltage Drain Current                                          | V <sub>DS</sub> = 650V, V <sub>GS</sub> = 0V                                                                       |      |      | 250  | μA    |

| R <sub>DS(ON)</sub>   | Drain-Source On-State Resistance                                         | V <sub>GS</sub> = 10V, V <sub>GS</sub> = 0V, T <sub>C</sub> = 25°C                                                 |      | 11.5 | 18.0 | Ω     |

| C <sub>ISS</sub>      | Input Capacitance                                                        | V <sub>GS</sub> = 0V, V <sub>DS</sub> = 25V, f = 1MHz                                                              |      | 137  |      | pF    |

| Coss                  | Output Capacitance                                                       | V <sub>GS</sub> = 0V, V <sub>DS</sub> = 25V, f = 1MHz                                                              |      | 15.7 |      | pF    |

| C <sub>RSS</sub>      | Reverse Transfer Capacitance                                             | V <sub>GS</sub> = 0V, V <sub>DS</sub> = 25V, f = 1MHz                                                              |      | 2.9  |      | pF    |

| t <sub>d(ON)</sub>    | Turn-On Delay                                                            | $V_{DD} = 350V, I_D = 0.7A$                                                                                        |      | 8.6  |      | ns    |

| t <sub>r</sub>        | Rise Time                                                                | $V_{DD} = 350V, I_D = 0.7A$                                                                                        |      | 9.7  |      | ns    |

| t <sub>d(OFF)</sub>   | Turn-Off Delay                                                           | $V_{DD} = 350V, I_D = 0.7A$                                                                                        |      | 23.6 |      | ns    |

| t <sub>f</sub>        | Fall Time                                                                | $V_{DD} = 350V, I_D = 0.7A$                                                                                        |      | 49.2 |      | ns    |

| Control S             | ection                                                                   |                                                                                                                    |      |      |      |       |

| f <sub>OSC</sub>      | Switching Frequency                                                      | V <sub>DS</sub> = 650V, V <sub>GS</sub> = 0V                                                                       | 61   | 67   | 73   | KHz   |

| $\Delta f_{OSC}$      | Switching Frequency Variation                                            | V <sub>GS</sub> = 10V, V <sub>GS</sub> = 0V, T <sub>C</sub> = 125°C                                                |      | ±5   | ±10  | %     |

| f <sub>FM</sub>       | Frequency Modulation                                                     |                                                                                                                    |      | ±3   |      | KHz   |

| D <sub>MAX</sub>      | Maximum Duty Cycle                                                       | V <sub>FB</sub> = 4V                                                                                               | 71   | 77   | 83   | %     |

| D <sub>MIN</sub>      | Minimum Duty Cycle                                                       | V <sub>FB</sub> = 0V                                                                                               | 0    | 0    | 0    | %     |

| V <sub>START</sub>    |                                                                          |                                                                                                                    | 11   | 12   | 13   | V     |

| V <sub>STOP</sub>     | UVLO Threshold Voltage                                                   | After Turn-On                                                                                                      | 7    | 8    | 9    | V     |

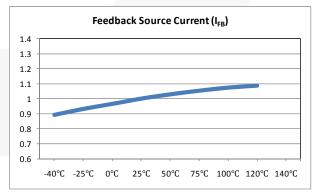

| I <sub>FB</sub>       | Feedback Source Current                                                  | V <sub>FB</sub> = 0V                                                                                               | 320  | 400  | 480  | μA    |

| t <sub>S/S</sub>      | Internal Soft-Start Time                                                 | V <sub>FB</sub> = 4V                                                                                               | 10   | 15   | 20   | ms    |

|                       | de Section                                                               |                                                                                                                    |      | l    | I.   |       |

| $V_{BURH}$            |                                                                          |                                                                                                                    | 0.56 | 0.70 | 0.84 | V     |

| V <sub>BURL</sub>     | Burst Mode Voltage                                                       | T <sub>J</sub> = 25°C                                                                                              | 0.37 | 0.50 | 0.63 | V     |

| V <sub>BUR(HYS)</sub> |                                                                          |                                                                                                                    |      | 200  |      | mV    |

| Protection            | n Section                                                                |                                                                                                                    |      | l    | l    |       |

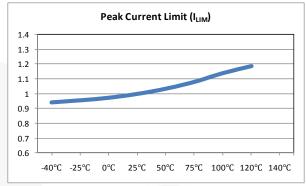

| I <sub>LIM</sub>      | Peak Current Limit                                                       | $T_J = 25^{\circ}C$ , di/dt = 200mA/µs                                                                             | 0.48 | 0.55 | 0.62 | Α     |

| t <sub>CLD</sub>      | Current Limit Delay Time <sup>(11)</sup>                                 |                                                                                                                    | 200  |      |      | ns    |

| V <sub>SD</sub>       | Shutdown Feedback Voltage                                                | V <sub>CC</sub> = 15V                                                                                              | 5.5  | 6.0  | 6.5  | V     |

| I <sub>DELAY</sub>    | Shutdown Delay Current                                                   | V <sub>FB</sub> = 5V                                                                                               | 3.5  | 5.0  | 6.5  | μA    |

| V <sub>OVP</sub>      | Over-Voltage Protection Threshold                                        | V <sub>FB</sub> = 2V                                                                                               | 22.5 | 24.0 | 25.5 | V     |

| t <sub>OSP</sub>      | Threshold Time                                                           |                                                                                                                    |      | 1.00 | 1.35 | μs    |

| V <sub>OSP</sub>      | Output-Short<br>Protection <sup>(11)</sup> Threshold Feedback<br>Voltage | OSP Triggered When t <sub>ON</sub> <t<sub>OSP,<br/>V<sub>FB</sub>&gt;V<sub>OSP</sub> and Lasts Longer than</t<sub> | 1.44 | 1.60 | 1    | V     |

| t <sub>OSP_FB</sub>   | Feedback Blanking<br>Time                                                | t <sub>OSP_FB</sub>                                                                                                | 2.0  | 2.5  |      | μs    |

| V <sub>AOCP</sub>     | AOCP Voltage (11)                                                        | T <sub>J</sub> = 25°C                                                                                              | 0.85 | 1.00 | 1.15 | V     |

| TSD                   | Thermal Shutdown Temperature                                             |                                                                                                                    | 125  | 137  | 150  | °C    |

| HYS <sub>TSD</sub>    | Shutdown <sup>(11)</sup> Hysteresis                                      |                                                                                                                    |      | 60   |      | °C    |

| t <sub>LEB</sub>      | Leading-Edge Blanking Time <sup>(11)</sup>                               |                                                                                                                    | 300  |      |      | ns    |

Continued on the following page...

# **Electrical Characteristics** (Continued)

$T_A$  = 25°C unless otherwise specified.

| Symbol           | Parameter                                                     | Conditions                                                        | Min. | Тур. | Max. | Units |

|------------------|---------------------------------------------------------------|-------------------------------------------------------------------|------|------|------|-------|

| Total Devi       | Total Device Section                                          |                                                                   |      |      |      |       |

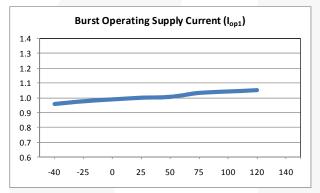

| I <sub>OP1</sub> | Operating Supply Current <sup>(11)</sup><br>(While Switching) | V <sub>CC</sub> = 14V, V <sub>FB</sub> > V <sub>BURH</sub>        |      | 2.5  | 3.5  | mA    |

| I <sub>OP2</sub> | Operating Supply Current (Control Part Only)                  | V <sub>CC</sub> = 14V, V <sub>FB</sub> < V <sub>BURL</sub>        |      | 1.8  | 2.5  | mA    |

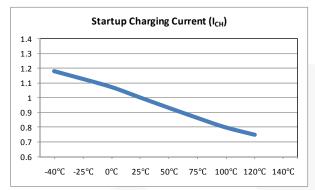

| I <sub>CH</sub>  | Startup Charging Current <sup>(11)</sup>                      | V <sub>CC</sub> = 0V                                              | 0.9  | 1.1  | 1.3  | mA    |

| V <sub>STR</sub> | Minimum V <sub>STR</sub> Supply Voltage                       | V <sub>CC</sub> = V <sub>FB</sub> = 0V, V <sub>STR</sub> Increase | 35   |      |      | V     |

### Note:

11. Though guaranteed by design, not 100% tested in production.

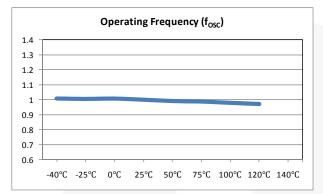

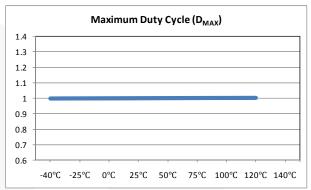

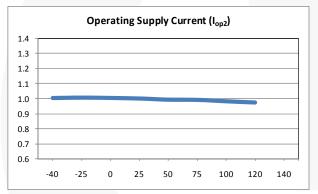

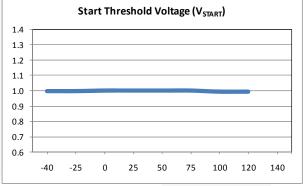

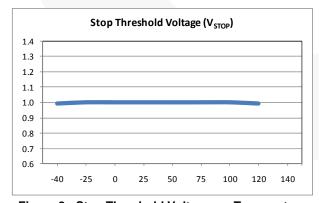

# **Typical Performance Characteristics**

These characteristic graphs are normalized at  $T_A$ =25.

Figure 4. Operating Frequency vs. Temperature

Figure 5. Maximum Duty Cycle vs. Temperature

Figure 6. Operating Supply Current vs. Temperature

Figure 7. Start Threshold Voltage vs. Temperature

Figure 8. Stop Threshold Voltage vs. Temperature

Figure 9. Feedback Source Current vs. Temperature

# **Typical Performance Characteristics** (Continued)

These characteristic graphs are normalized at  $T_A$ =25.

Figure 10. Startup Charging Current vs. Temperature

Figure 11. Peak Current Limit vs. Temperature

Figure 12. Burst Operating Supply Current vs. Temperature

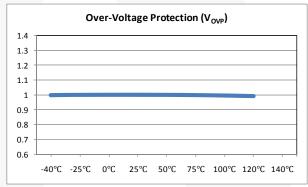

Figure 13. Over-Voltage Protection vs. Temperature

# **Functional Description**

### Startup

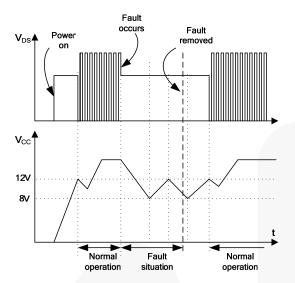

At startup, an internal high-voltage current source supplies the internal bias and charges the external capacitor ( $C_A$ ) connected with the  $V_{CC}$  pin, as illustrated in Figure 14. When  $V_{CC}$  reaches the start voltage of 12V, the FPS  $^{\text{TM}}$  begins switching and the internal high-voltage current source is disabled. The FPS continues normal switching operation and the power is provided from the auxiliary transformer winding unless  $V_{CC}$  goes below the stop voltage of 8V.

Figure 14. Startup Circuit

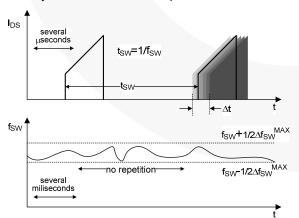

#### **Oscillator Block**

The oscillator frequency is set internally and the FPS has a random frequency fluctuation function.

Fluctuation of the switching frequency of a switched power supply can reduce EMI by spreading the energy over a wider frequency range than the bandwidth measured by the EMI test equipment. The amount of EMI reduction is directly related to the range of the frequency variation. The range of frequency variation is fixed internally; however, its selection is randomly chosen by the combination of external feedback voltage and internal free-running oscillator. This randomly chosen switching frequency effectively spreads the EMI noise nearby switching frequency and allows the use of a cost-effective inductor instead of an AC input line filter to satisfy the world-wide EMI requirements.

Figure 15. Frequency Fluctuation Waveform

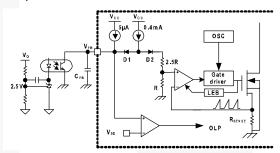

#### Feedback Control

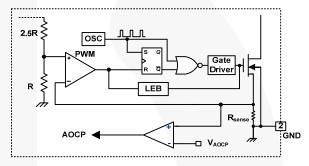

FSL106MR employs current-mode control, as shown in Figure 16. An opto-coupler (such as the FOD817A) and shunt regulator (such as the KA431) are typically used to implement the feedback network. Comparing the feedback voltage with the voltage across the  $R_{\rm SENSE}$  resistor makes it possible to control the switching duty cycle. When the shunt regulator reference pin voltage exceeds the internal reference voltage of 2.5V, the opto-coupler LED current increases, the feedback voltage  $V_{\rm FB}$  is pulled down, and the duty cycle is reduced. This typically occurs when the input voltage is increased or the output load is decreased.

Figure 16. Pulse-Width-Modulation Circuit

## Leading-Edge Blanking (LEB)

At the instant the internal SenseFET is turned on, the primary-side capacitance and secondary-side rectifier diode reverse recovery typically cause a high-current spike through the SenseFET. Excessive voltage across the  $R_{\mathsf{SENSE}}$  resistor leads to incorrect feedback operation in the current-mode PWM control. To counter this effect, the FPS employs a leading-edge blanking (LEB) circuit (see the Figure 16). This circuit inhibits the PWM comparator for a short time ( $t_{\mathsf{LEB}}$ ) after the SenseFET is turned on.

### **Protection Circuits**

The FPS has several protective functions, such as overload protection (OLP), over-voltage protection (OVP), output short-circuit protection (OSP), underlockout (UVLO), abnormal over-current protection (AOCP), and thermal shutdown (TSD). Because these various protection circuits are fully integrated inside the IC without external components, reliability is improved without increasing cost. Once a fault condition occurs, switching is terminated and the SenseFET remains off. This causes  $V_{\text{CC}}$  to fall. When V<sub>CC</sub> reaches the UVLO stop voltage V<sub>STOP</sub> (8V), the protection is reset and the internal high-voltage current source charges the V<sub>CC</sub> capacitor via the V<sub>STR</sub> pin. When  $V_{\text{CC}}$  reaches the UVLO start voltage  $V_{\text{START}}$  (12V), the FPS resumes normal operation. In this manner, the auto-restart can alternately enable and disable the switching of the power SenseFET until the fault condition is eliminated.

Figure 17. Auto-Restart Protection Waveforms

### **Overload Protection (OLP)**

Overload is defined as the load current exceeding a preset level due to an unexpected event. In this situation, the protection circuit should be activated to protect the SMPS. However, even when the SMPS is operating normally, the overload protection (OLP) circuit can be activated during the load transition or startup. To avoid this undesired operation, the OLP circuit is designed to be activated after a specified time to determine whether it is a transient situation or a true overload situation.

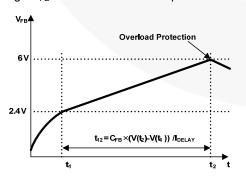

In conjunction with the  $I_{PK}$  current limit pin (if used), the current-mode feedback path limits the current in the SenseFET when the maximum PWM duty cycle is attained. If the output consumes more than this maximum power, the output voltage  $(V_O)$  decreases below its rating voltage. This reduces the current through the opto-coupler LED, which also reduces the opto-coupler transistor current, thus increasing the feedback voltage  $(V_{FB})$ . If  $V_{FB}$  exceeds 2.4V, the feedback input diode is blocked and the 5µA current source  $(I_{DELAY})$  starts to charge  $C_{FB}$  slowly. In this condition,  $V_{FB}$  increases until it reaches 6V, when the switching operation is terminated, as shown in Figure 18. The shutdown delay time is the time required to charge  $C_{FB}$  from 2.4V to 6V with 5µA current source.

Figure 18. Overload Protection (OLP)

### **Abnormal Over-Current Protection (AOCP)**

When the secondary rectifier diodes or the transformer pin are shorted, a steep current with extremely high di/dt can flow through the SenseFET during the LEB time. Even though the FPS has OLP (Overload Protection), it is not enough to protect the FPS in this abnormal case. since severe current stress is imposed on the SenseFET until OLP triggers. The FPS includes the internal AOCP (Abnormal Over-Current Protection) circuit shown in Figure 19. When the gate turn-on signal is applied to the power SenseFET, the AOCP block is enabled and monitors the current through the sensing resistor. The voltage across Figure 19 the resistor is compared with a preset AOCP level. If the sensing resistor voltage is greater than the AOCP level, the set signal is applied to the latch, resulting in the shutdown of the SMPS.

Figure 19. Abnormal Over-Current Protection

### Thermal Shutdown (TSD)

The SenseFET and the control IC are integrated, making it easier to detect the temperature of the SenseFET. When the temperature exceeds approximately 137°C, thermal shutdown is activated.

### **Over-Voltage Protection (OVP)**

In the event of a malfunction in the secondary-side feedback circuit or an open feedback loop caused by a soldering defect, the current through the opto-coupler transistor becomes almost zero. V<sub>FB</sub> climbs up in a similar manner to the overload situation, forcing the preset maximum current to be supplied to the SMPS until the overload protection is activated. Because excess energy is provided to the output, the output voltage may exceed the rated voltage before the overload protection is activated, resulting in the breakdown of the devices in the secondary side. To prevent this situation, an over-voltage protection (OVP) circuit is employed. In general, V<sub>CC</sub> is proportional to the output voltage and the FPS uses V<sub>CC</sub> instead of directly monitoring the output voltage. If V<sub>CC</sub> exceeds 24V, the OVP circuit is activated, resulting in termination of the switching operation. To avoid undesired activation of OVP during normal operation, V<sub>CC</sub> should be properly designed to be below 24V.

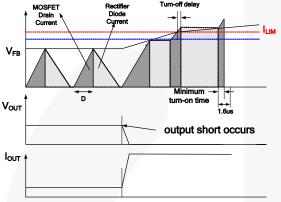

### **Output-Short Protection (OSP)**

If the output is shorted, steep current with extremely high di/dt can flow through the SenseFET during the LEB time. Such a steep current brings high-voltage stress on the drain of SenseFET when turned off. To protect the device from such an abnormal condition, OSP is included. It is comprised of detecting  $V_{FB}$  and SenseFET turn-on time. When the  $V_{FB}$  is higher than 1.6V and the SenseFET turn-on time is lower than 1.0µs, the FPS recognizes this condition as an abnormal error and shuts down PWM switching until  $V_{CC}$  reaches  $V_{START}$  again. An abnormal condition output is shown in Figure 20.

Figure 20. Output Short Waveforms (OSP)

### Soft-Start

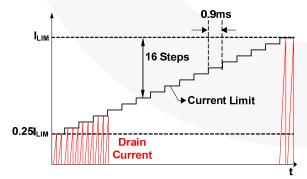

The FPS has an internal soft-start circuit that slowly increases the feedback voltage, together with the SenseFET current, after it starts. The typical soft-start time is 15ms, as shown in Figure 21, where progressive increments of the SenseFET current are allowed during the startup phase. The pulse width to the power switching device is progressively increased to establish the correct working conditions for transformers, inductors, and capacitors. The voltage on the output capacitors is progressively increased with the intention of smoothly establishing the required output voltage. It also helps to prevent transformer saturation and reduce the stress on the secondary diode.

Figure 21. Internal Soft-Start

### **Burst Operation**

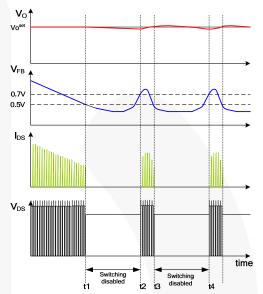

To minimize power dissipation in standby mode, the FPS  $^{\text{TM}}$  enters burst mode. As the load decreases, the

feedback voltage decreases. As shown in Figure 22, the device automatically enters burst mode when the feedback voltage drops below  $V_{\text{BURH}}$ . Switching continues until the feedback voltage drops below  $V_{\text{BURL}}$ . At this point, switching stops and the output voltages start to drop at a rate dependent on the standby current load. This causes the feedback voltage to rise. Once it passes  $V_{\text{BURH}}$ , switching resumes. The feedback voltage then falls and the process repeats. Burst mode alternately enables and disables switching of the SenseFET and reduces switching loss in standby mode.

Figure 22. Burst-Mode Operation

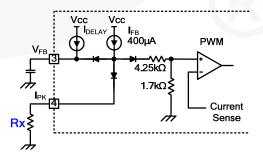

### **Adjusting Peak Current Limit**

As shown in Figure 23, a combined  $6k\Omega$  internal resistance is connected to the non-inverting lead on the PWM comparator. An external resistance of Rx on the current limit pin forms a parallel resistance with the  $6k\Omega$  when the internal diodes are biased by the main current source of  $400\mu\text{A}$ . For example, FSL106MR has a typical SenseFET peak current limit ( $I_{\text{LIM}}$ ) of 0.55A.  $I_{\text{LIM}}$  can be adjusted to 0.4A by inserting Rx between the  $I_{\text{PK}}$  pin and the ground. The value of the Rx can be estimated by the following equations:

$$0.55A0.4A=6k\Omega Xk\Omega$$

(1)

$$X = Rx \mid\mid 6k\Omega \tag{2}$$

where X represents the resistance of the parallel network.

Figure 23. Peak Current Limit Adjustment

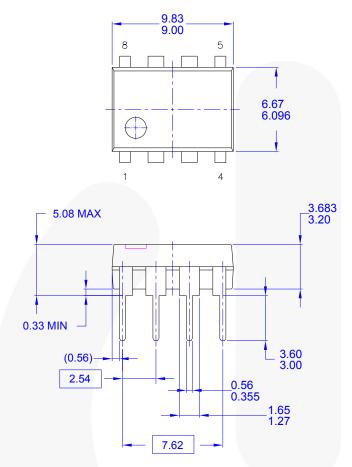

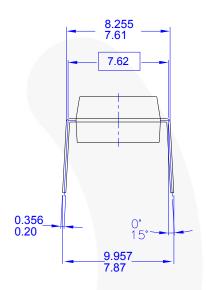

# **Physical Dimensions**

**NOTES: UNLESS OTHERWISE SPECIFIED**

- A) THIS PACKAGE CONFORMS TO JEDEC MS-001 VARIATION BA

- B) ALL DIMENSIONS ARE IN MILLIMETERS.

- C) DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH, AND TIE BAR EXTRUSIONS.

- D) DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994

- E) DRAWING FILENAME AND REVSION: MKT-N08FREV2.

Figure 24. 8-Lead, Dual In-Line Package(DIP)

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: <a href="http://www.fairchildsemi.com/packaging/">http://www.fairchildsemi.com/packaging/</a>.

#### TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

FRFET® AccuPower™ AX-CAPTM\* GreenBridge™ BitSiC™ Green FPS™ Build it Now™ CorePLUS™ Gmax™ CorePOWER™

GTO™ CROSSVOLT™ IntelliMAX™ CTL™ Current Transfer Logic™

DEUXPEED® Dual Cool™ EcoSPARK® EfficientMax™

ESBC<sup>TI</sup> 18 Fairchild

Fairchild Semiconductor® FACT Quiet Series™ FACT FAST® FastvCore™ FETBench™ FlashWriter®\*

Global Power Resource<sup>SM</sup>

Green FPS™ e-Series™

ISOPLANAR™

Making Small Speakers Sound Louder

and Better MegaBuck™ MICROCOUPLER™ MicroFET™ MicroPak™ MicroPak2™ Miller Drive™ MotionMax™

Motion-SPM™ mWSaver™ OptoHiT<sup>™</sup> OPTOLOGIC® **OPTOPLANAR®**  PowerTrench® PowerXS<sup>™</sup>

Programmable Active Droop™

OFET' QS™ Quiet Series™ RapidConfigure™

Saving our world, 1mW/W/kW at a time™

SignalWise™ SmartMax™ SMART START™

Solutions for Your Success™

SPM® STEALTH™ SuperFET<sup>®</sup> SuperSOT™-3 SuperSOT™-6 SuperSOT™-8 SupreMOS® SyncFET™ Sync-Lock™ SYSTEM GENERAL®

The Power Franchise®

wer franchise

TinyBoost™ TinyBuck™ TinyCalc™ TinyLogic<sup>6</sup> TINYOPTO™ TinyPower™ TinyPWM™ TinyWire™ Tran SiC™ TriFault Detect™ TRUECURRENT®\* μSerDes™

UHC Ultra FRFET™ UniFET™ **VCX™** VisualMax™ VoltagePlus™

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com,

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

| Deliminon of Terms       |                       |                                                                                                                                                                                                     |

|--------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Datasheet Identification | Product Status        | Definition                                                                                                                                                                                          |

| Advance Information      | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |

| Preliminary              | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |

| Obsolete                 | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor. The datasheet is for reference information only.                                                    |

Rev. 161

<sup>\*</sup> Trademarks of System General Corporation, used under license by Fairchild Semiconductor.