# GC2011A

## **3.3V DIGITAL FILTER CHIP**

## DATASHEET

March 21, 2000

Information provided by Graychip is believed to be accurate and reliable. No responsibility is assumed by Graychip for its use, nor for any infringement of patents or other rights of third parties which may arise from its use. No license is granted by implication or otherwise under any patent rights of Graychip.

## **REVISION HISTORY**

| Revision | Date          | Description                                                                                                                                                                                                                                                                                                         |

|----------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.0      | 3 Feb 1999    | Original                                                                                                                                                                                                                                                                                                            |

| 1.0      | 22 Sept, 1999 | Preliminary markings removed<br>Section 7: Electrical and timing tables changed to reflect production test<br>Pg 19, Sec 3.7, Table 8, changed Hilbert Transform output register to 2000<br>Pg 25: added ball grid array package<br>Pg 33: changed the gain equation to reference the MSBs of the input and output. |

| 1.1      | 21 Mar 2000   | Page 25, Rotated marking text on PBGA package<br>Page 35, Snap rate of 2 is invalid<br>Page 39, Changed test load to +/- 2mA from 4mA<br>Page 40, Changed Output delay threshold (Note 4) to 1.3v.<br>Page 40, Changed Data to output MIN delay to 1ns to match test.                                               |

| 1.0                                                                                                                                                                                 | KEY FEATURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

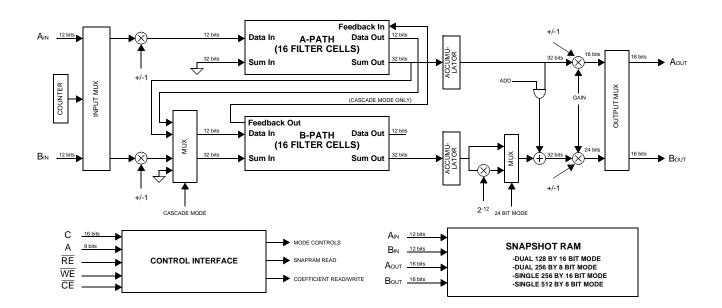

| 1.1                                                                                                                                                                                 | BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                                                                                                                                                                                    |

| 1.2                                                                                                                                                                                 | GC2011A TO GC2011 COMPARISON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                      |

| 1.3                                                                                                                                                                                 | DATASHEET OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                      |

|                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                                                                                                                                                                                                    |

| 2.0                                                                                                                                                                                 | FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                      |

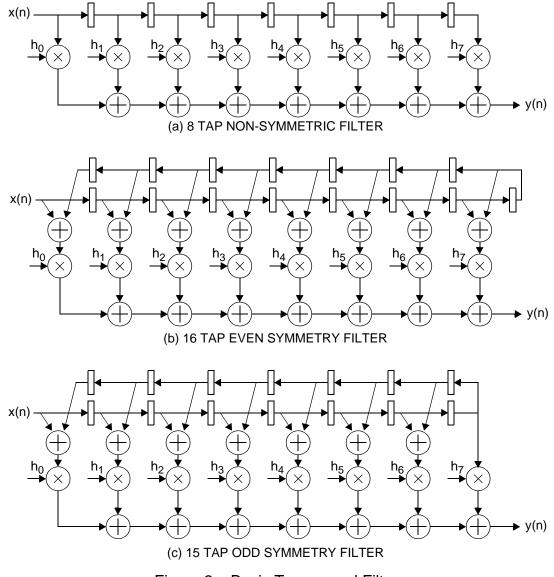

| 2.1                                                                                                                                                                                 | TRANSVERSAL FILTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                      |

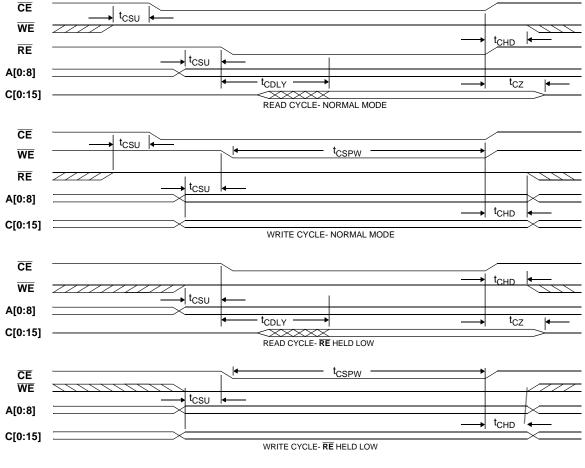

| 2.2                                                                                                                                                                                 | CONTROL INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                      |

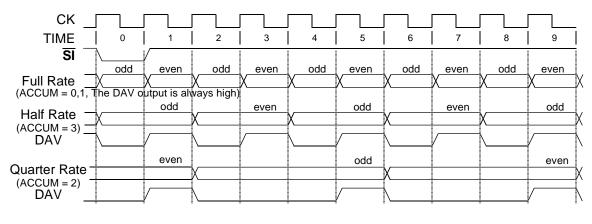

| 2.3                                                                                                                                                                                 | COUNTER AND SYNCHRONIZATION CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7                                                                                                                                                                                                                    |

| 2.4                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8                                                                                                                                                                                                                    |

| 2.5                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8                                                                                                                                                                                                                    |

| 2.6                                                                                                                                                                                 | A/B FILTER PATHS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8                                                                                                                                                                                                                    |

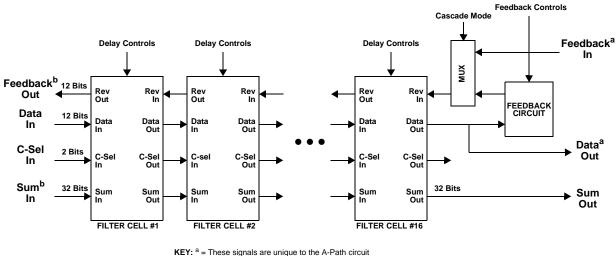

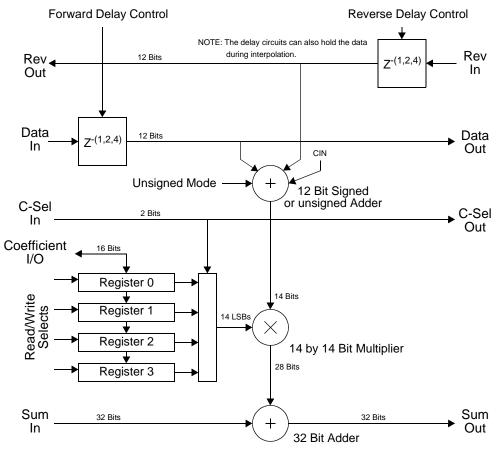

| 2.7                                                                                                                                                                                 | FILTER CELL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9                                                                                                                                                                                                                    |

| 2.8                                                                                                                                                                                 | ACCUMULATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                      |

| 2.9                                                                                                                                                                                 | 24 BIT MUX CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                      |

| 2.10                                                                                                                                                                                | SUMMER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                      |

| 2.11                                                                                                                                                                                | OUTPUT NEGATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                      |

| 2.12                                                                                                                                                                                | GAIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                      |

| 2.13                                                                                                                                                                                | OUTPUT MUX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                      |

| 2.10                                                                                                                                                                                | SNAPSHOT MEMORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                      |

|                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                      |

| 3.0                                                                                                                                                                                 | FILTERING MODES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                      |

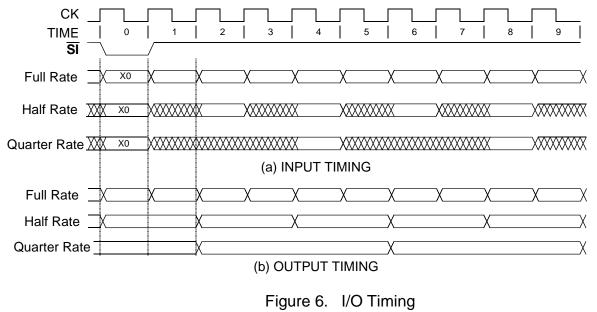

| 3.1                                                                                                                                                                                 | FULL RATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .14                                                                                                                                                                                                                  |

| 3.2                                                                                                                                                                                 | HALF RATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .15                                                                                                                                                                                                                  |

| 3.3                                                                                                                                                                                 | QUARTER RATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .16                                                                                                                                                                                                                  |

| 3.4                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .16                                                                                                                                                                                                                  |

| 3.5                                                                                                                                                                                 | DECIMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | .17                                                                                                                                                                                                                  |

| 3.6                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                      |

| 3.7                                                                                                                                                                                 | HILBERT TRANSFORM FILTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .19                                                                                                                                                                                                                  |

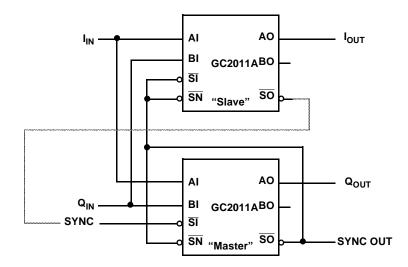

| 3.8                                                                                                                                                                                 | REAL TO COMPLEX QUADRATURE DOWN CONVERT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | .20                                                                                                                                                                                                                  |

| 3.9                                                                                                                                                                                 | COMPLEX TO REAL QUADRATURE UPCONVERT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                      |

| 3.10                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                      |

| 3.10                                                                                                                                                                                | DIAGNOSTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 22                                                                                                                                                                                                                 |

|                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                      |

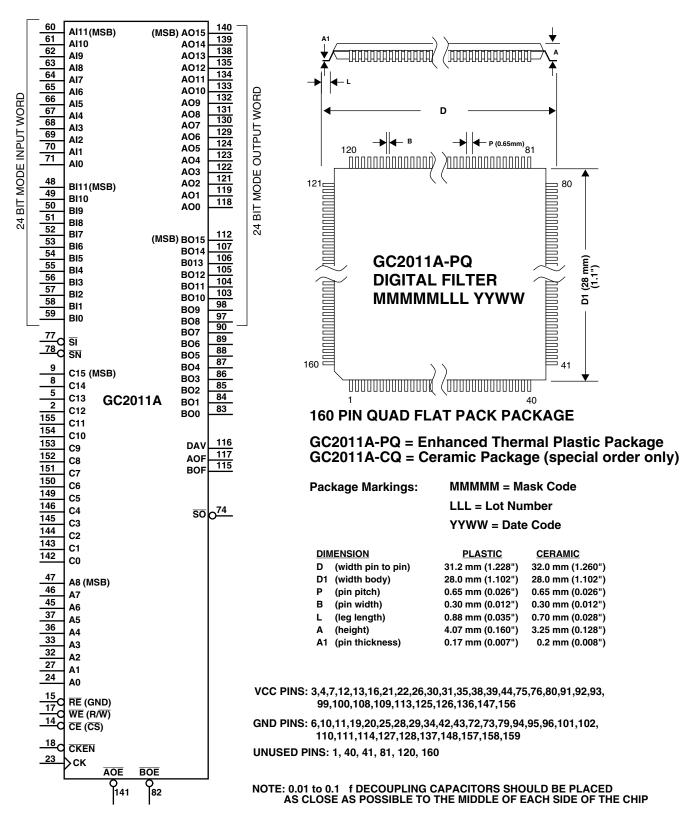

| 4.0                                                                                                                                                                                 | PACKAGING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23                                                                                                                                                                                                                   |

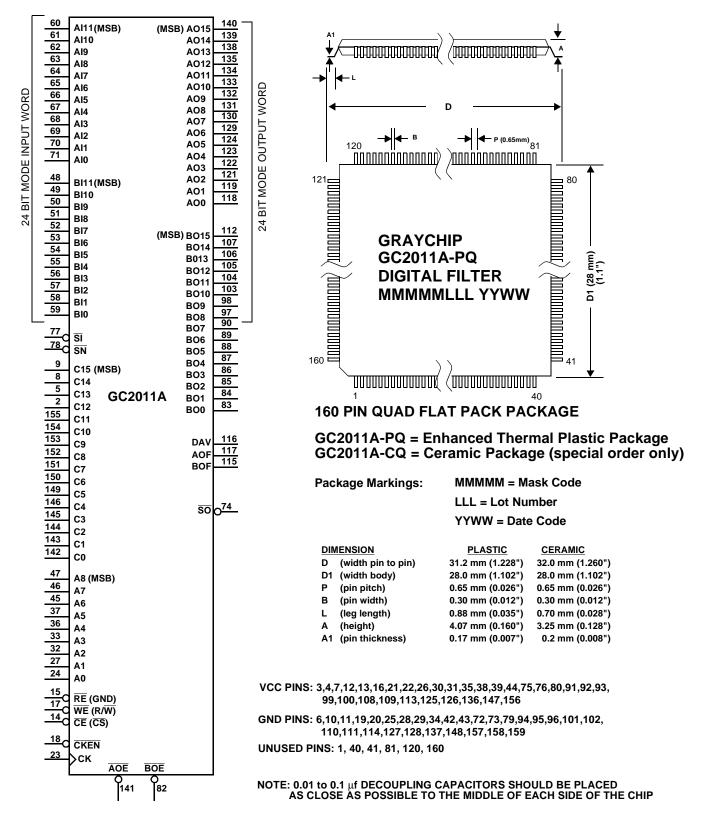

| <b>4.0</b><br>4.1                                                                                                                                                                   | PACKAGING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>23</b><br>.23                                                                                                                                                                                                     |

| 4.0                                                                                                                                                                                 | PACKAGING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>23</b><br>.23                                                                                                                                                                                                     |

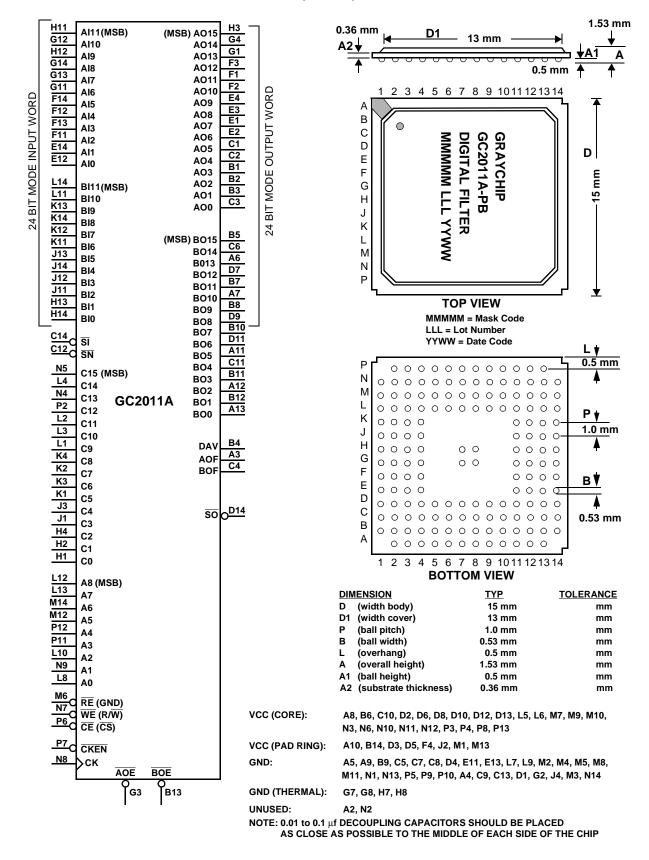

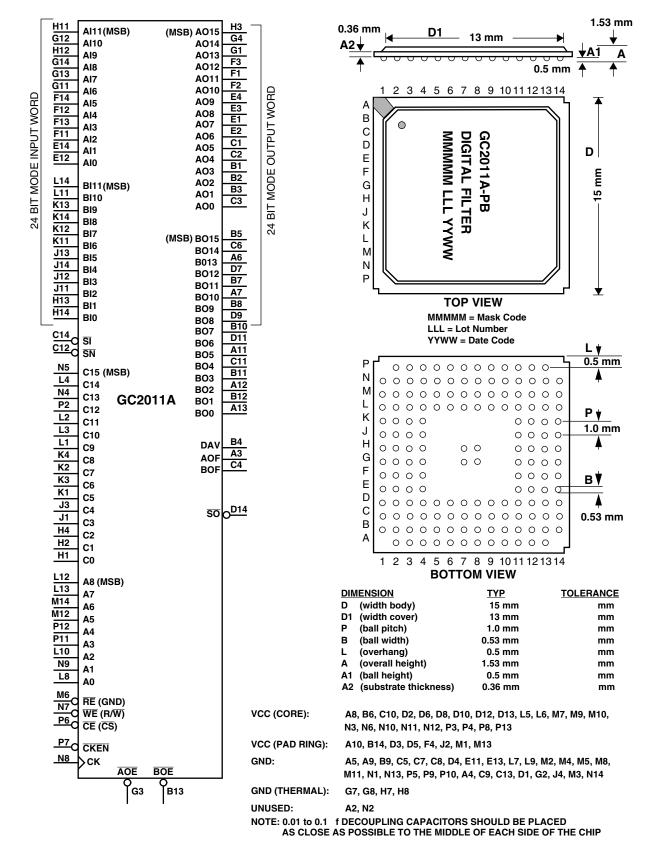

| <b>4.0</b><br>4.1<br>4.2                                                                                                                                                            | PACKAGING<br>160 PIN QUAD FLAT PACK (QFP) PACKAGE<br>160 PIN BALL GRID ARRAY (PBGA) PACKAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>23</b><br>.23<br>.25                                                                                                                                                                                              |

| 4.0<br>4.1<br>4.2<br>5.0                                                                                                                                                            | PACKAGING<br>160 PIN QUAD FLAT PACK (QFP) PACKAGE<br>160 PIN BALL GRID ARRAY (PBGA) PACKAGE<br>PIN DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .23<br>.23<br>.25<br>.25                                                                                                                                                                                             |

| <b>4.0</b><br>4.1<br>4.2                                                                                                                                                            | PACKAGING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23<br>.23<br>.25<br>27<br>28                                                                                                                                                                                         |

| 4.0<br>4.1<br>4.2<br>5.0                                                                                                                                                            | PACKAGING<br>160 PIN QUAD FLAT PACK (QFP) PACKAGE<br>160 PIN BALL GRID ARRAY (PBGA) PACKAGE<br>PIN DESCRIPTIONS<br>CONTROL REGISTERS<br>A-PATH AND B-PATH CONTROL REGISTER 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 23<br>.23<br>.25<br>27<br>28<br>.29                                                                                                                                                                                  |

| 4.0<br>4.1<br>4.2<br>5.0<br>6.0                                                                                                                                                     | PACKAGING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23<br>.23<br>.25<br>27<br>28<br>.29                                                                                                                                                                                  |

| 4.0<br>4.1<br>4.2<br>5.0<br>6.0<br>6.1                                                                                                                                              | PACKAGING<br>160 PIN QUAD FLAT PACK (QFP) PACKAGE<br>160 PIN BALL GRID ARRAY (PBGA) PACKAGE<br>PIN DESCRIPTIONS<br>CONTROL REGISTERS<br>A-PATH AND B-PATH CONTROL REGISTER 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .23<br>.25<br>.25<br>.27<br>.27<br>.28<br>.29<br>.31                                                                                                                                                                 |

| 4.0<br>4.1<br>4.2<br>5.0<br>6.0<br>6.1<br>6.2                                                                                                                                       | PACKAGING     160 PIN QUAD FLAT PACK (QFP) PACKAGE     160 PIN BALL GRID ARRAY (PBGA) PACKAGE     PIN DESCRIPTIONS     CONTROL REGISTERS     A-PATH AND B-PATH CONTROL REGISTER 0     A-PATH AND B-PATH CONTROL REGISTER 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 23<br>.23<br>.25<br>27<br>.27<br>.28<br>.29<br>.31<br>.32                                                                                                                                                            |

| 4.0<br>4.1<br>4.2<br>5.0<br>6.0<br>6.1<br>6.2<br>6.3                                                                                                                                | PACKAGING     160 PIN QUAD FLAT PACK (QFP) PACKAGE     160 PIN BALL GRID ARRAY (PBGA) PACKAGE     PIN DESCRIPTIONS     CONTROL REGISTERS     A-PATH AND B-PATH CONTROL REGISTER 0     A-PATH AND B-PATH CONTROL REGISTER 1     CASCADE MODE CONTROL REGISTER     COUNTER REGISTER     GAIN REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .23<br>.25<br>.25<br>.27<br>.27<br>.29<br>.31<br>.32<br>.32<br>.32                                                                                                                                                   |

| 4.0<br>4.1<br>4.2<br>5.0<br>6.0<br>6.1<br>6.2<br>6.3<br>6.4                                                                                                                         | PACKAGING     160 PIN QUAD FLAT PACK (QFP) PACKAGE     160 PIN BALL GRID ARRAY (PBGA) PACKAGE     PIN DESCRIPTIONS     CONTROL REGISTERS     A-PATH AND B-PATH CONTROL REGISTER 0     A-PATH AND B-PATH CONTROL REGISTER 1     CASCADE MODE CONTROL REGISTER     COUNTER REGISTER     GAIN REGISTER     OUTPUT MODE REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>23</b><br>.23<br>.25<br><b>27</b><br>.28<br>.29<br>.31<br>.32<br>.32<br>.32<br>.32<br>.34                                                                                                                         |

| 4.0<br>4.1<br>4.2<br>5.0<br>6.0<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5                                                                                                                  | PACKAGING     160 PIN QUAD FLAT PACK (QFP) PACKAGE     160 PIN BALL GRID ARRAY (PBGA) PACKAGE     PIN DESCRIPTIONS     CONTROL REGISTERS     A-PATH AND B-PATH CONTROL REGISTER 0     A-PATH AND B-PATH CONTROL REGISTER 1     CASCADE MODE CONTROL REGISTER     COUNTER REGISTER     GAIN REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>23</b><br>.23<br>.25<br><b>27</b><br>.28<br>.29<br>.31<br>.32<br>.32<br>.32<br>.32<br>.34                                                                                                                         |