**DATASHEET**

GD25LX256E-Rev1.4 1 October 2022

## **Contents**

| 1   | FEATURES                                                             | 4  |

|-----|----------------------------------------------------------------------|----|

| 2   | GENERAL DESCRIPTIONS                                                 | 5  |

|     | MEMORY ORGANIZATION                                                  |    |

|     | DEVICE OPERATIONS                                                    |    |

| 4.1 |                                                                      |    |

| 4.2 |                                                                      |    |

| 4.3 |                                                                      | _  |

| 4.4 |                                                                      |    |

| 4.5 |                                                                      |    |

| 5   | DATA PROTECTION                                                      | 12 |

| 6   | DATA INTEGRITY CHECK                                                 | 14 |

| 6.1 | 1 ECC (ERROR CHECKING AND CORRECTING)                                | 14 |

| 6.2 | 2 ECS# (Error corrected Signal) Pin                                  | 15 |

| 6.3 | 3 PARITY CHECK (CRC)                                                 | 15 |

| 7   | REGISTERS                                                            | 16 |

| 7.1 | 1 Status Register                                                    | 16 |

| 7.2 | 2 Flag Status Register                                               | 17 |

| 7.3 | 3 EXTENDED ADDRESS REGISTER                                          | 18 |

| 8   | INTERNAL CONFIGURATION REGISTER                                      | 20 |

| 8.1 | 1 Nonvolatile Configuration Register                                 | 20 |

| 8.2 | 2 VOLATILE CONFIGURATION REGISTER                                    | 22 |

| 8.3 | 3 SUPPORTED CLOCK FREQUENCIES                                        | 25 |

| 8.4 | 4 DATA SEQUENCE WRAPS BY DENSITY                                     | 26 |

| 9   | COMMAND DESCRIPTIONS                                                 | 27 |

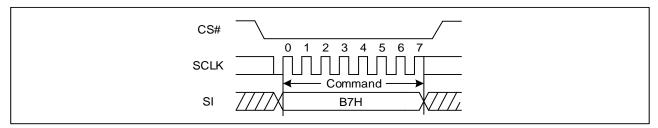

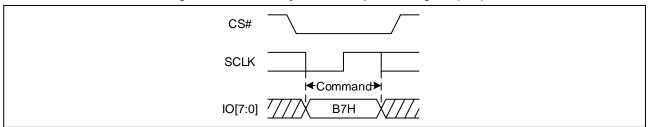

| 9.1 | 1 ENABLE 4-BYTE MODE (B7H)                                           | 31 |

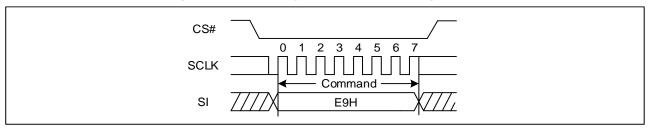

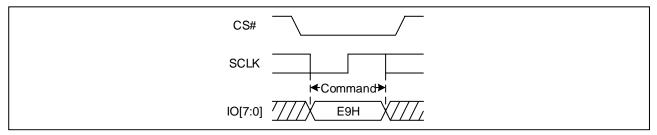

| 9.2 | 2 DISABLE 4-BYTE MODE (E9H)                                          | 31 |

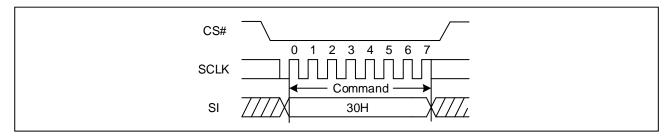

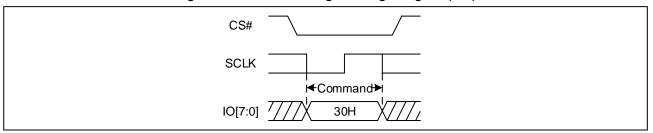

| 9.3 | 3 CLEAR FLAG STATUS REGISTER (30H)                                   | 32 |

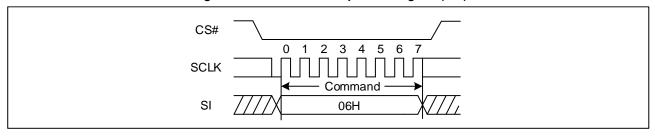

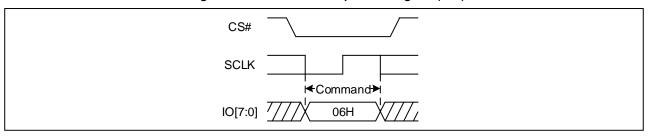

| 9.4 | 4 WRITE ENABLE (WREN) (06H)                                          | 32 |

| 9.5 | 5 WRITE DISABLE (WRDI) (04H)                                         | 33 |

| 9.6 | 6 WRITE ENABLE FOR VOLATILE STATUS REGISTER (50H)                    | 33 |

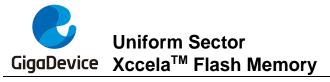

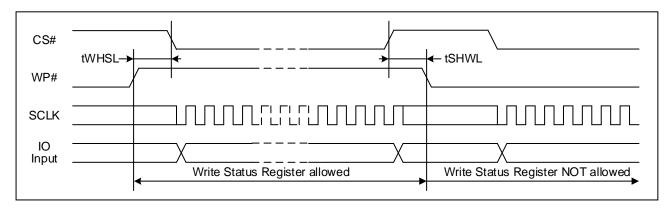

| 9.7 | 7 WRITE STATUS REGISTER (WRSR) (01H)                                 | 34 |

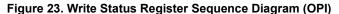

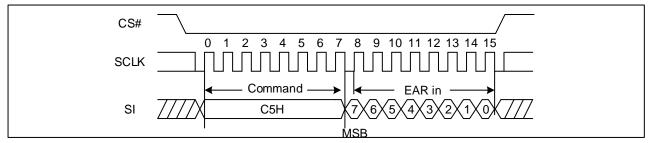

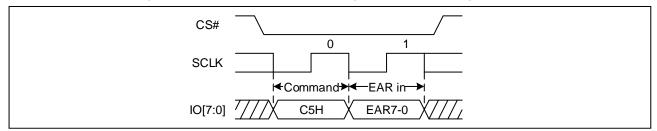

| 9.8 | 8 Write Extended Address Register (C5H)                              | 34 |

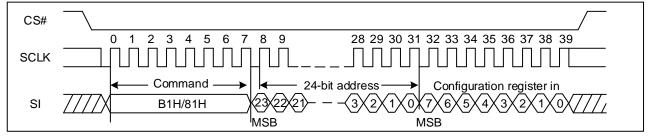

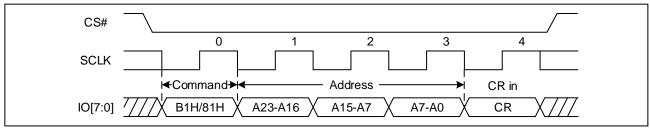

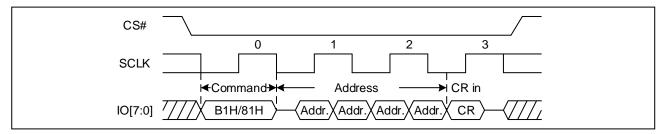

| 9.9 | 9 WRITE NONVOLATILE/VOLATILE CONFIGURATION REGISTER (WRCR) (B1H/81H) | 35 |

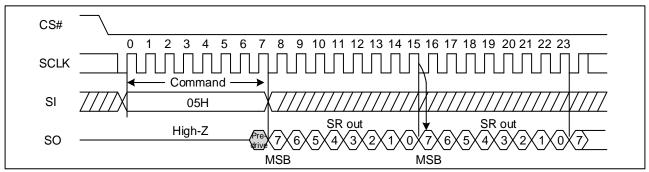

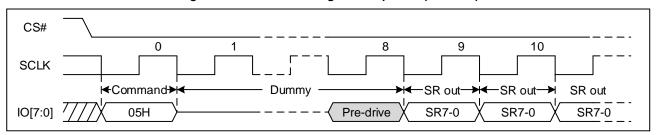

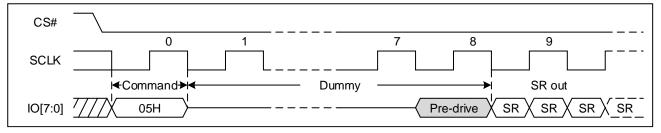

| 9.1 | 10 READ STATUS REGISTER (RDSR) (05H)                                 | 36 |

# Uniform Sector GigaDevice Xccela™ Flash Memory

# GD25LX256E

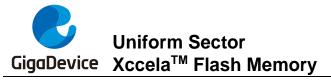

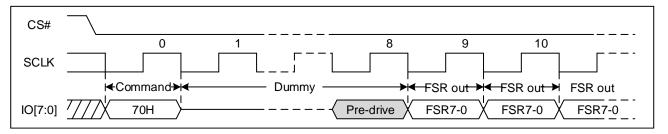

| 9.11 | READ FLAG STATUS REGISTER (RDSR) (70H)                     | 37 |

|------|------------------------------------------------------------|----|

| 9.12 | READ NONVOLATILE/VOLATILE CONFIGURATION REGISTER (B5H/85H) | 37 |

| 9.13 | READ EXTENDED ADDRESS REGISTER (C8H)                       | 38 |

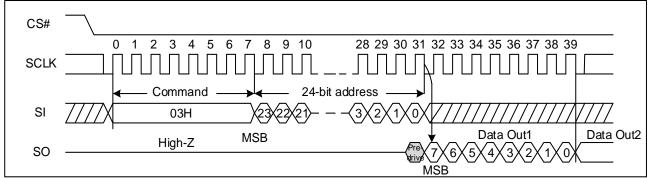

| 9.14 | READ DATA BYTES (READ) (03H/13H)                           | 39 |

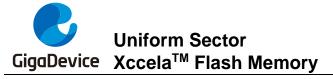

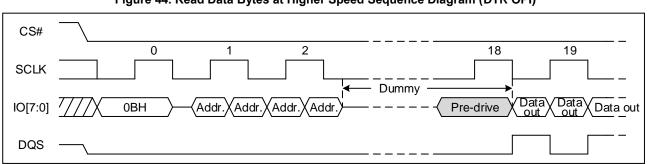

| 9.15 | READ DATA BYTES AT HIGHER SPEED (FAST READ) (OBH/OCH)      | 40 |

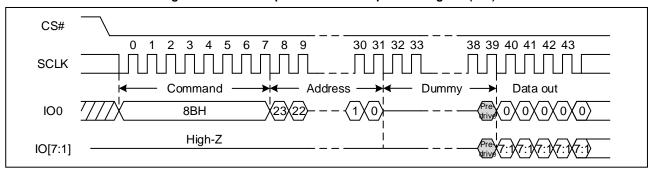

| 9.16 | OCTAL OUTPUT FAST READ (8BH/7CH)                           | 41 |

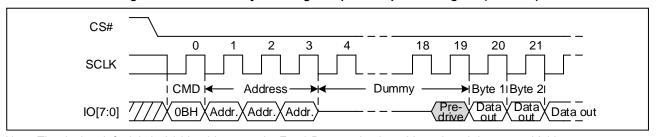

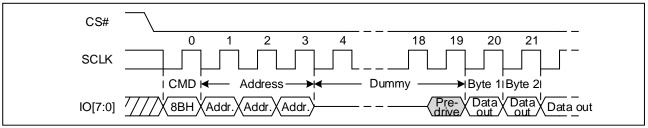

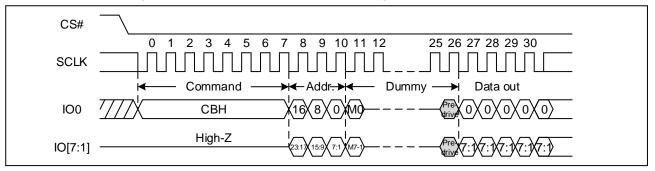

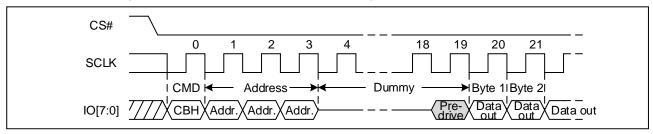

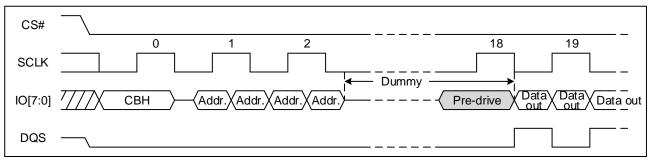

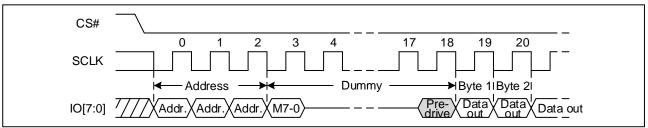

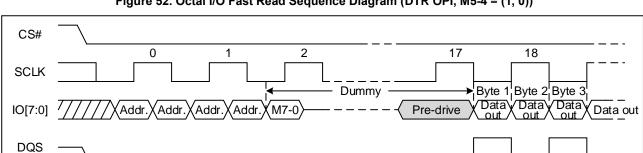

| 9.17 | OCTAL I/O FAST READ (CBH/CCH)                              | 41 |

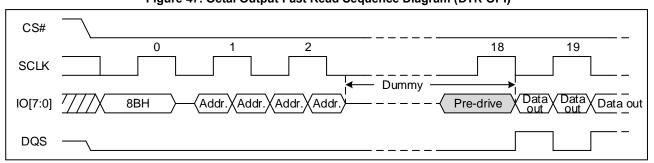

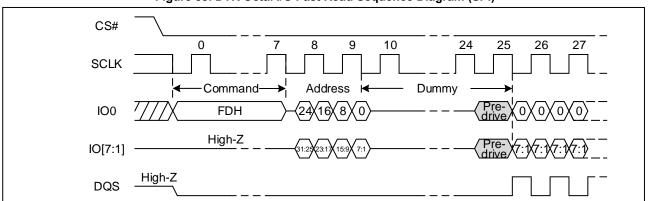

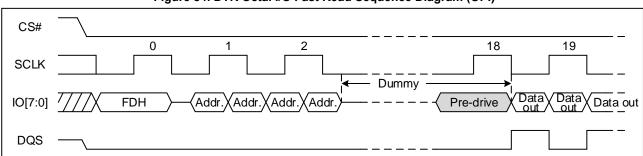

| 9.18 | OCTAL I/O DTR READ (FDH)                                   | 43 |

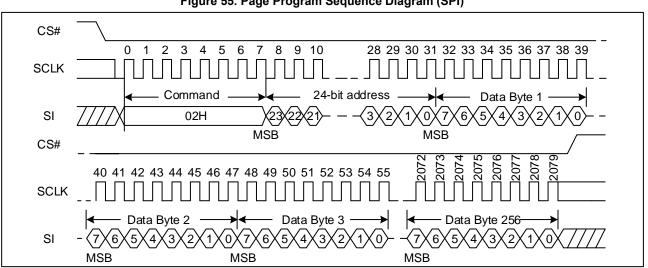

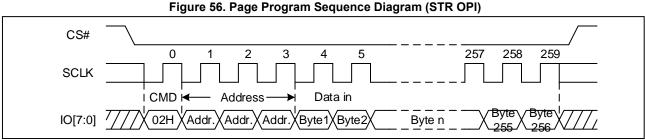

| 9.19 | Раде Program (PP) (02H/12H)                                | 44 |

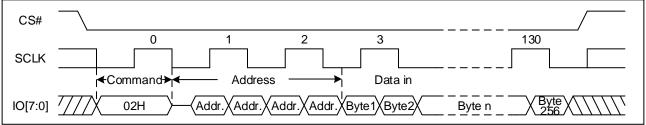

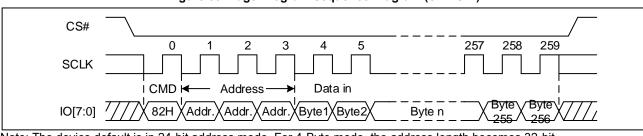

| 9.20 | Octal Page Program (82H/84H)                               | 45 |

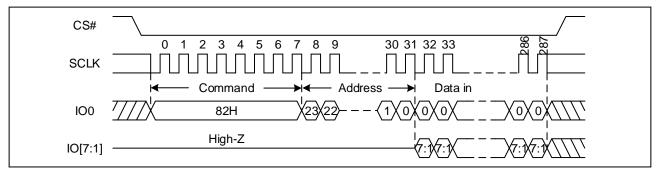

| 9.21 | EXTEND OCTAL PAGE PROGRAM (C2H/8EH)                        | 46 |

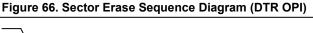

| 9.22 | Sector Erase (SE) (20H/21H)                                | 47 |

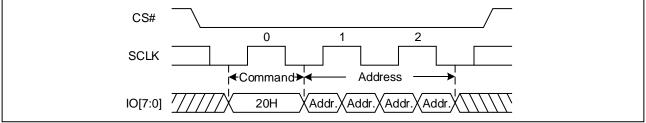

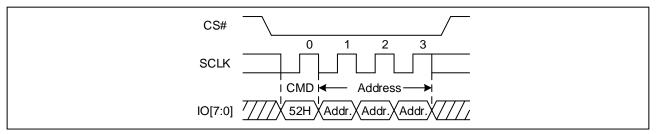

| 9.23 | 32KB BLOCK ERASE (BE32) (52H/5CH)                          | 48 |

| 9.24 | 64KB BLOCK ERASE (BE64) (D8H/DCH)                          | 49 |

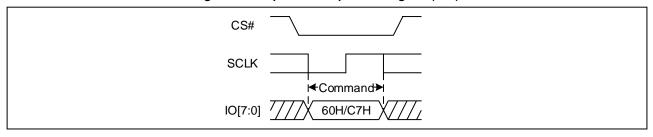

| 9.25 | CHIP ERASE (CE) (60H/C7H)                                  | 50 |

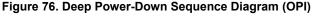

| 9.26 | DEEP POWER-DOWN (DP) (B9H)                                 | 51 |

| 9.27 | RELEASE FROM DEEP POWER-DOWN (ABH)                         | 51 |

| 9.28 | READ UNIQUE ID (4BH)                                       | 52 |

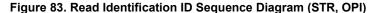

| 9.29 | READ IDENTIFICATION (RDID) (9FH/9EH)                       | 53 |

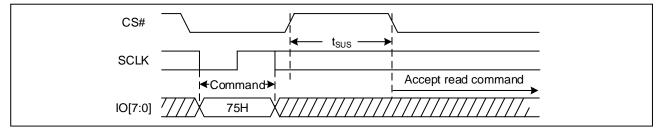

| 9.30 | PROGRAM/ERASE SUSPEND (PES) (75H)                          | 54 |

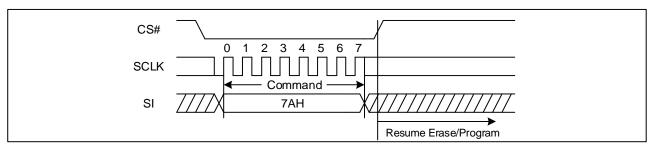

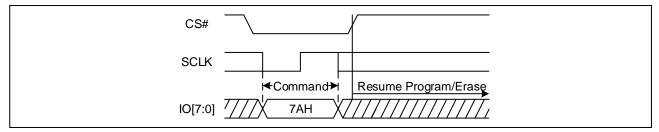

| 9.31 | PROGRAM/ERASE RESUME (PER) (7AH)                           | 55 |

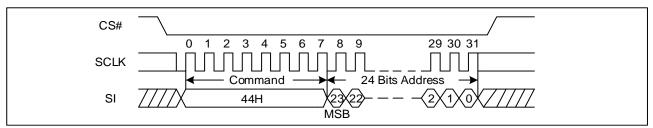

| 9.32 | Erase Security Registers (44H)                             | 56 |

| 9.33 | PROGRAM SECURITY REGISTERS (42H)                           | 57 |

| 9.34 | READ SECURITY REGISTERS (48H)                              | 58 |

| 9.35 | INDIVIDUAL BLOCK/SECTOR LOCK (36H)/UNLOCK (39H)/READ (3DH) | 59 |

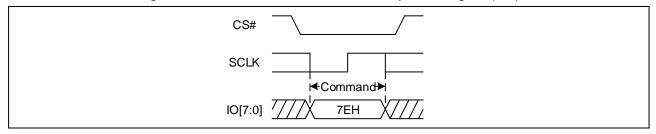

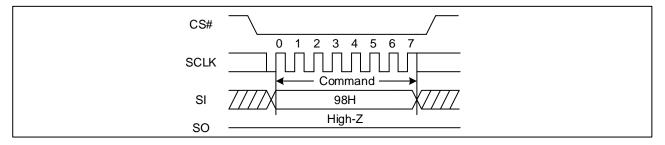

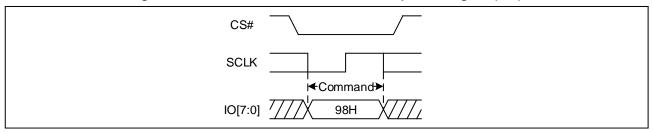

| 9.36 | GLOBAL BLOCK/SECTOR LOCK (7EH) OR UNLOCK (98H)             | 61 |

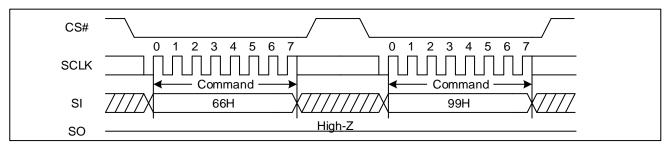

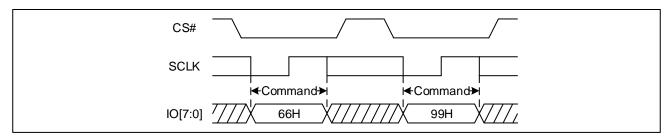

| 9.37 | Enable Reset (66H) and Reset (99H)                         | 62 |

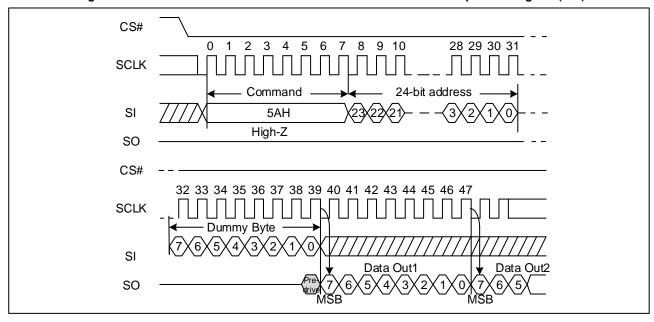

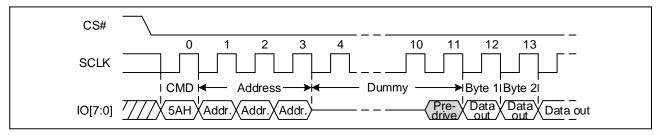

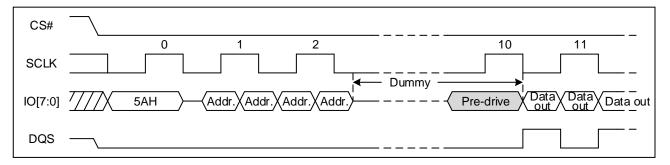

| 9.38 | READ SERIAL FLASH DISCOVERABLE PARAMETER (5AH)             | 63 |

| 10   | ELECTRICAL CHARACTERISTICS                                 | 65 |

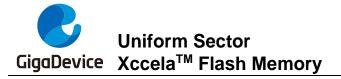

| 10.1 | Power-On Timing                                            | 65 |

| 10.2 | Initial Delivery State                                     | 65 |

| 10.3 | Absolute Maximum Ratings                                   | 65 |

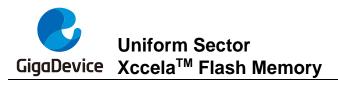

| 10.4 | CAPACITANCE MEASUREMENT CONDITIONS                         | 66 |

| 10.5 | DC Characteristics                                         | 67 |

| 10.6 | AC CHARACTERISTICS                                         | 70 |

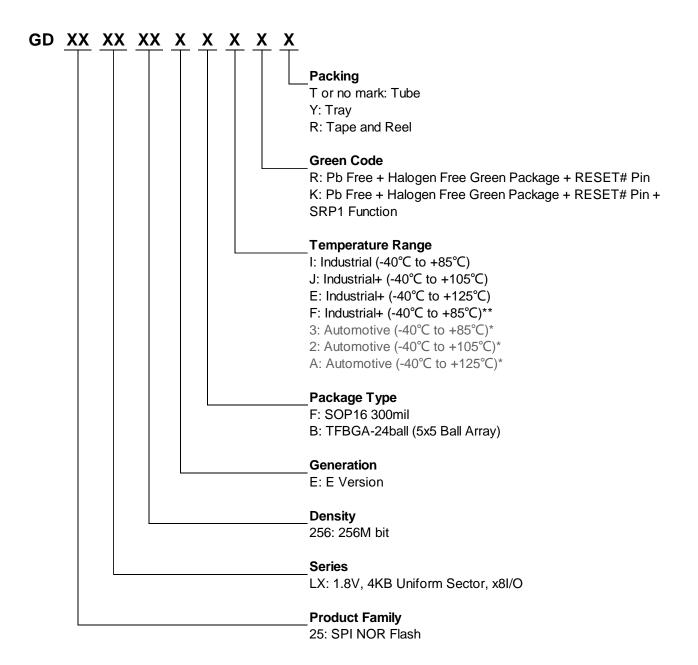

| 11   | ORDERING INFORMATION                                       | 79 |

| 11.1 | VALID PART NUMBERS                                         | 80 |

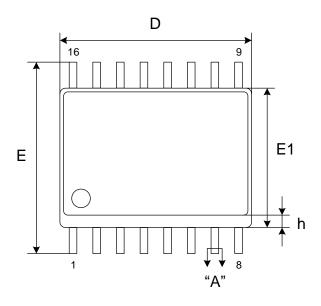

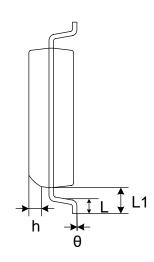

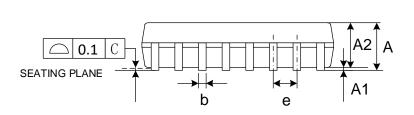

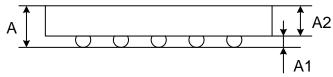

| 12   | PACKAGE INFORMATION                                        | 81 |

| 12.1 | PACKAGE SOP16 300MIL                                       | 81 |

| 12.2 | PACKAGE TFBGA-24BALL (5x5 ball array)                      | 82 |

| 13   | REVISION HISTORY                                           | 83 |

## 1 FEATURES

- ◆ 256M-bit Xccela<sup>™</sup> Flash

- 32M-Byte

- 256 Bytes per programmable page

- Standard, Octal SPI, DTR Octal SPI

- Standard SPI: SCLK, CS#, SI, SO, IO[7:2], WP#, RESET#

- Octal SPI: SCLK, CS#, IO[7:0], WP#, RESET#

- OPI DTR (Double Transfer Rate) Read

- 3- or 4-Byte Address Mode

- ◆ High Speed Clock Frequency

- 200MHz for fast read

- OPI Mode Data transfer up to 166MBytes/s

- Octal I/O Data transfer up to 166MBytes/s

- DTR Octal I/O Data transfer up to 400MBytes/s with DQS

- ◆ Allows XIP(eXecute in Place) Operation

- High speed Read reduce overall XiP instruction fetch time

- Continuous Read with Wrap further reduce data latency to fill up SoC cache

- ◆ Software/Hardware Write Protection

- Write protect all/portion of memory via software

- Enable/Disable protection with WP# Pin

- Individual Block Protection

- ◆ Data Integrity Check

- On-chip ECC (1-bit correction every 8-Byte) (1)

- CRC detects accidental changes to raw data

- ◆ Fast Program/Erase Speed

- Page Program time: 0.3ms typical

- Sector Erase time: 30ms typical

- Block Erase time: 0.1/0.2s typical

- Chip Erase time: 50s typical

- Flexible Architecture

- Sector of 4K-Byte

- Block of 32/64K-Byte

- Erase/Program Suspend/Resume

- ◆ Low Power Consumption

- 25µA typical stand-by current

- 5µA typical power-down current

- ◆ Advanced Security Features

- 128-bit Unique ID

- 4K-Byte Security Registers With OTP Lock

- ◆ Single Power Supply Voltage

- Full voltage range: 1.65~2.0V

- ◆ Endurance and Data Retention

- Minimum 100,000 Program/Erase Cycles

- 20-year data retention typical

- Package Information

- SOP16 300mil

- TFBGA-24ball (5x5 Ball Array)

#### Note:

1. When ECC is enabled, it is required to program minimum one or multiple aligned 8-Byte granularities. Every aligned 8-Byte granularity should only be programmed once before Erase to ensure correct ECC operations.

## 2 GENERAL DESCRIPTIONS

The GD25LX256E (256M-bit) Serial flash supports the standard Serial Peripheral Interface (SPI), and supports the Octal SPI and DTR mode: Serial Clock, Chip Select, Serial Data I/O0 (SI), I/O1 (SO), I/O2, I/O3, I/O4, I/O5, I/O6, I/O7, WP#, DQS, ECS# and RESET#. The Octal I/O & Octal output data is transferred with speed of 166MBytes/s, and the DTR Octal I/O data is transferred with speed of 400MBytes/s.

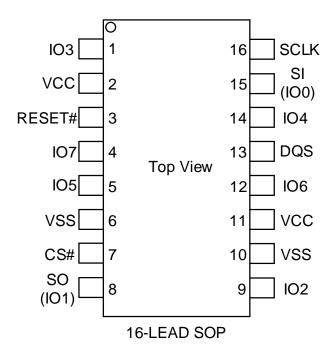

#### **CONNECTION DIAGRAM AND PIN DESCRIPTION**

Figure 1 Connection Diagram for SOP16 package

Table 1. Pin Description for SOP16 300mil package

| Pin No. | Pin Name | I/O | Description                       |

|---------|----------|-----|-----------------------------------|

| 1       | IO3      | I/O | Data Input Output 3               |

| 2       | VCC      |     | Power Supply                      |

| 3       | RESET#   | I   | Reset Input                       |

| 4       | 107      | I/O | Data Input Output 7               |

| 5       | IO5      | I/O | Data Input Output 5               |

| 6       | VSS      |     | Ground                            |

| 7       | CS#      | I   | Chip Select Input                 |

| 8       | SO (IO1) | I/O | Data Output (Data Input Output 1) |

| 9       | IO2      | I/O | Data Input Output 2               |

| 10      | VSS      |     | Ground                            |

| 11      | VCC      |     | Power Supply                      |

| 12      | IO6      | I/O | Data Input Output 6               |

| 13      | DQS      | 0   | Data Strobe Signal Output         |

| 14      | IO4      | I/O | Data Input Output 4               |

# **Uniform Sector** GigaDevice Xccela™ Flash Memory

**GD25LX256E**

| 15 | SI (IO0) | I/O | Data Input (Data Input Output 0) |

|----|----------|-----|----------------------------------|

| 16 | SCLK     | I   | Serial Clock Input               |

#### Note:

- 1. CS# must be driven high if chip is not selected. Please don't leave CS# floating any time after power is on.

- 2. The RESET# pin is a dedicated hardware reset pin regardless of device settings or operation states. If the hardware reset function is not used, it is recommended to connect it to VCC in the system but leaving it floating is OK.

- 3. Both two sets of VCC/VSS must be connected.

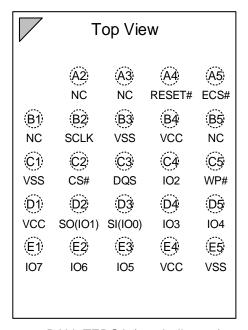

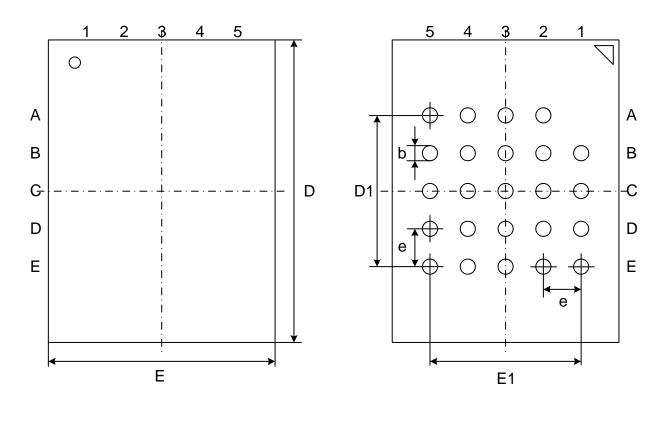

Figure 2 Connection Diagram for TFBGA24 5x5 ball array package

24-BALL TFBGA (5x5 ball array)

Table 2 Ball Description for TFBGA24 5x5 ball array package

| Pin No.  | Pin Name | 1/0 | Description                        |

|----------|----------|-----|------------------------------------|

| A4       | RESET#   | I   | Reset Input                        |

| A5       | ECS#     | 0   | ECC Correction Signal (Open Drain) |

| B2       | SCLK     | I   | Serial Clock Input                 |

| B3/C1/E5 | VSS      |     | Ground                             |

| B4/D1/E4 | VCC      |     | Power Supply                       |

| C2       | CS#      | I   | Chip Select Input                  |

| C3       | DQS      | 0   | Data Strobe Signal Output          |

| C4       | IO2      | I/O | Data Input Output 2                |

| C5       | WP#      | I   | Write Protect Input                |

| D2       | SO (IO1) | I/O | Data Output (Data Input Output 1)  |

| D3       | SI (IO0) | I/O | Data Input (Data Input Output 0)   |

| D4       | IO3      | I/O | Data Input Output 3                |

| D5       | 104      | I/O | Data Input Output 4                |

# **Uniform Sector** GigaDevice Xccela™ Flash Memory

**GD25LX256E**

| E1 | 107 | I/O | Data Input Output 7 |

|----|-----|-----|---------------------|

| E2 | IO6 | I/O | Data Input Output 6 |

| E3 | IO5 | I/O | Data Input Output 5 |

#### Note:

- 1. CS# must be driven high if chip is not selected. Please don't leave CS# floating any time after power is on.

- 2. The NC ball is not connected to any internal signal. It is OK to connect it to the system ground (GND) or leave it floating.

- 3. The RESET# pin is a dedicated hardware reset pin regardless of device settings or operation states. If the hardware reset function is not used, it is recommended to connect it to VCC in the system but leaving it floating is OK.

- 4. All the three sets of VCC/VSS must be connected.

- 5. If WP# is unused, it is recommended to connect it to VCC in the system but leaving it floating is OK.

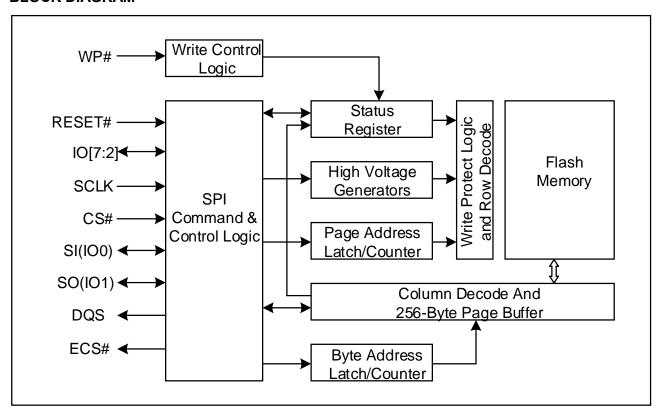

#### **BLOCK DIAGRAM**

## 3 MEMORY ORGANIZATION

## GD25LX256E

| Each device has | Each block has | Each sector has | Each page has |         |

|-----------------|----------------|-----------------|---------------|---------|

| 32M             | 64/32K         | 4K              | 256           | Bytes   |

| 128K            | 256/128        | 16              | -             | pages   |

| 8K              | 16/8           | -               | -             | sectors |

| 512/1K          | -              | -               | -             | blocks  |

#### **UNIFORM BLOCK SECTOR ARCHITECTURE**

GD25LX256E 64K Bytes Block Sector Architecture

| Block | Sector | Addres   | s range  |

|-------|--------|----------|----------|

|       | 8191   | 1FFF000H | 1FFFFFFH |

| 511   |        |          |          |

|       | 8176   | 1FF0000H | 1FF0FFFH |

|       | 8175   | 1FEF000H | 1FEFFFFH |

| 510   |        |          |          |

|       | 8160   | 1FE0000H | 1FE0FFFH |

|       |        |          |          |

|       |        |          |          |

|       |        |          |          |

|       |        |          |          |

|       |        |          |          |

|       |        |          |          |

|       | 47     | 02F000H  | 02FFFFH  |

| 2     |        |          |          |

|       | 32     | 020000H  | 020FFFH  |

|       | 31     | 01F000H  | 01FFFFH  |

| 1     |        |          |          |

|       | 16     | 010000H  | 010FFFH  |

|       | 15     | 00F000H  | 00FFFFH  |

| 0     |        |          |          |

|       | 0      | 000000H  | 000FFFH  |

## 4 DEVICE OPERATIONS

#### 4.1 SPI Mode

#### Standard SPI

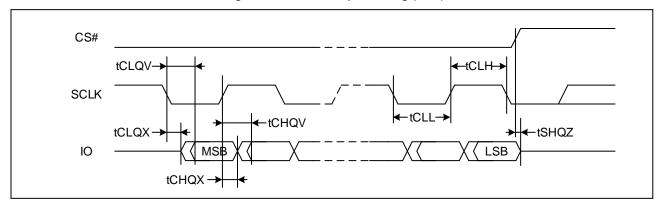

The GD25LX256E features a serial peripheral interface on 4 signals bus: Serial Clock (SCLK), Chip Select (CS#), Serial Data Input (SI) and Serial Data Output (SO). Both SPI bus mode 0 and 3 are supported. Input data is latched on the rising edge of SCLK and data shifts out on the falling edge of SCLK.

#### **Octal SPI**

The GD25LX256E supports Octal SPI operation when using the "Octal Output Fast Read", "Octal I/O Fast Read", "Octal Input Page Program, Extended Octal Input Fast Program" (8BH/7CH, CBH/CCH, 82H/84H,C2H/8EH) commands. These commands allow data to be transferred to or from the device at eight times the rate of the standard SPI. When using the Octal SPI command the SI and SO pins become bidirectional I/O pins: IO0 and IO1.

#### **Octal DTR SPI**

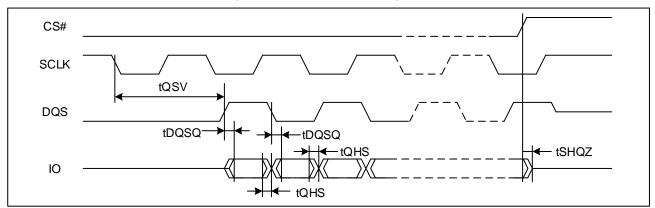

The GD25LX256E supports DTR Octal SPI operation when using the "DTR Octal I/O Fast Read" (FDH) command. This command allows data to be transferred to or from the device at sixteen times the rate of the standard SPI, and data output will be latched on both rising and falling edges of the serial clock. When using the DTR Octal SPI command the SI and SO pins become bidirectional I/O pins: IO0 and IO1.

#### 4.2 OPI Mode

#### Standard OPI

The GD25LX256E supports Octal Peripheral Interface (OPI) operations only when the device is switched to OPI mode by setting Byte<0> in Nonvolatile/Volatile Configuration Register. The OPI mode utilizes all 8 IO pins to input the command code. Input data is latched on the rising edge of SCLK and data shifts out on the falling edge of SCLK. Only one mode can be active at any given times. Upon power-up and after software reset using "Enable Reset (66H) and Reset (99H)" command, the state of the device is defined by the setting of Byte<0> in Nonvolatile Configuration Register.

#### **DTR OPI**

The GD25LX256E supports DTR OPI operation when the device is switched to DTR OPI mode by setting Byte<0> in Nonvolatile/Volatile Configuration Register. The data input/output will be latched on both rising and falling edges of the serial clock. Only one mode can be active at any given times. Upon power-up and after software reset using "Enable Reset (66H) and Reset (99H)" command, the state of the device is defined by the setting of Byte<0> in Nonvolatile Configuration Register.

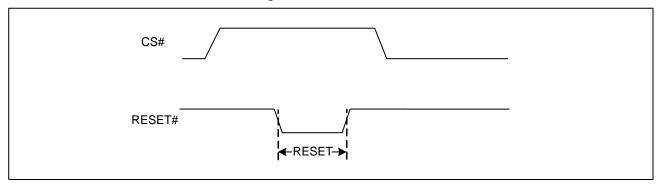

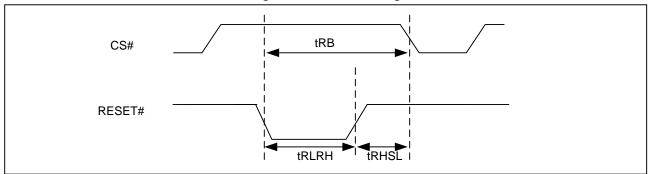

#### 4.3 RESET Function

The RESET# pin allows the device to be reset by the control.

The RESET# pin goes low for a minimum period of tRLRH will reset the flash. After reset cycle, the flash is at the following states:

- Standby mode

- All the volatile bits will return to the default status as power on.

#### **Figure 3 RESET Condition**

#### 4.4 ECC Function

The ECC Correction Signal (ECS#) pin is provided to the system hardware designers to determine the ECC status during any Read operation. The ECS# pin will be pulled low during any 8-Byte Read data output period in which an ECC event has occurred. ECS# pin can be used to represent SEC (Single Error Correction) event. ECC Correction Signal Output pin is an Open-Drain connection.

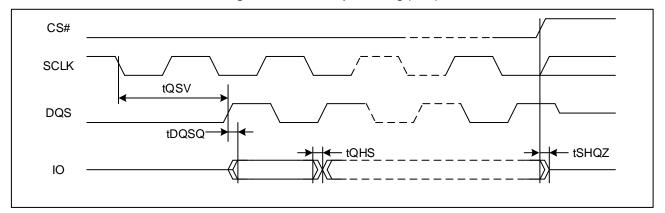

#### 4.5 Data Strobe Function

The Data Strobe function is enabled as default for this device, and the DQS pin is an active output pin for the Data Strobe (DQS) signal during Read operations. The DQS signal is typically used in high speed applications to indicate when the output data is ready to be fetched by the controllers. When the data strobe function is enabled, DQS signal is driven to ground once CS# goes LOW, and will start to toggle when the output data is ready on the I/O pins. The toggling frequency is the same as the CLK frequency. For STR Read operations, the data should only be latched on the rising edge of DQS signal. For DTR Read operations, the data should be latched on both rising edge and falling edge of the DQS signal. The Data Strobe function can also be disabled by setting the non-volatile or volatile Configuration Register Byte<0>. Please refer to the Configuration Register description for details. When disabled, the DQS signal is not driven and will stay at Hi-Z state.

#### 5 DATA PROTECTION

The GD25LX256E provide the following data protection methods:

- Write Enable (WREN) command: The WREN command is set the Write Enable Latch bit (WEL). The WEL bit will return to reset by the following situation:

- Power-Up/ Software reset (66H+99H)

- Write Disable (WRDI)

- Write Status Register (WRSR)

- Write Extended Address Register (WEAR)

- Write Nonvolatile Configuration Register (WNVCR)

- Write Volatile Configuration Register (WVCR)

- Page Program (PP)

- Sector Erase (SE) / Block Erase (BE) / Chip Erase (CE)

- Erase Security Registers / Program Security Registers

- ♦ Software Protection Mode:

- -The Block Protect (BP4, BP3, BP2, BP1, and BP0) bits define the section of the memory array that can be read but cannot be changed.

- Individual Block Protection bit provides the protection selection of each individual block.

- ◆ Hardware Protection Mode: WP# goes low to protect the BP0~BP4 bits and SRP0 bit.

- Deep Power-Down Mode: In Deep Power-Down Mode, all commands are ignored except the Release from Deep Power-Down Mode command and reset command (66H+99H).

Table 3. GD25LX256E Protected area size

| ;   | Status F | Register | Conten | t   |            | Memory Conte        | nt      |             |

|-----|----------|----------|--------|-----|------------|---------------------|---------|-------------|

| BP4 | BP3      | BP2      | BP1    | BP0 | Blocks     | Addresses           | Density | Portion     |

| Х   | 0        | 0        | 0      | 0   | NONE       | NONE                | NONE    | NONE        |

| 0   | 0        | 0        | 0      | 1   | 511        | 01FF0000h-01FFFFFh  | 64KB    | Upper 1/512 |

| 0   | 0        | 0        | 1      | 0   | 510 to 511 | 01FE0000h-01FFFFFh  | 128KB   | Upper 1/256 |

| 0   | 0        | 0        | 1      | 1   | 508 to 511 | 01FC0000h-01FFFFFh  | 256KB   | Upper 1/128 |

| 0   | 0        | 1        | 0      | 0   | 504 to 511 | 01F80000h-01FFFFFh  | 512KB   | Upper 1/64  |

| 0   | 0        | 1        | 0      | 1   | 496 to 511 | 01F00000h-01FFFFFh  | 1MB     | Upper 1/32  |

| 0   | 0        | 1        | 1      | 0   | 480 to 511 | 01E00000h-01FFFFFh  | 2MB     | Upper 1/16  |

| 0   | 0        | 1        | 1      | 1   | 448 to 511 | 01C00000h-01FFFFFh  | 4MB     | Upper 1/8   |

| 0   | 1        | 0        | 0      | 0   | 384 to 511 | 01800000h-01FFFFFh  | 8MB     | Upper 1/4   |

| 0   | 1        | 0        | 0      | 1   | 256 to 511 | 01000000h-01FFFFFh  | 16MB    | Upper 1/2   |

| 1   | 0        | 0        | 0      | 1   | 0          | 00000000h-0000FFFFh | 64KB    | Lower 1/512 |

| 1   | 0        | 0        | 1      | 0   | 0 to 1     | 00000000h-0001FFFFh | 128KB   | Lower 1/256 |

| 1   | 0        | 0        | 1      | 1   | 0 to 3     | 00000000h-0003FFFFh | 256KB   | Lower 1/128 |

| 1   | 0        | 1        | 0      | 0   | 0 to 7     | 00000000h-0007FFFFh | 512KB   | Lower 1/64  |

| 1   | 0        | 1        | 0      | 1   | 0 to 15    | 00000000h-000FFFFh  | 1MB     | Lower 1/32  |

| 1   | 0        | 1        | 1      | 0   | 0 to 31    | 00000000h-001FFFFh  | 2MB     | Lower 1/16  |

| 1   | 0        | 1        | 1      | 1   | 0 to 63    | 00000000h-003FFFFh  | 4MB     | Lower 1/8   |

# **Uniform Sector** GigaDevice Xccela<sup>™</sup> Flash Memory

## **GD25LX256E**

| 1 | 1 | 0 | 0 | 0 | 0 to 127 | 00000000h-007FFFFh | 8MB  | Lower 1/4 |

|---|---|---|---|---|----------|--------------------|------|-----------|

| 1 | 1 | 0 | 0 | 1 | 0 to 255 | 00000000h-00FFFFFh | 16MB | Lower 1/2 |

| Х | 1 | 1 | 0 | Х | ALL      | 00000000h-01FFFFFh | 32MB | ALL       |

| Х | 1 | Х | 1 | Χ | ALL      | 00000000h-01FFFFFh | 32MB | ALL       |

#### Table 4. GD25LX256E Individual Block Protection (WPS=0)

| Block | Sector    | Addres     | s range    | Individual Block Lock Operation |

|-------|-----------|------------|------------|---------------------------------|

|       | 8191      | 01FF F000h | 01FF FFFFh | 512 Blocks                      |

| 511   |           |            |            | Block Lock: 36H+Address         |

|       | 8176      | 01FF 0000h | 01FF 0FFFh | Block Unlock: 39H+Address       |

| 510   | 8160~8175 | 01FE 0000h | 01FE FFFFh | Read Block Lock: 3DH+Address    |

|       |           |            |            | Global Block Lock: 7EH          |

|       |           |            |            | Global Block Unlock: 98H        |

|       |           |            |            |                                 |

| 1     | 16~31     | 0001 0000h | 0001 FFFFh |                                 |

|       | 15        | 0000 F000h | 0000 FFFFh |                                 |

| 0     |           |            |            |                                 |

|       | 0         | 0000 0000h | 0000 0FFFh |                                 |

#### Notes:

- 1. Protection configuration: This bit is used to select which Write Protect scheme should be used.

- 2. Individual Block Protection bits are volatile lock bits. Each volatile bit corresponds to and provides volatile protection for an individual memory sector, which is locked temporarily (protection is cleared when the device is reset or powered down).

- 3. The first and last sectors will have volatile protections at the 4KB sector level. Each 4KB sector in these sectors can be individually locked by volatile lock bits setting.

#### 6 DATA INTEGRITY CHECK

The data storage and transmission errors will cause unexpected Flash device variation that makes a harmful impact on overall system functions. To prevent these errors, GD25LX256E product provides advanced Data Integrity Check function. For the data storage and data transmission in the flash device, Data Integrity Check can check errors and correct them, allowing self-checking and preventing errors in advance.

The Data Integrity Check function includes two methods:

- ECC (Error Checking and Correcting): to prevent the data storage errors

- CRC (Cyclic Redundancy Check): to prevent the data transmission errors

The register data and software signals can also be used to associate the Data Integrity Check function to fully record the results of checking, and can also immediately feedback.

## 6.1 ECC (Error Checking and Correcting)

Error Correction Codes (ECC) is a commonly used technique in non-volatile memory to reduce the device Bit Error Rate (BER) during the device operation life and improve device reliability. To achieve error detection and correction, redundancy data must be added to store the ECC calculation results for a given length of data. In GD25LX256E, every aligned 8-Byte data (A[2:0] = 0, 0, 0) stored in the memory array will be checked by the internal ECC engine using SEC (Single Error Correction) Hsiao Codes algorithm. With 8-Byte ECC data granularity, ECC calculation latency time can be minimized and highest level of data integrity can be preserved.

The default value of all memory data is FFH (Erased) when the device is shipped from the factory. A "Page Program (02H/12H)" or "Octal Page Program (82H/84H)" or "Extend Octal Page Program (C2H/8EH)" command can be used to program the user data into the memory array. ECC calculation will be performed during the internal programming operation and the results are stored in the redundancy or spare area of the memory array. It is necessary to program every page in aligned 8-Byte granularity so that ECC engine can store the correct ECC information. It is also required that every aligned 8-Byte data granularity can only be programmed once to avoid additional ECC calculation in the same granularity resulting incorrect ECC results. A technique previously known as "Incremental Byte/Bit Programming to the same Byte location" cannot be used for GD25LX256E when ECC is enabled.

During data read operations, the internal ECC engine will check the ECC results stored in the spare area and apply necessary error correction or error detection to the main array data being read out. It is necessary to check the ECC Status Bits (SEC) in the Status Register after every Read operation to see if the data read out contains one error or not. A Read operation can start from any Byte address and continue through the entire memory array, so it is not necessary to align the 8-Byte granularity boundary address to start a Read command.

Additional hardware monitoring of the ECC status can also be used to observe the ECC status in real time during any data output. When configured, the ECS# (ECC Correction Signal) pin will be pulled low during any aligned 8-Byte data output if it contains SEC event.

The SEC bit can be reset through anyone of the following situations:

- Sending a new Read Command

- Issuing Software Reset Command

- Hardware Reset

- Power-up cycle

## 6.2 ECS# (Error corrected Signal) Pin

The ECS# pin is a real time hardware signal to feedback the ECC correction status. The ECS# pin is designed as an open drain structure and a pull-up resistor (Rp) is required. In normal situation, the ECS# is kept on High-Z state. Once error correction begins, the ECS# pin will pull low during the whole ECC chunk unit after a duration of tECSV delay timing. The ECS# (ECC Correction Signal) pin will be pulled low during any aligned 8-Byte data output if it contains SEC (Single Error Correction) event.

CS#

SCLK

IO[7:0]

Command & Address & Dummys

High-Z

ECC chunk (8 Bytes)

ECC chunk (8 Bytes)

High-Z

High-Z

Figure 4. ECS# Timing

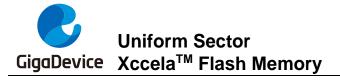

## 6.3 Parity Check (CRC)

The parity check function can only be operated in DTR read mode, and it is not supported in STR mode. The bit7~6 in Byte<4> of the Configuration Register can set the parity check function.

For read operation after the Parity check function is enabled, the data CRC bit should be output by each CRC chunk unit. Otherwise, read CRC code might be error.

The CRC Chunk size can be configured as 16-Byte, 32-Byte, or 64-Byte by the Configuration Register setting. However, when the device enters the "Read with Wrap" mode, while the CRC function is also enabled, and the CRC Chunk size will be set to be identical with the Wrap Length (16-Byte, 32-Byte, or 64-Byte) by internal circuitry. Only when the device is not in the "Read with Wrap" mode, the original CRC Chunk size setting will be restored.

The data CRC Bytes are calculated by exclusive-OR on each I/O bus in the CRC chunk.

Figure 5. CRC Timing

#### 7 REGISTERS

## 7.1 Status Register

Table 5. Status Register

| No. | Bit Name | Description                | Note                  |

|-----|----------|----------------------------|-----------------------|

| S7  | SRP0     | Status Register Protection | Non-volatile writable |

| S6  | BP4      | Block Protect Bits         | Non-volatile writable |

| S5  | BP3      | Block Protect Bits         | Non-volatile writable |

| S4  | BP2      | Block Protect Bits         | Non-volatile writable |

| S3  | BP1      | Block Protect Bits         | Non-volatile writable |

| S2  | BP0      | Block Protect Bits         | Non-volatile writable |

| S1  | WEL      | Write Enable Latch         | Volatile, read only   |

| S0  | WIP      | Erase/Write In Progress    | Volatile, read only   |

The status and control bits of the Status Register are as follows:

#### WIP bit

The Write in Progress (WIP) bit indicates whether the memory is busy in program/erase/write status register or configuration register progress. When WIP bit sets to 1, means the device is busy in program/erase/write status register or configuration register progress, when WIP bit sets 0, means the device is not in program/erase/write status register or configuration register progress.

#### **WEL** bit

The Write Enable Latch (WEL) bit indicates the status of the internal Write Enable Latch. When set to 1 the internal Write Enable Latch is set, when set to 0 the internal Write Enable Latch is reset and no Write, Program or Erase command is accepted.

#### BP4, BP3, BP2, BP1, BP0 bits

The Block Protect (BP4, BP3, BP2, BP1, and BP0) bits are non-volatile. They define the size of the area to be software protected against Program and Erase commands. These bits are written with the Write Status Register (WRSR) command. When the Block Protect (BP4, BP3, BP2, BP1, and BP0) bits are set to 1, the relevant memory area becomes protected against Page Program (PP), Sector Erase (SE) and Block Erase (BE) commands. The Block Protect (BP4, BP3, BP2, BP1, and BP0) bits can be written provided that the Hardware Protected mode has not been set. The Chip Erase (CE) command is executed only if none sector or block is protected.

#### SRP0 bit

The Status Register Protect SRP0 bit are non-volatile Read/Write bits in the status register. The SRP0 bit in conjunction with SRP1 bit (Reference Configuration Register) control the method of write protection: software protection, hardware protection, power supply lock-down or one time programmable protection.

| SRP1 | SRP0                     | WP#                | Status Register                                            | Description |

|------|--------------------------|--------------------|------------------------------------------------------------|-------------|

|      | X 0 X Software Protected | Software Dretected | The Status Register can be written to after a Write Enable |             |

| ^    |                          | Software Protected | command, WEL=1. (Default)                                  |             |

| 0 | 1 | 0 | Hardware Protected              | WP#=0, the Status Register locked and cannot be written to.                                       |

|---|---|---|---------------------------------|---------------------------------------------------------------------------------------------------|

| 0 | 1 | 1 | Hardware Unprotected            | WP#=1, the Status Register is unlocked and can be written to after a Write Enable command, WEL=1. |

| 1 | 1 | х | One Time Program <sup>(1)</sup> | Status Register is permanently protected and cannot be written to.                                |

#### NOTE:

## 7.2 Flag Status Register

Table 6. Flag Status Register

| No. | Bit Name | Description          | Note                |

|-----|----------|----------------------|---------------------|

| FS7 | RY/BY#   | Ready/Busy#          | Volatile, read only |

| FS6 | SUS1     | Erase Suspend        | Volatile, read only |

| FS5 | EE       | Erase Error bit      | Volatile, read only |

| FS4 | PE       | Program Error bit    | Volatile, read only |

| FS3 | Reserved | Reserved             | Volatile, read only |

| FS2 | SUS2     | Program Suspend      | Volatile, read only |

| FS1 | PTE      | Protection Error bit | Volatile, read only |

| FS0 | ADS      | Current Address Mode | Volatile, read only |

The status and control bits of the Flag Status Register are as follows:

#### **ADS** bit

The Address Status (ADS) bit is a read only bit that indicates the current address mode the device is operating in. The device is in 3-Byte address mode when ADS=0 (default), and in 4-Byte address mode when ADS=1.

#### PTE bit

The PTE bit is a read only bit that indicates a program or erase failure. Indicates whether an ERASE or PROGRAM operation has attempted to modify the protected array sector, or whether a PROGRAM operation has attempted to access the locked OTP space. PTE is cleared to "0" after program or erase operation resumes or by Clear Flag Status Register command (30H).

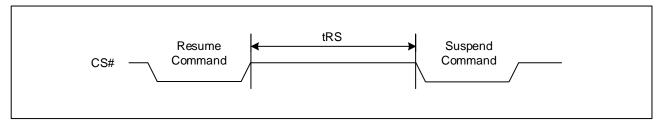

#### SUS1, SUS2 bits

The SUS1 and SUS2 bits are read only bit in the Flag Status Register (FS6 and FS2) that are set to 1 after executing an Erase/Program Suspend (75H) command (The Erase Suspend will set the SUS1 to 1, and the Program Suspend will set the SUS2 to 1). The SUS1 and SUS2 bits are cleared to 0 by Erase/Program Resume (7AH) command, software reset (66H+99H) command as well as a power-down, power-up cycle.

#### PE bit

The Program Error (PE) bit is a read only bit that indicates a program failure. It will also be set when the user attempts to program a protected array sector or access the locked OTP space. PE is cleared to "0" after program or erase operation resumes or by Clear Flag Status Register command (30H).

<sup>1.</sup> This feature is available on special order. Please contact GigaDevice for details.

#### **EE** bit

The Erase Error (EE) bit is a read only bit that indicates an erase failure. It will also be set when the user attempts to erase a protected array sector or access the locked OTP space. EE is cleared to "0" after erase or program operation resumes or by Clear Flag Status Register command (30H).

#### RY/BY# bit

The RY/BY# bit is a read only bit that indicates Program or Erase Status bit. Indicates whether one of the following command cycles is in progress: WRITE STATUS REGISTER, WRITE NONVOLATILE CONFIGURATION REGISTER, PROGRAM, or ERASE.

## 7.3 Extended Address Register

**Table 7 Extended Address Register**

| No. | Name     | Description                 | Note                |

|-----|----------|-----------------------------|---------------------|

| EA7 | SEC      | Single Error Correction Bit | Volatile, read only |

| EA6 | Reserved | Reserved                    | Reserved            |

| EA5 | Reserved | Reserved                    | Reserved            |

| EA4 | Reserved | Reserved                    | Reserved            |

| EA3 | Reserved | Reserved                    | Reserved            |

| EA2 | Reserved | Reserved                    | Reserved            |

| EA1 | Reserved | Reserved                    | Reserved            |

| EA0 | A24      | Address bit                 | Volatile writable   |

The extended address register is only used when the address mode is 3-Byte mode, as to set the higher address. The default value of the address bit is "0".

For the read operation, the whole array can be continually read out with one command. Data output starts from the selected 128Mb, and it can cross the boundary. When the last Byte of the segment is reached, the next Byte (in a continuous reading) is the first Byte of the next segment. However, the EAR (Extended Address Register) value does not change. The random access reading can only be operated in the selected segment.

The Chip erase command will erase the whole chip and is not limited by EAR selected segment. However, the sector erase, block erase, program operation are limited in selected segment and will not cross the boundary.

#### A24 bit

The Extended Address Bits A24 is used only when the device is operating in the 3-Byte Address Mode (ADS=0), which is volatile writable by C5H command. The lowest 128Mb memory array (00000000h – 00FFFFFh) is selected when A24 =0, and all instructions with 3-Byte addresses will be executed within that region.

If Configuration Register Byte <5> set to FEH, or an "Enter 4-Byte Address Mode (B7H)" instruction is issued, the device will require 4-Byte address input for all address related instructions, and the Extended Address Bit setting will be ignored.

| A24 | Address Range         |

|-----|-----------------------|

| 0   | 0000 0000h-00FF FFFFh |

| 1   | 0100 0000h-01FF FFFFh |

# **Uniform Sector** GigaDevice Xccela<sup>™</sup> Flash Memory

**GD25LX256E**

#### **SEC** bit

SEC (Single Error Correction) Status Bit are used to show the ECC results for the last Read operation. SEC bit will be cleared to 0 once the device accepts a new Read command.

| SEC | Definitions                                                                                                                                               |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | No ECC events in all aligned 8-Byte granularities                                                                                                         |

| 1   | SEC events in single or multiple 8-Byte granularities, and the data is OK to use. (Unless it contains more than one odd bit errors in 8-Byte granularity) |

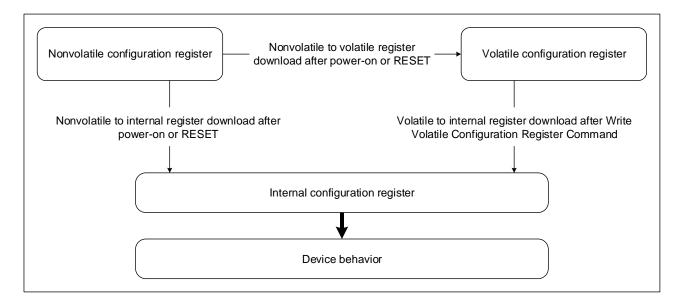

## INTERNAL CONFIGURATION REGISTER

The memory configuration is set by an internal configuration register that is not directly accessible to users. The user can change the default configuration at power up by using the WRITE NONVOLATILE CONFIGURATION REGISTER. Information from the nonvolatile configuration register overwrites the internal configuration register during power on or after a reset.

The user can change the configuration during device operation using the WRITE VOLATILE CONFIGURATION REGISTER command. Information from the volatile configuration registers overwrite the internal configuration register immediately after the WRITE command completes.

#### 8.1 Nonvolatile Configuration Register

Nonvolatile Configuration Register bits set the device configuration after power-up or reset. All bits are erased (FFh) unless stated otherwise. This register is read from and written to using the READ NONVOLATILE CONFIGURATION REGISTER and the WRITE NONVOLATILE CONFIGURATION REGISTER commands, respectively. The commands use the main array address scheme, but only the LSB is used to access different register settings, thereby providing up to 256 Bytes of registers (See the table below for the details). A WRITE command to a reserved address will set the device to the default status of the corresponding Byte.

|      | lable 8. Nonvolatile Configuration Register |       |      |      |      |      |          |      |      |                        |

|------|---------------------------------------------|-------|------|------|------|------|----------|------|------|------------------------|

| Addr | Settings                                    | bit7  | bit6 | bit5 | bit4 | bit3 | bit2     | bit1 | bit0 | Description            |

|      |                                             | 1     | 1    | 1    | 1    | 1    | 1        | 1    | 1    | SPI with DQS (Default) |

|      |                                             | 1     | 1    | 0    | 1    | 1    | 1        | 1    | 1    | SPI W/O DQS            |

|      |                                             | 1     | 1    | 1    | 0    | 0    | 1        | 1    | 1    | Octal DTR with DQS     |

| <0>  | I/O mode                                    | 1     | 1    | 0    | 0    | 0    | 1        | 1    | 1    | Octal DTR W/O DQS      |

|      |                                             | 1     | 0    | 1    | 1    | 0    | 1        | 1    | 1    | Octal STR with DQS     |

|      |                                             | 1     | 0    | 0    | 1    | 0    | 1        | 1    | 1    | Octal STR W/O DQS      |

|      |                                             | Other | rs   |      |      |      | Reserved |      |      |                        |

# Uniform Sector GigaDevice Xccela<sup>™</sup> Flash Memory

## **GD25LX256E**

|     |                               | 0     | 0        | 0 | 0        | 0                           | 0        | 1  | 1  | 3 Dummy                       |

|-----|-------------------------------|-------|----------|---|----------|-----------------------------|----------|----|----|-------------------------------|

|     |                               | 0     | 0        | 0 | 0        | 0                           | 1        | 0  | 0  | 4 Dummy                       |

| <1> | Dummy cycle                   | 0     | 0        | 0 | 0        | 0                           | '        | U  | 0  | 05~1E: 5~30 Dummy             |

|     | configuration(6-7)            |       |          |   |          |                             |          |    |    | (Default=10h)                 |

|     |                               | Othe  | re       |   |          |                             | Reserved |    |    |                               |

|     |                               | Otile | 15       |   |          | Security Registers Unlocked |          |    |    |                               |

|     |                               | х     | х        | х | х        | х                           | х        | х  | 0  | (Default)                     |

|     |                               | x     | х        | х | х        | х                           | х        | х  | 1  | Security Registers Locked     |

| <2> | OTP configuration             | X     | X        | x | 0        | x                           | x        | x  | x  | SRP1 Unlocked (Default)       |

|     |                               | x     | X        | x | 1        | x                           | x        | x  | x  | SRP1 Locked <sup>(11)</sup>   |

|     |                               | Othe  |          |   | <u>'</u> |                             |          | ^  |    | Reserved                      |

|     |                               | 1     | 1        | 1 | 1        | 1                           | 1        | 1  | 1  | 50 Ohm (Default)              |

|     |                               | 1     | 1        | 1 | 1        | 1                           | 1        | 1  | 0  | 35 Ohm                        |

| <3> | Driver Strength               | 1     | 1        | 1 | 1        | 1                           | 1        | 0  | 1  | 25 Ohm                        |

| \3> | configuration                 | 1     | 1        | 1 | 1        | 1                           | 1        | 0  | 0  | 18 Ohm                        |

|     |                               | Othe  | <u> </u> | ' | <u> </u> | '                           | '        | U  | 10 | Reserved                      |

|     |                               | 1     | 1        |   | Ι,,      |                             |          | ., |    |                               |

|     |                               | 1     | 0        | X | X        | X                           | X        | X  | X  | CRC Disabled (Default)        |

|     | CRC configuration             | 0     |          | X | X        | X                           | X        | X  | X  | 16-Byte CRC                   |

|     |                               | 0     | 1        | X | X        | X                           | X        | X  | X  | 32-Byte CRC                   |

|     |                               | 1     | 0        | X | X        | X                           | X        | X  | X  | 64-Byte CRC                   |

|     |                               | X     | X        | 1 | 1        | X                           | X        | X  | X  | ODT Disabled (Default)        |

|     | On die termination            | Х     | X        | 1 | 0        | X                           | X        | X  | X  | 150-Ohm ODT                   |

|     |                               | Х     | Х        | 0 | 1        | Х                           | Х        | Х  | Х  | 100-Ohm ODT                   |

| <4> |                               | Х     | Х        | 0 | 0        | X                           | Х        | Х  | Х  | 50-Ohm ODT                    |

|     | DLP configuration             | Х     | Х        | Х | Х        | 1                           | Х        | Х  | Х  | DLP Disabled (Default)        |

|     |                               | Х     | Х        | Х | Х        | 0                           | X        | Х  | Х  | DLP Enabled                   |

|     | Protection                    | Х     | Х        | Х | Х        | Х                           | 1        | Х  | Х  | BP Protection (Default)       |

|     | configuration                 | Х     | Х        | Х | Х        | Х                           | 0        | Х  | X  | WPS Protection <sup>(8)</sup> |

|     | ECC configuration             | Х     | Х        | Х | Х        | Х                           | Х        | Х  | 1  | ECC Enabled (Default)         |

|     |                               | Х     | Х        | Х | Х        | Х                           | Х        | Х  | 0  | ECC Disabled                  |

|     |                               | Othe  | 1        |   | T        |                             |          |    |    | Reserved                      |

|     | Beyond 128Mb                  | 1     | 1        | 1 | 1        | 1                           | 1        | 1  | 1  | 3-Byte Address (Default)      |

| <5> | addr configuration            | 1     | 1        | 1 | 1        | 1                           | 1        | 1  | 0  | 4-Byte Address                |

|     | 3                             | Othe  | rs       |   | 1        |                             |          | 1  |    | Reserved                      |

|     | Continuous Read               | 1     | 1        | 1 | 1        | 1                           | 1        | 1  | 1  | XIP Disabled (Default)        |

| <6> | configuration <sup>(9)</sup>  | 1     | 1        | 1 | 1        | 1                           | 1        | 1  | 0  | XIP Enabled                   |

|     | 3                             | Othe  | rs       |   | 1        |                             |          |    |    | Reserved                      |

|     |                               | 1     | 1        | 1 | 1        | 1                           | 1        | 1  | 1  | Wrap Disabled (Default)       |

|     | Wrap                          | 1     | 1        | 1 | 1        | 1                           | 1        | 1  | 0  | 64-Byte Wrap                  |

| <7> | configuration <sup>(10)</sup> | 1     | 1        | 1 | 1        | 1                           | 1        | 0  | 1  | 32-Byte Wrap                  |

|     | Comiguration                  | 1     | 1        | 1 | 1        | 1                           | 1        | 0  | 0  | 16-Byte Wrap                  |

|     |                               | Othe  | rs       |   | _        |                             |          |    |    | Reserved                      |

#### Notes:

- 1. The number of cycles must be set to accord with the clock frequency, which varies by the type of FAST READ command (See Supported Clock Frequencies table). Insufficient dummy clock cycles for the operating frequency causes the memory to read incorrect data.

- 2. 03H/13H: SPI 0 dummy; OPI&DTR N/A

- 3. 05H/70H/9EH/9FH: SPI 0dummy; OPI&DTR 8 dummy.

- 4. 3DH: SPI 0dummy; OPI&DTR 8 dummy.

- 5. 4BH/5AH/B5H/85H: SPI&OPI&DTR 8 dummy.

- 6. 0BH/0CH/8BH/7CH/48H: SPI 8 dummy; OPI&DTR dummy follow CONFIGURATION REGISTER<1> (initiation = 16 dummy)

- 7. CBH/CCH/FDH: SPI&OPI&DTR dummy follow CONFIGURATION REGISTER<1> (initiation = 16 dummy)

- 8. When WPS protection is enabled, the entire memory array is being protected after Power-up or Reset.

- 9. Only Octal I/O Fast Read (CBH/CCH) and DTR Octal I/O Fast Read (FDH) support Continuous Read.

- 10. Only Octal I/O Fast Read (CBH/CCH) and DTR Octal I/O Fast Read (FDH) support Wrap read.

- 11. This feature is available on special order. Please contact GigaDevice for details.

## 8.2 Volatile Configuration Register

Volatile Configuration Register bits temporarily set the device configuration after power-up or reset. All bits are erased (FFh) unless stated otherwise. This register is read from and written to using the READ VOLATILE CONFIGURATION REGISTER and the WRITE VOLATILE CONFIGURATION REGISTER commands, respectively. The commands use the main array address scheme; however, only the LSB is used to access different register settings to provide up to 256 Bytes of registers (See the table below for the details). A WRITE command to a reserved address will set the device to the default status of the corresponding Byte.

**Table 9 Volatile Configuration Register**

| Addr | Settings                                   | bit7  | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Description            |

|------|--------------------------------------------|-------|------|------|------|------|------|------|------|------------------------|

|      |                                            | 1     | 1    | 1    | 1    | 1    | 1    | 1    | 1    | SPI with DQS (Default) |

|      |                                            | 1     | 1    | 0    | 1    | 1    | 1    | 1    | 1    | SPI W/O DQS            |

|      |                                            | 1     | 1    | 1    | 0    | 0    | 1    | 1    | 1    | Octal DTR with DQS     |

| <0>  | I/O mode                                   | 1     | 1    | 0    | 0    | 0    | 1    | 1    | 1    | Octal DTR W/O DQS      |

|      |                                            | 1     | 0    | 1    | 1    | 0    | 1    | 1    | 1    | Octal STR with DQS     |

|      |                                            | 1     | 0    | 0    | 1    | 0    | 1    | 1    | 1    | Octal STR W/O DQS      |

|      |                                            | Other | 'S   |      |      |      |      |      |      | Reserved               |

|      |                                            | 0     | 0    | 0    | 0    | 0    | 0    | 1    | 1    | 3 Dummy                |

|      | Dummy avala                                | 0     | 0    | 0    | 0    | 0    | 1    | 0    | 0    | 4 Dummy                |

| <1>  | Dummy cycle configuration <sup>(6-7)</sup> |       |      |      |      |      |      |      |      | 05~1E: 5~30 Dummy      |

|      | Configuration                              | •••   |      | •••  |      |      |      |      |      | (Default=10h)          |

|      |                                            | Other | 'S   |      |      |      |      |      |      | Reserved               |

|      |                                            | 1     | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 50 Ohm (Default)       |

|      | Driver Strongth                            | 1     | 1    | 1    | 1    | 1    | 1    | 1    | 0    | 35 Ohm                 |

| <3>  | Driver Strength configuration              | 1     | 1    | 1    | 1    | 1    | 1    | 0    | 1    | 25 Ohm                 |

|      |                                            | 1     | 1    | 1    | 1    | 1    | 1    | 0    | 0    | 18 Ohm                 |

|      |                                            | Other | s    |      |      |      |      |      |      | Reserved               |

# **Uniform Sector** GigaDevice Xccela™ Flash Memory

### **GD25LX256E**

| _   |                                 |      |    |   |   |          |   |   |   |                               |

|-----|---------------------------------|------|----|---|---|----------|---|---|---|-------------------------------|

|     | CRC configuration               | 1    | 1  | х | х | х        | х | х | х | CRC Disabled (Default)        |

|     |                                 | 1    | 0  | х | х | х        | х | х | х | 16-Byte CRC                   |

|     | CRC configuration               | 0    | 1  | х | х | х        | х | х | х | 32-Byte CRC                   |

|     |                                 | 0    | 0  | х | х | х        | х | х | х | 64-Byte CRC                   |

|     |                                 | х    | х  | 1 | 1 | х        | х | х | х | ODT Disabled (Default)        |

|     | On die termination              | Х    | х  | 1 | 0 | х        | х | х | х | 150-Ohm ODT                   |

|     | On the termination              | Х    | х  | 0 | 1 | х        | х | х | х | 100-Ohm ODT                   |

| <4> |                                 | Х    | х  | 0 | 0 | х        | х | х | х | 50-Ohm ODT                    |

|     | DLP configuration               | х    | х  | х | х | 1        | х | х | х | DLP Disabled (Default)        |

|     | DLP configuration               | Х    | х  | х | х | 0        | х | х | х | DLP Enabled                   |

|     | Protection                      | х    | х  | Х | х | х        | 1 | х | х | BP Protection (Default)       |

|     | configuration                   | Х    | х  | х | х | х        | 0 | х | х | WPS Protection <sup>(8)</sup> |

|     | ECC configuration               | х    | х  | х | х | х        | х | х | 1 | ECC Enabled (Default)         |

|     | ECC configuration               | Х    | х  | х | х | х        | х | х | 0 | ECC Disabled                  |

|     |                                 | Othe | rs |   |   | Reserved |   |   |   |                               |

|     | Doyand 120Mb                    | 1    | 1  | 1 | 1 | 1        | 1 | 1 | 1 | 3-Byte Address (Default)      |

| <5> | Beyond 128Mb addr configuration | 1    | 1  | 1 | 1 | 1        | 1 | 1 | 0 | 4-Byte Address                |

|     | addi comiguration               | Othe | rs |   |   |          |   |   |   | Reserved                      |

|     | Continuous Read                 | 1    | 1  | 1 | 1 | 1        | 1 | 1 | 1 | XIP Disabled (Default)        |

| <6> | configuration <sup>(9)</sup>    | 1    | 1  | 1 | 1 | 1        | 1 | 1 | 0 | XIP Enabled                   |

|     | Configuration                   | Othe | rs |   |   |          |   |   |   | Reserved                      |

|     |                                 | 1    | 1  | 1 | 1 | 1        | 1 | 1 | 1 | Wrap Disabled (Default)       |

|     | Wrap                            | 1    | 1  | 1 | 1 | 1        | 1 | 1 | 0 | 64-Byte Wrap                  |

| <7> | configuration <sup>(10)</sup>   | 1    | 1  | 1 | 1 | 1        | 1 | 0 | 1 | 32-Byte Wrap                  |

|     | Comiguration                    | 1    | 1  | 1 | 1 | 1        | 1 | 0 | 0 | 16-Byte Wrap                  |

|     |                                 | Othe | rs |   |   |          |   |   |   | Reserved                      |

|     |                                 |      |    |   |   |          |   |   |   |                               |

#### Notes:

- 1. The number of cycles must be set to accord with the clock frequency, which varies by the type of FAST READ command (See Supported Clock Frequencies table). Insufficient dummy clock cycles for the operating frequency causes the memory to read incorrect data.

- 2. 03H/13H: SPI 0 dummy; OPI&DTR N/A

- 3. 05H/70H/9EH/9FH: SPI 0dummy; OPI&DTR 8 dummy.

- 4. 3DH: SPI 0dummy; OPI&DTR 8 dummy.

- 5. 4BH/5AH/B5H/85H: SPI&OPI&DTR 8 dummy.

- 6. 0BH/0CH/8BH/7CH/48H: SPI 8 dummy; OPI&DTR dummy follow CONFIGURATION REGISTER<1> (initiation = 16 dummy)

- 7. CBH/CCH/FDH: SPI&OPI&DTR dummy follow CONFIGURATION REGISTER<1> (initiation = 16 dummy)

- 8. When WPS protection is enabled, the entire memory array is being protected after Power-up or Reset.

- 9. Only Octal I/O Fast Read (CBH/CCH) and DTR Octal I/O Fast Read (FDH) support Continuous Read.

- 10. Only Octal I/O Fast Read (CBH/CCH) and DTR Octal I/O Fast Read (FDH) support Wrap read.

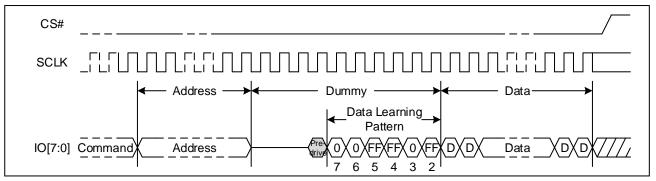

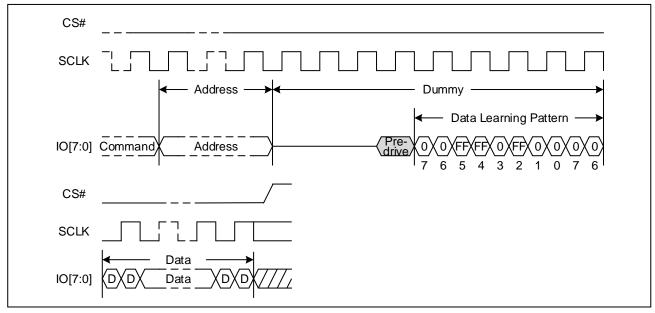

#### **DLP** bit

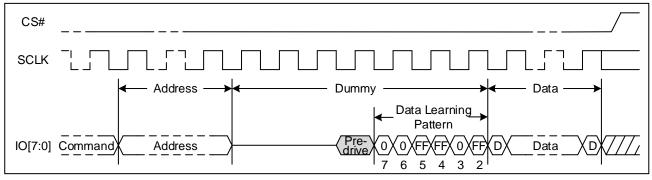

The DLP bit is Data Learning Pattern Enable bit, which is writable by B1/81H command. For Octal output, Octal I/O and Octal I/O DTR Fast Read commands, a pre-defined "Data Learning Pattern" can be used by the flash memory controller to determine the flash data output timing on 8 I/O pins. When DLP=0, from the falling edge of the fourth dummy clock, the flash will output "00110100" Data Learning Pattern sequence on each of the I/O or 8 I/O pins until data output. If the dummy clock is not enough for the output of the whole Data Learning Pattern, the last several bit of the Data Learning Pattern would be cut-off. During this period, controller can fine tune the data latching timing for each I/O pins to achieve optimum system performance. DLP=1 will disable the Data Learning Pattern output.

SCLK | Dummy Data Data | Document | Document

Figure 6. Data Learning Pattern Sequence Diagram (STR, Dummy Clock ≥ 12)

Note: 14 dummy cycle example

Figure 7. Data Learning Pattern Sequence Diagram (STR, Dummy Clock < 12)

Note: 10 dummy cycle example

Figure 8. Data Learning Pattern Sequence Diagram (DTR, Dummy Clock ≥ 8)

Note: 9 dummy cycle example

Figure 9. Data Learning Pattern Sequence Diagram (DTR, Dummy Clock < 8)

Note: 7 dummy cycle example

# 8.3 Supported Clock Frequencies

Table 10 Clock Frequencies of TFBGA-24 (5x5 Ball Array)

| Number of Dummy Clock | Octal I/O F | FAST READ | ODI DED |  |  |

|-----------------------|-------------|-----------|---------|--|--|

| Cycle                 | STR         | DTR       | OPI DTR |  |  |

| 4                     | 40          | 40        | 40      |  |  |

| 6                     | 84          | 84        | 84      |  |  |

| 8                     | 104         | 104       | 104     |  |  |

| 10                    | 133         | 133       | 133     |  |  |

| 12                    | 152         | 152       | 152     |  |  |

| 14                    | 166         | 166       | 166     |  |  |

| 16 and above          | 166         | 200       | 200     |  |  |

Table 11 Clock Frequencies of SOP16 (300mil)

| Number of Dummy Clock | Octal I/O F | Octal I/O FAST READ |         |  |  |  |  |  |

|-----------------------|-------------|---------------------|---------|--|--|--|--|--|

| Cycle                 | STR         | DTR                 | OPI DTR |  |  |  |  |  |

| 4                     | 40          | 40                  | 40      |  |  |  |  |  |

| 6                     | 84          | 84                  | 84      |  |  |  |  |  |

| 8                     | 104         | 104                 | 104     |  |  |  |  |  |

| 10                    | 133         | 133                 | 133     |  |  |  |  |  |

| 12                    | 152         | 152                 | 152     |  |  |  |  |  |

| 14 and above          | 166         | 166                 | 166     |  |  |  |  |  |

#### Note:

- 1. Values are guaranteed by characterization and not 100% tested in production

- 2. Dummy clock cycle listed above is recommended. Please contact GigaDevice for clock frequency of dummy clock cycle configuration out of the table above.

## 8.4 Data Sequence Wraps by Density

**Table 12 Sequence of Bytes during Wrap**

| Starting Address | 16-Byte Wrap     | 32-Byte Wrap     | 64-Byte Wrap   |

|------------------|------------------|------------------|----------------|

| 0                | 0-1-215-0-1      | 0-1-231-0-1      | 0-1-263-0-1    |

| 1                | 1-215-0-1-2      | 1-231-0-1-2      | 1-263-0-1-2    |

|                  |                  |                  |                |

| 15               | 15-0-1-2-315-0-1 | 15-16-1731-0-1   | 15-16-1763-0-1 |

|                  |                  |                  |                |

| 31               | -                | 31-0-1-2-331-0-1 | 31-32-3363-0-1 |

|                  |                  |                  |                |

| 63               | -                | -                | 63-0-163-0-1   |

#### 9 COMMAND DESCRIPTIONS

All commands, addresses and data are shifted in and out of the device, beginning with the most significant bit on the first rising edge of SCLK after CS# is driven low. Then, the one-Byte command code must be shifted in to the device, with most significant bit first on SI, and each bit is latched on the rising edges of SCLK.

Every command sequence starts with a one-Byte command code. Depending on the command, this might be followed by address Bytes, or by data Bytes, or by both or none. CS# must be driven high after the last bit of the command sequence has been completed. For the command of Read, Fast Read, Read Status Register or Release from Deep Power-Down, and Read Device ID, the shifted-in command sequence is followed by a data-out sequence. All read instruction can be completed after any bit of the data-out sequence is being shifted out, and then CS# must be driven high to return to deselected status.

For the command of Page Program, Sector Erase, Block Erase, Chip Erase, Write Status Register, Write Enable, Write Disable or Deep Power-Down command, CS# must be driven high exactly at a Byte boundary, otherwise the command is rejected, and is not executed. That is CS# must be driven high when the number of clock pulses after CS# being driven low is an exact multiple of eight. For Page Program, if at any time the input Byte is not a full Byte, nothing will happen and WEL will not be reset.

Table 13 Commands (Extended/Octal SPI)

|                                          |          | Extended SPI      |                          | Octal SPI                     |                               |                          |                    |               |

|------------------------------------------|----------|-------------------|--------------------------|-------------------------------|-------------------------------|--------------------------|--------------------|---------------|

| Command name                             | Code     | CMD-Addr-<br>Data | Dummy<br>Clock<br>Cycles | CMD- Addr-<br>Data<br>(S-D-D) | CMD- Addr-<br>Data<br>(S-S-S) | Dummy<br>Clock<br>Cycles | Addr.<br>Bytes     | Data<br>Bytes |

| Software Reset Op                        | erations |                   |                          |                               |                               |                          |                    |               |

| Enable Reset                             | 66h      | 1-0-0             | 0                        | 8-0-0                         | 8-0-0                         | 0                        | 0                  | 0             |

| Reset                                    | 99h      | 1-0-0             | 0                        | 8-0-0                         | 8-0-0                         | 0                        | 0                  | 0             |

| Read ID Operation                        | S        |                   |                          |                               |                               |                          |                    |               |

| Read<br>Identification                   | 9Eh/9Fh  | 1-0-(1)           | 0                        | 8-0-(8)                       | 8-0-(8)                       | 8                        | 0                  | 1 to 4        |

| Read Serial Flash Discoverable Parameter | 5Ah      | 1-1-(1)           | 8                        | 8-8-(8)                       | 8-8-(8)                       | 8                        | 3 (STR)<br>4 (DTR) | 1 to ∞        |

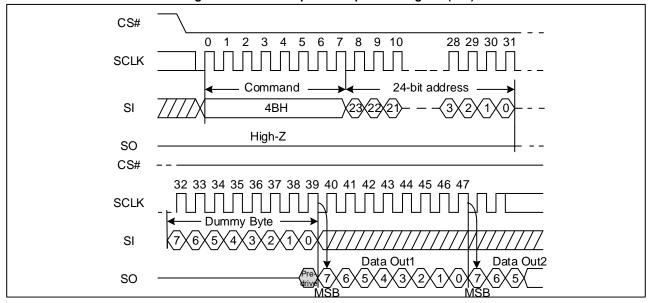

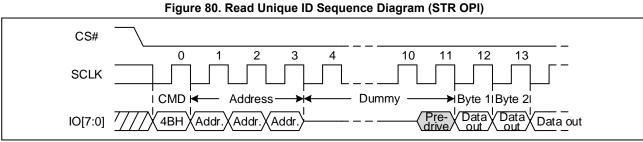

| Read Unique ID                           | 4Bh      | 1-1-(1)           | 8                        | 8-8-(8)                       | 8-8-(8)                       | 8                        | 3(4)               | 1 to ∞        |

| Read Memory Ope                          | rations  |                   |                          |                               |                               |                          |                    |               |

| Read Data Bytes                          | 03h      | 1-1-(1)           | 0                        | _                             | _                             | _                        | 3(4)               | 1 to ∞        |

| Read Data Bytes<br>at Higher Speed       | 0Bh      | 1-1-(1)           | 8                        | 8-8-(8)                       | 8-8-(8)                       | 16                       | 3(4)               | 1 to ∞        |

| Octal Output Fast<br>Read                | 8Bh      | 1-1-(8)           | 8                        | 8-8-(8)                       | 8-8-(8)                       | 16                       | 3(4)               | 1 to ∞        |

| Octal I/O Fast<br>Read                   | CBh      | 1-8-(8)           | 16                       | 8-8-(8)                       | 8-8-(8)                       | 16                       | 3(4)               | 1 to ∞        |

# Uniform Sector GigaDevice Xccela™ Flash Memory

## **GD25LX256E**

| Read Memory Ope    | rations wi | th 4-Byte Add | ress |         |             |         |         |         |   |   |

|--------------------|------------|---------------|------|---------|-------------|---------|---------|---------|---|---|

| 4-Byte Read Data   | 13h        | 1-1-(1)       | 0    |         |             |         | 4       | 1 to ∞  |   |   |

| Bytes              | 1311       | 1-1-(1)       | O    | _       | _           |         | 4       | 1 10 30 |   |   |

| 4-Byte Read Data   |            |               |      |         |             |         |         |         |   |   |

| Bytes at Higher    | 0Ch        | 1-1-(1)       | 8    | 8-8-(8) | 8-8-(8)     | 16      | 4       | 1 to ∞  |   |   |

| Speed              |            |               |      |         |             |         |         |         |   |   |

| 4-Byte Octal       | 7Ch        | 1 1 (0)       | 8    | 0 0 (0) | 0 0 (0)     | 16      | 4       | 1 to ∞  |   |   |

| Output Fast Read   | 7011       | 1-1-(8)       | 0    | 8-8-(8) | 8-8-(8)     | 10      | 4       | 110 0   |   |   |

| 4-Byte Octal I/O   | CCh        | 1.0.(0)       | 16   | 0.0.(0) | 0.0.(0)     | 16      | 4       | 1 to ∞  |   |   |

| Fast Read          | CCh        | 1-8-(8)       | 10   | 8-8-(8) | 8-8-(8)     | 16      | 4       | 1 10 0  |   |   |

| 4-Byte Octal I/O   | ED!        | 4.0-1.(0-1)   | 40   | 0.0.(0) | 0 0 1 (0 1) | 40      | 4       | 4.4     |   |   |

| DTR Fast Read      | FDh        | 1-8d-(8d)     | 16   | 8-8-(8) | 8-8d-(8d)   | 16      | 4       | 1 to ∞  |   |   |

| Write Operations   |            |               |      |         |             |         |         |         |   |   |

| Write Enable       | 06h        | 1-0-0         | 0    | 8-0-0   | 8-0-0       | 0       | 0       | 0       |   |   |

| Write Disable      | 04h        | 1-0-0         | 0    | 8-0-0   | 8-0-0       | 0       | 0       | 0       |   |   |

| Read Register Ope  | erations   |               |      |         |             |         |         |         |   |   |

| Read Status        | 051-       | 4.0 (4)       | 0    | 0.0.(0) | 0.0 (0)     | 0       | 0       | 4.4-    |   |   |

| Register           | 05h        | 1-0-(1)       | 0    | 8-0-(8) | 8-0-(8)     | 8       | 0       | 1 to ∝  |   |   |

| Read Flag Status   | 701        | 4.0 (4)       | •    | 0.0.(0) | 0.0 (0)     |         |         | 4.      |   |   |

| Register           | 70h        | 1-0-(1)       | 0    | 8-0-(8) | 8-0-(8)     | 8       | 0       | 1 to ∝  |   |   |

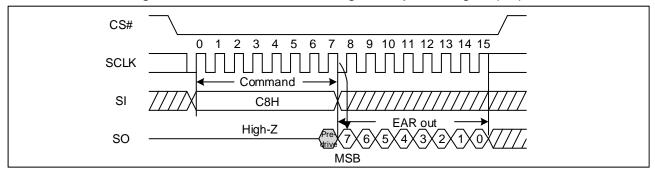

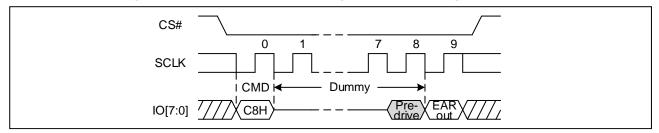

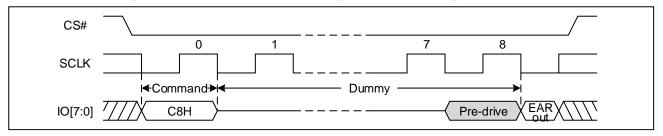

| Read Extended      | Coh        | Cob           | C8h  | 4.0 (4) | 0           | 9 ( (9) | 0 0 (0) | 8       | 0 | 1 |

| Addr. Register     | Con        | 1-0-(1)       | U    | 8-0-(8) | 8-0-(8)     | 8       | 0       | 1       |   |   |

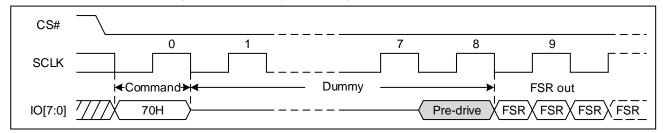

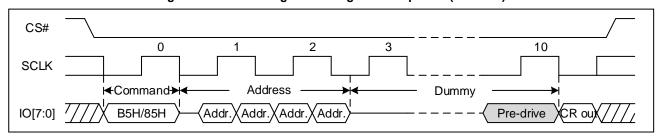

| Read Nonvolatile   |            |               |      |         |             |         |         |         |   |   |

| Configuration      | B5h        | 1-1-(1)       | 8    | 8-8-(8) | 8-8-(8)     | 8       | 3(4)    | 1       |   |   |

| Register           |            |               |      |         |             |         |         |         |   |   |

| Read Volatile      |            |               |      |         |             |         |         |         |   |   |

| Configuration      | 85h        | 1-1-(1)       | 8    | 8-8-(8) | 8-8-(8)     | 8       | 3(4)    | 1       |   |   |

| Register           |            |               |      |         |             |         |         |         |   |   |

| Write Register Ope | erations   |               |      |         |             |         |         |         |   |   |

| Write Status       | 01h        | 1-0-1         | 0    | 8-0-8   | 8-0-8       | 0       | 0       | 1       |   |   |

| Register           | 0111       | 1-0-1         | U    | 0-0-0   | 0-0-0       |         |         |         |   |   |

| Write Extended     | C5h        | 1-0-1         | 0    | 8-0-8   | 8-0-8       | 0       | 0       | 1       |   |   |

| Addr. Register     | Con        | 1-0-1         | U    | 0-0-6   | 0-0-0       | U       |         |         |   |   |

| Write Enable for   |            |               |      |         |             |         |         |         |   |   |

| Volatile Status    | 50h        | 1-0-0         | 0    | 8-0-0   | 8-0-0       | 0       | 0       | 0       |   |   |

| Register           |            |               |      |         |             |         |         |         |   |   |

| Clear Flag Status  | 2011       | 4.0.0         | 0    | 0.00    | 0.00        | 0       | 0       | _       |   |   |

| Register           | 30H        | 1-0-0         | 0    | 8-0-0   | 8-0-0       | 0       | 0       | 0       |   |   |

| Write Nonvolatile  |            |               |      |         |             |         |         |         |   |   |

| Configuration      | B1h        | 1-1-1         | 0    | 8-8-8   | 8-8-8       | 0       | 3(4)    | 1       |   |   |

| Register           |            |               |      |         |             |         |         |         |   |   |

# Uniform Sector GigaDevice Xccela<sup>™</sup> Flash Memory

# GD25LX256E

| Write Volatile                        |               |                |   |         |         |    |      |             |

|---------------------------------------|---------------|----------------|---|---------|---------|----|------|-------------|

| Configuration                         | 81h           | 1-1-1          | 0 | 8-8-8   | 8-8-8   | 0  | 3(4) | 1           |

| Register                              | 0111          | 1-1-1          | 0 | 0-0-0   | 0-0-0   | U  | 3(4) | '           |

| Program Operation                     | 25            |                |   |         |         |    |      |             |

| Frogram Operation                     |               |                |   |         |         |    |      | 1 to        |

| Page Program                          | 02h           | 1-1-1          | 0 | 8-8-8   | 8-8-8   | 0  | 3(4) | 256         |

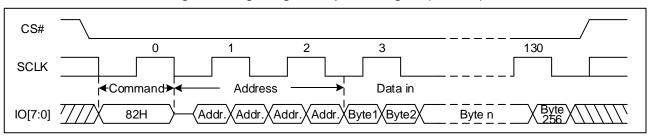

| Octal Page<br>Program                 | 82h           | 1-1-8          | 0 | 8-8-8   | 8-8-8   | 0  | 3(4) | 1 to<br>256 |

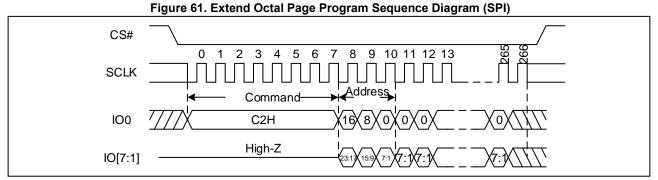

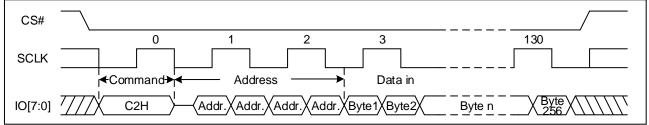

| Extended Octal Page Program           | C2h           | 1-8-8          | 0 | 8-8-8   | 8-8-8   | 0  | 3(4) | 1 to 256    |

| Program Operation                     | os with 4-E   | Ryto Addross   |   |         |         |    |      | 230         |

| 4-Byte Page                           | 115 WILLI 4-E | yie Audress    |   |         |         |    |      | 1 to        |

| Program                               | 12h           | 1-1-1          | 0 | 8-8-8   | 8-8-8   | 0  | 4    | 256         |

| 4-Byte Octal Page<br>Program          | 84h           | 1-1-8          | 0 | 8-8-8   | 8-8-8   | 0  | 4    | 1 to<br>256 |

| 4-Byte Extended Octal Page Program    | 8Eh           | 1-8-8          | 0 | 8-8-8   | 8-8-8   | 0  | 4    | 1 to<br>256 |

| <b>Erase Operations</b>               |               |                |   |         |         |    |      | _           |

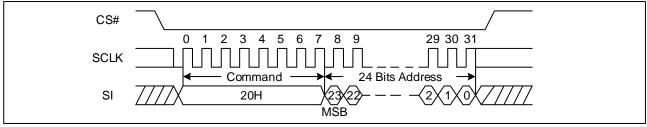

| Sector Erase                          | 20h           | 1-1-0          | 0 | 8-8-0   | 8-8-0   | 0  | 3(4) | 0           |

| 32KB Block Erase                      | 52h           | 1-1-0          | 0 | 8-8-0   | 8-8-0   | 0  | 3(4) | 0           |

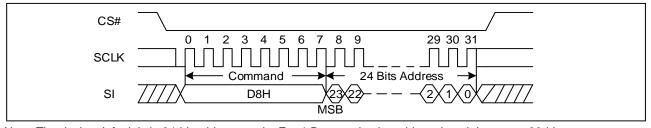

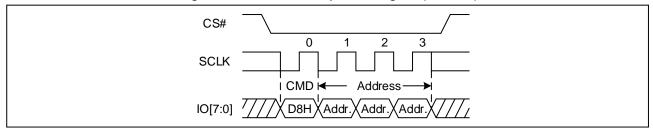

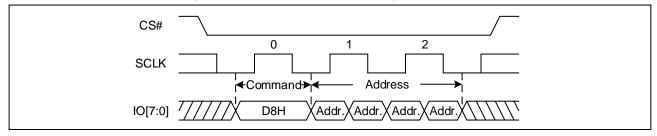

| 64KB Block Erase                      | D8h           | 1-1-0          | 0 | 8-8-0   | 8-8-0   | 0  | 3(4) | 0           |

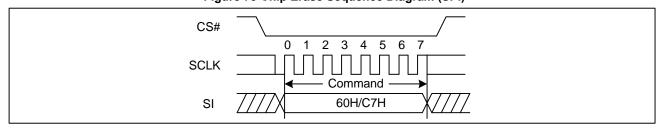

| Chip Erase                            | C7h/60<br>h   | 1-0-0          | 0 | 8-0-0   | 8-0-0   | 0  | 0    | 0           |

| Erase Operations                      | with 4-Byte   | e Address      |   |         |         |    |      |             |

| 4-Byte Sector<br>Erase                | 21h           | 1-1-0          | 0 | 8-8-0   | 8-8-0   | 0  | 4    | 0           |

| 4-Byte 32KB<br>Block Erase            | 5Ch           | 1-1-0          | 0 | 8-8-0   | 8-8-0   | 0  | 4    | 0           |

| 4-Byte 64KB<br>Block Erase            | DCh           | 1-1-0          | 0 | 8-8-0   | 8-8-0   | 0  | 4    | 0           |

| Suspend/Resume                        | Operation:    | <br>S          |   |         |         |    |      |             |

| Program/Erase<br>Suspend              | 75h           | 1-0-0          | 0 | 8-0-0   | 8-0-0   | 0  | 0    | 0           |

| Program/Erase Resume                  | 7Ah           | 1-0-0          | 0 | 8-0-0   | 8-0-0   | 0  | 0    | 0           |

| One-Time Programmable(OTP) Operations |               |                |   |         |         |    |      |             |

| Read Security                         |               | . , Operations |   |         |         |    |      |             |

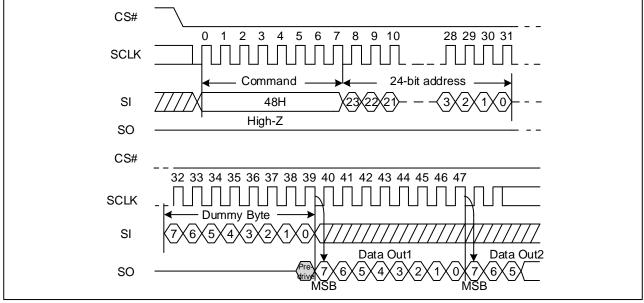

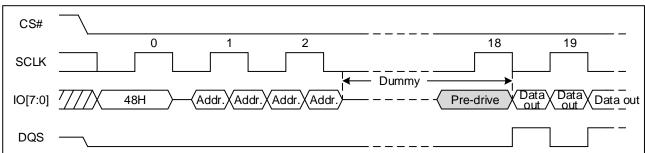

| Registers                             | 48h           | 1-1-(1)        | 8 | 8-8-(8) | 8-8-(8) | 16 | 3(4) | 1 to ∞      |

| Program Security<br>Registers         | 42h           | 1-1-1          | 0 | 8-8-8   | 8-8-8   | 0  | 3(4) | 1 to<br>256 |

| Erase Security Registers              | 44h           | 1-1-0          | 0 | 8-8-0   | 8-8-0   | 0  | 3(4) | 0           |

| - 3                                   | 1             | l              | l |         |         |    |      | l           |

# **Uniform Sector** GigaDevice Xccela<sup>™</sup> Flash Memory

## **GD25LX256E**

| 4-ByteAddress Mo  | 4-ByteAddress Mode Operations |            |   |         |         |   |      |   |

|-------------------|-------------------------------|------------|---|---------|---------|---|------|---|

| Enable 4-Byte     | B7h                           | 1-0-0      | 0 | 8-0-0   | 8-0-0   | 0 | 0    | 0 |

| Address Mode      | Dill                          | 1-0-0      | O | 0-0-0   | 0-0-0   | O | U    | 0 |

| Disable 4-Byte    | E9h                           | 1-0-0      | 0 | 8-0-0   | 8-0-0   | 0 | 0    | 0 |

| Address Mode      | L311                          | 1-0-0      | U | 0-0-0   | 0-0-0   | U | 0    |   |

| Deep Power-Down   | Operation                     | ıs         |   |         |         |   |      |   |

| Deep Power-       | B9h                           | 1-0-0      | 0 | 8-0-0   | 8-0-0   | 0 | 0    | 0 |

| Down              | וופּם                         | 1-0-0      | O | 0-0-0   | 0-0-0   | O | U    | 0 |

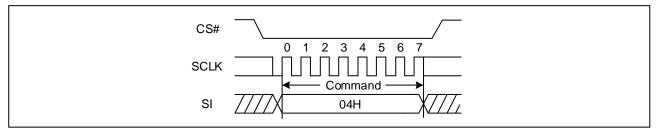

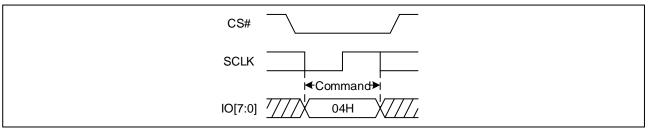

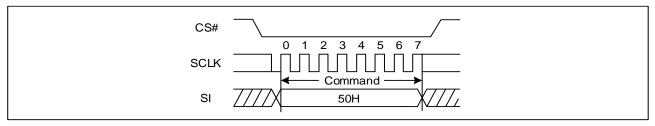

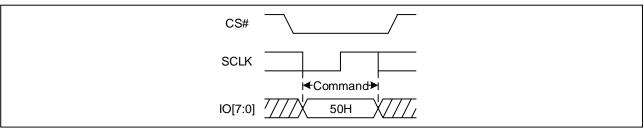

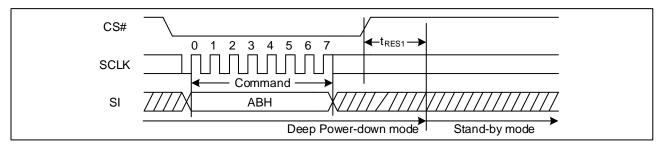

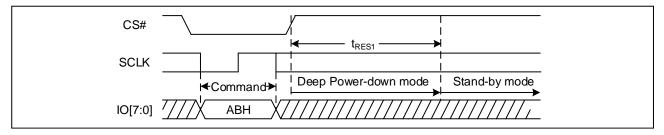

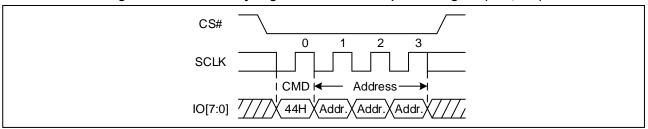

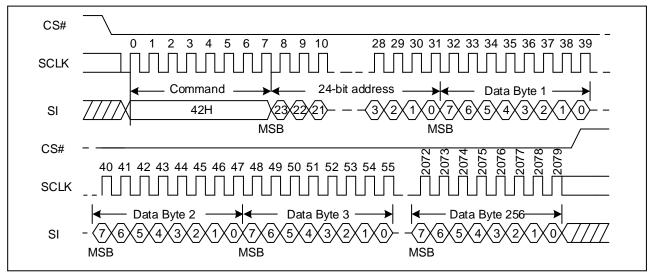

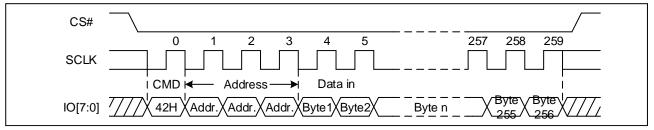

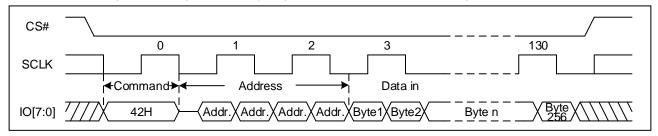

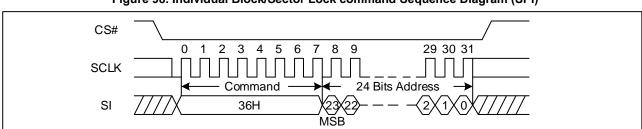

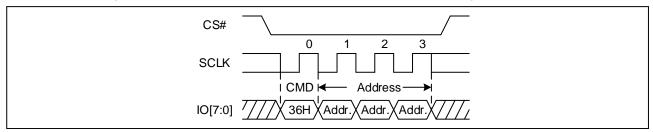

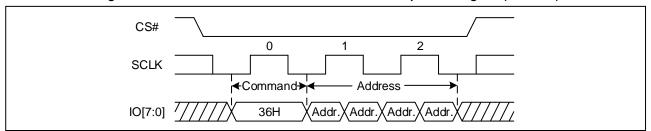

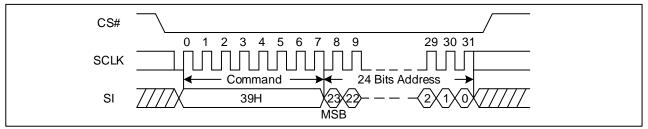

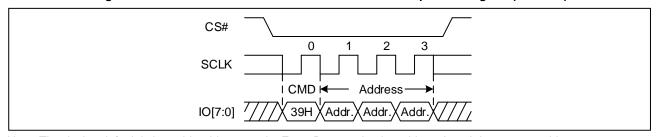

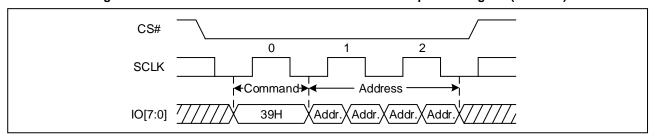

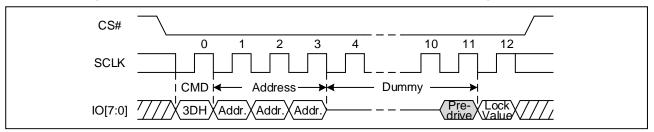

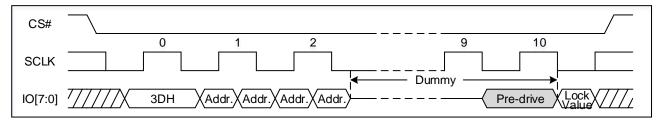

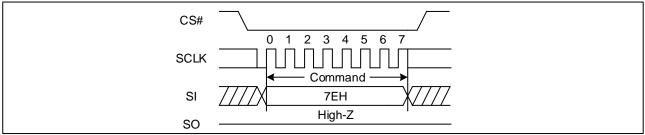

| Release From      |                               |            |   |         |         |   |      |   |