# GD9Fx1GxF3A DATASHEET

1G-bit 2K+64BPageSize

DS-GD9Fx1GxF3A-Rev1.8 1 February 2023

# Contents

| 1. | FEATURES                                                          | 4  |

|----|-------------------------------------------------------------------|----|

| 2. | GENERAL DESCRIPTION                                               | 5  |

|    | 2.1 PRODUCT LIST                                                  | 5  |

| 3. | PACKAGE                                                           | 6  |

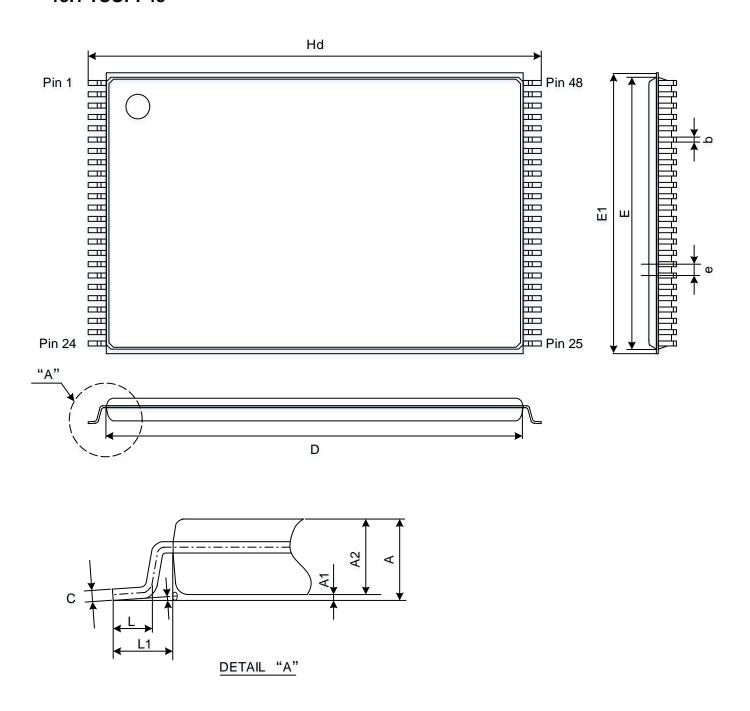

|    | 3.1 TSOPI-48                                                      | 6  |

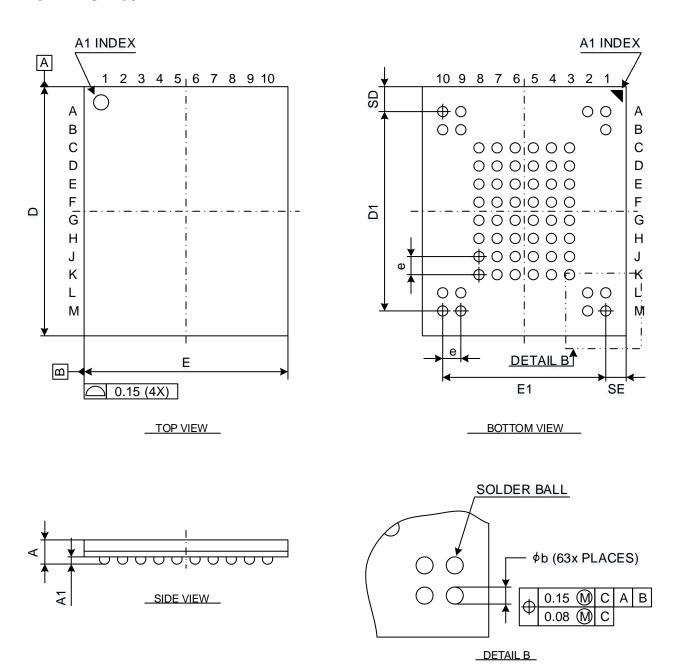

|    | 3.2 FBGA-63                                                       |    |

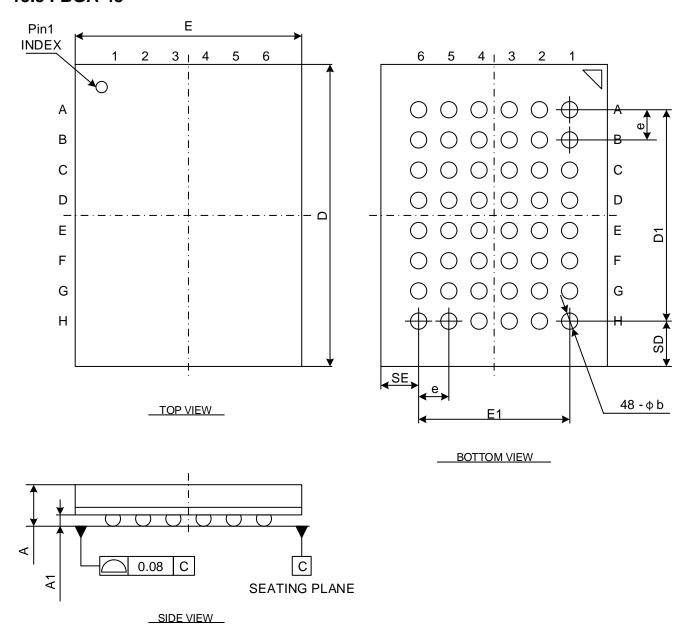

|    | 3.3 FBGA-48                                                       |    |

| 4. | BLOCK DIAGRAM                                                     | 8  |

|    | 4.1 PIN DESCRIPTION                                               | 9  |

| 5. | ARRAY ORGANIZATION                                                | 10 |

|    | 5.1 Addressing (X8)                                               | 10 |

|    | 5.2 Addressing (X16)                                              |    |

| ,  | 5.3 FACTORY DEFECT MAPPING                                        | 11 |

|    | 5.3.1. Device Requirements                                        | 11 |

|    | 5.3.2. Host Requirements                                          | 12 |

| 6. | COMMAND SET                                                       | 13 |

| 7. | BUS OPERATION                                                     | 14 |

|    | 7.1 COMMAND INPUT CYCLE                                           | 15 |

|    | 7.2 ADDRESS INPUT CYCLE                                           | 15 |

|    | 7.3 DATA INPUT CYCLE                                              | 16 |

|    | 7.4 DATA OUTPUT CYCLE                                             | 17 |

|    | 7.5 Write Protect                                                 | 18 |

| 8. | OPERATION DESCRIPTION                                             | 19 |

|    | 8.1 PAGE READ OPERATION                                           | 19 |

|    | 8.1.1 Common Page Read (00H-30H)                                  | 19 |

|    | 8.1.2 Random Data Output (05H-E0H)                                | 20 |

|    | 8.1.3 Cache Read Operation (31H/3FH)                              | 20 |

|    | 8.2 Page Program Operation                                        | 22 |

|    | 8.2.1 Common Page Program (80H-10H)                               | 22 |

|    | 8.2.2 Page Program Operation with Random Data Input (85H-10H)     | 23 |

|    | 8.2.3 Page Re-program (8BH-10H)                                   | 23 |

|    | 8.2.4 Cache Program Operation (80H-15H)                           | 24 |

|    | 8.2.5 Copy-Back Program with Random Data Input (00H-35H-85H-10H ) | 26 |

|    | 8.3 BLOCK ERASE OPERATION (60H-D0H)                               | 27 |

|    | 8.4 RESET (FFH)                                                   | 28 |

|    | 8.5 READ DEVICE INFORMATION                                       | 29 |

|    | 8.5.1 Read ID and ONFI Signature (90H)                            | 29 |

|    | 8.5.2 Read Unique ID (EDH)                                        | 33 |

| 8    | 8.5.3 Read Parameter Page (ECH)           | 34 |

|------|-------------------------------------------|----|

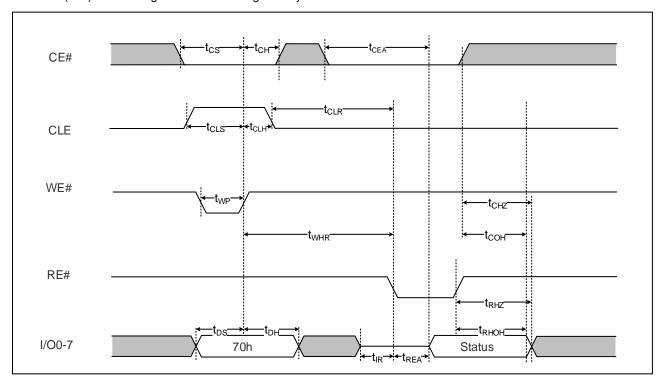

| 8.6  | S READ STATUS (70H)                       | 39 |

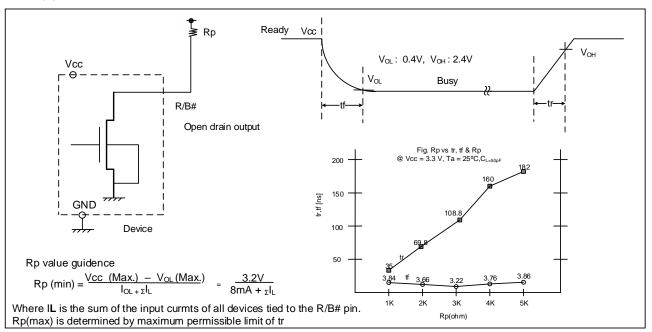

| 8.7  | 7 READY/BUSY# (R/B#)                      | 41 |

| 8.8  | B DATA PROTECTION & POWER ON/OFF SEQUENCE | 42 |

| 9. / | ABSOLUTE MAXIMUM RATINGS                  | 43 |

| 10.  | VALID BLOCKS                              | 44 |

| 11.  | DC CHARACTERISTICS                        | 45 |

| 12.  | AC CHARACTERISTICS                        | 46 |

| 12.  | .1 Test Condition                         | 46 |

| 12.  | .2 CAPACITANCE (TA=25°C, F=1.0MHz)        | 46 |

|      | .3 AC TIMING CHARACTERISTICS              |    |

| 12.  | .4 PERFORMANCE CHARACTERISTICS            | 48 |

| 13.  | PACKAGE INFORMATION                       | 49 |

| 13.  | .1 TSOPI-48                               | 49 |

| 13.  | .2 FBGA-63                                | 51 |

| 13.  | .3 FBGA-48                                | 53 |

| 14.  | PART NUMBERING INFORMATION                | 54 |

| 15.  | REVISION HISTORY                          | 55 |

## 1. FEATURES

- ◆ Single level cell technology

- ◆ ONFI 1.0 Compatible

- ◆ Power Supply Voltage

- VCC= 1.7 ~ 1.95v (GD9FS)

- VCC = 2.7 ~ 3.6v (GD9FU)

- ◆ Memory Cell Organization

- Page size:

X8: 2K + 64bytes

X16: 1K + 32words

- Block size:

X8: 128K + 4K bytes

X16: 64K + 2K words

- Plane size: 1024 blocks

- Device size: 1024 blocks

- ◆ Page Read / Program time

- Random Read Time (tR): 25us Max.

- Sequential Access Time

- 3.3v Device: 25ns Min.

- 1.8v Device:45ns Min.

- Page Program(tPROG): 300us Typ.

- ◆ Block Erase

- Block Erase Time(tBERS): 3ms Typ.

- ◆ Number of Valid Blocks

- Min 1004 blocks

- Max 1024 blocks

◆ Operating Current

- Read(25ns cycle): 15mA

- Program(Typ): 15mA

- Erase(Typ): 15mA

- Standby(Max):50uA (CMOS)

Reliability

- P/E cycles with ECC: 100K

- Data retention: 10 Years

- ◆ ECC Requirement

- 4bit/512 bytes

- ◆ Operating Temperature

- Industrial: -40C ~ 85C

- Industrial: -40C ~ 105C

- ◆ Chip Enable Don't Care Option

- ◆ Security

- OTP area

- Non-volatile protection

- ◆ Package

- TSOPI 48 (12mm x 20mm)

- FBGA63 (9mm x 11mm)

- FBGA48 (6mm x 8mm)

## 2. GENERAL DESCRIPTION

GigaDevice GD9Fx1G8F3A and GD9Fx1G6F3A are 1Gbit with spare 32Mbit capacity. A program operation can be performed in typical tPROG on the 2112-byte page and an erase operation can be performed in typical tBERS on a 128K+4K-bytes block. Data in the data page can be read out at tRC cycle time per byte. The I/O pins serve as the ports for address and data input/output as well as command input. The on-chip write controller automates all program and erase functions including pulse repetition, where required, and internal verification and margining of data. GD9Fx1G8F3A and GD9Fx1G6F3A's provide extended reliability of 100K program/erase cycles with ECC (Error Correcting Code).

#### 2.1 Product List

| PART NUMBER   | ORGANIZATION | VCC RANGE    | PACKAGE    | Temperature               |

|---------------|--------------|--------------|------------|---------------------------|

| GD9FU1G8F3AMG | 128M x 8bit  | 2.7v ~ 3.6v  | TSOP(I)-48 | Industrial -40~85/-40~105 |

| GD9FU1G6F3AMG | 64M x 16bit  | 2.7v ~ 3.6v  | TSOP(I)-48 | Industrial -40~85/-40~105 |

| GD9FU1G8F3ALG | 128M x 8bit  | 2.7v ~ 3.6v  | FBGA-63    | Industrial -40~85/-40~105 |

| GD9FU1G6F3ALG | 64M x 16bit  | 2.7v ~ 3.6v  | FBGA-63    | Industrial -40~85/-40~105 |

| GD9FU1G8F3ADG | 128M x 8bit  | 2.7v ~ 3.6v  | FBGA-48    | Industrial -40~85/-40~105 |

| GD9FU1G6F3ADG | 64M x 16bit  | 2.7v ~ 3.6v  | FBGA-48    | Industrial -40~85/-40~105 |

| GD9FS1G8F3AMG | 128M x 8bit  | 1.7v ~ 1.95v | TSOP(I)-48 | Industrial -40~85/-40~105 |

| GD9FS1G6F3AMG | 64M x 16bit  | 1.7v ~ 1.95v | TSOP(I)-48 | Industrial -40~85/-40~105 |

| GD9FS1G8F3ALG | 128M x 8bit  | 1.7v ~ 1.95v | FBGA-63    | Industrial -40~85/-40~105 |

| GD9FS1G6F3ALG | 64M x 16bit  | 1.7v ~ 1.95v | FBGA-63    | Industrial -40~85/-40~105 |

| GD9FS1G8F3ADG | 128M x 8bit  | 1.7v ~ 1.95v | FBGA-48    | Industrial -40~85/-40~105 |

| GD9FS1G6F3ADG | 64M x 16bit  | 1.7v ~ 1.95v | FBGA-48    | Industrial -40~85/-40~105 |

## 3. PACKAGE

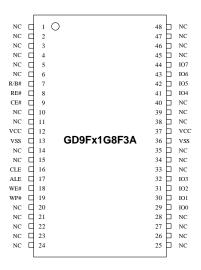

#### 3.1 TSOPI-48

Figure 1-a: GD9Fx1G8F3AMG package figures

Figure 1-b: GD9Fx1G6F3AMG package figures

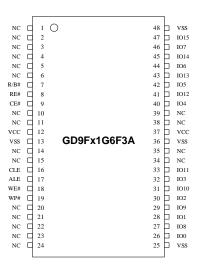

## 3.2 FBGA-63

Figure 2\_a: 63-FBGA x16 device ball location figures

Figure 2\_b: 63-FBGA x8 device ball location figures

#### Note:

1. Ball G4 can be either connected to VCC or NC.

DS-GD9Fx1GxF3A-Rev1.8 6 February 2023

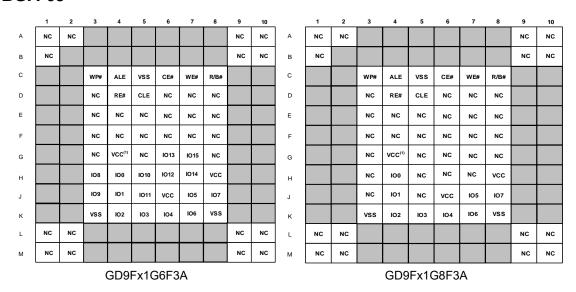

# 3.3 FBGA-48

|   |     | 2   | 3    | 4    | 3    | O    |

|---|-----|-----|------|------|------|------|

| Α | WP# | ALE | VSS  | CE#  | WE#  | R/B# |

| В | NC  | RE# | CLE  | NC   | NC   | NC   |

| С | NC  | NC  | NC   | NC   | NC   | NC   |

| D | NC  | NC  | NC   | NC   | NC   | NC   |

| E | NC  | NC  | NC   | IO13 | IO15 | NC   |

| F | IO8 | IO0 | IO10 | IO12 | IO14 | vcc  |

| G | 109 | IO1 | IO11 | VCC  | IO5  | 107  |

| н | vss | IO2 | IO3  | 104  | IO6  | vss  |

Figure 3\_a: 48-FBGA x16 device ball location figures

|   | 1   | 2   | 3   | 4   | 5   | ь    |

|---|-----|-----|-----|-----|-----|------|

| Α | WP# | ALE | VSS | CE# | WE# | R/B# |

| В | NC  | RE# | CLE | NC  | NC  | NC   |

| С | NC  | NC  | NC  | NC  | NC  | NC   |

| D | NC  | NC  | NC  | NC  | NC  | NC   |

| E | NC  | NC  | NC  | NC  | NC  | NC   |

| F | NC  | IO0 | NC  | NC  | NC  | vcc  |

| G | NC  | IO1 | NC  | VCC | IO5 | 107  |

| Н | VSS | IO2 | IO3 | IO4 | 106 | VSS  |

Figure 3\_b: 48-FBGA x8 device ball location figures

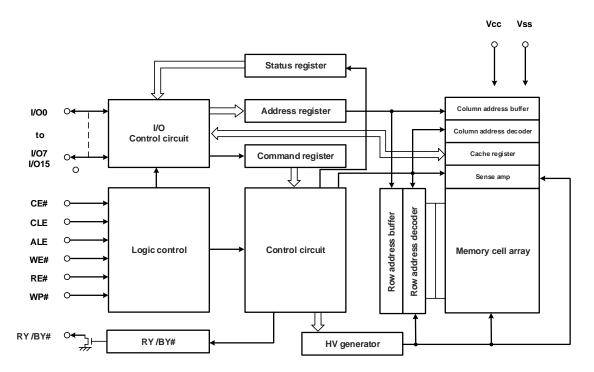

# 4. BLOCK DIAGRAM

Figure 4: Block Diagram figures

# **4.1 PIN DESCRIPTION**

| Signal Name      | Input/ Output | Description                                                                          |  |  |  |

|------------------|---------------|--------------------------------------------------------------------------------------|--|--|--|

| <b>R/B# O</b> Re |               | Ready/Busy: Open drain output to indicate the target status, low to indicate that    |  |  |  |

|                  |               | one or more operations are in progress.                                              |  |  |  |

| RE#              | I             | Read Enable: Enables serial data output, active low.                                 |  |  |  |

| CE#              | I             | Chip Enable: When high and the target is in the ready state, the target goes into    |  |  |  |

|                  |               | a low-power standby state. When low, the target is selected.                         |  |  |  |

| CLE              | I             | Command Latch Enable: Enable signal to load a command into the target on the         |  |  |  |

|                  |               | rising edge of WE#, active high.                                                     |  |  |  |

| ALE              | 1             | Address Latch Enable: Enable signal to load an address into the target on the        |  |  |  |

|                  |               | rising edge of WE#, active high.                                                     |  |  |  |

| WE#              | 1             | Write Enable: Data, Commands, and Addresses are latched on the rising edge           |  |  |  |

|                  |               | of WE#.                                                                              |  |  |  |

| WP#              | 1             | Write Protect: Low to disable Flash array program and erase operations.              |  |  |  |

| 100 ~ 107        | I/O           | I/O Port, bits 0-7: 8-bit wide bidirectional port for transferring address, command, |  |  |  |

|                  |               | and data to and from the device.                                                     |  |  |  |

| IO8 ~ IO15       | I/O           | I/O Port, bits 8-15: Upper 8 bits for the 16-bit wide bidirectional port used to     |  |  |  |

|                  |               | transfer data to and from the device.                                                |  |  |  |

| VCC              | I             | Power: Power supply to the device.                                                   |  |  |  |

| vss              | I             | Ground: Power supply ground.                                                         |  |  |  |

| NC               | -             | No Connection: Lead is not internally connected.                                     |  |  |  |

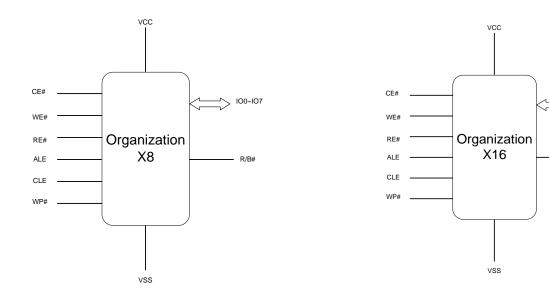

Figure 5\_a: GD9Fx1G8F3A figures

Figure 5\_b: GD9Fx1G6F3A figures

R/B#

## 5. ARRAY ORGANIZATION

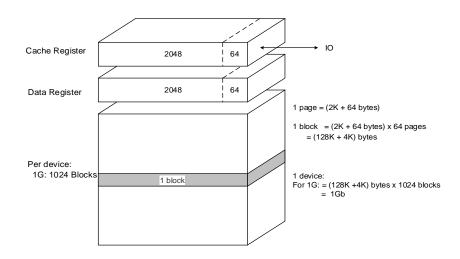

| Each device has | Each block has | Each page has |        |

|-----------------|----------------|---------------|--------|

| 1G              |                |               |        |

| 128M+4M         | 128K+4K        | 2K+64         | bytes  |

| 1024 x 64       | 64             | -             | pages  |

| 1024            | -              | -             | blocks |

Figure 6: Array Organization figures

# 5.1 Addressing (X8)

| Bus Cycle             | 100 | IO1 | IO2 | IO3 | 104 | IO5 | 106 | 107 |

|-----------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| 1st Cycle             | A0  | A1  | A2  | A3  | A4  | A5  | A6  | A7  |

| 2 <sup>nd</sup> Cycle | A8  | A9  | A10 | A11 | L   | L   | L   | L   |

| 3 <sup>rd</sup> Cycle | A12 | A13 | A14 | A15 | A16 | A17 | A18 | A19 |

| 4 <sup>th</sup> Cycle | A20 | A21 | A22 | A23 | A24 | A25 | A26 | A27 |

A0-A11: column address in the page A12-A17: page address in the block

A18-A27: block address

# 5.2 Addressing (X16)

| Bus Cycle             | 100 | IO1 | 102 | IO3 | IO4 | IO5 | 106 | 107 |

|-----------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| 1 <sup>st</sup> Cycle | A0  | A1  | A2  | A3  | A4  | A5  | A6  | A7  |

| 2 <sup>nd</sup> Cycle | A8  | A9  | A10 | L   | L   | L   | L   | L   |

| 3 <sup>rd</sup> Cycle | A11 | A12 | A13 | A14 | A15 | A16 | A17 | A18 |

| 4 <sup>th</sup> Cycle | A19 | A20 | A21 | A22 | A23 | A24 | A25 | A26 |

A0-A10: column address in the page A11-A16: page address in the block

A17-A26: block address

DS-GD9Fx1GxF3A-Rev1.8 10 February 2023

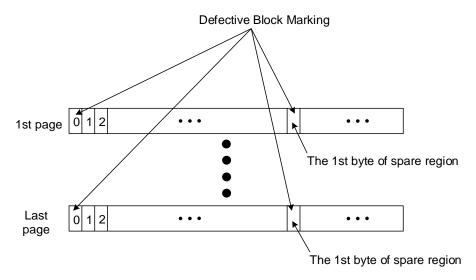

## **5.3 Factory Defect Mapping**

The Flash array is not presumed to be pristine, and a number of defects that makes the blocks unusable may be present. Invalid blocks shall be sorted out from normal blocks by software.

## 5.3.1. Device Requirements

If a block is defective, the manufacturer shall mark the block as defective by setting the Defective Block Marking, as shown in Figure of "Area marked in first or last page of block indicating defect", of the last page of the defective block to a value of non-FFh. The Defective Block Marking is located on the first byte of user data area or the first byte of spare data area in the pages within a block.

Figure 7. Area marked in first or last page of block indicating defect sequential figures

DS-GD9Fx1GxF3A-Rev1.8 11 February 2023

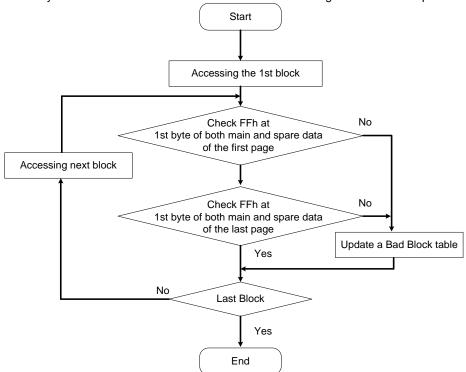

#### 5.3.2. Host Requirements

The host shall not erase or program blocks marked as defective by the manufacturer, and any attempt to do so yields indeterminate results.

Figure of "Flow chart to create initial invalid block table" outlines the flow chart how to create an initial invalid block table. It should be performed by the host to create the initial bad block table prior to performing any erase or programming operations on the target. The 1st byte of both main and spare region in non-defective blocks are read FFh with ECC enabled on the controller. A defective block is indicated by the majority of bits being read non-FFh in the Defective Block Marking location of either the first page or last page of the block. The host shall check the Defective Block Marking location of both the first and last past page of each block to verify the block is valid prior to any erase or program operations on that block.

NOTE: Over the lifetime use of a NAND device, the Defective Block Marking of defective blocks may encounter read disturbs that cause bit changes. The initial defect marks by the manufacturer may change value over the lifetime of the device, and are expected to be read by the host and used to create a bad block table during initial use of the part.

Figure 8: flow chart to create initial invalid block table sequential figures

DS-GD9Fx1GxF3A-Rev1.8 12 February 2023

# 6. COMMAND SET

| Function                               | 1 <sup>st</sup> | 2 <sup>nd</sup> | 3 <sup>rd</sup> | 4 <sup>th</sup> | During busy |

|----------------------------------------|-----------------|-----------------|-----------------|-----------------|-------------|

| Page read                              | 00H             | 30H             |                 |                 | no          |

| Read for copy-back                     | 00H             | 35H             |                 |                 | no          |

| Random data output                     | 05H             | E0H             |                 |                 | no          |

| Cache read start                       | 31H             |                 |                 |                 | no          |

| Cache read random                      | 00H             | 31H             |                 |                 | no          |

| Cache read end                         | 3FH             |                 |                 |                 | no          |

| Read id                                | 90H             |                 |                 |                 | no          |

| Read status register                   | 70H             |                 |                 |                 | yes         |

| Page program start / Cache program end | 80H             | 10H             |                 |                 | no          |

| Random data input                      | 85H             |                 |                 |                 | no          |

| Copy back program                      | 85H             | 10H             |                 |                 | no          |

| Cache program start                    | 80H             | 15H             |                 |                 | no          |

| Block erase                            | 60H             | D0H             |                 |                 | no          |

| Reset                                  | FFH             |                 |                 |                 | yes         |

| Page re-program                        | 8BH             | 10H             |                 |                 | no          |

| Read parameter page                    | ECH             |                 |                 |                 | no          |

| Read unique ID                         | EDH             |                 |                 |                 | no          |

Note: 1. read status, read ID are always output on IO [7:0].

## 7. BUS OPERATION

The bus on the device is multiplexed. Data I/O, addresses, and commands all share the same pins. I/O [15:8] are used only for data in the x16 configuration. Addresses and commands are always supplied on I/O [7:0].

The command sequence typically consists of a COMMAND LATCH cycle, address input cycles, and one or more data cycles, either READ or WRITE.

There are several standard bus operations that control the device. These are Command Input, Address Input, Data Input, Data Output, Write Protect, and Standby.

| CLE | ALE | CE# | WE#    | RE#     | WP#      | MODE                                     |

|-----|-----|-----|--------|---------|----------|------------------------------------------|

| Н   | L   | L   | Rising | Н       | Х        | Command input for read mode              |

| L   | Н   | L   | Rising | Н       | Х        | Address input (4 cycles) for read mode   |

| Н   | L   | L   | Rising | Н       | Н        | Command input for write mode             |

| L   | Н   | L   | Rising | Н       | Н        | Address input (4 cycles) for write cycle |

| L   | L   | L   | Rising | Н       | Н        | Data input                               |

| L   | L   | L   | Н      | Falling | Х        | Sequential read and data output          |

| L   | L   | L   | Н      | Н       | Х        | During read(busy)                        |

| Х   | Х   | Х   | Х      | Х       | Н        | During program/Erase(busy)               |

| Х   | Х   | Х   | Х      | Х       | L        | Write protect                            |

| Х   | Х   | Н   | Х      | Х       | 0V / VCC | Standby                                  |

#### Notes:

- 1. X can be VIL or VIH. H = Logic level HIGH. L = Logic level LOW.

- 2. WP# should be biased to CMOS high or CMOS low for stand-by mode.

- 3. WE# and RE# during Read Busy must be keep on high to prevent unplanned command/address/data input or to avert unintended data out. In this time, only Reset and Read Status can be input to the device.

DS-GD9Fx1GxF3A-Rev1.8 14 February 2023

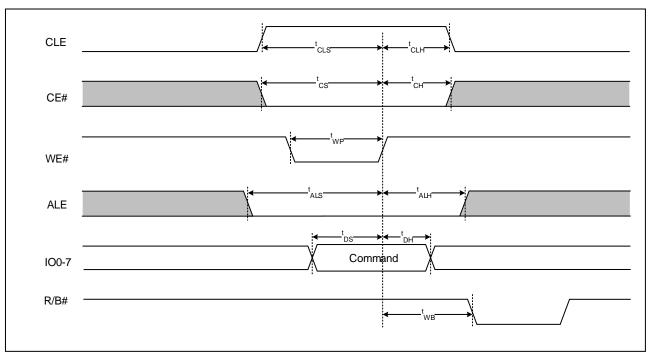

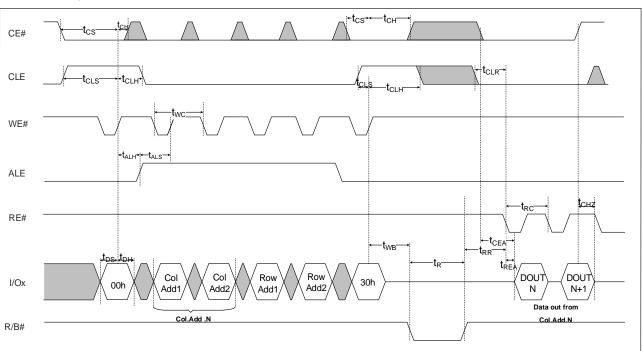

## 7.1 Command Input Cycle

Command Input bus operation is used to give a command to the memory device. Commands are accepted with Chip Enable low, Command Latch Enable High, Address Latch Enable low and Read Enable High and latched on the rising edge of Write Enable. Moreover, for commands that starts a modify operation (write/erase) the Write Protect pin must be high.

Figure 9: Command Input Cycle figures

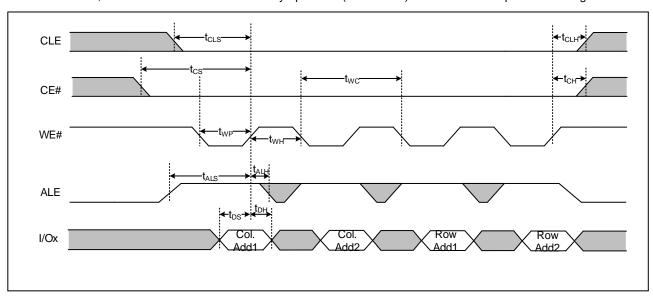

## 7.2 Address Input Cycle

Address Input bus operation allows the insertion of the memory address. Addresses are accepted with Chip Enable low, Address Latch Enable High, Command Latch Enable low and Read Enable High and latched on the rising edge of Write Enable. Moreover, for commands that starts a modify operation (write/erase) the Write Protect pin must be high.

Figure 10: Address Input Cycle figures

DS-GD9Fx1GxF3A-Rev1.8 15 February 2023

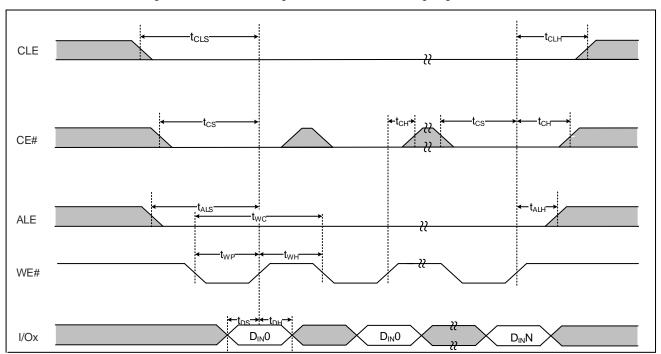

# 7.3 Data Input Cycle

Data Input bus operation allows to feed to the device the data to be programmed. The data insertion is serially and timed by the Write Enable cycles. Data are accepted only with Chip Enable low, Address Latch Enable low, Command Latch Enable low, Read Enable High, and Write Protect High and latched on the rising edge of Write Enable.

Figure 11: Data Input Cycle figures

DS-GD9Fx1GxF3A-Rev1.8 16 February 2023

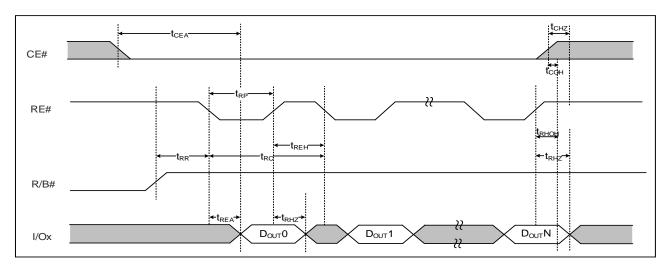

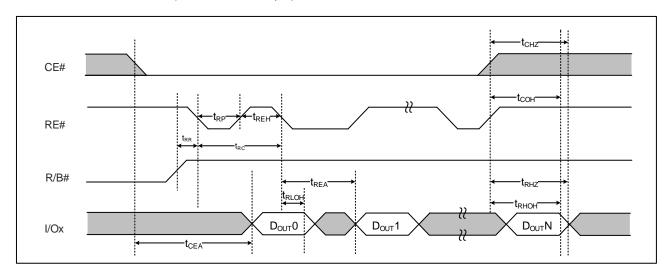

# 7.4 Data Output Cycle

Data Output bus operation allows to output data from the device. The data output cycle is serially and timed by the Read Enable cycles. Data output may be used with CE# don't care. However, if CE# don't care is used tCEA and tCOH timing requirements shall be met by the host.

Figure 12\_a: Data Output Cycle figures

If the host side uses a sequential access time (tRC) of less than 30ns, the data can be latched on the next falling edge of RE# as the waveform of EDO (Extended data output) mode.

Figure 12\_b: Data Output Cycle figures

DS-GD9Fx1GxF3A-Rev1.8 17 February 2023

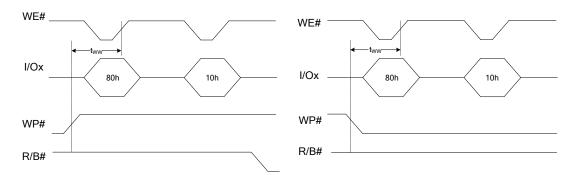

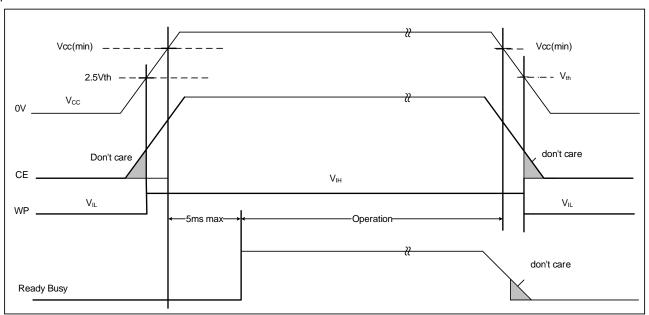

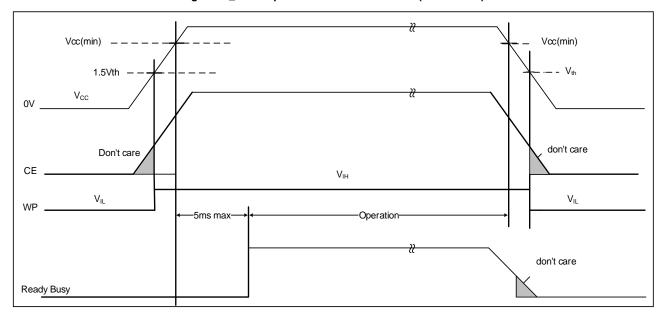

## 7.5 Write Protect

The Erase and Program Operations are automatically reset when WP# goes Low. The operations are enabled and disabled as follows.

Figure 13\_a: Write Protect Disable with program figures

Figure 13\_b: Write Protect Enable with program figures

Figure 13\_c: Write Protect Disable with erase figures

Figure 13\_d: Write Protect Enable with erase figures

DS-GD9Fx1GxF3A-Rev1.8 18 February 2023

## 8. OPERATION DESCRIPTION

## 8.1 Page Read Operation

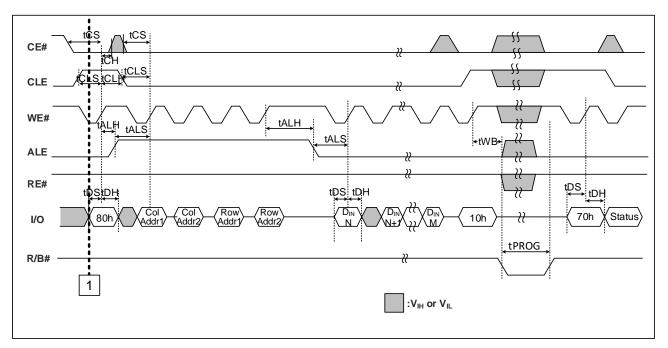

## 8.1.1 Common Page Read (00H-30H)

Read is initiated by writing 00H-30H to the command register along with four address cycles. The 2112 bytes of data within the selected page are transferred to the data registers. The system controller can detect the completion of this data transfer (tR) by analyzing the output of R/B# pin. Once the data in a page is loaded into the data registers, they may be read out in tRC by sequentially pulsing RE#. The repetitive high to low transitions of the RE# clock make the device output the data starting from the selected column address up to the last column address.

After the last data has been read out, CE# may be pulled up for some time to end the read operation, while during the RE# toggle cycle, CE# may be don't care when RE# is high. The CE# Don't Care feature may simplify the system interface, which allows controller to directly download the code from flash device, and the CE# transitions will not stop the read operation during the latency time.

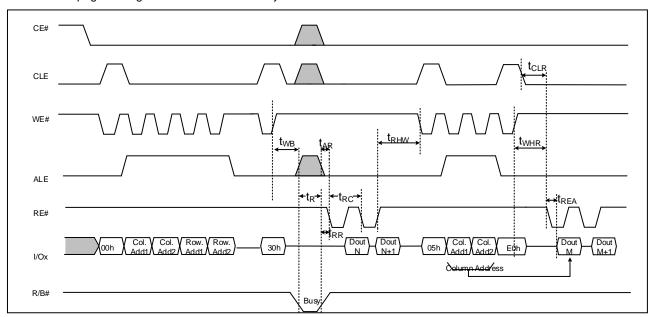

Figure 14: Common Page Read figures

DS-GD9Fx1GxF3A-Rev1.8 19 February 2023

#### 8.1.2 Random Data Output (05H-E0H)

The device may output random data in a page instead of the consecutive sequential data by writing random data output command (05H-E0H). The column address of next data, which is going to be out, may be changed to the address which follows random data output command. Random data output can be operated multiple times regardless of how many times it is done in a page Change Read Column shall only be issued when the device is in a read idle condition.

Figure 15: Random Data Output figures

#### 8.1.3 Cache Read Operation (31H/3FH)

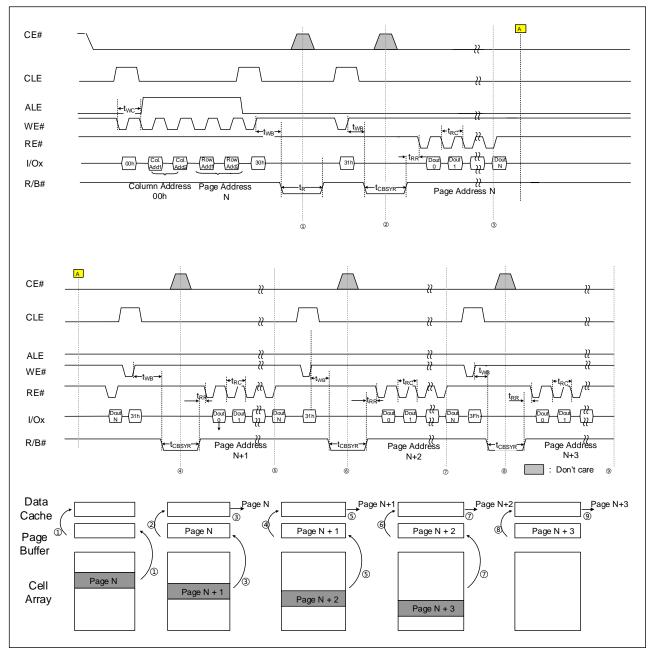

The Cache Read function permits a page to be read from the page register while another page is simultaneously read from the Flash array. A Read Page command shall be issued prior to the initial sequential or random Read Cache command in a read cache sequence. A Read Cache command shall be issued prior to a Read Cache End (3FH) command being issued. The Cache Read function may be issued after the Read function is complete. The host may enter the address of the next page to be read from the Flash array. Data output always begins at column address 00H. If the host does not enter an address to retrieve, the next sequential page is read, when the Read Cache function is issued. After the operation is begun R/B# is set to one (ready) and the host may begin to read the data from the previous Read or Read Cache function. Issuing an additional Read Cache function copies the data most recently read from the array into the page register. When no more pages are to be read, the final page is copied into the page register by issuing the 3FH command.

The host may begin to read data from the page register when R/B# is set to one (ready). When the 31H and 3FH commands are issued, R/B# shall be cleared to zero (busy) until the page has finished being copied from the Flash array.

DS-GD9Fx1GxF3A-Rev1.8 20 February 2023

Figure 16: Cache Read Operation figures

#### Note:

C1-C2: Column address of the page to retrieve. C1 is the least significant byte.

R1-R2: Row address of the page to retrieve. R1 is the least significant byte.

D0-Dn: Data bytes/words read from page requested by the original Read or the previous cache operation.

DS-GD9Fx1GxF3A-Rev1.8 21 February 2023

## 8.2 Page Program Operation

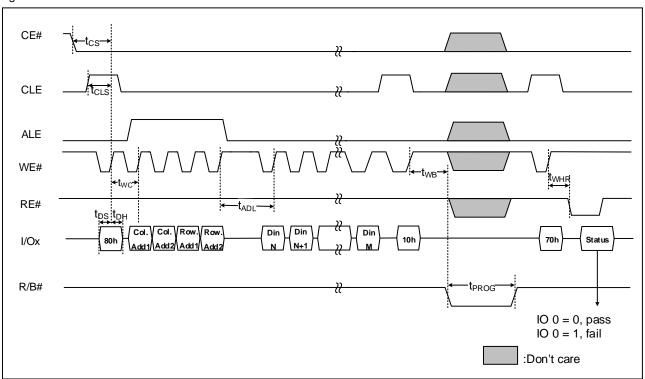

#### 8.2.1 Common Page Program (80H-10H)

The device is programmed basically on a page basis, but it does allow multiple partial pages programming of a word or consecutive bytes up to 2,112 in a single page program cycle. The number of consecutive partial page programming operation within the same page without an intervening erase operation must not exceed 4 times for main array (1time/512byte) and 4 times for spare array (1time/16byte). The addressing must be done in sequential order in a block. A page program cycle consists of a serial data loading period in which up to 2,112bytes of data may be loaded into the data register, followed by a non-volatile programming period where the loaded data is programmed into the appropriate cell.

The serial data loading period begins by inputting the Serial Data Input command (80h), followed by the four cycle address inputs and then serial data loading. The words other than those to be programmed do not need to be loaded.

The Page Program Confirm command (10h) initiates the programming process. Writing 10h alone without previously entering the serial data will not initiate the programming process. The internal write state controller automatically executes the algorithms and timings necessary for program and verify, thereby freeing the system controller for other tasks. Once the program process starts, the Read Status Register command may be issued to read the status register.

The command register remains in Read Status command mode until another valid command is written to the command register.

Figure 17: Common Page Program figures

DS-GD9Fx1GxF3A-Rev1.8 22 February 2023

## 8.2.2 Page Program Operation with Random Data Input (85H-10H)

The device supports random data input in a page. The column address of next data, which will be entered, may be changed to the address which follows random data input command (85H). Random data input may be operated multiple times regardless of how many times it is done in a page.

Figure 18: Page Program Operation with Random Data Input figures

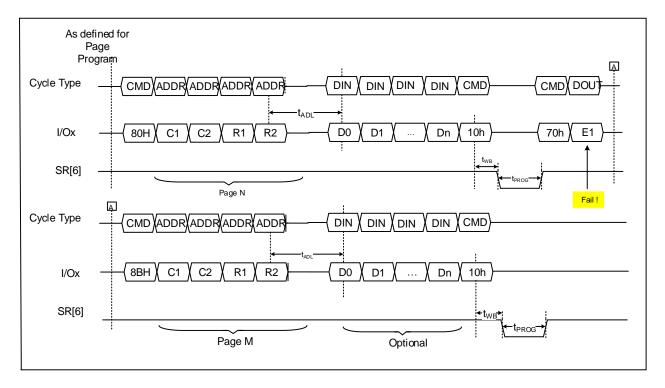

## 8.2.3 Page Re-program (8BH-10H)

It was also highlighted that page program may result in a fail, which can be detected by Read Status Register. In this event, it implements the innovative feature of "page re-program". This command allows the re-programming of the same pattern of the (failed) page into another memory location. The command sequence initiates with re-program setup (8BH), followed by the four cycle address inputs of the target page. If the target pattern for the destination page is not changed compared to the page, the program confirm can be issued (10H) without any data input cycle.

On the other hand, if the pattern bound for the target page is different from that of the previous page, data in cycles can be issued before program confirm "10H"

DS-GD9Fx1GxF3A-Rev1.8 23 February 2023

Figure 19: Page Re-program figures

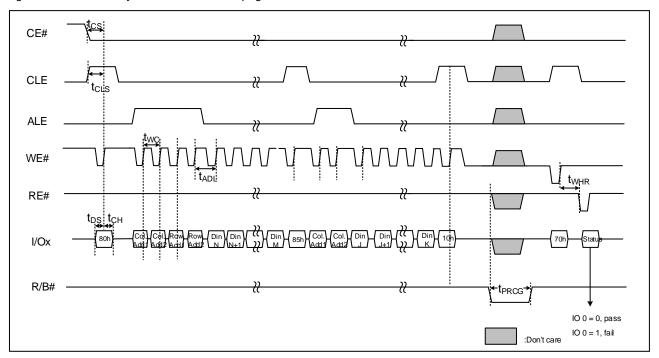

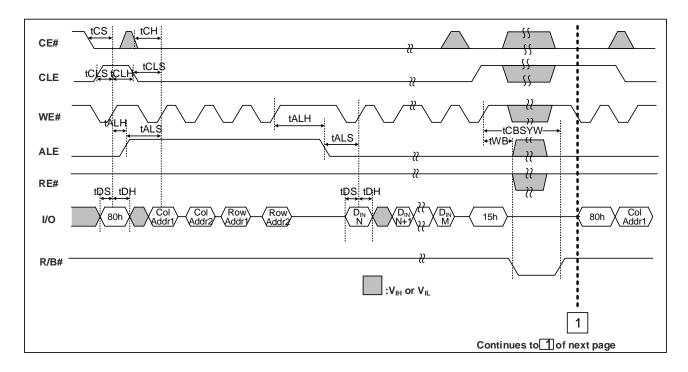

#### 8.2.4 Cache Program Operation (80H-15H)

Cache Program is an extension of Page Program, which is executed with one page data registers, and is available only within a block. Since the device has one page of cache memory, serial data input may be executed while data stored in data register are programmed into memory cell.

After writing the first set of data up to one page into the selected cache registers, Cache Program command (15H) instead of actual Page Program (10H) is inputted to make cache registers free and to start internal program operation. To transfer data from cache registers to data registers, the device remains in Busy state for a short period of time (tCBSYW) and has its cache registers ready for the next data-input while the internal programming gets started with the data loaded into data registers. Read Status command (70H) may be issued to find out when cache registers become ready by polling the Cache-Busy status bit (I/O 6). Pass/fail status of only the previous page is available upon the return to Ready state. When the next set of data is loaded with the Cache Program command, tCBSYW is affected by the progress of pending internal programming. The programming of the cache registers is initiated only when the pending program cycle is finished and the data registers are available for the transfer of data from cache registers. The status bit (I/O5) for internal Ready/Busy may be polled to identify the completion of internal programming. If the system monitors the progress of programming only with R/B#, the last page of the target programming sequence must be programmed with actual Page Program command (10H).

DS-GD9Fx1GxF3A-Rev1.8 24 February 2023

Figure 20: Cache Program Operation figures

DS-GD9Fx1GxF3A-Rev1.8 25 February 2023

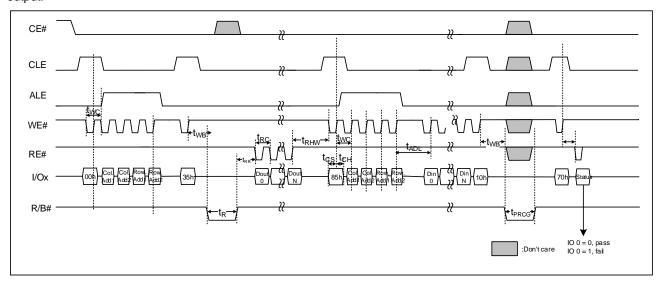

#### 8.2.5 Copy-Back Program with Random Data Input (00H-35H-85H-10H)

The copy-back program is configured to quickly and efficiently rewrite data stored in one page without utilizing an external memory. Since the time-consuming cycles of serial access and re-loading cycles are removed, the system performance is improved. The benefit is especially obvious when a portion of a block is updated and the rest of the block is also needed to be copied to the newly assigned free block. The operation for performing a copy-back program is a sequential execution of page-read without serial access and copying-program with the address of destination page. A read operation with "35h" command and the address of the source page moves the whole page bytes data into the internal data buffer. As soon as the device returns to Ready state, optional data read-out is allowed by toggling RE#, or Copy Back command (85H) with the address cycles of destination page may be written. The Program Confirm command (10H) is required to actually begin the programming operation. Data input cycle for modifying a portion or multiple distant portions of the source page is allowed. When there is a program-failure at Copy-Back operation, error is reported by pass/fail status. But, if Copy-Back operations are accumulated over time, bit error due to charge loss is not checked by external error detection/correction scheme. Please note that Random Data Input (with/without data) is entered before Program Confirm command (10H) after Random Data output.

Figure 21: Copy-Back Program with Random Data Input figures

DS-GD9Fx1GxF3A-Rev1.8 26 February 2023

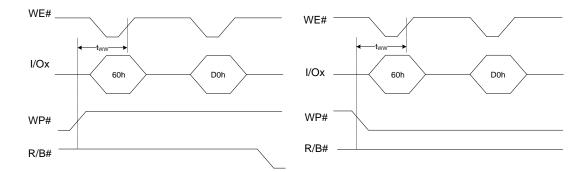

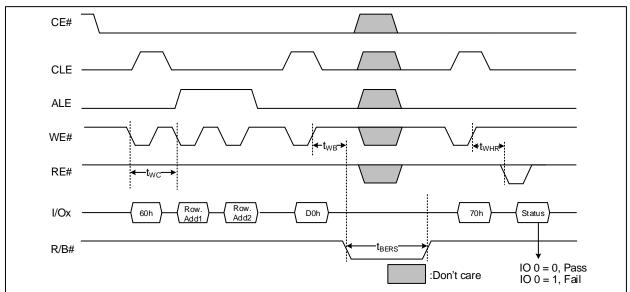

## 8.3 Block Erase Operation (60H-D0H)

The Erase operation is done on a block basis. Block address loading is accomplished in two cycles initiated by an Erase Setup command (60H). Only address Row Address is valid while Column Addresses ignored. The Erase Confirm command (D0H) following the block address loading initiates the internal erasing process. At the rising edge of WE after the erase confirm command input, the internal write controller handles erase and erase verify. Once the erase process starts, the Read Status Register command may be entered to read the status register. The system controller can detect the completion of an erase by monitoring the R/B output, or the Status bit (I/O 6) of the Status Register. Only the Read Status command and Reset command are valid while erasing is in progress. When the erase operation is completed, the Write Status Bit (I/O 0) may be checked.

Figure 22: Common Block Erase Operation figures

DS-GD9Fx1GxF3A-Rev1.8 27 February 2023

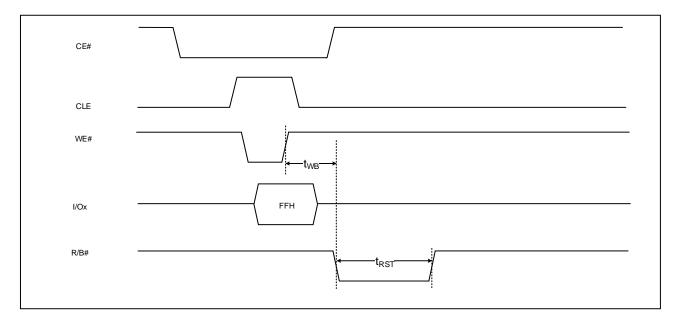

## 8.4 Reset (FFH)

The device offers a reset feature, executed by writing FFH to the command register. When the device is in busy state during random read, program or erase mode, the reset operation will abort these operations. The contents of memory cells being altered are no longer valid, as the data will be partially programmed or erased. The command register is cleared to wait for the next command, and the Status Register is cleared to value C0h when R/B# is high. If the device is already in reset state a new reset command will be accepted by the command register. The R/B# pin transitions to low for tRST after the Reset command is written.

Figure 23: Reset (FFH) figures

DS-GD9Fx1GxF3A-Rev1.8 28 February 2023

## **8.5 Read Device Information**

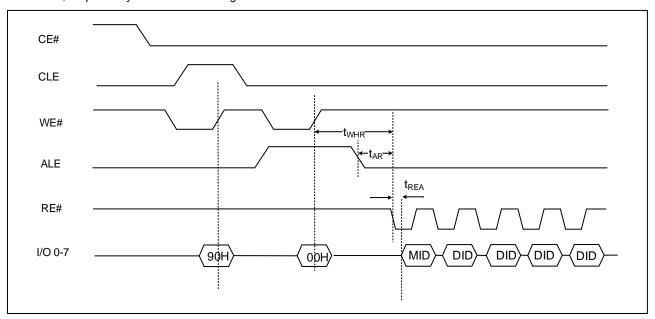

## 8.5.1 Read ID and ONFI Signature (90H)

The device contains a product identification mode, initiated by writing 90H to the command register, followed by an address input of 00H. Four read cycles sequentially output the manufacturer code, and the device code and other information, respectively. The command register remains in Read ID mode until further commands are issued to.

Figure 24: Read ID figures

#### **ID Definition Table**

| Byte                                                                 | Description                                                                 |  |  |  |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|--|

| 1 <sup>st</sup> Byte                                                 | Manufacturer Code (MID)                                                     |  |  |  |

| 2 <sup>nd</sup> Byte                                                 | Byte Device Code (DID)                                                      |  |  |  |

| 2rd Puto                                                             | Internal Chip Number, Cell Type, Number of Simultaneously Programmed Pages, |  |  |  |

| 3 <sup>rd</sup> Byte                                                 | Interleaved Program, Write Cache                                            |  |  |  |

| 4 <sup>th</sup> Byte Page size, Block size, Spare size, Organization |                                                                             |  |  |  |

| 5 <sup>th</sup> Byte                                                 | ECC & Plane                                                                 |  |  |  |

#### **Read ID Data Table**

| Part Number | VCC  | Bus Width | MID(1st) | DID(2 <sup>nd</sup> ) | 3 <sup>rd</sup> | 4 <sup>th</sup> | 5 <sup>th</sup> |

|-------------|------|-----------|----------|-----------------------|-----------------|-----------------|-----------------|

| GD9FU1G8F3A | 3.3v | x8        | C8       | F1H                   | 80H             | 19H             | 42H             |

| GD9FU1G6F3A | 3.3v | x16       | C8       | C1H                   | 80H             | 59H             | 42H             |

| GD9FS1G8F3A | 1.8v | x8        | C8       | A1H                   | 80H             | 11H             | 42H             |

| GD9FS1G6F3A | 1.8v | x16       | C8       | B1H                   | 80H             | 51H             | 42H             |

DS-GD9Fx1GxF3A-Rev1.8 29 February 2023

## $2^{\rm rd}$ Byte of Device Code Description

| 2 <sup>rd</sup> Cycle | Description | 107 | 106 | IO5 | 104 | IO3 | 102 | IO1 | 100 |

|-----------------------|-------------|-----|-----|-----|-----|-----|-----|-----|-----|

|                       | 3.3v 8bits  | 1   | 1   | 1   | 1   |     |     |     |     |

| VCC Due Width         | 3.3v 16bits | 1   | 1   | 0   | 0   |     |     |     |     |

| VCC, Bus Width        | 1.8v 8bits  | 1   | 0   | 1   | 0   |     |     |     |     |

|                       | 1.8v 16bits | 1   | 0   | 1   | 1   |     |     |     |     |

|                       | 1G          |     |     |     |     | 0   | 0   | 0   | 1   |

|                       | 2G          |     |     |     |     | 0   | 0   | 1   | 0   |

|                       | 4G          |     |     |     |     | 0   | 0   | 1   | 1   |

|                       | 8G          |     |     |     |     | 0   | 1   | 0   | 0   |

|                       | 16G         |     |     |     |     | 0   | 1   | 0   | 1   |

| Mamary danaity        | 32G         |     |     |     |     | 0   | 1   | 1   | 0   |

| Memory density        | 64G         |     |     |     |     | 0   | 1   | 1   | 1   |

|                       | 256G        |     |     |     |     | 1   | 0   | 0   | 0   |

|                       | 512G        |     |     |     |     | 1   | 0   | 0   | 1   |

|                       | 1T          |     |     |     |     | 1   | 0   | 1   | 0   |

|                       | 2T          |     |     |     |     | 1   | 0   | 1   | 1   |

|                       | 22G         |     |     |     |     | 1   | 1   | 0   | 0   |

## 3<sup>rd</sup> Byte of Device Identifier Description

| 3 <sup>rd</sup> Cycle                    | Description      | 107 | 106 | IO5 | 104 | IO3 | IO2 | IO1 | 100 |

|------------------------------------------|------------------|-----|-----|-----|-----|-----|-----|-----|-----|

|                                          | 1                |     |     |     |     |     |     | 0   | 0   |

| Internal Chin Number                     | 2                |     |     |     |     |     |     | 0   | 1   |

| Internal Chip Number                     | 4                |     |     |     |     |     |     | 1   | 0   |

|                                          | 8                |     |     |     |     |     |     | 1   | 1   |

|                                          | 2 Level Cell     |     |     |     |     | 0   | 0   |     |     |

| Oall Tomas                               | 4 Level Cell     |     |     |     |     | 0   | 1   |     |     |

| Cell Type                                | 8 Level Cell     |     |     |     |     | 1   | 0   |     |     |

|                                          | 16 Level Cell    |     |     |     |     | 1   | 1   |     |     |

|                                          | 1                |     |     | 0   | 0   |     |     |     |     |

| Number of Simultaneously                 | 2                |     |     | 0   | 1   |     |     |     |     |

| Programmed Pages                         | 4                |     |     | 1   | 0   |     |     |     |     |

|                                          | 8                |     |     | 1   | 1   |     |     |     |     |

| letedered December Detuces               | Not              |     | 0   |     |     |     |     |     |     |

| Interleaved Program Between Multiple Die | Supported        |     | 0   |     |     |     |     |     |     |

|                                          | Supported        |     | 1   |     |     |     |     |     |     |

| Write Cache                              | Not<br>Supported | 0   |     |     |     |     |     |     |     |

| (Cache Programming)                      | Supported        | 1   |     |     |     |     |     |     |     |

## 4<sup>th</sup> Byte of Device Identifier Description

| 4 <sup>th</sup> Cycle           | Description | 107 | 106 | IO5 | 104 | IO3 | IO2 | IO1 | 100 |

|---------------------------------|-------------|-----|-----|-----|-----|-----|-----|-----|-----|

|                                 | 1KB         |     |     |     |     |     |     | 0   | 0   |

| Dago Ciza (without Chara Area)  | 2KB         |     |     |     |     |     |     | 0   | 1   |

| Page Size (without Spare Area)  | 4KB         |     |     |     |     |     |     | 1   | 0   |

|                                 | 8KB         |     |     |     |     |     |     | 1   | 1   |

| Size of spare area (byte per    | 16          |     |     |     |     |     | 0   |     |     |

| 512-byte)                       | 32          |     |     |     |     |     | 1   |     |     |

|                                 | 45ns        | 0   |     |     |     | 0   |     |     |     |

| Carial Assass Times             | 25ns        | 0   |     |     |     | 1   |     |     |     |

| Serial Access Time              | Reserved    | 1   |     |     |     | 0   |     |     |     |

|                                 | Reserved    | 1   |     |     |     | 1   |     |     |     |

|                                 | 64KB        |     |     | 0   | 0   |     |     |     |     |

| Dlock Cize (Mithout Chare Area) | 128KB       |     |     | 0   | 1   |     |     |     |     |

| Block Size (Without Spare Area) | 256KB       |     |     | 1   | 0   |     |     |     |     |

|                                 | 512KB       |     |     | 1   | 1   |     |     |     |     |

| Organization                    | x8          |     | 0   |     |     |     |     |     |     |

| Organization                    | x16         |     | 1   |     |     |     |     |     |     |

## 5<sup>th</sup> Byte of ECC & Plane

| 5 <sup>th</sup> Cycle | Description | 107      | 106 | IO5 | 104 | IO3 | IO2 | IO1 | 100 |

|-----------------------|-------------|----------|-----|-----|-----|-----|-----|-----|-----|

|                       | 1           |          |     |     |     |     |     | 0   | 0   |

| ECC Lovel             | 2           |          |     |     |     |     |     | 0   | 1   |

| ECC Level             | 4           |          |     |     |     |     |     | 1   | 0   |

|                       | 8           |          |     |     |     |     |     | 1   | 1   |

|                       | 1           |          |     |     |     | 0   | 0   |     |     |

| Diana Niverkan        | 2           |          |     |     |     | 0   | 1   |     |     |

| Plane Number          | 4           |          |     |     |     | 1   | 0   |     |     |

|                       | 8           |          |     |     |     | 1   | 1   |     |     |

|                       | 64Mb        |          | 0   | 0   | 0   |     |     |     |     |

|                       | 128Mb       |          | 0   | 0   | 1   |     |     |     |     |

|                       | 256Mb       |          | 0   | 1   | 0   |     |     |     |     |

| Diana sina            | 512Mb       |          | 0   | 1   | 1   |     |     |     |     |

| Plane size            | 1Gb         |          | 1   | 0   | 0   |     |     |     |     |

|                       | 2Gb         |          | 1   | 0   | 1   |     |     |     |     |

|                       | 4Gb         |          | 1   | 1   | 0   |     |     |     |     |

|                       | 8Gb         |          | 1   | 1   | 1   |     |     |     |     |

|                       | ECC         | 0        |     |     |     |     |     |     |     |

| Internal ECC          | disabled    | U        |     |     |     |     |     |     |     |

| Internal Loo          | ECC         | 1        |     |     |     |     |     |     |     |

|                       | enabled     | <u> </u> |     |     |     |     |     |     |     |

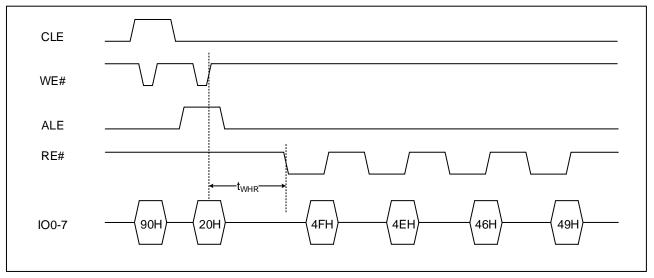

To retrieve the ONFI signature, the command 90H together with an address of 20H shall be entered. The ONFI signature is the ASCII encoding of 'ONFI' where 'O' = 4FH, 'N' = 4EH, 'F' = 46H, and 'I' = 49H. Reading beyond four bytes yields indeterminate values.

Figure 25: Read ONFI Signature figures

DS-GD9Fx1GxF3A-Rev1.8 32 February 2023

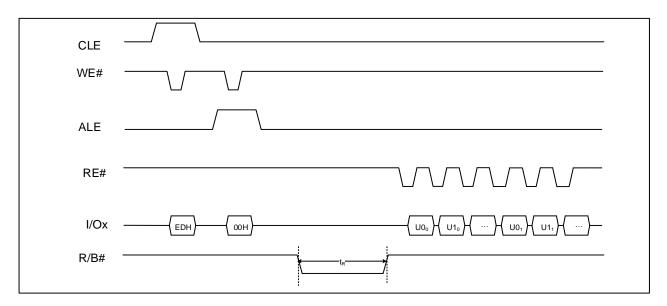

## 8.5.2 Read Unique ID (EDH)

The Read Unique ID function is used to retrieve the 16 byte unique ID (UID) for the device. The unique ID when combined with the device manufacturer shall be unique.

The UID data may be stored within the Flash array. To allow the host to determine if the UID is without bit errors, the UID is returned with its complement. If the XOR of the UID and its bit-wise complement is all ones, then the UID is valid. To accommodate robust retrieval of the UID in the case of bit errors, sixteen copies of the UID and the corresponding complement shall be stored by the target. For example, reading bytes 32-63 returns to the host another copy of the UID and its complement.

To change the data output location, it is recommended to use the Random Data Out command set (05H-E0H). The Status Read command (70H) can be used to check the completion. To continue the read operation, a following read command (00h) to re-enable the data out is necessary.

| Bytes | Value                     |

|-------|---------------------------|

| 0-15  | UID                       |

| 16-31 | UID complement (bit-wise) |

Figure 26: Read Unique ID Timing

DS-GD9Fx1GxF3A-Rev1.8 33 February 2023

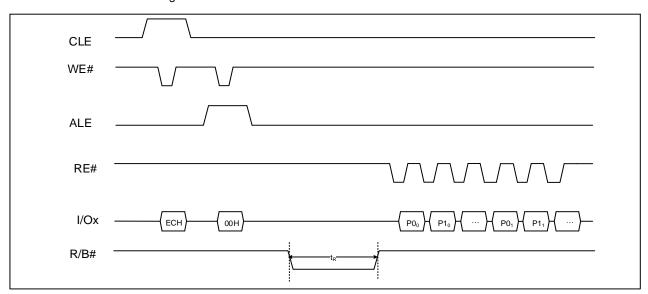

## 8.5.3 Read Parameter Page (ECH)

The Read Parameter Page function retrieves the data structure that describes the chip's organization, features, timing-sand other behavioral parameters. This data structure enables the host processor to automatically recognize the NAND Flash configuration of a device. The whole data structure is repeated at least three times. The Random Data Read command (05H-E0H) can be issued during execution of the read parameter page to read specific portion-soft the parameter page. The Read Status command (70H) may be used to check the status of read parameter page during execution. After completion of the Read Status command, 00H is issued by the host on the command line to continue with the data output flow for the Read Parameter Page command.

Figure 27: Read Parameter Page figures

DS-GD9Fx1GxF3A-Rev1.8 34 February 2023

Parameter Page Table

| Byte  | O/M | Description                                            |          |

|-------|-----|--------------------------------------------------------|----------|

| 0-3   | М   | Parameter page signature                               | 4FH      |

|       |     | Byte 0: 4FH, "O"                                       | 4EH      |

|       |     | Byte 1: 4EH, "N"                                       | 46H      |

|       |     | Byte 2: 46H, "F"                                       | 49H      |

|       |     | Byte 3: 49H, "I"                                       |          |

| 4-5   | М   | Revision number                                        | 02H      |

|       |     | 2-15 Reserved (0)                                      | 00H      |

|       |     | 1 1 = supports ONFI version 1.0                        |          |

|       |     | 0 Reserved (0)                                         |          |

| 6-7   | М   | Features supported                                     | 10H(X8)/ |

|       |     | 5-15 Reserved (0)                                      | 11H(X16) |

|       |     | 4 1 = supports odd to even page Copy back              | 00H      |

|       |     | 3 1 = supports interleaved operations                  |          |

|       |     | 2 1 = supports non-sequential page programming         |          |

|       |     | 1 1 = supports multiple LUN operations                 |          |

|       |     | 0 1 = supports 16-bit data bus width                   |          |

| 8-9   | М   | Optional commands supported                            | 33H      |

|       |     | 6-15 Reserved (0)                                      | 00H      |

|       |     | 5 1 = supports Read Unique ID                          |          |

|       |     | 4 1 = supports Copy-back                               |          |

|       |     | 3 1 = supports Read Status Enhanced                    |          |

|       |     | 2 1 = supports Get Features and Set Features           |          |

|       |     | 1 1 = supports Read Cache Integrity                    |          |

|       |     | 0 1 = supports Page Cache Program command              |          |

| 10-31 |     | Reserved (0)                                           | 00H      |

|       |     |                                                        |          |

|       |     |                                                        | 00H      |

|       |     | Manufacturer Information block                         |          |

| 32-43 | М   | Device manufacturer (12 ASCII characters)"GIGADEVICE " | 47H      |

|       |     |                                                        | 49H      |

|       |     |                                                        | 47H      |

|       |     |                                                        | 41H      |

|       |     |                                                        | 44H      |

|       |     |                                                        | 45H      |

|       |     |                                                        | 56H      |

|       |     |                                                        | 49H      |

|       |     |                                                        | 43H      |

|       |     |                                                        | 45H      |

|       |     |                                                        | 20H      |

|       |     |                                                        | 20H      |

| 44-63 | М | Device model (20 ASCII cha  | aracters)    |              | 47H     |  |  |  |  |  |

|-------|---|-----------------------------|--------------|--------------|---------|--|--|--|--|--|

|       |   | Device Model                | ORGANIZATION | VCC RANGE    | 44H     |  |  |  |  |  |

|       |   | "GD9FS1G8F3A"               | 128M x 8bit  | 1.7v ~ 1.95v | 39H     |  |  |  |  |  |

|       |   | "GD9FS1G6F3A"               | 64M x 16bit  | 1.7v ~ 1.95v | 46H     |  |  |  |  |  |

|       |   | "GD9FU1G8F3A"               | 128M x 8bit  | 2.7v ~ 3.6v  | 53H/55H |  |  |  |  |  |

|       |   | "GD9FU1G6F3A"               | 64M x 16bit  | 2.7v ~ 3.6v  | 31H     |  |  |  |  |  |

|       |   |                             | <u> </u>     |              | 47H     |  |  |  |  |  |

|       |   |                             |              |              | 38H/36H |  |  |  |  |  |

|       |   |                             |              |              | 46H     |  |  |  |  |  |

|       |   |                             |              |              | 33H     |  |  |  |  |  |

|       |   |                             |              |              | 41H     |  |  |  |  |  |

|       |   |                             |              |              | 20H     |  |  |  |  |  |

|       |   |                             |              |              | 20H     |  |  |  |  |  |

|       |   |                             |              |              | 20H     |  |  |  |  |  |

|       |   |                             |              |              | 20H     |  |  |  |  |  |

|       |   |                             |              |              | 20H     |  |  |  |  |  |

|       |   |                             |              |              | 20H     |  |  |  |  |  |

|       |   |                             |              |              | 20H     |  |  |  |  |  |

|       |   |                             |              |              | 20H     |  |  |  |  |  |

|       |   |                             |              |              | 20H     |  |  |  |  |  |

| 64    | М | JEDEC manufacturer ID"C8    | "            |              | C8H     |  |  |  |  |  |

| 65-66 | 0 | Date code                   |              |              |         |  |  |  |  |  |

|       |   |                             |              |              | 00H     |  |  |  |  |  |

| 67-79 |   | Reserved                    |              |              |         |  |  |  |  |  |

|       |   |                             |              |              | 00H     |  |  |  |  |  |

|       |   |                             |              |              | 00H     |  |  |  |  |  |

|       |   | Memory organization block   |              |              |         |  |  |  |  |  |

| 80-83 | М | Number of data bytes per pa | age          |              | 00H     |  |  |  |  |  |

|       |   |                             |              |              | 08H     |  |  |  |  |  |

|       |   |                             |              |              | 00H     |  |  |  |  |  |

|       |   |                             |              |              | 00H     |  |  |  |  |  |

| 84-85 | М | Number of spare bytes per p | page         |              | 40H     |  |  |  |  |  |

|       |   |                             |              |              | 00H     |  |  |  |  |  |

| 86-89 | М | Number of data bytes per pa | artial page  |              | 00H     |  |  |  |  |  |

|       |   |                             |              |              | 02H     |  |  |  |  |  |

|       |   |                             |              |              | 00H     |  |  |  |  |  |

|       |   |                             |              |              | 00H     |  |  |  |  |  |

| 90-91 | М | Number of spare bytes per p | partial page |              | 10H     |  |  |  |  |  |

|       |   |                             |              |              | 00H     |  |  |  |  |  |

| 92-95 | М | Number of pages per block   |              |              | 40H     |  |  |  |  |  |

|       |   |                             |              |              | 00H     |  |  |  |  |  |

|       |   |                             |              |              | 00H     |  |  |  |  |  |

|       |   |                             |              |              | 00H     |  |  |  |  |  |

| 96-99 | М | Number of blocks per logica | l unit (LUN) |              | 00H     |  |  |  |  |  |

|       |   |                             |              |              | 04H     |  |  |  |  |  |

|         |   |                                                                               | 00H        |

|---------|---|-------------------------------------------------------------------------------|------------|

|         |   |                                                                               | 00H        |

| 100     | М | Number of logical units (LUNs)                                                | 01H        |

| 101     | М | Number of address cycles                                                      | 22H        |

|         |   | 4-7 Column address cycles                                                     |            |

|         |   | 0-3 Row address cycles                                                        |            |

| 102     | М | Number of bits per cell                                                       | 01H        |

| 103-104 | М | Bad blocks maximum per LUN                                                    | 14H        |

|         |   |                                                                               | 00H        |

| 105-106 | М | Block endurance                                                               | 01H        |

|         |   |                                                                               | 05H        |

| 107     | М | Guaranteed valid blocks at beginning of target                                | 01H        |

| 108-109 | М | Block endurance for guaranteed valid blocks                                   | 01H        |

|         |   |                                                                               | 05H        |

| 110     | М | Number of programs per page                                                   | 04H        |

| 111     | М | Partial programming attributes                                                | 00H        |

|         |   | 5-7 Reserved                                                                  |            |

|         |   | 4 1 = partial page layout is partial page data followed by partial page spare |            |

|         |   | 1-3 Reserved                                                                  |            |

|         |   | 0 1 = partial page programming has constraints                                |            |

| 112     | М | Number of bits ECC correctability                                             | 04H        |

| 113     | М | Number of interleaved address bits                                            | 00H        |

|         |   | 4-7 Reserved (0)                                                              |            |

|         |   | 0-3 Number of interleaved address bits                                        |            |

| 114     | 0 | Interleaved operation attributes                                              | 00H        |

|         |   | 4-7 Reserved (0)                                                              |            |

|         |   | 3 Address restrictions for program cache                                      |            |

|         |   | 2 1 = program cache supported                                                 |            |

|         |   | 1 1 = no block address restrictions                                           |            |

|         |   | 0 Overlapped / concurrent interleaving support                                |            |

| 115-127 |   | Reserved                                                                      | 00H        |

|         |   |                                                                               |            |

|         |   |                                                                               | 00H        |

|         |   | Electrical parameters block                                                   |            |

| 128     | М | I/O capacitance                                                               | 06H        |

| 129-130 | М | Timing mode support                                                           | 07H(3.3V)/ |

|         |   | 6-1 5Reserved (0)                                                             | 03H(1.8V)  |

|         |   | 5 1 = supports timing mode 5                                                  | 00H        |

|         |   | 4 1 = supports timing mode 4                                                  |            |

|         |   | 3 1 = supports timing mode 3                                                  |            |

|         |   | 2 1 = supports timing mode 2                                                  |            |

|         |   | 1 1 = supports timing mode 1                                                  |            |

|         |   | 0 1 = supports timing mode 0, shall be 1                                      |            |

| 6-1 5Reserved (0) 5 1 = supports timing mode 5 4 1 = supports timing mode 4 3 1 = supports timing mode 3 2 1 = supports timing mode 2 1 1 = supports timing mode 0, 133-134 M tPROG Maximum page program time (us)  135-136 M tBERS Maximum block erase time (us)  137-138 M tR Maximum page read time (us)  139-140 M tCCS Minimum Change Column setup time (ns)  141-163 Reserved  OOH  Vendor block  164-165 M Vendor specific Revision number  OOH  154-255 M Integrity CRC  Redundant parameter pages                                                                               | 131-132  | 0   | Program cache timing mode support                   | 07H(3.3V)/ |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|-----------------------------------------------------|------------|

| 5 1 = supports timing mode 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 101 102  | Ü   |                                                     | ` ,        |

| 4 1 = supports timing mode 4 3 1 = supports timing mode 3 2 1 = supports timing mode 2 1 1 = supports timing mode 1 0 1 = supports timing mode 0,  133-134 M tPROG Maximum page program time (us)  BCH 02H 135-136 M tBERS Maximum block erase time (us)  10H 27H 137-138 M tR Maximum page read time (us)  19H 00H 139-140 M tCCS Minimum Change Column setup time (ns)  3CH 00H 141-163 Reserved  00H Vendor block  164-165 M Vendor specific Revision number 00H 166-253 Vendor specific 00H                                                                                          |          |     |                                                     | ` ,        |

| 3 1 = supports timing mode 3 2 1 = supports timing mode 2 1 1 = supports timing mode 0,  133-134 M tPROG Maximum page program time (us)  BCH 02H 135-136 M tBERS Maximum block erase time (us)  10H 27H 137-138 M tR Maximum page read time (us)  19H 00H 139-140 M tCCS Minimum Change Column setup time (ns)  3 CH 00H 141-163 Reserved 00H Vendor block  164-165 M Vendor specific Revision number 00H 254-255 M Integrity CRC                                                                                                                                                        |          |     |                                                     | 0011       |

| 2 1 = supports timing mode 2 1 1 = supports timing mode 1 0 1 = supports timing mode 0,  133-134 M tPROG Maximum page program time (us)  BCH 02H 135-136 M tBERS Maximum block erase time (us)  10H 27H 137-138 M tR Maximum page read time (us)  19H 00H 139-140 M tCCS Minimum Change Column setup time (ns)  3CH 00H 141-163 Reserved  00H Vendor block  164-165 M Vendor specific Revision number  00H 254-255 M Integrity CRC                                                                                                                                                       |          |     |                                                     |            |

| 1 1 = supports timing mode 1       0 1 = supports timing mode 0,         133-134 M       tPROG Maximum page program time (us)       BCH         135-136 M       tBERS Maximum block erase time (us)       10H         27H       27H         137-138 M       tR Maximum page read time (us)       19H         139-140 M       tCCS Minimum Change Column setup time (ns)       3CH         141-163 Reserved       00H         Vendor block       00H         164-165 M       Vendor specific Revision number       00H         254-255 M       Integrity CRC                              |          |     |                                                     |            |

| 0 1 = supports timing mode 0,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |     |                                                     |            |

| 133-134         M         tPROG Maximum page program time (us)         BCH 02H           135-136         M         tBERS Maximum block erase time (us)         10H 27H           137-138         M         tR Maximum page read time (us)         19H 00H           139-140         M         tCCS Minimum Change Column setup time (ns)         3CH 00H           141-163         Reserved         00H           Vendor block         00H           164-165         M         Vendor specific Revision number         00H           254-255         M         Integrity CRC         00H |          |     |                                                     |            |

| 135-136   M   tBERS Maximum block erase time (us)   10H   27H   137-138   M   tR Maximum page read time (us)   19H   00H   139-140   M   tCCS Minimum Change Column setup time (ns)   3CH   00H   141-163   Reserved   00H   Vendor block   164-165   M   Vendor specific Revision number   00H   166-253   Vendor specific   00H   254-255   M   Integrity CRC                                                                                                                                                                                                                          | 133_134  | М   |                                                     | BCH        |

| 135-136       M       tBERS Maximum block erase time (us)       10H         137-138       M       tR Maximum page read time (us)       19H         139-140       M       tCCS Minimum Change Column setup time (ns)       3CH         141-163       Reserved       00H         Vendor block       00H         164-165       M       Vendor specific Revision number       00H         166-253       Vendor specific       00H         254-255       M       Integrity CRC       00H                                                                                                      | 100-10-1 | 101 | a 1700 Maximum page program time (45)               |            |

| 27H   137-138   M   tR Maximum page read time (us)   19H   00H   139-140   M   tCCS Minimum Change Column setup time (ns)   3CH   00H   141-163   Reserved   00H   Vendor block     164-165   M   Vendor specific Revision number   00H   166-253   Vendor specific   00H   254-255   M   Integrity CRC                                                                                                                                                                                                                                                                                  | 135-136  | М   | tBERS Maximum block erase time (us)                 |            |

| 137-138       M       tR Maximum page read time (us)       19H 00H         139-140       M       tCCS Minimum Change Column setup time (ns)       3CH 00H         141-163       Reserved       00H         Vendor block       00H         164-165       M       Vendor specific Revision number       00H         166-253       Vendor specific       00H         254-255       M       Integrity CRC                                                                                                                                                                                    | 133-130  | IVI | IDENO MAXIMUM BIOCK CLASC LINE (US)                 |            |

| 139-140   M   tCCS Minimum Change Column setup time (ns)   3CH   00H     141-163   Reserved   00H   Vendor block     164-165   M   Vendor specific Revision number   00H   166-253   Vendor specific   00H   254-255   M   Integrity CRC                                                                                                                                                                                                                                                                                                                                                 | 137_138  | M   | tP Maximum page read time (us)                      |            |

| 139-140         M         tCCS Minimum Change Column setup time (ns)         3CH 00H           141-163         Reserved         00H           Vendor block         00H           164-165         M         Vendor specific Revision number         00H           166-253         Vendor specific         00H           254-255         M         Integrity CRC                                                                                                                                                                                                                           | 137-130  | IVI | ut waximum page read time (ds)                      |            |

| 00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 130 140  | NA  | tCCS Minimum Change Column setup time (ns)          |            |

| 141-163         Reserved         00H           Vendor block         00H           164-165         M         Vendor specific Revision number         00H           166-253         Vendor specific         00H           254-255         M         Integrity CRC                                                                                                                                                                                                                                                                                                                          | 139-140  | IVI | 1 CCS Will influtiff Change Column setup time (fis) |            |

| Vendor block         00H           164-165         M         Vendor specific Revision number         00H           166-253         Vendor specific         00H           254-255         M         Integrity CRC                                                                                                                                                                                                                                                                                                                                                                         | 141 162  |     | Personal                                            |            |

| 164-165         M         Vendor specific Revision number         00H           166-253         Vendor specific         00H           254-255         M         Integrity CRC                                                                                                                                                                                                                                                                                                                                                                                                            | 141-103  |     |                                                     | ООП        |

| 166-253         Vendor specific         00H           254-255         M         Integrity CRC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 404.405  |     |                                                     | 2011       |

| 254-255 M Integrity CRC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          | M   |                                                     |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |     |                                                     | 00H        |

| Redundant parameter pages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 254-255  | М   |                                                     |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |     | Redundant parameter pages                           |            |

| 256-511 M Value of bytes 0-255                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 256-511  | М   | Value of bytes 0-255                                |            |

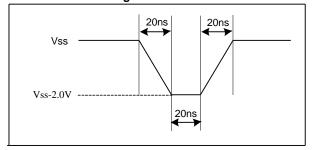

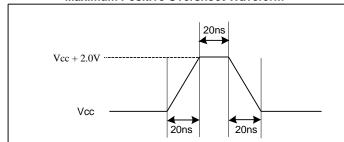

| 512-767 M Value of bytes 0-255                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 512-767  | М   | Value of bytes 0-255                                |            |