# GPFA32D1

## **32K Music Synthesizer**

Oct. 22, 2015

Version 1.1

GENERALPLUS TECHNOLOGY INC. reserves the right to change this documentation without prior notice. Information provided by GENERALPLUS TECHNOLOGY INC. is believed to be accurate and reliable. However, GENERALPLUS TECHNOLOGY INC. makes no warranty for any errors which may appear in this document. Contact GENERALPLUS TECHNOLOGY INC. to obtain the latest version of device specifications before placing your order. No responsibility is assumed by GENERALPLUS TECHNOLOGY INC. for any infringement of patent or other rights of third parties which may result from its use. In addition, GENERALPLUS products are not authorized for use as critical components in life support devices/systems or aviation devices/systems, where a malfunction or failure of the product may reasonably be expected to result in significant injury to the user, without the express written approval of Generalplus.

### **Table of Contents**

#### **PAGE**

| TA | BLE OF CONTENTS                                                                                          | 2  |

|----|----------------------------------------------------------------------------------------------------------|----|

| 32 | K MUSIC SYNTHESIZER                                                                                      | 3  |

| 1. | GENERAL DESCRIPTION                                                                                      | 3  |

| 2. | BLOCK DIAGRAM                                                                                            | 3  |

| 3. | FEATURES                                                                                                 | 3  |

| 4. | APPLICATION FIELDS                                                                                       | 3  |

| 5. | PAD ASSIGNMENT AND SIGNAL DESCRIPTIONS                                                                   | 4  |

|    | 5.1. SIGNAL DESCRIPTION                                                                                  | 4  |

| 6. | FUNCTION DESCRIPTION                                                                                     | 5  |

|    | 6.1. MEMORY MAPPING                                                                                      | 5  |

|    | 6.2. CPU                                                                                                 | 5  |

|    | 6.3. OSCILLATOR                                                                                          | 5  |

|    | 6.4. I/O PORT CONFIGURATION                                                                              | 5  |

|    | 6.5. KEY AND AUTO-WAKEUP                                                                                 | 6  |

|    | 6.6. INTERRUPT                                                                                           | 6  |

|    | 6.7. GENERATION OF SPEECH AND MELODY                                                                     | 6  |

|    | 6.8. POWER DOWN AND HALT MODE                                                                            | 6  |

|    | 6.9. MAIN VOLUME CONTROL FUNCTION                                                                        | 6  |

|    | 6.10.AUD CONTROL FUNCTION                                                                                | 6  |

| 7. | ELECTRICAL SPECIFICATIONS                                                                                | 7  |

|    | 7.1. ABSOLUTE MAXIMUM RATINGS                                                                            |    |

|    | 7.2. DC Characteristics (TA=25°C)                                                                        | 7  |

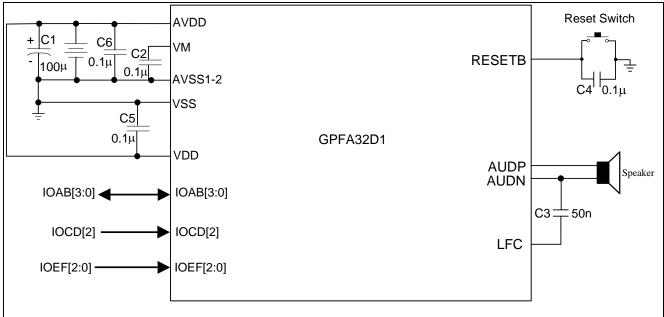

| 8. | APPLICATION CIRCUIT                                                                                      | 8  |

|    | 8.1. GPFA32D1 Application Circuits-(1): Application Circuit without External Resistor for Volume Control | 8  |

|    | 8.2. GPFA32D1 Application Circuits-(2): Application Circuit with External Resistor for Volume Control    | 9  |

|    | 8.3. GPFA32D1 Application Circuits-(3): Application Circuit for Microphone Audio Input                   | 10 |

| 9. | PACKAGE/PAD LOCATIONS                                                                                    | 11 |

|    | 9.1. Ordering Information                                                                                | 11 |

| 10 | DISCLAIMER                                                                                               | 12 |

| 11 | . REVISION HISTORY                                                                                       | 13 |

### **32K MUSIC SYNTHESIZER**

#### **1. GENERAL DESCRIPTION**

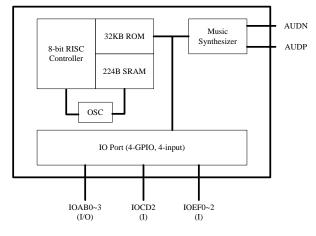

The GPFA32D1, a fully CMOS integrated circuit, adopts advanced design and process technology to combine an 8-bit RISC processor, an 8-channel music synthesizer, 32K bytes program ROM, 224 bytes working SRAM, timer/counter and I/Os interface in a single chip. The sound processing logic is a unique design to achieve high quality melody effect. It can simulate all types of musical instruments by programming the tone ROM and controlling the envelope slope of each channel. Every channel can also be defined as a speech channel to provide percussion, animal sounds, gun-fire, explosions and other special sound effects in PCM to accompany the main music rhythm.

#### 2. BLOCK DIAGRAM

#### 3. FEATURES

- 8-bit microprocessor

- 8-channel speech / melody

- Operating voltage: 2.2V 5.5V

- Four general inputs / outputs, IOAB0~3

- Four input pins, IOCD2 and IOEF0~2

- Two audio output pins drive speaker directly

- Watchdog mode (code option)

- 224 bytes SRAM

- 32K bytes program ROM

- Power down mode with system and auto wake-up clock stop

Halt mode with system clock stop, but keeping auto-wakeup clock working

- Built-in max. 14.318MHz Rosc

- Power-on reset

- Volume adjustment by 3-bit software control or external resistor

- Key-change and system auto wakeup capability

- Low voltage reset

#### 4. APPLICATION FIELDS

- Electronic piano

- Music clock

- Music box

- Children's storybook

#### 5. PAD ASSIGNMENT AND SIGNAL DESCRIPTIONS

#### 5.1. Signal Description

| Mnemonic  | PIN No. | Туре | Description                                                     |

|-----------|---------|------|-----------------------------------------------------------------|

| VDD       | 1       | I    | Positive supply voltage                                         |

| VSS       | 11      | I    | Ground input                                                    |

| RESETB    | 10      | I    | Reset input, active low, internal pull high                     |

| VM        | 17      | I    | Capacitor input ,should connect it with 0.1uF capacitor to AVSS |

| LFC       | 18      | I    | Capacitor input, should connect it with 50nF capacitor to AUDN  |

| AUDN      | 15      | 0    | Audio output                                                    |

| AUDP      | 13      |      |                                                                 |

| IOCD2     | 5       | I    | Data input pins                                                 |

| IOEF2 - 0 | 4 - 2   |      |                                                                 |

| IOAB3 - 0 | 9 - 6   | I/O  | Programmable input/output pins                                  |

| AVSS1     | 16      | I    | Analog VSS                                                      |

| AVSS2     | 12      |      |                                                                 |

| AVDD      | 14      | I    | Analog VDD                                                      |

#### 6. FUNCTION DESCRIPTION

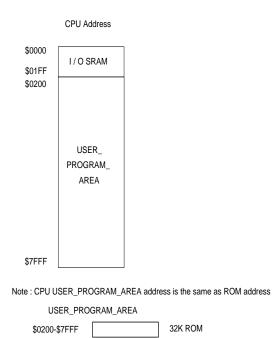

#### 6.1. Memory Mapping

#### 6.2. CPU

The 8-bit micro-processor of GPFA32D1 is a high performance processor equipped with Accumulator, Program Counter, X Register, Stack pointer, and Processor Status Register (this is the same as the 6502 instruction structure). GPFA32D1 is able to reach 7.16MHz (max.) performing speed depending on the application specifications.

#### 6.3. Oscillator

The GPFA32D1 provides an internal 14.318MHz ROSC for system clock source and it takes less cost and component for user's system. In addition to 14.318Mhz system clock, GPFA32D1 also equips a 41KHz ROSC that will be the auto wakeup clock source. The wakeup frequency can be 2.5Hz, 5Hz, 10Hz and 20Hz depending on bit-2&3 in P\_07H\_SleepWakeup. Note that the 41KHz ROSC can be activated only when system is under sleep mode and the relevant control register, P\_07\_SleepWakeup, in which bit-1 is written as "1".

**Note:** \*The frequency deviation for auto wakeup clock may be +-30%. **Note:** \*\*The frequency deviation for internal ROSC is +-3.5%.

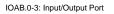

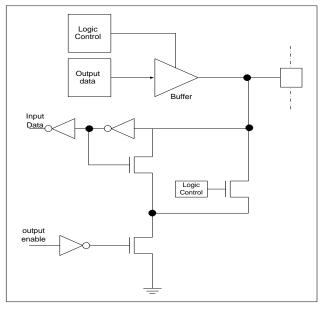

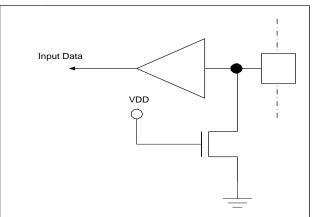

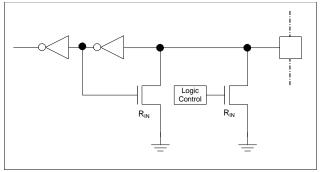

#### 6.4. I/O Port Configuration

## GPFA32D1

#### 6.5. Key and Auto-Wakeup

CPU waking up from sleep mode requires a wakeup signal to turn the system clock on. The wakeup sources of GPFA32D1 include IOEF.0-2 key change and auto wakeup.

#### 6.6. Interrupt

The GPFA32D1 has two interrupt modes: FIQ (Fast Interrupt Request) and IRQ (Interrupt Request). The priority of FIQ is higher than IRQ. FIQ is the high-priority interrupt while IRQ is low-priority. An IRQ can be interrupted by a FIQ, but not by another IRQ. A FIQ cannot be interrupted by any other interrupt source. The interrupt controller handles 7 INTs sources, which are depicted in the following table:

| Interrupt Source                   | Priority              |

|------------------------------------|-----------------------|

| Channel 3 interrupt                | IRQ                   |

| Channel 2 interrupt                | IRQ                   |

| Channel 1 interrupt                | IRQ                   |

| Channel 0 interrupt                | FIQ/IRQ (by program)* |

| T11 interrupt<br>(system CLK/4096) | IRQ                   |

| T8 interrupt<br>(system CLK/512)   | IRQ                   |

| External interrupt                 | IRQ                   |

Note: \*User can assign the priority to FIQ or IRQ via programming.

#### 6.7. Generation of Speech and Melody

The fixed address of RAM area \$0020 - \$005F is designed as address pointers and a data buffer for the 8 channel speech/melody generation. When a channel is defined as speech, the user sets the 16-bit address pointer to point to the ROM area. The data can directly be sent to DA in direct output mode. The EA register is used to control the volume of the speech at AUD output. If the channel is defined as a melody channel, user should set it to normal speech mode, fetch the chord and decode the note first. After that, the user should set the channel to melody mode, which selects the tone ROM for programming and controlling the envelope to choose an instrument. Then play the data to DA buffer in synchronous rhythm with the change of the time base (tempo).

#### 6.8. Power Down and Halt Mode

GPFA32D1 supports a power saving mode for those applications that need very low stand-by current. The user simply enables the wake-up sources, then stops the CPU clock by writing the SLPSTAR register. Thus CPU will go to stand-by and the RAM and I/O remain in their previous state until awoken. If auto wake-up is needed, the 41KHz ROSC enable bit, P\_07H\_SleepWakeup bit-1, should be written as "1" then stops the CPU clock but keeps auto wake-up clock working by writing the SLPSTAR register.

#### 6.9. Main Volume Control Function

The main volume adjustment of GPFA32D1 provides 3-bit (8 level) software control to adjust D/A output voltage. The software volume control register is P\_09\_Vol\_Ctrl bit0-2 and its default value is #05H that is about 60% of maximum volume. Users can adjust volume by writing different values into P\_09\_Vol\_Ctrl bit0-2. The larger value written, the larger volume is implemented.

#### 6.10. AUD Control Function

GPFA32D1 facilitates AUD output to drive speaker directly. In order to eliminate the start-up noise, it is not allowed to turn on the AUD enable control registers, P\_00H\_DACOP\_EN bit0-1, at the same time. Users should write the control registers with a interval which is not less than 10us. The AUD turn-on procedure should be as followings:

- 1. Set envelope data=00H, DAC data=80H.

- 2. Set P\_00H\_DACOP\_EN = 01H.

- 3. Delay 10us.

- 4. Set P\_00H\_DACOP\_EN = 03H.

If users would disable AUD output, it is also not allowed to turn-off the AUD control register at the same time, or the unexpected noise might be generated as well. The AUD turn-off procedure should be as followings:

- 1. Set envelope data=00H, DAC data=80H.

- 2. Set  $P_{00H}_{DACOP}_{EN} = 01H$ .

- 3. Delay 10us.

- 4. Set P\_00H\_DACOP\_EN = 00H.

#### Low Voltage Reset

The Low Voltage Reset (LVR), preventing system from running into malfunction state, will intend to reset all functions back to the initial states if the system power drops too low.

#### 7. ELECTRICAL SPECIFICATIONS

#### 7.1. Absolute Maximum Ratings

| Characteristics       | Symbol           | Ratings             |

|-----------------------|------------------|---------------------|

| DC Supply Voltage     | VDD              | < 7.0V              |

| Input Voltage Range   | V <sub>IN</sub>  | -0.5V to VDD + 0.5V |

| Operating Temperature | T <sub>A</sub>   | 0°C to +60°C        |

| Storage Temperature   | T <sub>STO</sub> | -50°℃ to +150°℃     |

Note: Stresses beyond those given in the Absolute Maximum Ratings table may cause permanent damage to the device. For normal operational conditions see AC/DC Electrical Characteristics.

#### 7.2. DC Characteristics (TA=25°C)

|                                       |                                           | Limit   |        |         |                              |                                            |  |

|---------------------------------------|-------------------------------------------|---------|--------|---------|------------------------------|--------------------------------------------|--|

| Characteristics                       | Symbol                                    | Min.    | Тур.   | Max.    | Unit                         | Test Condition                             |  |

| Operating Voltage                     | VDD                                       | 2.2     | -      | 5.5     | V                            | -                                          |  |

| Operating Current-1                   | I <sub>OP1</sub>                          | -       | 15.7   | -       | mA                           | F <sub>CPU</sub> = 7.16MHz @ 5.0V, no load |  |

| (internal DAC and Amplifier active)   |                                           | -       | 8.5    | -       | mA                           | F <sub>CPU</sub> = 7.16MHz @ 3.0V, no load |  |

| Operating Current-2                   |                                           | -       | 6.3    | -       | mA                           | F <sub>CPU</sub> = 7.16MHz @ 5.0V, no load |  |

| (internal DAC and Amplifier inactive) | I <sub>OP2</sub>                          | -       | 2.5    | -       | mA                           | F <sub>CPU</sub> = 7.16MHz @ 3.0V, no load |  |

| Standby Current                       | I <sub>STBY</sub>                         | -       | -      | 3.0     | μA                           | VDD = 5.0V                                 |  |

| OSC Frequency                         | F <sub>OSC2</sub>                         | -       | 14.318 | -       | MHz                          | VDD = 5.0V                                 |  |

|                                       |                                           |         |        |         | (Fosc2 (VDD_CORE)-14.318MHz) |                                            |  |

| Frequency lot deviation               | ⊿F <sub>osc2</sub> /<br>F <sub>osc2</sub> | -3.5    | -      | 3.5     | %                            | /14.318MHz, VDD_CORE =3.3V,                |  |

|                                       | FOSC2                                     |         |        |         |                              | For Internal OSC                           |  |

| Input High Level                      | V <sub>IH</sub>                           | 0.7*VDD | -      | -       | V                            | -                                          |  |

| Input Low Level                       | VIL                                       | -       | -      | 0.3*VDD | V                            | -                                          |  |

| Output High Current                   |                                           | -       | 17.0   | -       | mA                           | VDD = 5.0V, V <sub>OH</sub> = 0.8xVDD      |  |

| (IOAB[3:0])                           | I <sub>он</sub>                           | -       | 7.0    | -       | mA                           | VDD = 3.0V, V <sub>OH</sub> = 0.8xVDD      |  |

| Output Sink Current                   |                                           | -       | -42.0  | -       | mA                           | $VDD = 5.0V, V_{OL} = 0.2xVDD$             |  |

| (IOAB[2:0])                           | I <sub>OL</sub>                           | -       | -19.0  | -       | mA                           | $VDD = 3.0V, V_{OL} = 0.2xVDD$             |  |

| Output Sink Current                   | I <sub>OL</sub>                           | -       | -60.0  | -       | mA                           | $VDD = 5.0V, V_{OL} = 0.2xVDD$             |  |

| (IOAB[3])                             |                                           | -       | -28.0  | -       | mA                           | VDD = 3.0V, V <sub>OL</sub> = 0.2xVDD      |  |

| Input Pull-Low Resistor               | R <sub>PL</sub>                           | -       | 100    | -       | Kohm                         | VDD = 5.0V, VIN = VDD                      |  |

| (IOEF[2:0])                           |                                           | -       | 205    | -       | Kohm                         | VDD = 3.0V, VIN = VDD                      |  |

| Input Pull-Low Resistor               | R <sub>PL</sub>                           | -       | 100    | -       | Kohm                         | VDD = 5.0V, VIN = VDD                      |  |

| (IOCD2)                               |                                           | -       | 205    | -       | Kohm                         | VDD = 3.0V, VIN = VDD                      |  |

| CPU Clock                             | F <sub>CPU</sub>                          | -       | 7.16   | -       | MHz                          | F <sub>CPU</sub> = F <sub>OSC2</sub> /2    |  |

#### 8. APPLICATION CIRCUIT

Notes:

- 1. VDD, AVDD must connect to power input port directly.

- 2. VSS, AVSS1-2 must connect to power input port directly.

- **3.** For system stability, it is recommended to connect capacitors as illustrated. It is not allowed to remove C1~C3 due to possible performance or function issue. C4~C6 may be ignored depending on applications and PCB layout.

- 4. It is recommended C1=100uF but users could try other values depending on the application.

- 5. If C5/C6 used, C5/C6 should be as close as possible to VDD/VSS and AVDD/AVSS1-2.

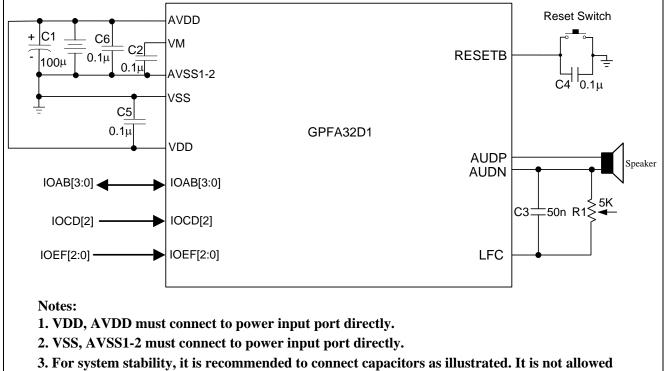

#### 8.2. GPFA32D1 Application Circuits-(2): Application Circuit with External Resistor for Volume Control

to remove C1~C3 due to possible performance or function issue. C4~C6 may be ignored depending on applications and PCB layout.

4. It is recommended C1=100uF but users could try other values depending on the application.

5. If C5/C6 used, C5/C6 should be as close as possible to VDD/VSS and AVDD/AVSS1-2.

6. Connecting variable resistor, R1(max.=5K), between LFC and AUDN for volume control

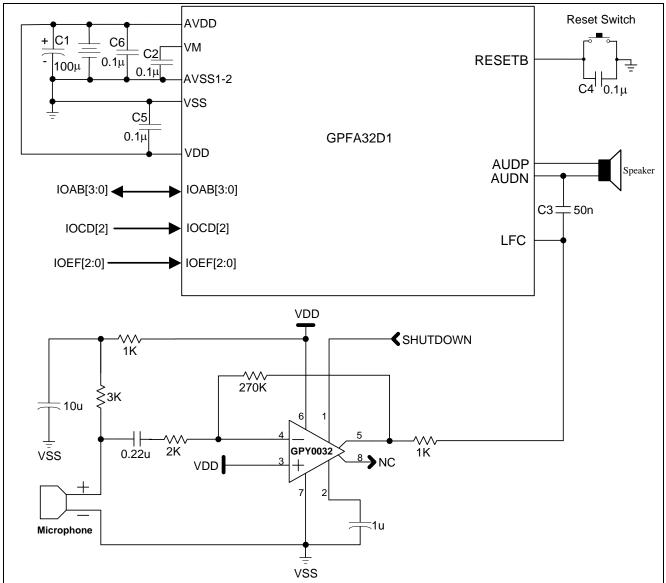

#### 8.3. GPFA32D1 Application Circuits-(3): Application Circuit for Microphone Audio Input

Notes:

- 1. VDD, AVDD must connect to power input port directly.

- 2. VSS, AVSS1-2 must connect to power input port directly.

- **3.** For system stability, it is recommended to connect capacitors as illustrated. It is not allowed to remove C1~C3 due to possible performance or function issue. C4~C6 may be ignored depending on applications and PCB layout.

- 4. It is recommended C1=100uF but users could try other values depending on the application.

- 5. If C5/C6 used, C5/C6 should be as close as possible to VDD/VSS and AVDD/AVSS1-2.

- 6. For microphone audio input application, external circuit is as illustrated. The SHUTDOWN signal to GPY0032 could be GPFA32D1 GPIO.

#### 9. PACKAGE/PAD LOCATIONS

#### 9.1. Ordering Information

| Product Number  | Package Type |

|-----------------|--------------|

| GPFA32D1-NnnV-A | Chip form    |

Note1: Code number is assigned for customer.

Note2: Code number (N = A - Z or 0 - 9, nn = 00 - 99); version (V = A - Z).

#### **10. DISCLAIMER**

The information appearing in this publication is believed to be accurate.

Integrated circuits sold by Generalplus Technology are covered by the warranty and patent indemnification provisions stipulated in the terms of sale only. GENERALPLUS makes no warranty, express, statutory implied or by description regarding the information in this publication or regarding the freedom of the described chip(s) from patent infringement. FURTHERMORE, GENERALPLUS MAKES NO WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PURPOSE. GENERALPLUS reserves the right to halt production or alter the specifications and prices at any time without notice. Accordingly, the reader is cautioned to verify that the data sheets and other information in this publications involving unusual environmental or reliability requirements, e.g. military equipment or medical life support equipment, are specifically not recommended without additional processing by GENERALPLUS for such applications. Please note that application circuits illustrated in this document are for reference purposes only.

#### **11. REVISION HISTORY**

| Date Revision # |     | Description                                   |    |  |  |

|-----------------|-----|-----------------------------------------------|----|--|--|

| Oct. 22, 2015   | 1.1 | Modify Internal OSC SPEC in section 6.3 & 7.2 |    |  |  |

| Aug. 31, 2015   | 1.0 | Original                                      | 13 |  |  |