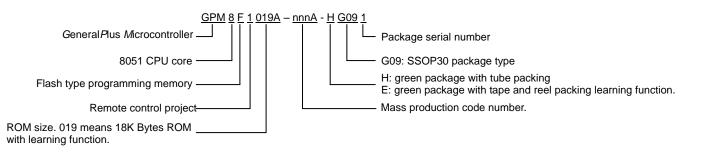

# GPM8F1129A GPM8F1065A GPM8F1033A GPM8F1019A

# 30/20-pin Microcontroller with 128/64/32/18KB Flash Memory

Jan. 21, 2015 Version 1.0

Generalplus Technology Inc. reserves the right to change this documentation without prior notice. Information provided by Generalplus Technology Inc. is believed to be accurate and reliable. However, Generalplus Technology Inc. makes no warranty for any errors which may appear in this document. Contact Generalplus Technology Inc. to obtain the latest version of device specifications before placing your order. No responsibility is assumed by Generalplus Technology Inc. for any infringement of patent or other rights of third parties which may result from its use. In addition, Generalplus products are not authorized for use as critical components in life support devices/systems or aviation devices/systems, where a malfunction or failure of the product may reasonably be expected to result in significant injury to the user, without the express written approval of Generalplus.

### **Table of Contents**

### **PAGE**

| ITal | ole o | f Contents                            | 2  |

|------|-------|---------------------------------------|----|

| 30/2 | 20 P  | N 8-BIT MICROCONTROLLER               | 5  |

| WIT  | TH 12 | 28/64/32/18KB FLASH                   | 5  |

| 1.   | GEN   | ERAL DESCRIPTION                      | 5  |

| 2.   | FEA   | rures                                 | 5  |

| 3.   | BLO   |                                       | 7  |

|      | 3.1.  | GPM8F1129A                            | 7  |

|      | 3.2.  | GPM8F1065A                            | 8  |

|      | 3.3.  | GPM8F1033A                            | 9  |

|      | 3.4.  | GPM8F1019A                            | 10 |

| 4.   | SIGN  | IAL DESCRIPTIONS                      | 11 |

|      | 4.1.  | PIN Map                               | 13 |

| 5.   | FUN   | CTIONAL DESCRIPTIONS                  | 14 |

|      | 5.1.  | CPU                                   | 14 |

|      |       | 5.1.1. CPU Features                   | 14 |

|      |       | 5.1.2. Arithmetic Logic Unit (ALU)    | 14 |

|      |       | 5.1.3. Accumulator A register         | 14 |

|      |       | 5.1.4. B Register                     | 14 |

|      |       | 5.1.5. Program Status Word (PSW)      | 14 |

|      |       | 5.1.6. Program Counter (PC)           | 14 |

|      | 5.2.  | Memory                                | 16 |

|      |       | 5.2.1. Introduction                   | 16 |

|      |       | 5.2.2. Program Memory Allocation      | 16 |

|      |       | 5.2.3. Data Memory Allocation         | 23 |

|      |       | 5.2.4. Memory Related SFR             | 24 |

|      |       | 5.2.4.1. Program write enable bit     | 24 |

|      |       | 5.2.4.2. Data pointer registers       | 24 |

|      |       | 5.2.4.3. Stack pointer                | 24 |

|      | 5.3.  | SPECIAL FUNCTION REGISTERS (SFR)      | 28 |

|      | 5.4.  | Power Saving Mode                     | 30 |

|      |       | 5.4.1. Introduction                   | 30 |

|      |       | 5.4.2. IDLE mode                      | 30 |

|      |       | 5.4.3. STOP mode                      | 30 |

|      | 5.5.  | INTERRUPT SYSTEM                      | 32 |

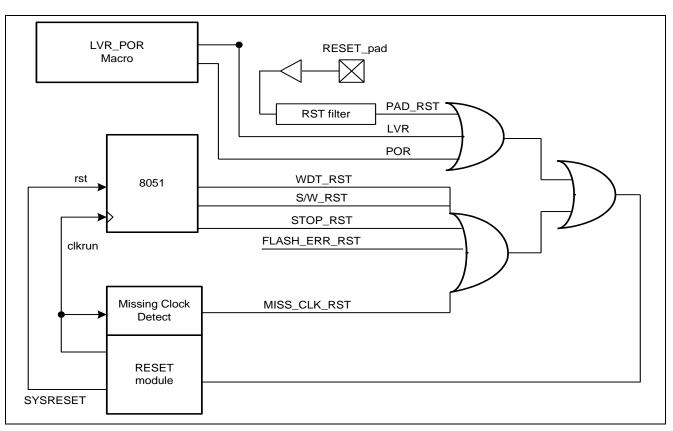

|      | 5.6.  | RESET SOURCE                          | 39 |

|      |       | 5.6.1. Introduction                   | 39 |

|      |       | 5.6.2. Power-On Reset (POR)           | 39 |

|      |       | 5.6.3. Low Voltage Reset (LVR)        | 39 |

|      |       | 5.6.4. Low Voltage Detection (LVD)    | 39 |

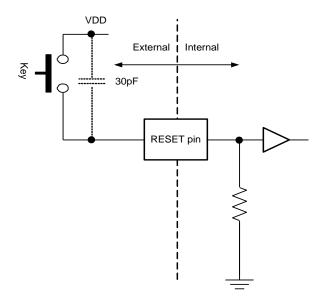

|      |       | 5.6.5. Pad Reset (PAD_RST)            | 39 |

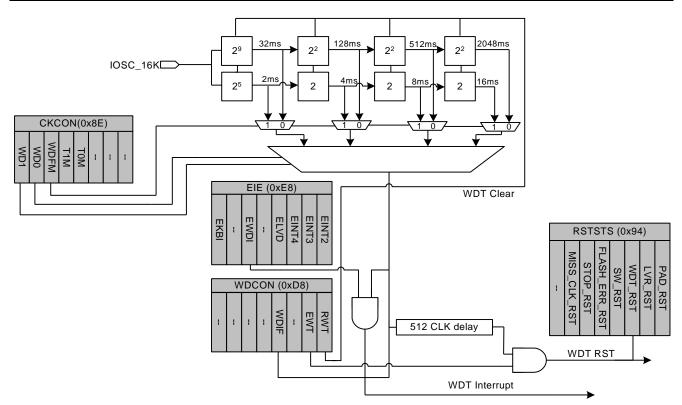

|      |       | 5.6.6. Watchdog Timer Reset (WDT_RST) | 40 |

| 5.6.7. Other Reset Sources                                                | 41 |

|---------------------------------------------------------------------------|----|

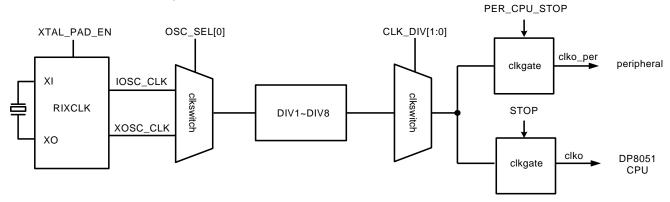

| 5.7. CLOCK SOURCE                                                         | 45 |

| 5.8. SLOW CLOCK                                                           | 47 |

| 5.9. I/O Ports                                                            | 47 |

| 5.10. TIMER MODULE                                                        | 54 |

| 5.10.1. Introduction                                                      | -  |

| 5.10.2. Timer 0/1                                                         |    |

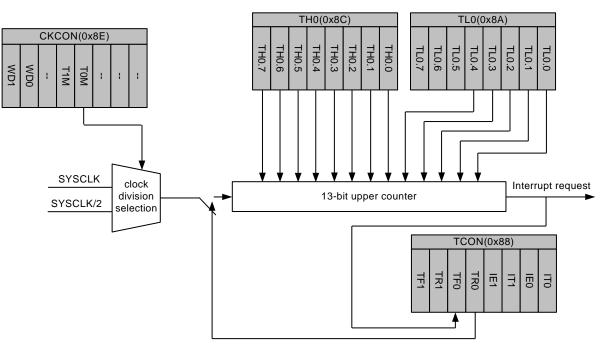

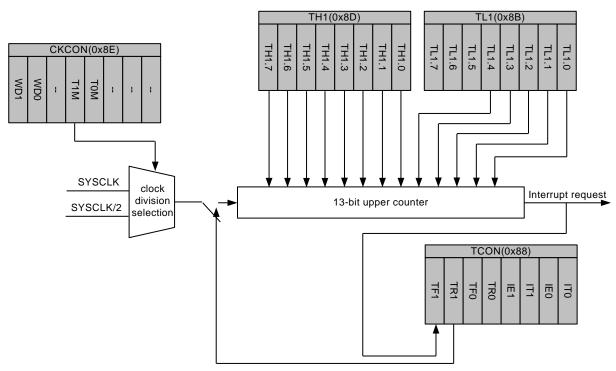

| 5.10.2.1. Timer 0: Mode 0(13-Bit Timer)                                   |    |

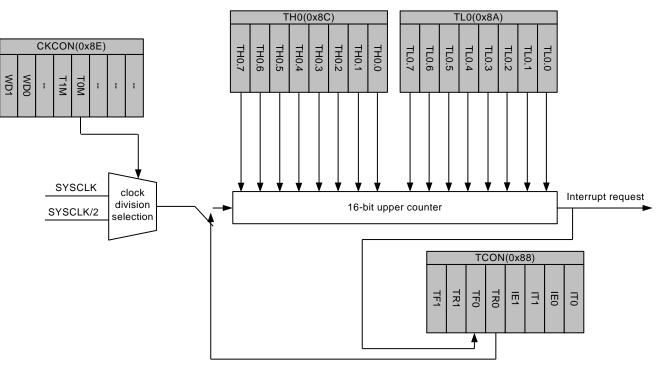

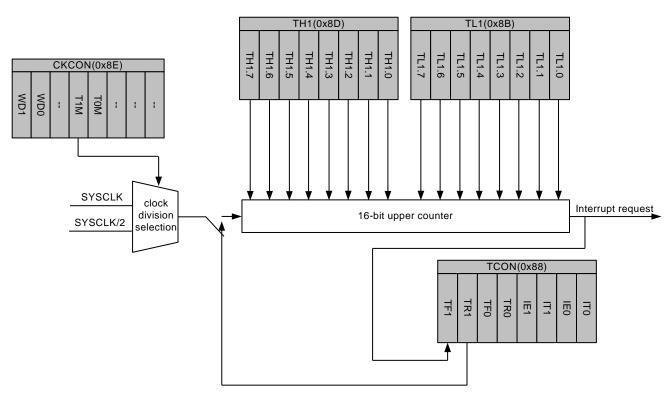

| 5.10.2.2. Timer 0: Mode 1(16-bit Timer)                                   |    |

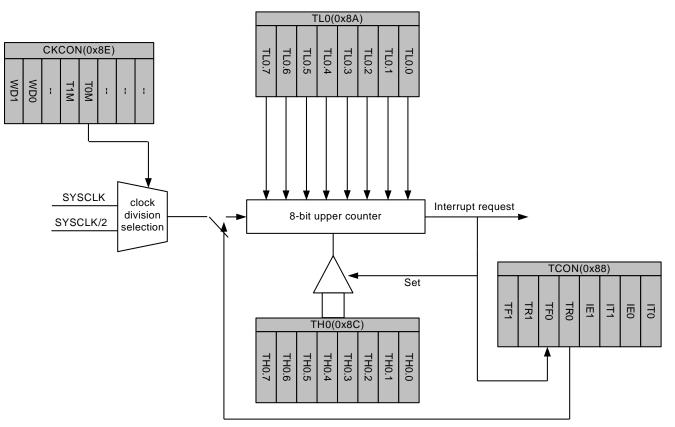

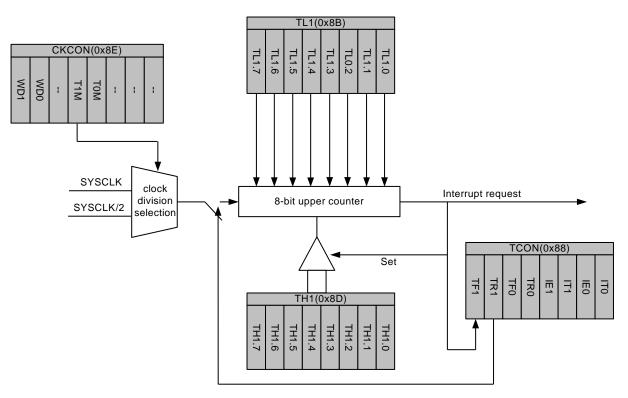

| 5.10.2.3. Timer 0: Mode 2(8-Bit Timer with Auto-reload Function)          |    |

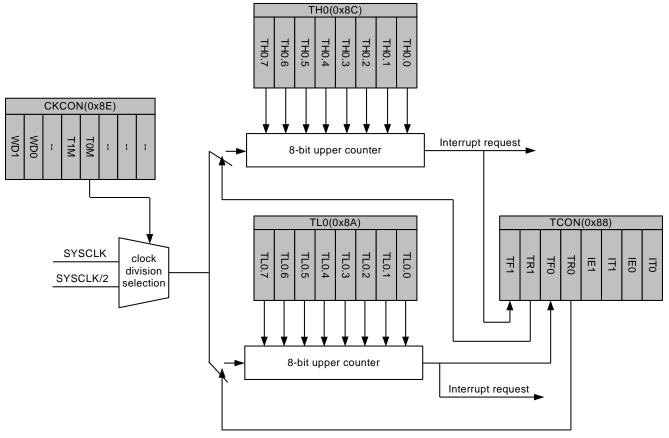

| 5.10.2.4. Timer 0: Mode 3(Two 8-Bit Timers)                               | 61 |

| 5.10.2.5. Timer 1: Mode 0(13-Bit Timer)                                   | 61 |

| 5.10.2.6. Timer 1: Mode 1(16-Bit Timer)                                   | 62 |

| 5.10.2.7. Timer 1: Mode 2(8-Bit Timer with Auto-reload Function)          | 63 |

| 5.10.2.8. Timer 1: Mode 3                                                 | 63 |

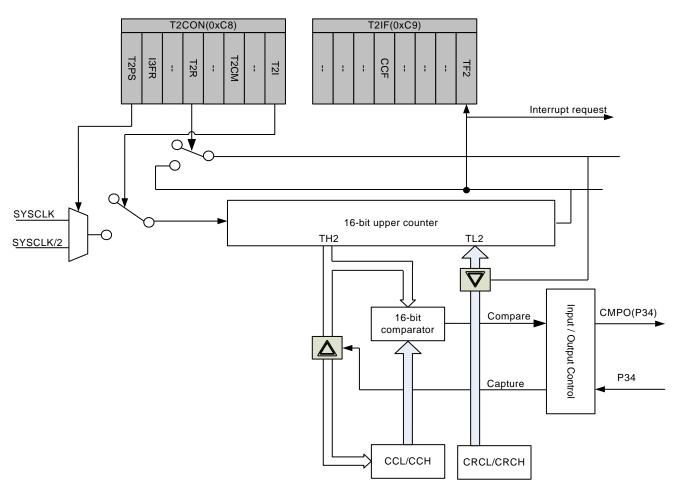

| 5.10.3. Timer 2                                                           | 64 |

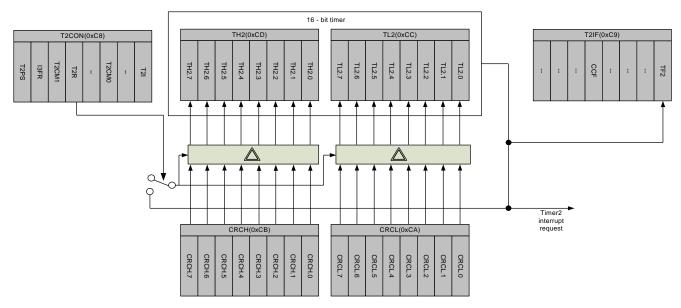

| 5.10.3.1. Timer Mode                                                      | 64 |

| 5.10.3.2. Reload of Timer 2                                               | 64 |

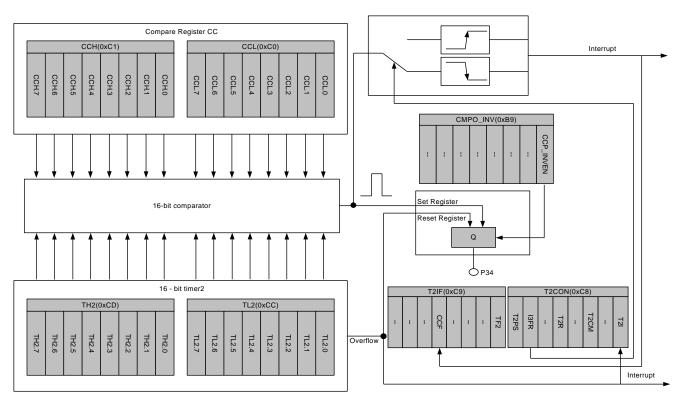

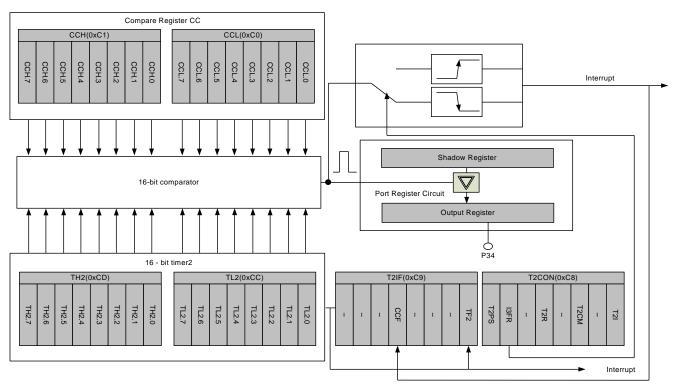

| 5.10.3.3. Compare Functions                                               | 65 |

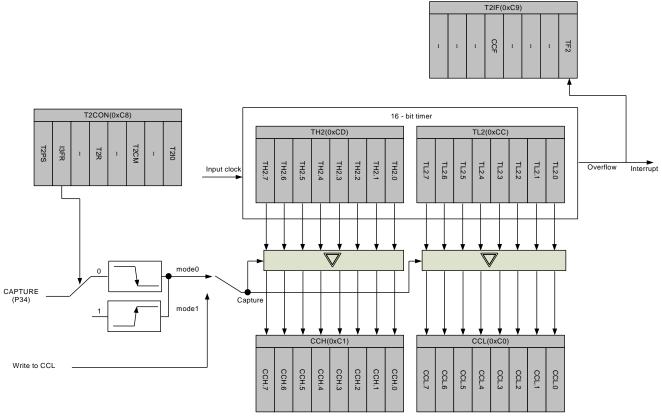

| 5.10.3.4. Capture Functions                                               | 67 |

| 5.10.3.5. Timer 2 Related Registers                                       | 68 |

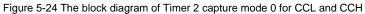

| 5.11. UART0                                                               | 71 |

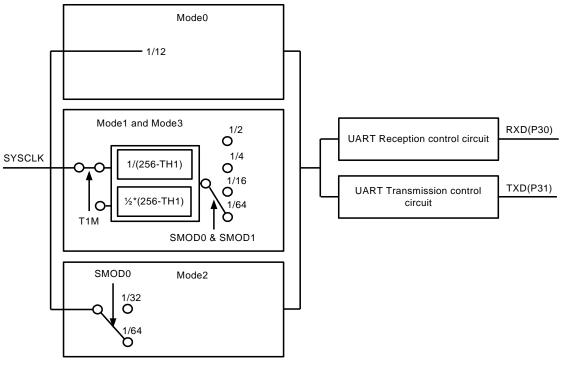

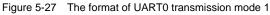

| 5.11.1.UART0: Mode 0(Synchronous Shift register)                          |    |

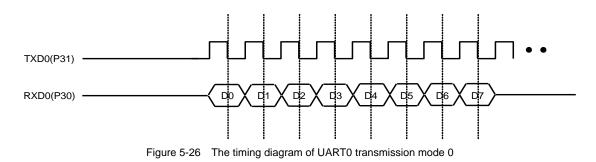

| 5.11.2.UART0: Mode 1(8-Bit UART, Variable Baud Rate, Timer1 Clock Source) |    |

| 5.11.3.UART0: Mode 2(9-Bit UART, Fixed Baud Rate)                         | 72 |

| 5.11.4.UART0: Mode 3(9-Bit UART, Variable Baud Rate, Timer1 Clock Source) | 72 |

| 5.11.5.UART0 Related Registers                                            | 72 |

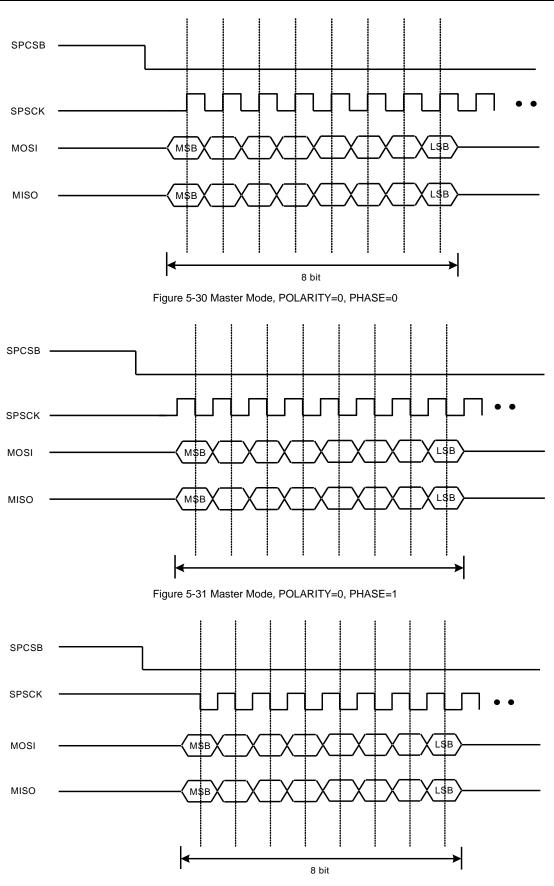

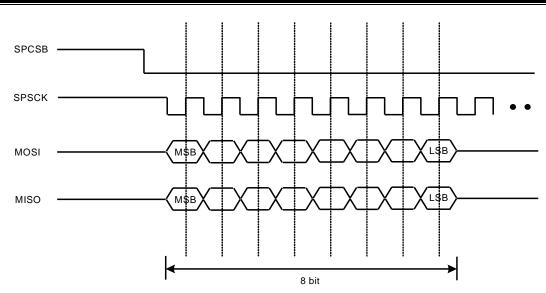

| 5.12. SPI                                                                 | 74 |

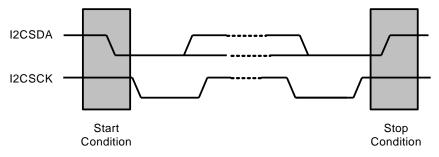

| 5.13. I2C                                                                 |    |

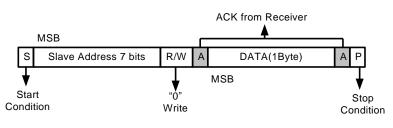

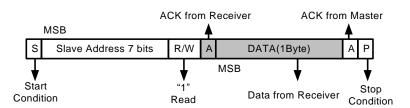

| 5.13.1. I2C Bus Protocol                                                  |    |

| 5.13.2. Bus Arbitration Procedures                                        | -  |

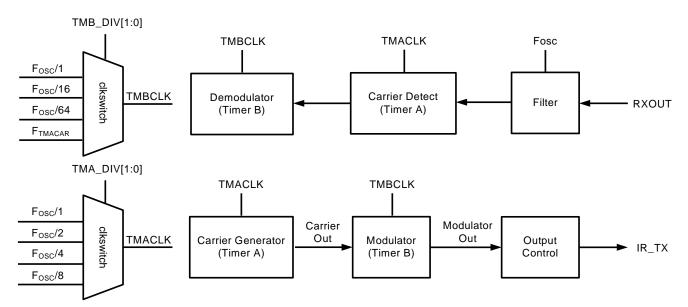

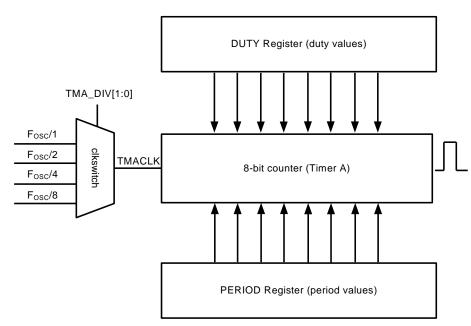

| 5.14.1. Carrier Generator                                                 | -  |

| 5.14.2. Modulator                                                         |    |

| 5.14.2.1. PWM output with carrier signal mode                             |    |

| 5.14.2.2. PWM output without carrier signal mode                          | 86 |

| 5.14.2.3. Direct control mode                                             | 86 |

| 5.14.3. Output control                                                    | 86 |

| 5.14.4. Extended space operation                                          |    |

| 5.14.5. Carrier detect and demodulator                                    |    |

| 5.15. ALPHABETICAL LIST OF INSTRUCTION SET                                | 93 |

| 5.15.1. Arithmetic Operations                                             | 93 |

|    |      | 5.15.2.  | Logic Operations                                | 93 |

|----|------|----------|-------------------------------------------------|----|

|    |      | 5.15.3.  | Boolean Operations                              | 94 |

|    |      | 5.15.4.  | Data Transfers                                  | 94 |

|    |      | 5.15.5.  | Program Branches                                | 96 |

| 6. | ELE  | CTRICAL  | CHARACTERISTICS                                 | 97 |

|    | 6.1. | ABSOLUT  | TE MAXIMUM RATING                               | 97 |

|    | 6.2. | DC CHA   | RACTERISTICS (VDD = 5V, $T_A = 25^{\circ}C$ )   | 97 |

|    | 6.3. | DC CHAR  | RACTERISTICS (VDD = 3.3V, $T_A = 25^{\circ}C$ ) | 97 |

|    | 6.4. | AC CHAF  | RACTERISTICS ( $T_A = 25^{\circ}C$ )            | 98 |

| 7. | APP  | LICATIO  | N CIRCUITS                                      | 99 |

|    |      |          | AD LOCATIONS                                    |    |

|    | 8.1. | Orderin  | IG INFORMATION                                  | 00 |

|    |      |          | E INFORMATION                                   |    |

| 9. | DISC | CLAIMER  |                                                 | 03 |

| 10 | REV  | ISION HI | STORY 1                                         | 04 |

### 30/20 PIN 8-BIT MICROCONTROLLER WITH 128/64/32/18KB FLASH

### **1. GENERAL DESCRIPTION**

The GPM8F1129A/GPM8F1065A/GPM8F1033A/GPM8F1019A, a highly integrated microcontroller, integrates a pipelined 1T 8051 CPU. 1.5K-byte XRAM, 256-byte IDM SRAM and 128K/64K/32K/18K-byte program Flash memory. It also contains a maximum of 23 programmable multi-functional I/Os, Timer0/1/2, UART0, SPI (master), I2C, and CMDT for a variety of applications. It operates over a wide voltage range from 1.8V through 5.5V and wide temperature range from -5  $^\circ\!{\rm C}\,$  ~ 70  $^\circ\!{\rm C}\,.~$  It features two power management modes for power saving purpose. To make development and debug work more easily, an on-chip debug circuit is included to facilitate full speed in-system debug. For more details about GPM8F series, please refer to the feature list in the following section.

### 2. FEATURES

- CPU

- High speed, high performance 1T 8051

- 100% software compatible with industry standard 8051

- Pipeline RISC architecture enhances executing instructions 10 times faster than standard 8051

- Up to 16MHz clock operation

- Memories

- 1.5K bytes XRAM

- 256 bytes internal Data Memory (IDM) SRAM

- Up to 128/64/32/18K bytes Flash with high endurance

- Minimum of 100K progam/erase cycles

- Minimum of 10 years data retention

- Page size 1kB

- Programming lock level for software security

#### Clock Management

- Internal oscillator: 16MHz±1.5% @ 2.0V~5.5V

- Crystal input with 1MHz~16MHz

- Slow Clock

- Internal oscillator: 4KHz

- Power Management

- One STOP mode for power saving

- One IDLE mode for only peripheral operation

- Interrupt Management

- Up to 9 internal interrupt sources

- Up to 5 external interrupt sources

- Up to 8 keyboard Interrupt sources

- Reset Management

- Power On Reset (POR)

- Low Voltage Reset (LVR)

- Pad Reset (PAD\_RST)

- Watchdog Reset (WDT\_RST)

- Software Reset (S/W\_RST)

- Stop mode Reset (STOP\_RST)

- Miss Clock Reset (MISS\_CLK\_RST)

- Flash Related Error Reset (FLASH\_ERR\_RST)

- Programmable Watchdog Timer

- A time-base generator

- An event timer

- System supervisor

- I/O Ports

- Max. 23 multifunction bi-directional I/Os

- Each incorporate with pull-up resistor, pull-down resistor, output high, output low or floating input, depending on the settings in the corresponding registers

- I/O ports with 12mA current sink

- I/O ports with 12mA current drive

- Two 16-bit Timer/Counter (Timer 0/1)

- Timer mode with clock source selectable

- Auto reload 8-bit timers

- One Powerful Timer2 with 16-bit Compare/Capture Unit

- Timer mode with clock source selectable

- Auto reload 16-bit timers

- Event capturing

- Digital signals generator

- Pulse width modulation and measurement

- UART0

- One synchronous mode

- Three asynchronous modes

- SPI (master mode)

- Programmable phase and polarity of master clock

- Programmable master clock frequency

- Auto read/write function

- Max SPI clock: 4MHz (F<sub>OSC</sub> /4) @16MHz

- I2C (master/slave mode)

- Carrier Modulator/Demodulator Timer (CMDT)

- One 8-bit Timer A for carrier generation and detection

- One 16-bit Timer B for envelop generation and detection

- Drives IR\_TX pin for remote control communication

- Receive IR signal from IR\_RX pin

- Built-in Low Voltage Reset

- Trigger level: 1.9V

- Built-in low Voltage Detect

- Programmable level: 2.3V, 2.5V, 3.3V, 3.5V

- On-chip Debug Unit

- C compatible Development Tools

|            | M. H. 60   | Speed | Flash  | IDM    | XDM    |      |          | CPU | OSC. |        |               |

|------------|------------|-------|--------|--------|--------|------|----------|-----|------|--------|---------------|

| Part NO.   | Voltage(V) | (MHz) | (Byte) | (Byte) | (Byte) | CMDT | IR Tx/Rx | INT | XTAL | IO No. | PKG           |

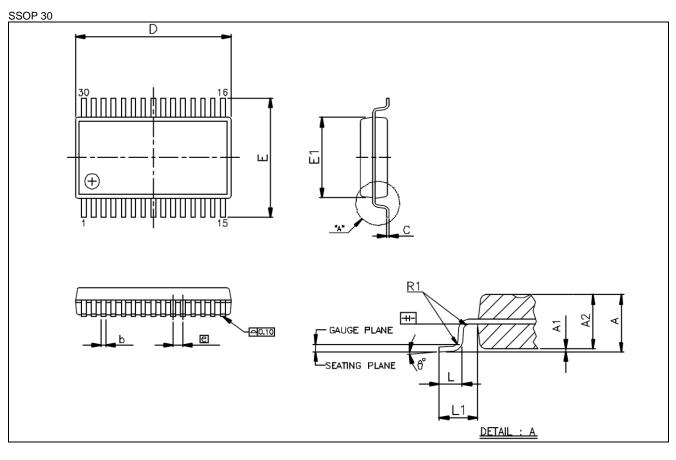

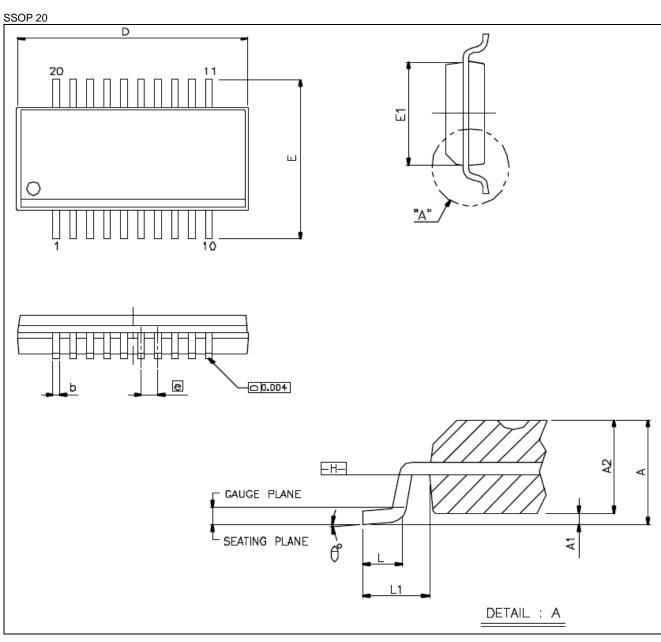

| GPM8F1129A | 1.8~5.5    | 16    | 128K   | 256    | 1.5k   | •    | Tx/Rx    | •   | •    | 23/15  | SSOP30/SSOP20 |

| GPM8F1065A | 1.8~5.5    | 16    | 64K    | 256    | 1.5k   | •    | Tx/Rx    | •   | •    | 23/15  | SSOP30/SSOP20 |

| GPM8F1033A | 1.8~5.5    | 16    | 32K    | 256    | 1.5k   | •    | Tx/Rx    | •   | •    | 23/15  | SSOP30/SSOP20 |

| GPM8F1019A | 1.8~5.5    | 16    | 18K    | 256    | 1.5k   | •    | Tx/Rx    | •   | •    | 23/15  | SSOP30/SSOP20 |

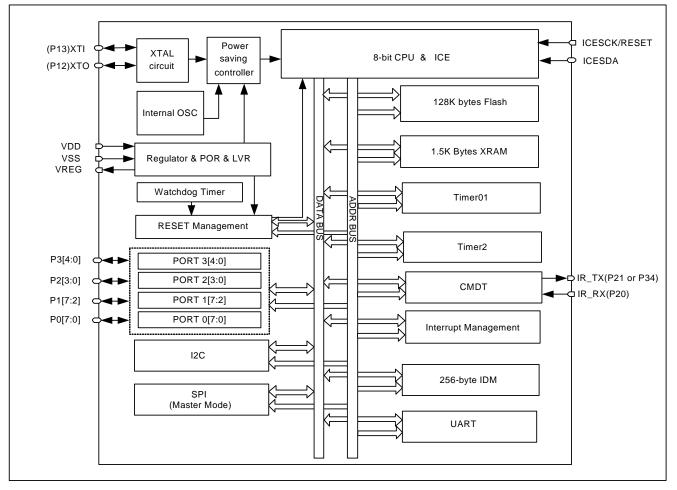

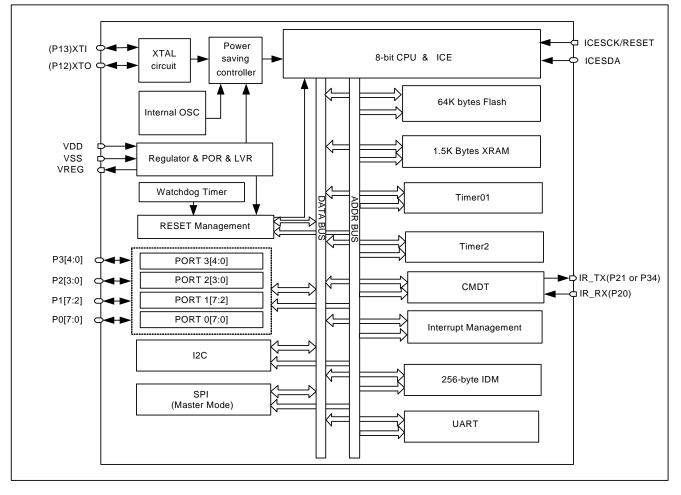

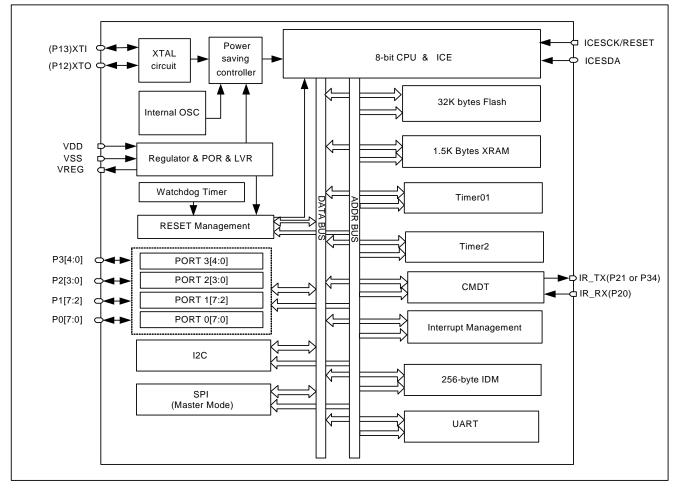

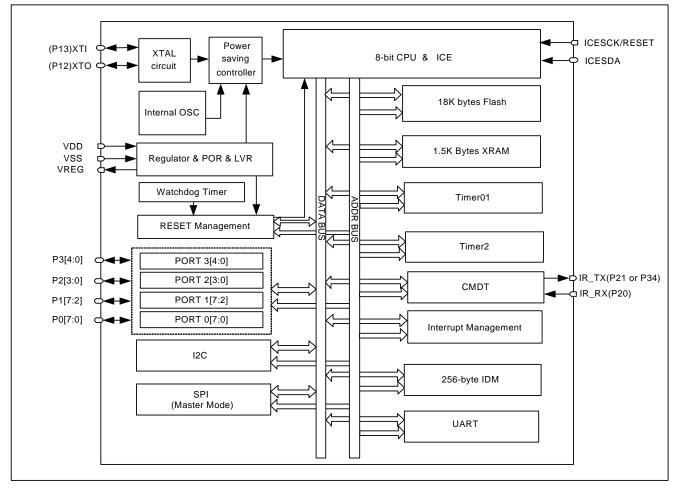

### 3. BLOCK DIAGRAM

### 3.1. GPM8F1129A

### 3.2. GPM8F1065A

### 3.3. GPM8F1033A

### 3.4. GPM8F1019A

### 4. SIGNAL DESCRIPTIONS

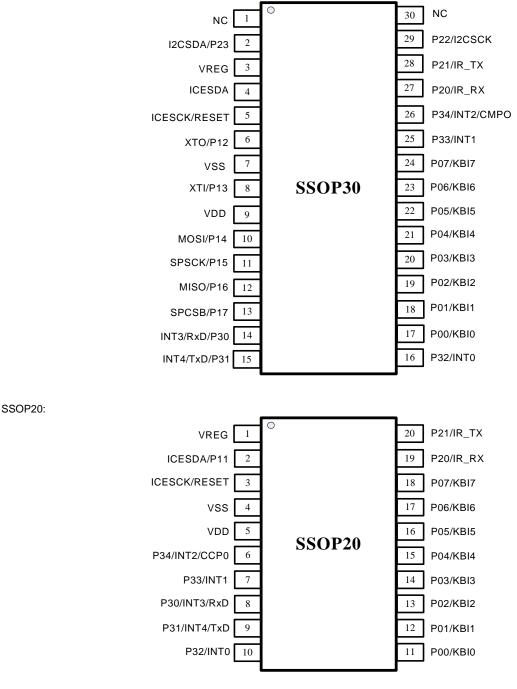

#### SSOP30:

Type: I = Input, O = Output, S = Supply

| Pin Name | SSOP30 | Туре | Description                       |  |  |  |  |

|----------|--------|------|-----------------------------------|--|--|--|--|

| NC       | 1      | NA   | Not connected                     |  |  |  |  |

| P23      | 2      | I/O  | Port 2's bit 3/ I2CSDA            |  |  |  |  |

| VREG     | 3      | S    | Regulator output                  |  |  |  |  |

| ICESDA   | 4      | I/O  | CE data input/output              |  |  |  |  |

| ICESCK   | 5      | I/O  | ICE clock input/ RESET            |  |  |  |  |

| P12      | 6      | I/O  | Port 1's bit 2/ XTO               |  |  |  |  |

| VSS      | 7      | S    | Ground                            |  |  |  |  |

| P13      | 8      | I/O  | Port 1's bit 3/ XTI               |  |  |  |  |

| VDD      | 9      | S    | Power 5V input                    |  |  |  |  |

| P14      | 10     | I/O  | Port 1's bit 4/ MOSI              |  |  |  |  |

| P15      | 11     | I/O  | Port 1's bit 5/ SPSCK             |  |  |  |  |

| P16      | 12     | I/O  | Port 1's bit 6/ MISO              |  |  |  |  |

| P17      | 13     | I/O  | Port 1's bit 7/ SPCSB             |  |  |  |  |

| P30      | 14     | I/O  | Port 3's bit 0/ RXD/ INT3         |  |  |  |  |

| P31      | 15     | I/O  | Port 3's bit 1/TXD/ INT4          |  |  |  |  |

| P32      | 16     | I/O  | Port 3's bit 2/ INT0              |  |  |  |  |

| P00      | 17     | I/O  | Port 0's bit 0/ KBI_0             |  |  |  |  |

| P01      | 18     | I/O  | Port 0's bit 1/KBI_1              |  |  |  |  |

| P02      | 19     | I/O  | Port 0's bit 2/ KBI_2             |  |  |  |  |

| P03      | 20     | I/O  | Port 0's bit 3/ KBI_3             |  |  |  |  |

| P04      | 21     | I/O  | Port 0's bit 6/ KBI_4             |  |  |  |  |

| P05      | 22     | I/O  | Port 0's bit 7/ KBI_5             |  |  |  |  |

| P06      | 23     | I/O  | Port 0's bit 6/ KBI_6             |  |  |  |  |

| P07      | 24     | I/O  | Port 0's bit 7/ KBI_7             |  |  |  |  |

| P33      | 25     | I/O  | Port 3's bit 3/ INT1              |  |  |  |  |

| P34      | 26     | I/O  | Port 3's bit 4/ INT2/ CMPO/ IR_TX |  |  |  |  |

| P20      | 27     | I/O  | Port 2's bit 0/ IR_RX             |  |  |  |  |

| P21      | 28     | I/O  | Port 2's bit 1/ IR_TX             |  |  |  |  |

| P22      | 29     | I/O  | Port 2's bit 2/ I2CSCK            |  |  |  |  |

| NC       | 30     | NA   | Not connected                     |  |  |  |  |

### SSOP20:

Type: I = Input, O = Output, S = Supply

| Pin Name | SSOP20 | Туре | Description                       |  |  |  |  |  |

|----------|--------|------|-----------------------------------|--|--|--|--|--|

| VREG     | 1      | S    | Regulator output                  |  |  |  |  |  |

| ICESDA   | 2      | I/O  | ICE data input/output             |  |  |  |  |  |

| ICESCK   | 3      | I/O  | ICE clock input/ RESET            |  |  |  |  |  |

| VSS      | 4      | S    | Ground                            |  |  |  |  |  |

| VDD      | 5      | S    | Power 5V input                    |  |  |  |  |  |

| P34      | 6      | I/O  | Port 3's bit 4/ INT2/ CMPO/ IR_TX |  |  |  |  |  |

| P33      | 7      | I/O  | Port 3's bit 3/ INT1              |  |  |  |  |  |

| P30      | 8      | I/O  | Port 3's bit 0/ RXD/ INT3         |  |  |  |  |  |

| P31      | 9      | I/O  | Port 3's bit 1/ TXD/ INT4         |  |  |  |  |  |

| P32      | 10     | I/O  | Port 3's bit 2/ INT0              |  |  |  |  |  |

| P00      | 11     | I/O  | Port 0's bit 0/ KBI_0             |  |  |  |  |  |

| P01      | 12     | I/O  | Port 0's bit 1/ KBI_1             |  |  |  |  |  |

| P02      | 13     | I/O  | Port 0's bit 2/ KBI_2             |  |  |  |  |  |

| P03      | 14     | I/O  | Port 0's bit 3/ KBI_3             |  |  |  |  |  |

| P04      | 15     | I/O  | Port 0's bit 6/ KBI_4             |  |  |  |  |  |

| P05      | 16     | I/O  | Port 0's bit 7/ KBI_5             |  |  |  |  |  |

| P06      | 17     | I/O  | Port 0's bit 6/ KBI_6             |  |  |  |  |  |

| P07      | 18     | I/O  | Port 0's bit 7/ KBI_7             |  |  |  |  |  |

| P20      | 19     | I/O  | Port 2's bit 0/ IR_RX             |  |  |  |  |  |

| P21      | 20     | I/O  | Port 2's bit 1/ IR_TX             |  |  |  |  |  |

### 4.1. PIN Map

SSOP30:

#### Note:

The pins which are not used is SSOP20 must be configured to avoid current leakage.

### **5. FUNCTION DESCRIPTION**

#### 5.1. CPU

The CPU is an ultra-high performance, high speed embedded microcontroller. Pipelined architecture enables the CPU 10 times faster than standard architecture. This performance can also be exploited to great advantage in low power application where the core can be clocked over ten times slower than original implementation for no performance penalty.

The CPU is fully compatible with industry standard 8051 microcontroller, maintaining all instruction mnemonics and binary compatibility. It incorporates some great architectural enhancements, allowing the CPU instructions execution with high performance and high speed.

#### 5.1.1. CPU Features

- □ 100 % software compatible with industry 8051

- 24 times faster multiplication operation

- 12 times faster addition operation

The CPU is fully compatible with industry standard 8051 microcontroller, maintaining all instruction mnemonics and binary compatibility. It incorporates some great architectural enhancements, allowing the CPU instructions execution with high performance and high speed.

The arithmetic section of the processor performs extensive data manipulation and is comprised of an 8-bit arithmetic logic unit (ALU), an ACC(0xE0) register, B(0xF0) register and PSW(0xD0) register.

#### 5.1.2. Arithmetic Logic Unit (ALU)

The ALU performs the arithmetic and logic operations during one instruction execution. Typical arithmetic operations are addition, subtraction, multiplication and division. Additional operations are

such as increment, decrement, BCD-decimal-add-adjust and compare. Within logic unit, operation such as AND, OR, Exclusive OR, complement and rotation are performed. The Boolean processor performs the bit operations as set, clear, complement, jump-if-not-set, jump-if-set-and-clear and move to/from carry.

#### 5.1.3. Accumulator A register

The accumulation is the 8-bit general-purpose register, which can be operated with data transfer, temporary saving, condition judgment, etc.

#### 5.1.4. B Register

The B register is used during multiplying and dividing operations. In other cases, it may be used as normal SFR.

#### 5.1.5. Program Status Word (PSW)

The PSW contains several bits that reflect the current state of the CPU which is similar to the flag-register of general CPU.

#### 5.1.6. Program Counter (PC)

The program counter is a 16-bit wide register. It consists of two 8-bit registers which are PCH and PCL. This register indicates the address of next instruction to be executed. In Reset state, the content of 0x0000 is stored into program counter.

The GPM8F1129A supports both LARGE mode and FLAT mode. The program counter is a 16-bit register in LARGE mode, but 23-bit register in FLAT mode. Switching between LARGE and FLAT modes is performed by appropriate writing into AM bit of ACON (0x9D) register.

| ACC      |   |   | Address: 0xE0 |    | Accumulator A Register |   |   |   |

|----------|---|---|---------------|----|------------------------|---|---|---|

| Bit      | 7 | 6 | 5             | 4  | 3                      | 2 | 1 | 0 |

| Function |   |   |               | AC | C[7:0]                 |   |   |   |

| Default  | 0 | 0 | 0             | 0  | 0                      | 0 | 0 | 0 |

| Bit Function |          | Туре | Description   | Condition |

|--------------|----------|------|---------------|-----------|

| 7:0          | ACC[7:0] | R/W  | Accumulator A |           |

Table 5-1 The ACC register

| В        |   |   | Address: 0xF0 |   | B Register |   |   |   |

|----------|---|---|---------------|---|------------|---|---|---|

| Bit      | 7 | 6 | 5             | 4 | 3          | 2 | 1 | 0 |

| Function |   |   |               | E | B[7:0]     |   |   |   |

| Default  | 0 | 0 | 0             | 0 | 0          | 0 | 0 | 0 |

| Bit | Function | Туре | Description | Condition |

|-----|----------|------|-------------|-----------|

| 7:0 | B[7:0]   | R/W  | В           |           |

Table 5-2 The B register

| PSW      |    |    | Address: 0xD0 | )   | Program Status Word Register |    |    |   |  |

|----------|----|----|---------------|-----|------------------------------|----|----|---|--|

| Bit      | 7  | 6  | 5             | 4   | 3                            | 2  | 1  | 0 |  |

| Function | CY | AC | F0            | RS1 | RS0                          | OV | F1 | Р |  |

| Default  | 0  | 0  | 0             | 0   | 0                            | 0  | 0  | 0 |  |

| Bit | Function | Туре | Description                                                                                                                                                                                                                  | Condition |

|-----|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 7   | CY       | R/W  | Carry flag                                                                                                                                                                                                                   |           |

| 6   | AC       | R/W  | Auxiliary carry flag                                                                                                                                                                                                         |           |

| 5   |          | R    | Reserved                                                                                                                                                                                                                     |           |

| 4:3 | RS[1:0]  | R/W  | Register bank select bits     RS[1:0]   Function description     00   Bank 0, data address 0x00-0x07     01   Bank 1, data address 0x08-0x0F     10   Bank 2, data address 0x10-0x17     11   Data 2, data address 0x10-0x17 |           |

| 2   | OV       | R/W  | 11 Bank 3, data address 0x18-0x1F   Overflow flag                                                                                                                                                                            |           |

| 1   |          | R    | Reserved                                                                                                                                                                                                                     |           |

| 0   | Р        | R/W  | Parity flag                                                                                                                                                                                                                  |           |

Table 5-3 The PSW register

| ACON     |   |     | Address: 0x9D |   | Address Control Register |   |    |   |

|----------|---|-----|---------------|---|--------------------------|---|----|---|

| Bit 7 6  |   | 5 4 |               | 3 | 2                        | 1 | 0  |   |

| Function |   |     |               |   |                          |   | AM |   |

| Default  | 0 | 0   | 0             | 0 | 0                        | 0 | 0  | 0 |

| Bit | Function | Туре | Description                                 | Condition |

|-----|----------|------|---------------------------------------------|-----------|

| 7:2 |          | R/W  | Reserved                                    |           |

| 1   | AM       | R/W  | Addressing Mode                             |           |

|     |          |      | 0: 16-bit Addressing Mode - LARGE           |           |

|     |          |      | 1: 23-bit Contiguous Addressing Mode - FLAT |           |

| 0   |          | R/W  | Reserved                                    |           |

Table 5-4 The ACON register (GPM8F1129A only)

### 5.2. Memory

### 5.2.1. Introduction

The GPM8F1129/1065/1033/1019A has three separated address spaces for program memory and data memory. The program memory is on-chip, re-programmable Flash memory and contains up to 128/ 64/ 32/ 18K bytes spaces. The data memory is divided into 1.5K bytes of external RAM, 256 bytes IDM SRAM with 128 bytes of SFR which can be read and written. The upper IDM and SFR use the same access address in different access ways, described in Figure 5-2.

#### 5.2.2. Program Memory Allocation

The GPM8F1129/ 1065/ 1033/ 1019A implement 128/ 64/ 32/ 18KB program memory size. The program memory allocation is divided into four parts, including first page, normal page, data flash and loader zone. The address space between 0x00000 and 0x03FF is called FIRST\_PAGE. It is used for reset vector, IRQ vectors, passwords and CONFIG\_BYTE. The CONFIG\_BYTE is located in 0x008F of program memory. The content of CONFIG\_BYTE also can be read from CONFIG\_BYTE register (0xB7) of SFR. The definition of CONFIG\_BYTE is shown in Table 5-5. The address space between 0x88 and 0x8b is used for passwords (i.e. PASSWD0~PASSWD3). If CONFIG\_BYTE[0] is programmed to be '0', the whole chip memory is protected and any page erase or program by two wire serial interface is not allowed. The only thing user can do is to erase the entire chip. A user can choose to allow or disallow the read operation of whole chip memory in code lock state by setting CONFIG\_BYTE[3] to "0". If CONFIG\_BYTE[3] is set to "0" and user-entered passwords match contents of PASSWD0~PASSWD3, the whole chip memory can be read even in code lock state. The address space between 0x0400 and 0x01CFFF/0xCFFF/0x4FFF/0x17FF is used for user code area. The last 12K bytes are used for data flash and loader zone

After each reset, CPU starts execution in the program memory at location 0x0000 or loader zone based on the value of 0x8E in Flash or 0xCF in SFR. The value of JMP\_LZ is 0xFF in default, and CPU will jump to loader zone after reset. Each interrupt has its own start address for service routine. The Flash memory can be programmed in-system, through the SCK/SDA interface or by software using the MOVX instruction when PWE= 1. Flash data cannot be programmed from a '0' to a '1', and can only be recognized by erase operation. Therefore, flash data will typically be erased (set to 0xFF) before being programmed. The write and erase operations are executed using PSIDLE (Pseudo-idle) mode to be automatically timed by hardware without data polling to determine the end of the write and erase operation.

For software security consideration, user can set the programmable Flash level by FL\_LEVEL register to limit the code area that avoids inadvertently erased or written by software; the protected region is called READONLY\_PAGE.

The GPM8F1129/ 1065/ 1033/ 1019A implements three control bytes for boot loader applications (i.e. JMP\_LZ, LZ\_SEL and The JMP\_LZ/LZ\_SEL/DF\_SEL is allocated in DF\_SEL). 0x8E/0x8D/0x8C of program memory. The reset vector of GPM8F1129/ 1065/ 1033/ 1019A can be changed to 0x1FC00/ 0xFC00/ 0x7C00/ 0x4400 by writing #0xFF to JMP\_LZ (0x8E of program memory). The LZ\_SEL is used to protect the content of loader zone. The DF\_SEL is used to protect the content of data flash when CPU is executing loader code. CPU should execute "JLMP 0x1FC00(GMP8F1129A) / 0xFC00(GMP8F1065A) / 0x7C00(GMP8F1033A) / 0x4400(GMP8F1019A)" instruction or write #0xFF to JMP\_LZ before executing loader code. The FIRST PAGE can be programmed or erased, when the loader code is in progress, Table 5-8, Table 5-9 and Table 5-10 show the definition of JMP\_LZ, LZ\_SEL and DF\_SEL respectively.

| First Page                               | 0x00000<br>0x003FF<br>0x00400 | First Page                               | 0x0000<br>0x03FF<br>0x0400 | First Page                               | 0x0000<br>0x03FF<br>0x0400 | First Page                               | 0x0000<br>0x03FF<br>0x0400 |

|------------------------------------------|-------------------------------|------------------------------------------|----------------------------|------------------------------------------|----------------------------|------------------------------------------|----------------------------|

| Normal Page                              |                               | Normal Page                              |                            | Normal Page                              |                            | Normal Page                              |                            |

|                                          | 0x1CFFF                       |                                          | 0xCFFF                     |                                          | 0x4FFF                     |                                          | 0x17FF                     |

| Data Flash+<br>Loader Zone<br>(12KBytes) | 0x1D000<br>0x1FFFF            | Data Flash+<br>Loader Zone<br>(12KBytes) | 0xD000<br>0xFFFF           | Data Flash+<br>Loader Zone<br>(12KBytes) | 0x5000<br>0x7FFF           | Data Flash+<br>Loader Zone<br>(12KBytes) | 0x1800<br>0x47FF           |

| GPM8F1129A                               | - ·                           | GPM8F1065A                               | -                          | GPM8F1033A                               | -                          | GPM8F1019A                               | - UX4/FF                   |

Figure 5-1 Program memory organization

| CONFIG_BYTE |   |   | Address: 0 | (B7 | CONFIG_BYTE Register |   |       |             |

|-------------|---|---|------------|-----|----------------------|---|-------|-------------|

| Bit         | 7 | 6 | 5          | 4   | 3                    | 2 | 1     | 0           |

| Function    |   | - |            |     | PWENB                |   | IOSEL | CODE_UNLOCK |

| Default     | 1 | 1 | 1          | 1   | 1                    | 1 | 1     | 1           |

| Bit | Function    | Туре | Description                                                                                      | Condition |

|-----|-------------|------|--------------------------------------------------------------------------------------------------|-----------|

| 7:4 |             | R    | Reserved                                                                                         |           |

| 3   | PWENB       | R/W  | Password mechanism enable bit<br>0: Passwords mechanism enable<br>1: Passwords mechanism disable |           |

| 2   |             | R    | Reserved                                                                                         |           |

| 1   | IOSEL       | R/W  | IO initial state selection bit<br>0: Input pull high<br>1: floating                              |           |

| 0   | CODE_UNLOCK | R/W  | Program memory protection enable bits<br>0: CODE is locked<br>1: CODE is unlocked                |           |

Note: default value of CONFIG\_BYTE = 0xFF

Table 5-5 CONFIG\_BYTE description

| FL_LEVEL |   |   | Address: 0xED    |   | Flash Level R | egister |   |   |

|----------|---|---|------------------|---|---------------|---------|---|---|

| Bit      | 7 | 6 | 5                | 4 | 3             | 2       | 1 | 0 |

| Function |   |   | FLASH LEVEL[6:0] |   |               |         |   |   |

| Default  | 1 |   |                  |   |               |         | 1 |   |

| Bit | Function         | Туре | Description                                              | Condition |

|-----|------------------|------|----------------------------------------------------------|-----------|

| 7   |                  | R/W  | Reserved                                                 |           |

| 6:0 | FLASH_LEVEL[6:0] | R/W  | FLASH_LEVEL, it determines the number of 1K page is read |           |

|     |                  |      | only, shown in the following table.                      |           |

|     |                  |      | Note 1. Only FLASH_LEVEL[4:0] is useful in GPM8F1019A    |           |

|     |                  |      | Note 2. Only FLASH_LEVEL[4:0] is useful in GPM8F1033A    |           |

|     |                  |      | Note 3. Only FLASH_LEVEL[5:0] is useful in GPM8F1065A    |           |

|     |                  |      | Note 4. Only FLASH_LEVEL[6:0] is useful in GPM8F1129A    |           |

Table 5-6 The FL\_LEVEL register

| FLASH_LEVEL | Note                          | FLASH_LEVEL | Note                           |

|-------------|-------------------------------|-------------|--------------------------------|

| 0x00        | no page is read only          | 0x40        | address < 0x10400 is read only |

| 0x01        | address < 0x800 is read only  | 0x41        | address < 0x10800 is read only |

| 0x02        | address < 0xC00 is read only  | 0x42        | address < 0x10C00 is read only |

| 0x03        | address < 0x1000 is read only | 0x43        | address < 0x11000 is read only |

| 0x04        | address < 0x1400 is read only | 0x44        | address < 0x11400 is read only |

| 0x05        | address < 0x1800 is read only | 0x45        | address < 0x11800 is read only |

| 0x06        | address < 0x1C00 is read only | 0x46        | address < 0x11C00 is read only |

| 0x07        | address < 0x2000 is read only | 0x47        | address < 0x12000 is read only |

| 0x08        | address < 0x2400 is read only | 0x48        | address < 0x12400 is read only |

| 0x09        | address < 0x2800 is read only | 0x49        | address < 0x12800 is read only |

| FLASH_LEVEL | Note                          | FLASH_LEVEL | Note                           |

|-------------|-------------------------------|-------------|--------------------------------|

| 0x0A        | address < 0x2C00 is read only | 0x4A        | address < 0x12C00 is read only |

| 0x0B        | address < 0x3000 is read only | 0x4B        | address < 0x13000 is read only |

| 0x0C        | address < 0x3400 is read only | 0x4C        | address < 0x13400 is read only |

| 0x0D        | address < 0x3800 is read only | 0x4D        | address < 0x13800 is read only |

| 0x0E        | address < 0x3C00 is read only | 0x4E        | address < 0x13C00 is read only |

| 0x0F        | address < 0x4000 is read only | 0x4F        | address < 0x14000 is read only |

| 0x10        | address < 0x4400 is read only | 0x50        | address < 0x14400 is read only |

| 0x11        | address < 0x4800 is read only | 0x51        | address < 0x14800 is read only |

| 0x12        | address < 0x4C00 is read only | 0x52        | address < 0x14C0 is read only  |

| 0x13        | address < 0x5000 is read only | 0x53        | address < 0x15000 is read only |

| 0x14        | address < 0x5400 is read only | 0x54        | address < 0x15400 is read only |

| 0x15        | address < 0x5800 is read only | 0x55        | address < 0x15800 is read only |

| 0x16        | address < 0x5C00 is read only | 0x56        | address < 0x15C00 is read only |

| 0x17        | address < 0x6000 is read only | 0x57        | address < 0x16000 is read only |

| 0x18        | address < 0x6400 is read only | 0x58        | address < 0x16400 is read only |

| 0x19        | address < 0x6800 is read only | 0x59        | address < 0x16800 is read only |

| 0x1A        | address < 0x6C00 is read only | 0x5A        | address < 0x16C00 is read only |

| 0x1B        | address < 0x7000 is read only | 0x5B        | address < 0x17000 is read only |

| 0x1C        | address < 0x7400 is read only | 0x5C        | address < 0x17400 is read only |

| 0x1D        | address < 0x7800 is read only | 0x5D        | address < 0x17800 is read only |

| 0x1E        | address < 0x7C00 is read only | 0x5E        | address < 0x17C00 is read only |

| 0x1F        | address < 0x8000 is read only | 0x5F        | address < 0x18000 is read only |

| 0x20        | address < 0x8400 is read only | 0x60        | address < 0x18400 is read only |

| 0x21        | address < 0x8800 is read only | 0x61        | address < 0x18800 is read only |

| 0x22        | address < 0x8C00 is read only | 0x62        | address < 0x18C00 is read only |

| 0x23        | address < 0x9000 is read only | 0x63        | address < 0x19000 is read only |

| 0x24        | address < 0x9400 is read only | 0x64        | address < 0x19400 is read only |

| 0x25        | address < 0x9800 is read only | 0x65        | address < 0x19800 is read only |

| 0x26        | address < 0x9C00 is read only | 0x66        | address < 0x19C00 is read only |

| 0x27        | address < 0xA000 is read only | 0x67        | address < 0x1A000 is read only |

| 0x28        | address < 0xA400 is read only | 0x68        | address < 0x1A400 is read only |

| 0x29        | address < 0xA800 is read only | 0x69        | address < 0x1A800 is read only |

| 0x2A        | address < 0xAC00 is read only | 0x6A        | address < 0x1AC00 is read only |

| 0x2B        | address < 0xB000 is read only | 0x6B        | address < 0x1B000 is read only |

| 0x2C        | address < 0xB400 is read only | 0x6C        | address < 0x1B400 is read only |

| 0x2D        | address < 0xB800 is read only | 0x6D        | address < 0x1B800 is read only |

| 0x2E        | address < 0xBC00 is read only | 0x6E        | address < 0x1BC00 is read only |

| 0x2F        | address < 0xC000 is read only | 0x6F        | address < 0x1C000 is read only |

| 0x30        | address < 0xC400 is read only | 0x70        | address < 0x1C400 is read only |

| 0x31        | address < 0xC800 is read only | 0x71        | address < 0x1C800 is read only |

| 0x32        | address < 0xCC00 is read only | 0x72        | address < 0x1CC00 is read only |

| 0x33        | address < 0xD000 is read only | 0x73        | address < 0x1D000 is read only |

| 0x34        | address < 0xD400 is read only | 0x74        | address < 0x1D400 is read only |

| 0x35        | address < 0xD800 is read only | 0x75        | address < 0x1D800 is read only |

| 0x36        | address < 0xDC00 is read only | 0x76        | address < 0x1DC00 is read only |

| FLASH_LEVEL | Note                           | FLASH_LEVEL | Note                           |

|-------------|--------------------------------|-------------|--------------------------------|

| 0x37        | address < 0xE000 is read only  | 0x77        | address < 0x1E000 is read only |

| 0x38        | address < 0xE400 is read only  | 0x78        | address < 0x1E400 is read only |

| 0x39        | address < 0xE800 is read only  | 0x79        | address < 0x1E800 is read only |

| 0x3A        | address < 0xEC00 is read only  | 0x7A        | address < 0x1EC00 is read only |

| 0x3B        | address < 0xF000 is read only  | 0x7B        | address < 0x1F000 is read only |

| 0x3C        | address < 0xF400 is read only  | 0x7C        | address < 0x1F400 is read only |

| 0x3D        | address < 0xF800 is read only  | 0x7D        | address < 0x1F800 is read only |

| 0x3E        | address < 0xFC00 is read only  | 0x7E        | address < 0x1FC00 is read only |

| 0x3F        | address < 0x10000 is read only | 0x7F        | address < 0x20000 is read only |

Table 5-7 The description of FL\_LEVEL register

| JMP_LZ   |         |  | dress: 0x008E<br>ogram Memory |      | Jump to Loader Zone Control Register |   |   |   |

|----------|---------|--|-------------------------------|------|--------------------------------------|---|---|---|

| Bit      | 7 6 5 4 |  |                               |      | 3                                    | 2 | 1 | 0 |

| Function |         |  |                               | JMP_ | LZ[7:0]                              |   |   |   |

| Default  |         |  |                               |      |                                      | 1 | 1 | 1 |

| Bit | Function    | Туре | Description                                                  | Condition |

|-----|-------------|------|--------------------------------------------------------------|-----------|

| 7:0 | JMP_LZ[7:0] | R/W  | CPU jumps to loader zone control bits                        |           |

|     |             |      | #0x55: After each reset, CPU starts execution in the program |           |

|     |             |      | memory at location 0x0000                                    |           |

|     |             |      | #0xFF: After each reset, CPU starts execution in the program |           |

|     |             |      | memory at location 0x1FC00 (GPM8F1129A)/                     |           |

|     |             |      | 0xFC00(GPM8F1065A)/                                          |           |

|     |             |      | 0x7C00(GPM8F1033A)/                                          |           |

|     |             |      | 0x4400(GPM8F1019A)                                           |           |

Table 5-8 The JMP\_LZ register

| LZ_SEL   |   |     | dress: 0x008D |    | Loader Zone Area Control Register |             |   |   |  |

|----------|---|-----|---------------|----|-----------------------------------|-------------|---|---|--|

|          |   | (Pi | ogram Memory  | () |                                   |             |   |   |  |

| Bit      | 7 | 6   | 5             | 4  | 3                                 | 2           | 1 | 0 |  |

| Function |   |     |               |    |                                   | LZ_SEL[2:0] |   |   |  |

| Default  | 1 | 1   | 1             | 1  | 1                                 | 1           | 1 | 1 |  |

| Bit | Function    | Туре | Description                                                                                                                                                                                                                                                 | Condition |

|-----|-------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 7:3 |             | R    | Reserved                                                                                                                                                                                                                                                    |           |

| 2:0 | LZ_SEL[2:0] | R/W  | Loader zone area control bits     GPM8F1129A:     000   No loader zone selected     001   The size of loader zone is 1K bytes (0x1FC00~0x1FFFF)<br>and it cannot be programmed by software.     010   The size of loader zone is 2K bytes (0x1F800~0x1FFFF) |           |

|     |             |      | and it cannot be programmed by software.     011   The size of loader zone is 3K bytes (0x1F400~0x1FFFF) and it cannot be programmed by software.                                                                                                           |           |

| Bit | Function | Туре |        | Description                                                                                  | Condition |

|-----|----------|------|--------|----------------------------------------------------------------------------------------------|-----------|

|     |          |      | 100    | The size of loader zone is 4K bytes (0x1F000~0x1FFFF)                                        |           |

|     |          |      |        | and it cannot be programmed by software.                                                     |           |

|     |          |      | GPM8F1 | 065A:                                                                                        |           |

|     |          |      | 000    | No loader zone selected                                                                      |           |

|     |          |      | 001    | The size of loader zone is 1K bytes (0xFC00~0xFFFF) and it cannot be programmed by software. |           |

|     |          |      | 010    | The size of loader zone is 2K bytes (0xF800~0xFFFF) and it cannot be programmed by software. |           |

|     |          |      | 011    | The size of loader zone is 3K bytes (0xF400~0xFFFF) and it cannot be programmed by software. |           |

|     |          |      | 100    | The size of loader zone is 4K bytes (0xF000~0xFFFF) and it cannot be programmed by software. |           |

|     |          |      | GPM8F1 |                                                                                              |           |

|     |          |      | 000    | No loader zone selected                                                                      |           |

|     |          |      | 001    | The size of loader zone is 1K bytes (0x7C00~0x7FFF) and                                      |           |

|     |          |      |        | it cannot be programmed by software.                                                         |           |

|     |          |      | 010    | The size of loader zone is 2K bytes (0x7800~0x7FFF) and it cannot be programmed by software. |           |

|     |          |      | 011    | The size of loader zone is 3K bytes (0x7400~0x7FFF) and it cannot be programmed by software. |           |

|     |          |      | 100    | The size of loader zone is 4K bytes (0x7000~0x7FFF) and it cannot be programmed by software. |           |

|     |          |      | GPM8F1 |                                                                                              |           |

|     |          |      | 000    | No loader zone selected                                                                      |           |

|     |          |      | 000    | The size of loader zone is 1K bytes (0x4400~0x47FF) and                                      |           |

|     |          |      |        | it cannot be programmed by software.                                                         |           |

|     |          |      | 010    | The size of loader zone is 2K bytes (0x4000~0x47FF) and                                      |           |

|     |          |      | -      | it cannot be programmed by software.                                                         |           |

|     |          |      | 011    | The size of loader zone is 3K bytes (0x3C00~0x47FF) and                                      |           |

|     |          |      | ┣───   | it cannot be programmed by software.                                                         |           |

|     |          |      | 100    | The size of loader zone is 4K bytes (0x3800~0x47FF) and                                      |           |

|     |          |      |        | it cannot be programmed by software.                                                         |           |

Table 5-9 The LZ\_SEL register

| DF_SEL   |   |   | dress: 0x008C<br>ogram Memory |   | Data Flash Area Control Register |   |   |   |  |

|----------|---|---|-------------------------------|---|----------------------------------|---|---|---|--|

| Bit 7 6  |   |   | 5                             | 4 | 3                                | 2 | 1 | 0 |  |

| Function |   |   |                               |   | DF_SEL[3:0]                      |   |   |   |  |

| Default  | 1 | 1 | 1                             | 1 | 1                                | 1 | 1 | 1 |  |

| Bit | Function    | Туре |          | Description                                                                              |  |  |  |

|-----|-------------|------|----------|------------------------------------------------------------------------------------------|--|--|--|

| 7:4 |             | R    | Reserved | Reserved                                                                                 |  |  |  |

| 3:0 | DF_SEL[2:0] | R/W  |          | area control bits.<br>lash cannot be programmed when loader code is in progress.<br>29A: |  |  |  |

|     |             |      | 0000     | No loader zone and data flash selected                                                   |  |  |  |

| Bit | Function | Туре |        | Description                                                       | Condition |

|-----|----------|------|--------|-------------------------------------------------------------------|-----------|

|     |          |      | 0001   | The size of loader zone + data flash is 1K bytes                  |           |

|     |          |      |        | (0x1FC00~0x1FFFF).                                                |           |

|     |          |      | 0010   | The size of loader zone + data flash is 2K bytes                  |           |

|     |          |      |        | (0x1F800~0x1FFFF).                                                | _         |

|     |          |      | 0011   | The size of loader zone + data flash is 3K bytes                  |           |

|     |          |      |        | (0x1F400~0x1FFFF).                                                |           |

|     |          |      | 0100   | The size of loader zone + data flash is 4K bytes                  |           |

|     |          |      |        | (0x1F000~0x1FFFF).                                                |           |

|     |          |      | 0101   | The size of loader zone + data flash is 5K bytes                  |           |

|     |          |      |        | (0x1EC00~0x1FFFF).                                                | _         |

|     |          |      | 0110   | The size of loader zone + data flash is 6K bytes                  |           |

|     |          |      |        | (0x1E800~0x1FFFF).                                                | _         |

|     |          |      | 0111   | The size of loader zone + data flash is 7K bytes                  |           |

|     |          |      |        | (0x1E400~0x1FFFF).                                                | _         |

|     |          |      | 1000   | The size of loader zone + data flash is 8K bytes                  |           |

|     |          |      |        | (0x1E000~0x1FFFF).                                                |           |

|     |          |      | 1001   | The size of loader zone + data flash is 9K bytes                  |           |

|     |          |      |        | (0x1DC00~0x1FFFF).                                                |           |

|     |          |      | 1010   | The size of loader zone + data flash is 10K bytes                 |           |

|     |          |      |        | (0x1D800~0x1FFFF).                                                |           |

|     |          |      | 1011   | The size of loader zone + data flash is 11K bytes                 |           |

|     |          |      |        | (0x1D400~0x1FFFF).                                                |           |

|     |          |      | 1100   | The size of loader zone + data flash is 12K bytes                 |           |

|     |          |      |        | (0x1D000~0x1FFFF).                                                |           |

|     |          |      | GPM8F1 | 065A:                                                             | _         |

|     |          |      | 0000   | No loader zone and data flash selected                            |           |

|     |          |      | 0001   | The size of loader zone + data flash is 1K bytes                  |           |

|     |          |      |        | (0xFC00~0xFFFF).                                                  |           |

|     |          |      | 0010   | The size of loader zone + data flash is 2K bytes                  |           |

|     |          |      |        | (0xF800~0xFFFF).                                                  |           |

|     |          |      | 0011   | The size of loader zone + data flash is 3K bytes                  |           |

|     |          |      |        | (0xF400~0xFFFF).                                                  | _         |

|     |          |      | 0100   | The size of loader zone + data flash is 4K bytes (0xF000~0xFFFF). |           |

|     |          |      | 0101   | The size of loader zone + data flash is 5K bytes (0xEC00~0xFFFF). |           |

|     |          |      | 0110   | The size of loader zone + data flash is 6K bytes                  |           |

|     |          |      | 0111   | (0xE800~0xFFFF).                                                  |           |

|     |          |      |        | The size of loader zone + data flash is 7K bytes                  |           |

|     |          |      | 1000   | (0xE400~0xFFFF).                                                  |           |

|     |          |      | 1000   | The size of loader zone + data flash is 8K bytes                  |           |

|     |          |      | 1001   | (0xE000~0xFFFF).                                                  |           |

|     |          |      | 1001   | The size of loader zone + data flash is 9K bytes                  |           |

| l   |          |      | 1010   | (0xDC00~0xFFF).                                                   |           |

|     |          |      | 1010   | The size of loader zone + data flash is 10K bytes                 |           |

|     |          |      |        | (0xD800~0xFFF).                                                   |           |

| Bit | Function | Туре |        | Description                                       | Condition |

|-----|----------|------|--------|---------------------------------------------------|-----------|

|     |          |      | 1011   | The size of loader zone + data flash is 11K bytes |           |

|     |          |      |        | (0xD400~0xFFFF).                                  |           |

|     |          |      | 1100   | The size of loader zone + data flash is 12K bytes |           |

|     |          |      |        | (0xD000~0xFFFF).                                  |           |

|     |          |      | GPM8F1 | 033A:                                             |           |

|     |          |      | 0000   | No loader zone and data flash selected            |           |

|     |          |      | 0001   | The size of loader zone + data flash is 1K bytes  |           |

|     |          |      |        | (0x7C00~0x7FFF).                                  |           |

|     |          |      | 0010   | The size of loader zone + data flash is 2K bytes  |           |

|     |          |      |        | (0x7800~0x7FFF).                                  |           |

|     |          |      | 0011   | The size of loader zone + data flash is 3K bytes  |           |

|     |          |      |        | (0x7400~0x7FFF).                                  |           |

|     |          |      | 0100   | The size of loader zone + data flash is 4K bytes  |           |

|     |          |      |        | (0x7000~0x7FFF).                                  |           |

|     |          |      | 0101   | The size of loader zone + data flash is 5K bytes  |           |

|     |          |      |        | (0x6C00~0x7FFF).                                  |           |

|     |          |      | 0110   | The size of loader zone + data flash is 6K bytes  |           |

|     |          |      |        | (0x6800~0x7FFF).                                  |           |

|     |          |      | 0111   | The size of loader zone + data flash is 7K bytes  |           |

|     |          |      |        | (0x6400~0x7FFF).                                  |           |

|     |          |      | 1000   | The size of loader zone + data flash is 8K bytes  |           |

|     |          |      |        | (0x6000~0x7FFF).                                  |           |

|     |          |      | 1001   | The size of loader zone + data flash is 9K bytes  |           |

|     |          |      |        | (0x5C00~0x7FFF).                                  |           |

|     |          |      | 1010   | The size of loader zone + data flash is 10K bytes |           |

|     |          |      |        | (0x5800~0x7FFF).                                  |           |

|     |          |      | 1011   | The size of loader zone + data flash is 11K bytes |           |

|     |          |      |        | (0x5400~0x7FFF).                                  | _         |

|     |          |      | 1100   | The size of loader zone + data flash is 12K bytes |           |

|     |          |      |        | (0x5000~0x7FFF).                                  |           |

|     |          |      | GPM8F1 |                                                   |           |

|     |          |      | 0000   | No loader zone and data flash selected            |           |

|     |          |      | 0001   | The size of loader zone + data flash is 1K bytes  |           |

|     |          |      |        | (0x4400~0x47FF).                                  | _         |

|     |          |      | 0010   | The size of loader zone + data flash is 2K bytes  |           |

|     |          |      |        | (0x4000~0x47FF).                                  | _         |

|     |          |      | 0011   | The size of loader zone + data flash is 3K bytes  |           |

|     |          |      |        | (0x3C00~0x47FF).                                  | _         |

|     |          |      | 0100   | The size of loader zone + data flash is 4K bytes  |           |

|     |          |      |        | (0x3800~0x47FF).                                  |           |

|     |          |      | 0101   | The size of loader zone + data flash is 5K bytes  |           |

|     |          |      |        | (0x3400~0x47FF).                                  |           |

|     |          |      | 0110   | The size of loader zone + data flash is 6K bytes  |           |

|     |          |      |        | (0x3000~0x47FF).                                  |           |

|     |          |      | 0111   | The size of loader zone + data flash is 7K bytes  |           |

|     |          |      |        | (0x2C00~0x47FF).                                  |           |

| Bit | Function | Туре |      | Description                                                        | Condition |

|-----|----------|------|------|--------------------------------------------------------------------|-----------|

|     |          |      | 1000 | The size of loader zone + data flash is 8K bytes (0x2800~0x47FF).  |           |

|     |          |      | 1001 | The size of loader zone + data flash is 9K bytes (0x2400~0x47FF).  |           |

|     |          |      | 1010 | The size of loader zone + data flash is 10K bytes (0x2000~0x47FF). |           |

|     |          |      | 1011 | The size of loader zone + data flash is 11K bytes (0x1C00~0x47FF). |           |

|     |          |      | 1100 | The size of loader zone + data flash is 12K bytes (0x1800~0x47FF). |           |

Table 5-10 The DF\_SEL register

| FLASHCON |   |   | Address: 0xB7 |   | Flash Control Register |   |         |      |

|----------|---|---|---------------|---|------------------------|---|---------|------|

| Bit      | 7 | 6 | 5             | 4 | 3                      | 2 | 1       | 0    |

| Function |   |   |               |   |                        |   | P_ERASE | PROG |

| Default  | 0 | 0 | 0             | 0 | 0                      | 0 | 0       | 0    |

| Bit | Function | Туре | Description                     | Condition |

|-----|----------|------|---------------------------------|-----------|

| 7:2 |          | R/W  | Reserved                        |           |

| 1   | P_ERASE  | R/W  | Flash page erase enable bit     |           |

|     |          |      | 0: Flash page erase is disabled |           |

|     |          |      | 1: Flash page erase is enabled  |           |

| 0   | PROG     | R/W  | Flash program enable bit        |           |

|     |          |      | 0: Flash program is disabled    |           |

|     |          |      | 1: Flash program is enabled     |           |

Table 5-11 The FLASHCON register

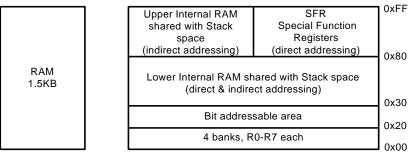

### 5.2.3. Data Memory Allocation

Data memory address allocations on the GPM8F1129/ 1065/ 1033/ 1019A are divided into two parts. The first part is 1.5K bytes of external RAM and the second one is 256 byte IDM shown in Figure 5-2. The lowest internal data memory (IDM) consists of four register banks with eight registers each. A bit addressable segment with 128 bits (16 bytes) begins at 0x20. The address from 0x30 to 0x7F is not defined and can be utilized freely by user. The last 128 bytes of data memory can be used by different addressing modes. With the indirect addressing mode, address from 0x80 to 0xFF shared with stack space is addressed. With the direct addressing mode, the SFR addressing from 0x80 to 0xFF is accessed. The SFR memory map is shown in Table 5-12.

XRAM: 1.5KB

IDM: (256B) and SFR

Figure 5-2 Data memory organization

| -    | 0/8   | 1/9      | 2/A    | 3/B     | 4/C      | 5/D      | 6/E       | 7/F         |

|------|-------|----------|--------|---------|----------|----------|-----------|-------------|

| 0x80 | P0    | SP       | DPL0   | DPH0    | DPL1     | DPH1     | DPS       | PCON        |

| 0x88 | TCON  | TMOD     | TL0    | TL1     | тно      | TH1      | CKCON     | RSTCON      |

| 0x90 | P1    | EIF      |        | DPX0    | RSTSTS   | DPX1     | BIP       | BIF         |

| 0x98 | SCON0 | SBUF0    |        |         |          | ACON     | P2_PU     | P2_PD       |

| 0xA0 | P2    |          | P3_PU  | P3_PD   |          | SRCON    | FLASHERRF |             |

| 0xA8 | IE    | KBIEN    | P0_PU  | P0_PD   | P1_PU    | P1_PD    | SYSCON0   | SYSCON1     |

| 0xB0 | P3    | CMDTCON  | CAPCON | TMAIF   | PERIOD   | DUTY     | WKUEN     | CONFIG_BYTE |

| 0xB8 | IP    | CMPO_INV | TMBIF  | MARKL   | MARKH    | SPACEL   | SPACEH    | RXCON       |

| 0xC0 | CCL   | ССН      |        |         |          |          |           |             |

| 0xC8 | T2CON | T2IF     | CRCL   | CRCH    | TL2      | TH2      | CCEN      | JMP_LZ      |

| 0xD0 | PSW   |          |        |         |          |          |           |             |

| 0xD8 | WDCON |          | I2CCON | I2CSTS  | I2CADR   | I2CDAT   | I2CDEB    |             |

| 0xE0 | ACC   | P0_SC    | P3_SC  | P0_TKEY | P3_TKEY  | TKEY_XOR |           |             |

| 0xE8 | EIE   | EXIPOL   | EXIMOD | KEYCODE | FLASHCON | FL_LEVEL |           |             |

| 0xF0 | В     |          |        |         |          |          |           |             |

| 0xF8 | EIP   | IOSCCON  | IOSCT0 | IOSCT1  | SPICON   | SPITXD   | SPIRXD    | BODYID      |

Note1: Black: standard 8051 register; gray: additional register;

Table 5-12 SFR memory map

### 5.2.4. Memory Related SFR

The following sub-sections describe program, external and internal memories related SFRs of 8051 core and their functionality. For other information about standard SFRs, please refer to appropriate peripheral section.

### 5.2.4.1. Program write enable bit

The Program Write Enable (PWE) bit, located in PCON register bit 4, is used during MOVX instructions. When PWE bit is set to logic 1, the MOVX @DPTR, an instruction writes data located in accumulator register into program memory addressed by DPTR register. Program memory can only be read by MOVC regardless of PWE bit.

### 5.2.4.2. Data pointer registers

Dual data pointer registers are implemented to speed up data block copy. DPTR0 and DPTR1 are located in four SFR addresses. Active DPTR register is selected by SEL bit (DPS[0]). If SEL=0, DPTR0 is selected, else DPTR1.

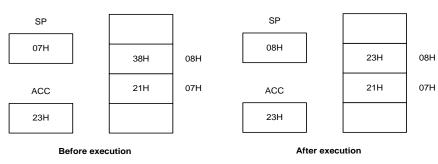

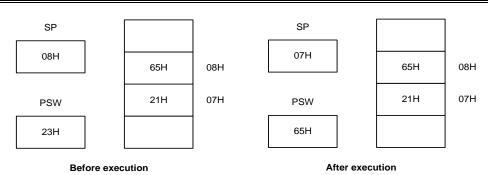

### 5.2.4.3. Stack pointer

The 8051 has 8-bit stack pointer called SP (0x81) located in the internal RAM space. It is incremented before data is stored during PUSH and CALL execution and decremented after data is popped during POP, RET and RETI execution. In the other words, it always points to the last valid stack byte. The SP is accessed as any other SFRs. Figure 5-3 shows an example when PUSH A is executed and Figure 5-4 shows an example when POP PSW is executed.

Figure 5-3 Stack byte order for PUSH A instruction

Figure 5-4 Stack byte order for POP PSW instruction

| PCON     |       |       | Address: 0x87 |     | Power Configuration Register |   |      |   |

|----------|-------|-------|---------------|-----|------------------------------|---|------|---|

| Bit      | 7     | 6     | 5             | 4   | 3                            | 2 | 1    | 0 |

| Function | SMOD0 | SMOD1 | CPU_IDLE      | PWE | STOP_RST_EN                  |   | STOP |   |

| Default  | 0     | 0     | 0             | 0   | 0                            | 0 | 0    | 0 |

| Bit | Function    | Туре | Description                                             | Condition |

|-----|-------------|------|---------------------------------------------------------|-----------|

| 7   | SMOD0       | R/W  | UART0 baud rate bit when clocked by Timer1              |           |

| 6   | SMOD1       | R/W  | UART0 baud rate bit when clocked by Timer1              |           |

| 5   | CPU_IDLE    | R/W  | IDLE mode enable bit                                    |           |

|     |             |      | 0: IDLE mode disabled ;                                 |           |

|     |             |      | 1: IDLE mode entered                                    |           |

| 4   | PWE         | R/W  | Program Write Enable (PWE)                              |           |

|     |             |      | 0: Disable Flash write activity during MOVX instruction |           |

|     |             |      | 1: Enable Flash write activity during MOVX instruction  |           |

| 3   | STOP_RST_EN | R/W  | Wakeup state selection bit                              |           |

|     |             |      | 0: Next instruction state after wakeup                  |           |

|     |             |      | 1: Reset state afer wakeup                              |           |

| 2   |             | R/W  | Reserved                                                |           |

| 1   | STOP        | R/W  | STOP mode enable bit                                    |           |

|     |             |      | 0: Disabled                                             |           |

|     |             |      | 1: Enabled                                              |           |

| 0   |             | R/W  | Reserved                                                |           |

Table 5-13 The PCON register

| DPH0     |             |   | Address: 0x83 |   | Data Pointer F | Register - high byte |   |   |

|----------|-------------|---|---------------|---|----------------|----------------------|---|---|

| Bit      | 7           | 6 | 5             | 4 | 3              | 2                    | 1 | 0 |

| Function | DPTR0[15:8] |   |               |   |                |                      |   |   |

| Default  | 0           | 0 | 0             | 0 | 0              | 0                    | 0 | 0 |

| Bit | Function    | Туре | Description                             | Condition |

|-----|-------------|------|-----------------------------------------|-----------|

| 7:0 | DPTR0[15:8] | R/W  | Data pointer register DPTR0 - high byte |           |

Table 5-14 The DPH0 register

| DPL0     |   |   | Address: 0x82 |     | Data Pointer F | Register - low b | yte |   |

|----------|---|---|---------------|-----|----------------|------------------|-----|---|

| Bit      | 7 | 6 | 5             | 4   | 3              | 2                | 1   | 0 |

| Function |   |   |               | DPT | R0[7:0]        |                  |     |   |

| Default  | 0 | 0 | 0             | 0   | 0              | 0                | 0   | 0 |

| Bit | Function   | Туре | Description                            | Condition |

|-----|------------|------|----------------------------------------|-----------|

| 7:0 | DPTR0[7:0] | R/W  | Data pointer register DPTR0 - low byte |           |

Table 5-15 The DPL0 register

| DPX0     |                                     |   | Address: 0x93 |   | Data Pointer Extended Register |   |   |   |

|----------|-------------------------------------|---|---------------|---|--------------------------------|---|---|---|

| Bit      | 7                                   | 6 | 5             | 4 | 3                              | 2 | 1 | 0 |

| Function | DPTR0[23:16] (GPM8F1129/1065A only) |   |               |   |                                |   |   |   |

| Default  | 0                                   | 0 | 0             | 0 | 0                              | 0 | 0 | 0 |

| Bit | Function     | Туре | Description                    | Condition |

|-----|--------------|------|--------------------------------|-----------|

| 7:0 | DPTR0[23:16] | R/W  | Data pointer extended register |           |

Table 5-16 The DPX0 register

| DPH1     |   |             | Address: 0x85 |   | Data Pointer 1 | 1 Register - high byte |   |   |

|----------|---|-------------|---------------|---|----------------|------------------------|---|---|

| Bit      | 7 | 6           | 5             | 4 | 3              | 2                      | 1 | 0 |

| Function |   | DPTR1[15:8] |               |   |                |                        |   |   |

| Default  | 0 | 0           | 0             | 0 | 0              | 0                      | 0 | 0 |

| Bit | Function    | Туре | Description                               | Condition |

|-----|-------------|------|-------------------------------------------|-----------|

| 7:0 | DPTR1[15:8] | R/W  | Data pointer 1 register DPTR1 - high byte |           |

Table 5-17 The DPH1 register

| DPL1     |            |   | Address: 0x84 |   | Data Pointer 1 | 1 Register - Iow byte |   |   |

|----------|------------|---|---------------|---|----------------|-----------------------|---|---|

| Bit      | 7          | 6 | 5             | 4 | 3              | 2                     | 1 | 0 |

| Function | DPTR0[7:0] |   |               |   |                |                       |   |   |

| Default  | 0          | 0 | 0             | 0 | 0              | 0                     | 0 | 0 |

| Bit | Function   | Туре | Description                              | Condition |

|-----|------------|------|------------------------------------------|-----------|

| 7:0 | DPTR1[7:0] | R/W  | Data pointer 1 register DPTR1 - low byte |           |

| Table 5-18 The | DPL1 r | egister |

|----------------|--------|---------|

|----------------|--------|---------|

| DPX1     |                                     |   | Address: 0x95 |   | Data Pointer Extended 1 Register |   |   |   |  |  |  |

|----------|-------------------------------------|---|---------------|---|----------------------------------|---|---|---|--|--|--|

| Bit      | 7                                   | 6 | 5             | 4 | 3                                | 2 | 1 | 0 |  |  |  |

| Function | DPTR1[23:16] (GPM8F1129/1065A only) |   |               |   |                                  |   |   |   |  |  |  |

| Default  | 0                                   | 0 | 0             | 0 | 0                                | 0 | 0 | 0 |  |  |  |

| Bit | Function     | Туре | Description                      | Condition |

|-----|--------------|------|----------------------------------|-----------|

| 7:0 | DPTR1[23:16] | R/W  | Data pointer extended 1 register |           |

Table 5-19 The DPX1 register

| DPS      |     |     | Address: 0x86 |   | Data Pointer Select Register |   |   |     |

|----------|-----|-----|---------------|---|------------------------------|---|---|-----|

| Bit      | 7   | 6   | 5             | 4 | 3                            | 2 | 1 | 0   |

| Function | ID1 | ID0 | TSL           | - | -                            | - | - | SEL |

| Default  | 0   | 0   | 0             | 0 | 0                            | 0 | 0 | 0   |

| Bit | Function | Туре | Description                                                                                                                                   | Condition |

|-----|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 7:6 | ID[1:0]  | R/W  | Increment/decrement function selection.<br>See Table 5-21                                                                                     |           |

| 5   | TSL      | R/W  | Toggle select enable bit<br>0: DPTR related instructions do not affect state of SEL bit<br>1: DPTR related instructions to toggle the SEL bit |           |

| 4:1 |          | R/W  | Reserved                                                                                                                                      |           |

| 0   | SEL      | R/W  | Active data pointer select bit<br>See Table 5-21                                                                                              |           |

Table 5-20 The DPS register

| ID1 | ID0 | SEL=0     | SEL=1     |

|-----|-----|-----------|-----------|

| 0   | 0   | INC DPTR0 | INC DPTR1 |

| 0   | 1   | DEC DPTR0 | INC DPTR1 |

| 1   | 0   | INC DPTR0 | DEC DPTR1 |

| 1   | 1   | DEC DPTR0 | DEC DPTR1 |

Table 5-21 DPTR0/DPTR1 operations

| SP       |   |         | Address: 0x81 |   | Stack Pointer Register |   |   |   |  |  |  |  |

|----------|---|---------|---------------|---|------------------------|---|---|---|--|--|--|--|

| Bit      | 7 | 6       | 5             | 4 | 3                      | 2 | 1 | 0 |  |  |  |  |

| Function |   | SP[7:0] |               |   |                        |   |   |   |  |  |  |  |

| Default  | 0 | 0       | 0             | 0 | 0                      | 1 | 1 | 1 |  |  |  |  |

| Bit | Function | Туре | Description   | Condition |

|-----|----------|------|---------------|-----------|

| 7:0 | SP[7:0]  | R/W  | Stack pointer |           |

Table 5-22 The SP register

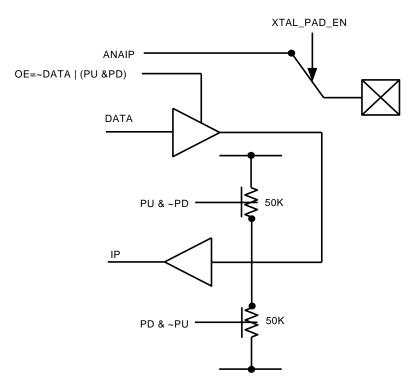

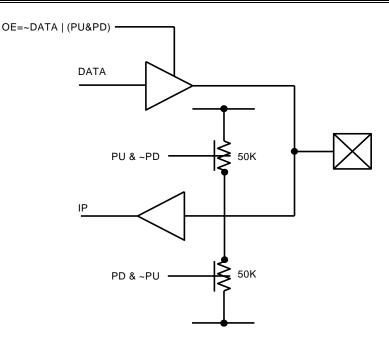

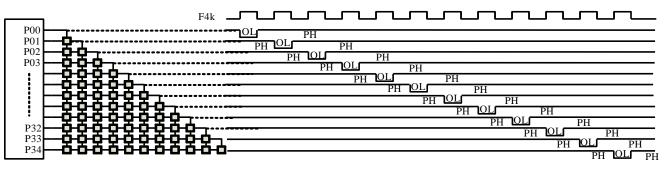

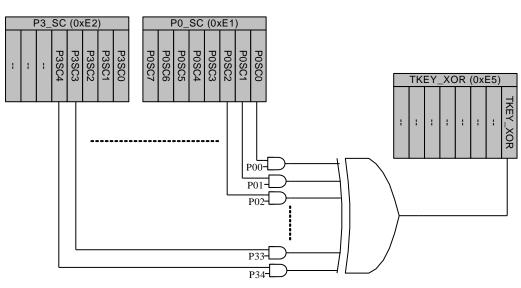

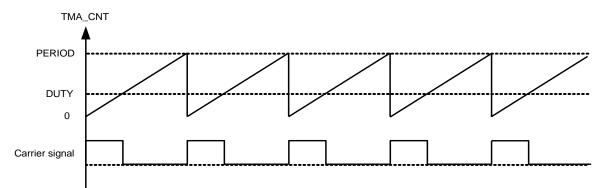

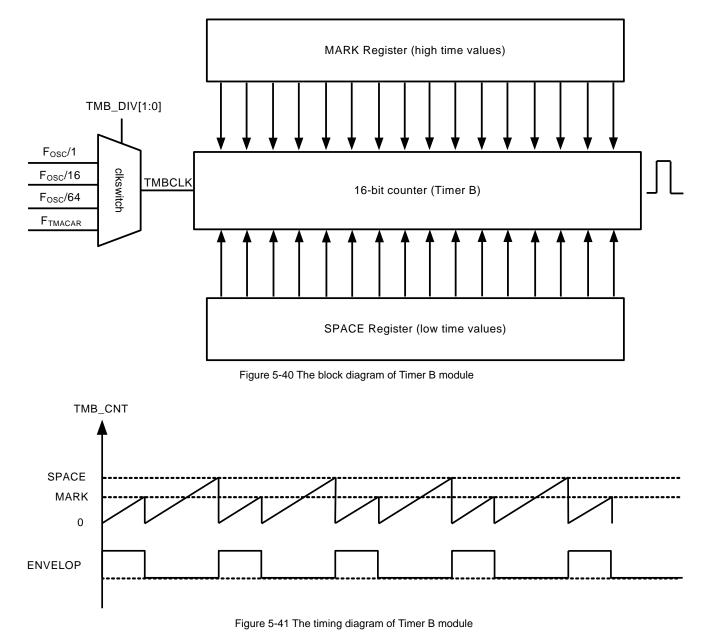

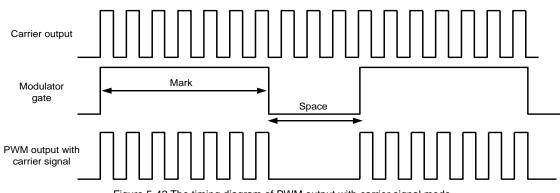

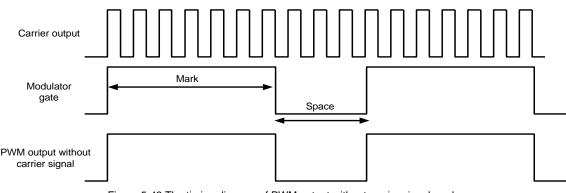

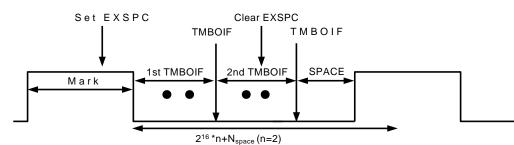

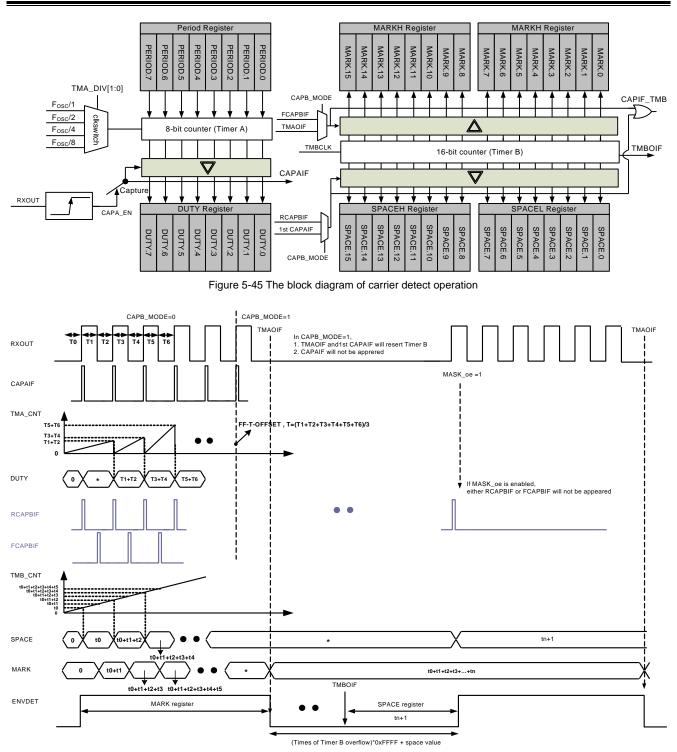

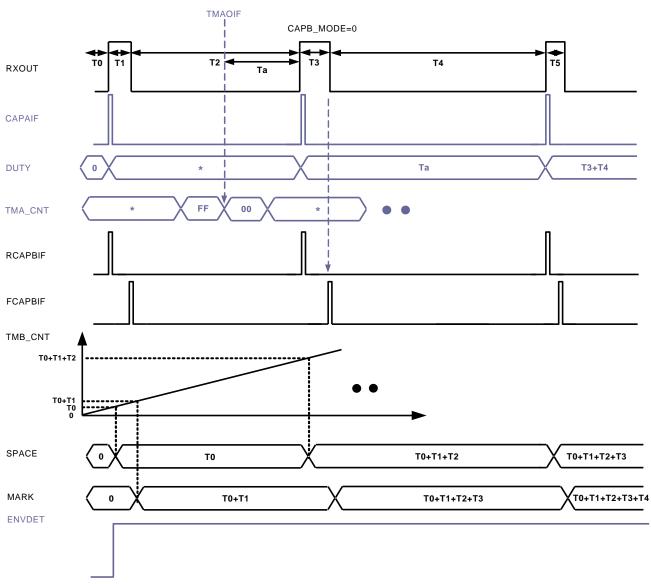

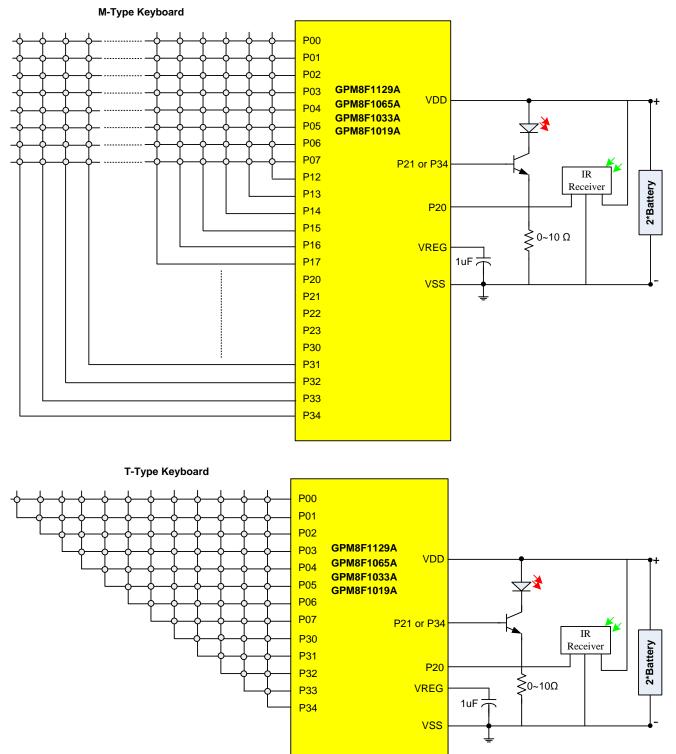

### 5.3. Special Function Registers (SFR)