# LANGUAGE REPEATER

#### **1. GENERAL DESCRIPTION**

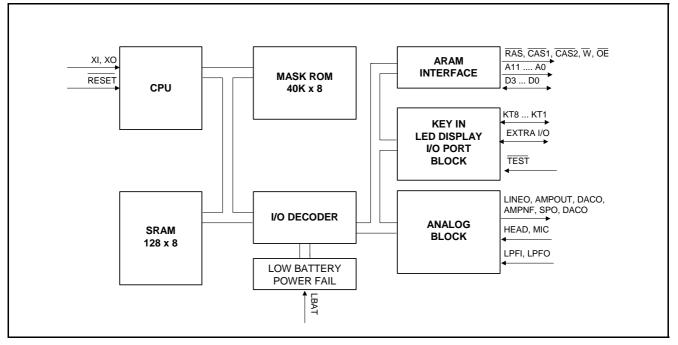

The GPRT5507A integrates an 8-bit CPU, speech generator, segment LED driver, analog switches, programmable attenuator and a gain amplifier into one chip. The GPRT5507A includes a 40K-byte ROM, 128-byte working SRAM, 4 edge-mode interrupts and a fixed time based generator ( $F_{CPU}/1024$ )\*. This chip which incorporated with 1 or 2 pieces of 4M X 4 ARAM, can be applied to the versatile audio field, such as a language repeater.

\*F<sub>CPU</sub>: CPU clock

### 2. FEATURES

- 8-bit microprocessor

- Provide 40K x 8 ROM area for program and audio data

- 128 x 8 working SRAM

- Embedded LPF, ADC, DAC for analog processing

- Provide controlled DRAM interfaces

- 4 Interrupt sources

- Built in watch dog timer

- ROSC. or Crystal OSC. selections

- Provide low battery detector

- Provide power down mode

#### 3. BLOCK DIAGRAM

# 4. SIGNAL DESCRIPTIONS

| Mnemonic | PIN No. | Туре | Description                                                                                     |

|----------|---------|------|-------------------------------------------------------------------------------------------------|

| XI       | 44      | I    | Crystal OSC Input or ROSC tuning resistor, connected to AVDD                                    |

| ХО       | 45      | 0    | Crystal OSC Output                                                                              |

| OPT      | 46      | I    | OSC type selector. '0' or open for X'TAL, '1' for ROSC                                          |

| RESET    | 59      | I    | System reset, active low                                                                        |

| KT8 - 1  | 67 - 60 | I/O  | LED segment driver, Open Drain NMOS output, and Key input (8-1), TTL and CMOS compatible Input. |

| A2 - 0   | 71 - 69 | 0    | ARAM Address A11 - 0                                                                            |

| A8 - 3   | 84 - 79 |      |                                                                                                 |

| A11 - 9  | 3 - 1   |      |                                                                                                 |

| D3 - 0   | 7 - 4   | I/O  | ARAM Data D3 - 0                                                                                |

| W        | 16      | 0    | ARAM Write Enable                                                                               |

| OE       | 17      | 0    | ARAM Output Enable                                                                              |

| RAS      | 18      | 0    | ARAM ROW Address Strobe                                                                         |

| CAS1     | 19      | 0    | ARAM1 Column Address Strobe                                                                     |

| CAS2     | 20      | 0    | ARAM2 Column Address Strobe                                                                     |

| DACO     | 23      | 0    | DAC Output                                                                                      |

| LPFI     | 24      | I    | Low Pass Filter Input                                                                           |

| LPFO     | 25      | 0    | Low Pass Filter Output                                                                          |

| LBAT     | 26      | I    | Low Battery detector Input                                                                      |

| AMPOUT   | 27      | 0    | Gain Amplifier Output                                                                           |

| SPO      | 37      | 0    | Signal Output, goes to speaker amplifier                                                        |

| AMPNF    | 38      | I    | Gain Amplifier Input                                                                            |

| VREF     | 39      | 0    | Voltage Reference Output                                                                        |

| MIC      | 40      | I    | Input signal, comes from microphone                                                             |

| HEAD     | 41      | I    | Input signal, comes from magnetic head of tape                                                  |

| TEST     | 42      | L    | IC test pin, Active Low                                                                         |

| EXIO1    | 58      | I/O  | Extra I/O port 1                                                                                |

| EXIO2    | 49      | I/O  | Extra I/O port 2                                                                                |

| EXIO3    | 48      | I/O  | Extra I/O port 3                                                                                |

| EXIO4    | 47      | I/O  | Extra I/O port 4                                                                                |

| VDD      | 68      | Р    | Logic power                                                                                     |

| VSS      | 21, 43  | G    | Logic ground                                                                                    |

| AVDD     | 22      | Р    | Analog power                                                                                    |

| AVSS     | 28      | G    | Analog ground                                                                                   |

\* OPT is the selection pin for ROSC or X'TAL. When ROSC is selected, OPT is connected to VDD and if X'TAL is selected, OPT is floating or connected to GND. The PCB layout that looks like in the right figure is proper. This will make it easier for OSC type change.

## 5. FUNCTIONAL DESCRIPTIONS

The GPRT5507A is a CMOS; low cost, audio processor that can operate with a supply rang from 4.0V to 5.5V. The GPRT5507A has mainly an 8-bit CPU, 128B SRAM, 40KB ROM, several I/O ports and an analog processor. The address map of memory and I/O ports please refer to the programming guide. The analog processor is described in detail in next section.

#### 5.1. Clock Source Selection

There are two options for clock sources. When OPT pin is open or connected to VSS, the crystal oscillator is selected. If the OPT pin connects to VDD, the less accurate R-oscillator is selected. The clock frequency of ROSC depends on the resistor connected between XI and AVDD. The recommended value is 30K Ohms for 3.58MHz and 16K Ohms for 6 MHz respectively.

#### 5.2. Linear Block Description

There are four major parts in the linear block including signal switches, gain amplifier, DAC converter and low pass filter. In recording mode, signal switches select desired inputs and turn on sample and hold circuits. Gain amplifier amplifies the selected signal, and provides flexible gain–adjustment by external resisters and capacitors. A/D converter, which uses SAR algorithm based on CPU converts the amplified signal to digital signal, than store those digital data into ARAM. In playing back mode, D/A converter converts digital signals, which comes from ARAM to analog signal. Following that DAC, low-pass filter with external resistors and capacitors is used to smooth the DAC output waveform.

**Note:** Heretofore, the above are just hardware descriptions. Please refer to user programming guides for the detail information.

# 6. ELECTRICAL SPECIFICATIONS

#### 6.1. Absolute Maximum Ratings

| Characteristics       | Symbol           | Ratings                        |

|-----------------------|------------------|--------------------------------|

| DC Supply Voltage     | V.+              | < 7.0V                         |

| Input Voltage Range   | V <sub>IN</sub>  | -0.5V to V <sub>+</sub> + 0.5V |

| Operating Temperature | T <sub>A</sub>   | -10 °C to +60 °C               |

| Storage Temperature   | T <sub>STO</sub> | -50 °C to +150 °C              |

Note: Stresses beyond those given in the Absolute Maximum Ratings table may cause operational errors or damage to the device. For normal operational conditions see AC/DC Electrical Characteristics.

## 6.2. DC Characteristics (VDD = 5.0V; $T_{AMB}$ = 25°C, CPU clock = 3.58MHz)

|                        |                    | Limit |      |                               |      |                               |

|------------------------|--------------------|-------|------|-------------------------------|------|-------------------------------|

| Characteristics        | Symbol             | Min.  | Тур. | Max.                          | Unit | Test Conditions               |

| hannet Maltana *4      | V <sub>IL</sub>    | -     | -    | 0.4                           |      |                               |

| Input Voltage *1       | VIH                | 2.4   | -    | -                             | V    | -                             |

|                        | V <sub>IL</sub>    | -     | -    | 0.8                           |      |                               |

| Input Voltage *2       | V <sub>IH</sub>    | 4.0   | -    | 0.8 V   0.8 V   0.8 V   0.4 V |      |                               |

| Output Voltage *3      | V <sub>OL</sub>    | -     | -    | 0.8                           | V    | I <sub>OUT</sub> = 8mA        |

| Outrast Malla and MA   | V <sub>OL</sub>    | -     | -    | 0.4                           |      | I <sub>OUT</sub> = 0.1mA      |

| Output Voltage *4      | V <sub>OH</sub>    | 4.0   | -    | -                             | V    | I <sub>OUT</sub> = -0.1mA     |

| Operating Voltage      | VDD                | 4.5   | 5.0  | 5.5                           | V    | -                             |

| DAC full scale voltage | V <sub>FS</sub>    | -     | 1.5  | -                             | V    | Peak to peak value            |

| Operating Current      | I <sub>OP</sub>    | -     | 15   | -                             | mA   | Chip goes into recording mode |

| Standby Current        | I <sub>STABY</sub> | -     | 4.0  | -                             | mA   | Chip goes into backup mode    |

Note\*1: KT8 - 1, TTL and CMOS compatible input Note\*2: Other Logic Pins, CMOS input

Note\*3: KT8 - 1, Open NMOS drain output

Note\*4: Other Logic Pins, CMOS output

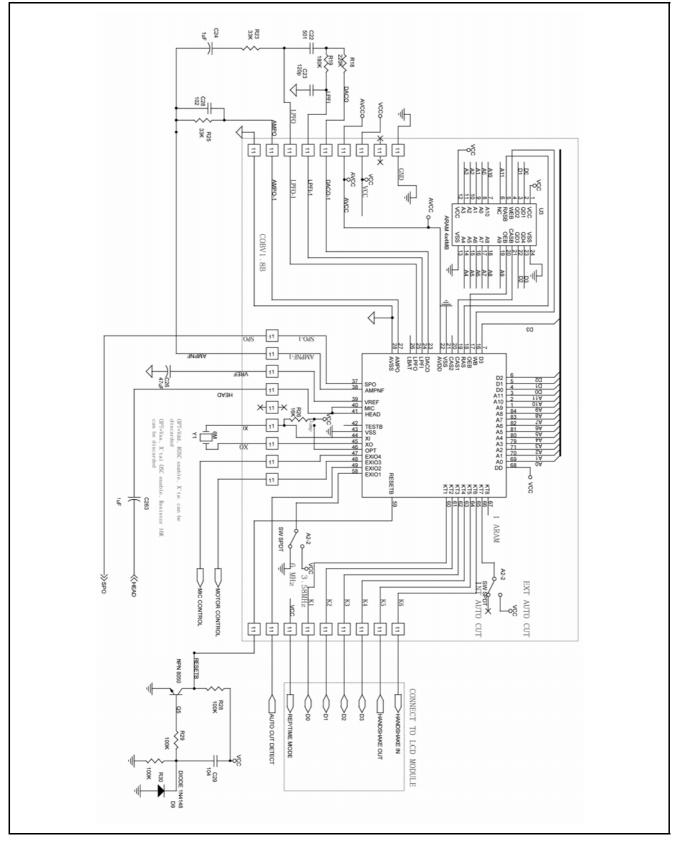

# 7. APPLICATION CIRCUIT

## 7.1. LCD Language Repeater Application Circuit

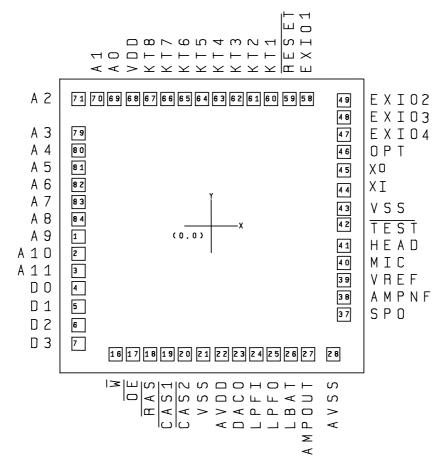

#### 8. PACKAGE/PAD LOCATIONS

#### 8.1. PAD Assignment

This IC substrate should be connected to VSS

Note1: Chip size included scribe line.

Note2: To ensure that the IC functions properly, please bond all of VDD and VSS pins.

Note3: The  $0.1 \mu F$  capacitor between VDD and VSS should be placed to IC as close as possible.

## 8.2. Ordering Information

| Product Number   | Package Type |

|------------------|--------------|

| GPRT5507A-NnnV-C | Chip form    |

Note1: Code number is assigned for customer.

Note2: Code number (N = A - Z or 0 - 9, nn = 00 - 99); version (V = A - Z).

### 8.3. PAD Locations

| PAD No. | PAD Name | X     | Y    | PAD No. | PAD Name | X     | Y   |

|---------|----------|-------|------|---------|----------|-------|-----|

| 1       | A9       | -1000 | -76  | 44      | XI       | 993   | 274 |

| 2       | A10      | -1000 | -206 | 45      | хо       | 993   | 417 |

| 3       | A11      | -1000 | -336 | 46      | OPT      | 993   | 558 |

| 4       | D0       | -1000 | -468 | 47      | EXIO4    | 993   | 688 |

| 5       | D1       | -1000 | -608 | 48      | EXIO3    | 993   | 818 |

| 6       | D2       | -1000 | -748 | 49      | EXIO2    | 993   | 948 |

| 7       | D3       | -1000 | -888 | 58      | EXIO1    | 720   | 962 |

| 16      | W        | -726  | -965 | 59      | RESET    | 585   | 962 |

| 17      | OE       | -596  | -965 | 60      | KT1      | 450   | 962 |

| 18      | RAS      | -466  | -965 | 61      | KT2      | 320   | 962 |

| 19      | CAS1     | -336  | -965 | 62      | KT3      | 190   | 962 |

| 20      | CAS2     | -206  | -965 | 63      | KT4      | 60    | 962 |

| 21      | VSS      | -63   | -965 | 64      | KT5      | -70   | 962 |

| 22      | AVDD     | 79    | -965 | 65      | KT6      | -200  | 962 |

| 23      | DACO     | 209   | -965 | 66      | KT7      | -330  | 962 |

| 24      | LPFI     | 339   | -965 | 67      | KT8      | -460  | 962 |

| 25      | LPFO     | 469   | -965 | 68      | VDD      | -595  | 962 |

| 26      | LBAT     | 599   | -965 | 69      | A0       | -730  | 962 |

| 27      | AMPOUT   | 729   | -965 | 70      | A1       | -865  | 962 |

| 28      | AVSS     | 916   | -965 | 71      | A2       | -1000 | 962 |

| 37      | SPO      | 993   | -673 | 79      | A3       | -1000 | 704 |

| 38      | AMPNF    | 993   | -543 | 80      | A4       | -1000 | 574 |

| 39      | VREF     | 993   | -413 | 81      | A5       | -1000 | 444 |

| 40      | MIC      | 993   | -283 | 82      | A6       | -1000 | 314 |

| 41      | HEAD     | 993   | -153 | 83      | A7       | -1000 | 184 |

| 42      | TEST     | 993   | 7    | 84      | A8       | -1000 | 54  |

| 43      | VSS      | 993   | 132  |         |          |       |     |

# 9. DISCLAIMER

The information appearing in this publication is believed to be accurate.

Integrated circuits sold by Generalplus Technology are covered by the warranty and patent indemnification provisions stipulated in the terms of sale only. GENERALPLUS makes no warranty, express, statutory implied or by description regarding the information in this publication or regarding the freedom of the described chip(s) from patent infringement. FURTHERMORE, GENERALPLUS MAKES NO WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PURPOSE. GENERALPLUS reserves the right to halt production or alter the specifications and prices at any time without notice. Accordingly, the reader is cautioned to verify that the data sheets and other information in this publications involving unusual environmental or reliability requirements, e.g. military equipment or medical life support equipment, are specifically not recommended without additional processing by GENERALPLUS for such applications. Please note that application circuits illustrated in this document are for reference purposes only.

# **10. REVISION HISTORY**

| Date          | Revision # | Description                                                                             | Page |  |

|---------------|------------|-----------------------------------------------------------------------------------------|------|--|

| MAR. 04, 2005 | 1.1        | Remove chip size.                                                                       | 6    |  |

| MAY. 24, 2004 | 1.0        | First Edition                                                                           | 9    |  |

|               |            | Note: The GPRT5507A data sheet v1.0 is a continued version of SPT5507A data sheet v1.1. |      |  |