### Features

- 650 V enhancement mode power transistor

- Bottom-side cooled configuration

- R<sub>DS(on)</sub> = 50 mΩ

- I<sub>DS(max)</sub> = 30 A

- Ultra-low FOM die

- Low inductance GaNPX® package

- Simple gate drive requirements (0 V to 6 V)

- Transient tolerant gate drive (-20 V / +10 V)

- Very high switching frequency (> 10 MHz)

- Fast and controllable fall and rise times

- Reverse conduction capability

- Zero reverse recovery loss

- Small 7.0 x 8.4 mm<sup>2</sup> PCB footprint

- Source Sense (SS) pin for optimized gate drive

- RoHS 3 (6+4) compliant

### Applications

- AC-DC Converters

- DC-DC Converters

- Bridgeless Totem Pole PFC

- Inverters

- Energy Storage Systems

- On Board Battery Chargers

- Uninterruptable Power Supplies

- Solar Energy

- Industrial Motor Drives

- Appliances

- Laser Drivers

- Wireless Power Transfer

## Description

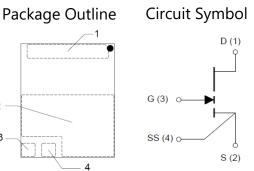

2

3

The GS66508B is an enhancement mode GaN-onsilicon power transistor. The properties of GaN allow for high current, high voltage breakdown and high switching frequency. GaN Systems innovates with industry leading advancements such as patented **Island Technology®** and **GaN***Px*® packaging. **Island Technology®** cell layout realizes high-current die and high yield. **GaN***Px*® packaging enables low inductance & low thermal resistance in a small package. The GS66508B is a bottom-side cooled transistor that offers very low junction-tocase thermal resistance for demanding high power applications. These features combine to provide very high efficiency power switching.

| Parameter                                                                       | Symbol                     | Value       | Unit |

|---------------------------------------------------------------------------------|----------------------------|-------------|------|

| Operating Junction Temperature                                                  | ۲                          | -55 to +150 | °C   |

| Storage Temperature Range                                                       | Ts                         | -55 to +150 | °C   |

| Drain-to-Source Voltage                                                         | V <sub>DS</sub>            | 650         | V    |

| Drain-to-Source Voltage - transient (Note 1)                                    | $V_{\text{DS(transient)}}$ | 750         | V    |

| Gate-to-Source Voltage                                                          | $V_{GS}$                   | -10 to +7   | V    |

| Gate-to-Source Voltage - transient (Note 1)                                     | $V_{GS(transient)}$        | -20 to +10  | V    |

| Continuous Drain Current (T <sub>case</sub> = 25 °C)                            | I <sub>DS</sub>            | 30          | А    |

| Continuous Drain Current (T <sub>case</sub> = 100 °C)                           | I <sub>DS</sub>            | 25          | А    |

| Pulse Drain Current (Pulse width 50 $\mu$ s, V <sub>GS</sub> = 6 V)<br>(Note 2) | I <sub>DS Pulse</sub>      | 60          | А    |

### Absolute Maximum Ratings (T<sub>case</sub> = 25 °C except as noted)

(1) For <u><</u> 1 μs

(2) Defined by product design and characterization. Value is not tested to full current in production.

### Thermal Characteristics (Typical values unless otherwise noted)

| Parameter                                           | Symbol            | Value | Units |

|-----------------------------------------------------|-------------------|-------|-------|

| Thermal Resistance (junction-to-case) – bottom side | R <sub>ojc</sub>  | 0.5   | °C /W |

| Thermal Resistance (junction-to-ambient) (Note 3)   | $R_{\Theta JA}$   | 24    | °C /W |

| Maximum Soldering Temperature (MSL3 rated)          | T <sub>SOLD</sub> | 260   | °C    |

(3) Device mounted on 1.6 mm PCB thickness FR4, 4-layer PCB with 2 oz. copper on each layer. The recommendation for thermal vias under the thermal pad are 0.3 mm diameter (12 mil) with 0.635 mm pitch (25 mil). The copper layers under the thermal pad and drain pad are 25 x 25 mm<sup>2</sup> each. The PCB is mounted in horizontal position without air stream cooling.

### **Ordering Information**

| Ordering<br>code | Package type                          | Packing<br>method | Qty  | Reel<br>Diameter | Reel<br>Width |

|------------------|---------------------------------------|-------------------|------|------------------|---------------|

| GS66508B-TR      | GaN <i>PX</i> ® Bottom-Side<br>Cooled | Tape-and-Reel     | 3000 | 13"<br>(330mm)   | 16mm          |

| GS66508B-MR      | GaN <i>PX</i> ® Bottom-Side<br>Cooled | Mini-Reel         | 250  | 7" (180mm)       | 16mm          |

| Parameters                                               | Sym.                 | Min. | Тур. | Max. | Units | Conditions                                                             |

|----------------------------------------------------------|----------------------|------|------|------|-------|------------------------------------------------------------------------|

| Drain-to-Source Blocking<br>Voltage                      | V <sub>(BL)DSS</sub> | 650  |      |      | V     | $V_{GS} = 0 V, I_{DSS} = 50 \mu A$                                     |

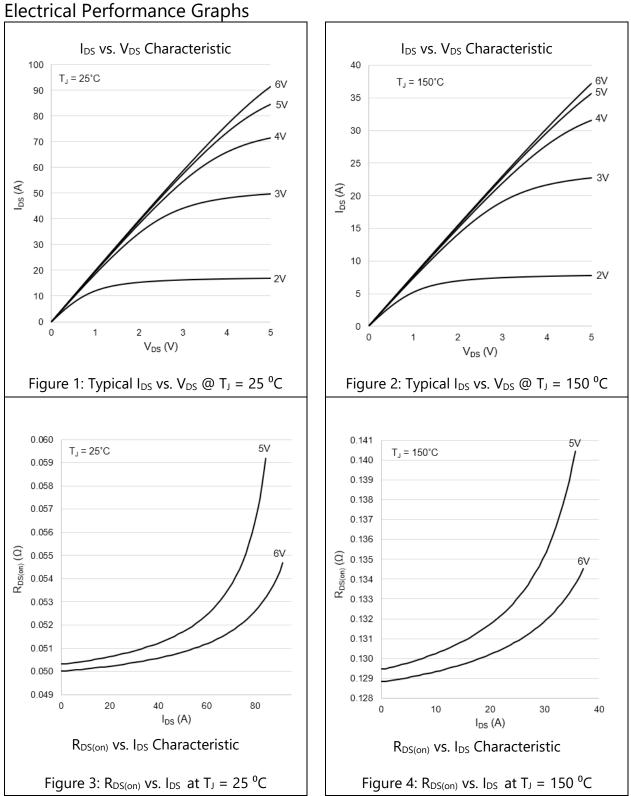

| Drain-to-Source On Resistance                            | R <sub>DS(on)</sub>  |      | 50   | 63   | mΩ    | V <sub>GS</sub> = 6 V, T <sub>J</sub> = 25 °C<br>I <sub>DS</sub> = 9 A |

| Drain-to-Source On Resistance                            | R <sub>DS(on)</sub>  |      | 129  |      | mΩ    | V <sub>G</sub> = 6 V, T <sub>J</sub> = 150 °C<br>I <sub>DS</sub> = 9 A |

| Gate-to-Source Threshold                                 | $V_{GS(th)}$         | 1.1  | 1.7  | 2.6  | V     | $V_{DS} = V_{GS}$ , $I_{DS} = 7 \text{ mA}$                            |

| Gate-to-Source Current                                   | I <sub>GS</sub>      |      | 160  |      | μΑ    | $V_{GS} = 6 V, V_{DS} = 0 V$                                           |

| Gate Plateau Voltage                                     | $V_{plat}$           |      | 3    |      | V     | V <sub>DS</sub> = 400 V, I <sub>DS</sub> = 30 A                        |

| Drain-to-Source Leakage<br>Current                       | I <sub>DSS</sub>     |      | 2    | 50   | μΑ    | $V_{DS} = 650 V, V_{GS} = 0 V$<br>T <sub>J</sub> = 25 °C               |

| Drain-to-Source Leakage<br>Current                       | I <sub>DSS</sub>     |      | 400  |      | μΑ    | $V_{DS} = 650 V, V_{GS} = 0 V$<br>T <sub>J</sub> = 150 °C              |

| Internal Gate Resistance                                 | R <sub>G</sub>       |      | 1.1  |      | Ω     | f = 5 MHz, open drain                                                  |

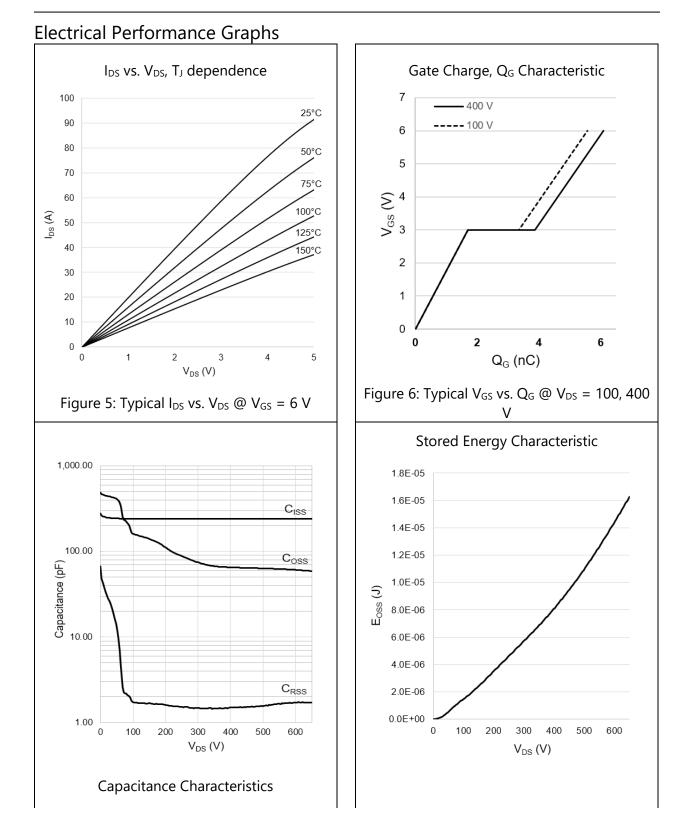

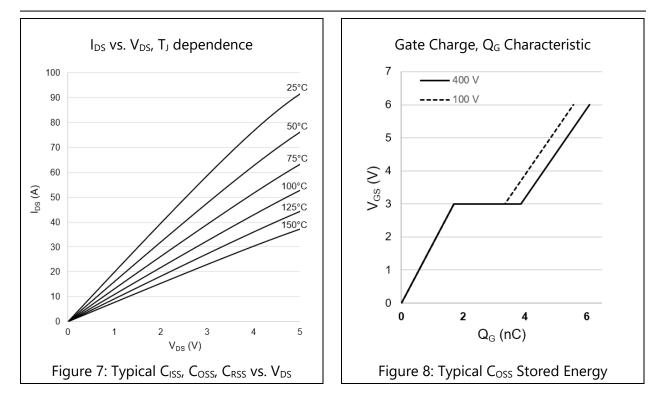

| Input Capacitance                                        | C <sub>ISS</sub>     |      | 242  |      | pF    | V <sub>DS</sub> = 400 V                                                |

| Output Capacitance                                       | Coss                 |      | 65   |      | pF    | $V_{GS} = 0 V$                                                         |

| Reverse Transfer Capacitance                             | C <sub>RSS</sub>     |      | 1.5  |      | pF    | f = 100 kHz                                                            |

| Effective Output Capacitance,<br>Energy Related (Note 4) | C <sub>O(ER)</sub>   |      | 100  |      | pF    | V <sub>GS</sub> = 0 V                                                  |

| Effective Output Capacitance,<br>Time Related (Note 5)   | C <sub>O(TR)</sub>   |      | 160  |      | pF    | V <sub>DS</sub> = 0 to 400 V                                           |

| Total Gate Charge                                        | Q <sub>G</sub>       |      | 6.1  |      | nC    |                                                                        |

| Gate-to-Source Charge                                    | Q <sub>GS</sub>      |      | 1.7  |      | nC    | $V_{GS} = 0 \text{ to } 6 \text{ V}$<br>$V_{DS} = 400 \text{ V}$       |

| Gate-to-Drain Charge                                     | Q <sub>GD</sub>      |      | 2.2  |      | nC    |                                                                        |

| Output Charge                                            | Qoss                 |      | 64   |      | nC    | $V_{GS} = 0 V, V_{DS} = 400 V$                                         |

| Reverse Recovery Charge                                  | Q <sub>RR</sub>      |      | 0    |      | nC    |                                                                        |

(4)  $C_{O(ER)}$  is the fixed capacitance that would give the same stored energy as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 V to the stated  $V_{DS}$

(5)  $C_{O(TR)}$  is the fixed capacitance that would give the same charging time as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 V to the stated  $V_{DS}$ .

| Electrical Characteristics cont'd (Typical values at T <sub>J</sub> = 25 °C, V <sub>GS</sub> = 6 V unless otherwise |

|---------------------------------------------------------------------------------------------------------------------|

| noted)                                                                                                              |

| Parameters                          | Sym.                | Min. | Тур. | Max. | Units | Conditions                                                                         |

|-------------------------------------|---------------------|------|------|------|-------|------------------------------------------------------------------------------------|

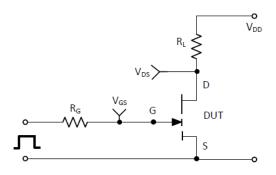

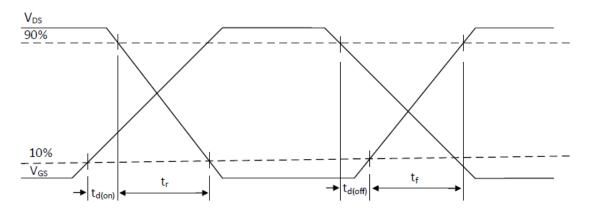

| Turn-On Delay                       | t <sub>D(on)</sub>  |      | 4.1  |      | ns    |                                                                                    |

| Rise Time                           | t <sub>R</sub>      |      | 3.7  |      | ns    | $V_{DD} = 400 \text{ V}, \text{ V}_{GS} = 0.6 \text{ V}$                           |

| Turn-Off Delay                      | t <sub>D(off)</sub> |      | 8    |      | ns    | $I_{DS} = 16 \text{ A}, R_{G(ext)} = 5 \Omega$<br>$T_J = 25 \text{ °C (Note 6)}$   |

| Fall Time                           | t <sub>F</sub>      |      | 5.2  |      | ns    |                                                                                    |

| Turn-On Delay                       | t <sub>D(on)</sub>  |      | 4.3  |      | ns    |                                                                                    |

| Rise Time                           | t <sub>R</sub>      |      | 4.9  |      | ns    | $V_{DD} = 400 V, V_{GS} = 0.6 V$                                                   |

| Turn-Off Delay                      | $t_{\text{D(off)}}$ |      | 8.2  |      | ns    | $I_{DS} = 16 \text{ A}, R_{G(ext)} = 5 \Omega$<br>T <sub>J</sub> = 125 °C (Note 6) |

| Fall Time                           | tF                  |      | 3.4  |      | ns    |                                                                                    |

| Output Capacitance Stored<br>Energy | E <sub>oss</sub>    |      | 8    |      | μJ    | V <sub>DS</sub> = 400 V<br>V <sub>GS</sub> = 0 V, f = 100 kHz                      |

| Switching Energy during turn-on     | Eon                 |      | 47.5 |      | μJ    |                                                                                    |

| Switching Energy during turn-off    | E <sub>off</sub>    |      | 8    |      | μJ    | Ω<br>R <sub>G(off)</sub> = 1 Ω, L = 40 µH<br>L <sub>P</sub> = 2 nH (Notes 7, 8)    |

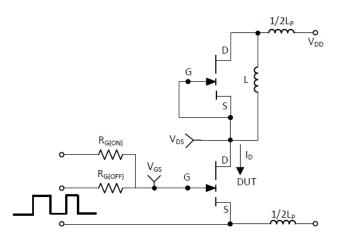

(6) See Figure 16 for timing test circuit diagram and Figure 17 for definition waveforms

(7)  $L_P$  = parasitic inductance

(8) See Figure 18 for switching test circuit

### **Test Circuits**

Figure 16: switching time test circuit

Figure 17: switching time waveforms

Figure 18: Switching Loss Test Circuit

### **Application Information**

### **Gate Drive**

The recommended gate drive voltage range,  $V_{GS}$ , is 0 V to + 6 V for optimal  $R_{DS(on)}$  performance. Also, the repetitive gate to source voltage, maximum rating,  $V_{GS(AC)}$ , is +7 V to -10 V. The gate can survive non-repetitive transients up to +10 V and – 20 V for pulses up to 1 µs. These specifications allow designers to easily use 6.0 V or 6.5 V gate drive settings. At 6 V gate drive voltage, the enhancement mode high electron mobility transistor (E-HEMT) is fully enhanced and reaches its optimal efficiency point. A 5 V gate drive can be used but may result in lower operating efficiency. Inherently, GaN Systems E-HEMT do not require negative gate bias to turn off. Negative gate bias, typically  $V_{GS} = -3$  V, ensures safe operation against the voltage spike on the gate, however it may increase reverse conduction losses if not driven properly. For more details, please refer to the gate driver application note "GN001 How to Drive GaN Enhancement Mode Power Switching Transistors" at <u>www.gansystems.com</u>

Similar to a silicon MOSFET, an external gate resistor can be used to control the switching speed and slew rate. Adjusting the resistor to achieve the desired slew rate may be needed. Lower turn-off gate resistance, R<sub>G(OFF)</sub> is recommended for better immunity to cross conduction. Please see the gate driver application note (GN001) for more details.

A standard MOSFET driver can be used as long as it supports 6 V for gate drive and the UVLO is suitable for 6 V operation. Gate drivers with low impedance and high peak current are recommended for fast switching speed. GaN Systems E-HEMTs have significantly lower Q<sub>G</sub> when compared to equally sized R<sub>DS(on)</sub> MOSFETs, so high speed can be reached with smaller and lower cost gate drivers.

Some non-isolated half bridge MOSFET drivers are not compatible with 6 V gate drive due to their high under-voltage lockout threshold. Also, a simple bootstrap method for high side gate drive may not be able to provide tight tolerance on the gate voltage. Therefore, special care should be taken when you select and use the half bridge drivers. Please see the gate driver application note (GN001) for more details.

#### **Parallel Operation**

Design wide tracks or polygons on the PCB to distribute the gate drive signals to multiple devices. Keep the drive loop length to each device as short and equal length as possible.

GaN enhancement mode HEMTs have a positive temperature coefficient on-state resistance which helps to balance the current. However, special care should be taken in the driver circuit and PCB layout since the device switches at very fast speed. It is recommended to have a symmetric PCB layout and equal gate drive loop length (star connection if possible) on all parallel devices to ensure balanced dynamic current sharing. Adding a small gate resistor (1-2  $\Omega$ ) on each gate is strongly recommended to minimize the gate parasitic oscillation.

#### **Source Sensing**

The package features a dedicated source sense pin. The GaNPX® packaging utilizes no wire bonds so the source connection is very low inductance. The dedicated source sense pin will further enhance performance by eliminating the common source inductance if a dedicated gate drive signal kelvin connection is created. This can be achieved connecting the gate drive signal from the driver to the gate pad and returning from the source sense pad to the driver ground reference.

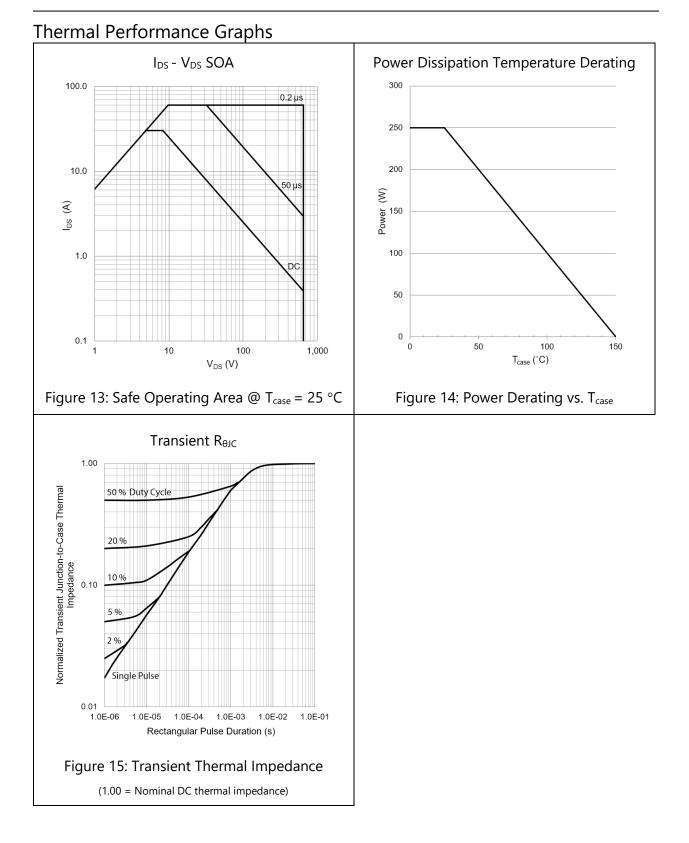

#### Thermal

The substrate is internally connected to the source/thermal pad on the bottom-side of the package. The transistor is designed to be cooled using the printed circuit board. The Drain pad is not as thermally conductive as the thermal pad. However, adding more copper under this pad will improve thermal performance by reducing the package temperature.

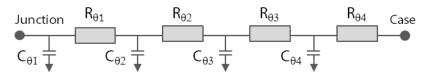

#### **Thermal Modeling**

RC thermal models are available to support detailed thermal simulation using SPICE. The thermal models are created using the Cauer model, an RC network model that reflects the real physical property and packaging structure of our devices. This approach allows our customers to extend the thermal model to their system by adding extra  $R_{\theta}$  and  $C_{\theta}$  to simulate the Thermal Interface Material (TIM) or Heatsink.

RC thermal model:

RC breakdown of  $R_{\Theta JC}$

| R <sub>θ</sub> (°C/W)   | C <sub>θ</sub> (W·s/°C)   |

|-------------------------|---------------------------|

| R <sub>01</sub> = 0.015 | C <sub>01</sub> = 8.0E-05 |

| R <sub>02</sub> = 0.23  | C <sub>02</sub> = 7.4E-04 |

| R <sub>03</sub> = 0.24  | С <sub>өз</sub> = 6.5Е-03 |

| R <sub>04</sub> = 0.015 | C <sub>04</sub> = 2.0E-03 |

For more detail, please refer to Application Note GN007 "Modeling Thermal Behavior of GaN Systems' GaNPX® Using RC Thermal SPICE Models" available at <u>www.gansystems.com</u>

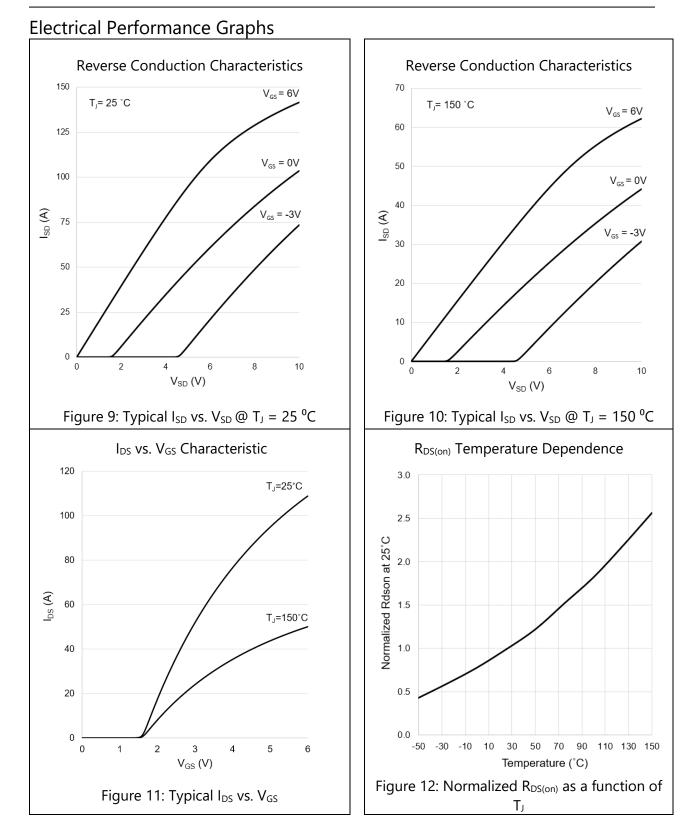

#### **Reverse Conduction**

GaN Systems enhancement mode HEMTs do not have an intrinsic body diode and there is zero reverse recovery charge. The devices are naturally capable of reverse conduction and exhibit different characteristics depending on the gate voltage. Anti-parallel diodes are not required for GaN Systems transistors as is the case for IGBTs to achieve reverse conduction performance.

On-state condition ( $V_{GS}$  = +6 V): The reverse conduction characteristics of a GaN Systems enhancement mode HEMT in the on-state is similar to that of a silicon MOSFET, with the I-V curve symmetrical about the origin and it exhibits a channel resistance,  $R_{DS(on)}$ , similar to forward conduction operation.

Off-state condition ( $V_{GS} \le 0$  V): The reverse characteristics in the off-state are different from silicon MOSFETs as the GaN device has no body diode. In the reverse direction, the device starts to conduct when the gate voltage, with respect to the drain,  $V_{GD}$ , exceeds the gate threshold voltage. At this point the device exhibits a channel resistance. This condition can be modeled as a "body diode" with slightly higher  $V_F$  and no reverse recovery charge.

If negative gate voltage is used in the off-state, the source-drain voltage must be higher than  $V_{GS(th)}+V_{GS(off)}$  in order to turn the device on. Therefore, a negative gate voltage will add to the reverse voltage drop " $V_F$ " and hence increase the reverse conduction loss.

#### **Blocking Voltage**

The blocking voltage rating,  $V_{(BL)DSS}$ , is defined by the drain leakage current. The hard (unrecoverable) breakdown voltage is approximately 30 % higher than the rated  $V_{(BL)DSS}$ . As a general practice, the maximum drain voltage should be de-rated in a similar manner as IGBTs or silicon MOSFETs. All GaN E-HEMTs do not avalanche and thus do not have an avalanche breakdown rating. The maximum drain-to-source rating is 650 V and does not change with negative gate voltage. GaN Systems tests devices in production with a 750V Drain-to-source voltage pulse to insure blocking voltage margin.

pulse to insure blocking voltage margin.

#### **Packaging and Soldering**

The package material is high temperature epoxy-based PCB material which is similar to FR4 but has a higher temperature rating, thus allowing the device to be specified to 150 °C. The device can handle at least 3 reflow cycles.

It is recommended to use the reflow profile in IPC/JEDEC J-STD-020 REV D.1 (March 2008)

The basic temperature profiles for Pb-free (Sn-Aq-Cu) assembly are:

- Preheat/Soak: 60 120 seconds.  $T_{min} = 150 \text{ °C}$ ,  $T_{max} = 200 \text{ °C}$ .

- Reflow: Ramp up rate 3 °C/sec, max. Peak temperature is 260 °C and time within 5 °C of peak temperature is 30 seconds.

- Cool down: Ramp down rate 6 °C/sec max.

Using "No-Clean" soldering paste and operating at high temperatures may cause a reactivation of the "No-Clean" flux residues. In extreme conditions, unwanted conduction paths may be created. Therefore, when the product operates at greater than 100  $^{\circ}$ C it is recommended to also clean the "No-Clean" paste residues.

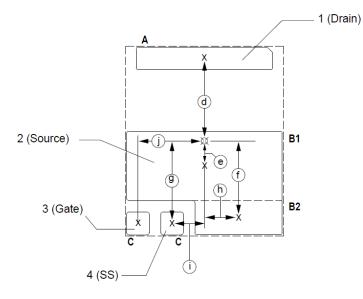

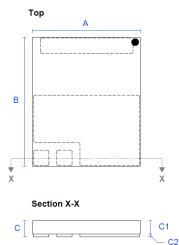

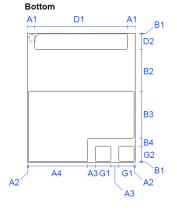

# Recommended PCB Footprint

| Pad sizes |           |            |           |            |  |  |  |

|-----------|-----------|------------|-----------|------------|--|--|--|

| mm Inches |           |            |           |            |  |  |  |

|           | X (width) | Y (height) | X (width) | Y (height) |  |  |  |

| Α         | 6.00      | 1.00       | 0.236     | 0.039      |  |  |  |

| <b>B1</b> | 6.85      | 3.05       | 0.270     | 0.120      |  |  |  |

| <b>B2</b> | 3.85      | 1.50       | 0.152     | 0.059      |  |  |  |

| С         | 1.00      | 1.00       | 0.039     | 0.039      |  |  |  |

#### Dimensions

|   | mm   | Inches |

|---|------|--------|

| d | 3.63 | 0.143  |

| е | 1.10 | 0.043  |

| f | 3.38 | 0.133  |

| g | 3.63 | 0.143  |

| h | 1.50 | 0.059  |

| i | 1.43 | 0.056  |

| j | 2.93 | 0.115  |

|   |      |        |

PCB pad openings

Package outline

Package Dimensions

Surface Finish: ENIG Ni: 4.5 um +/- 1.5 um Au: 0.09 um +/- 0.03 um

\*Inch measurements are approximate values

### Part Marking

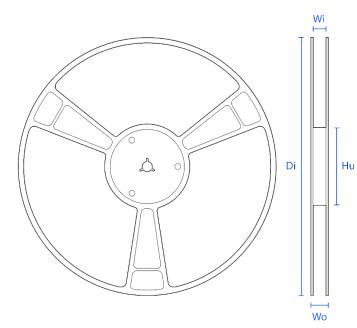

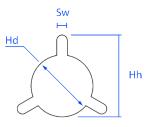

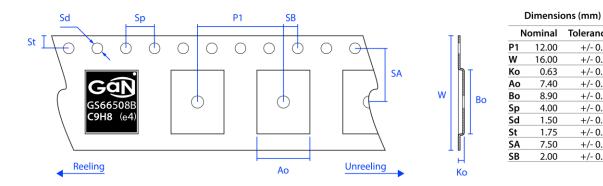

# Tape and Reel Information

|       | Dimensions (mm)          |       |    |       |       |  |  |  |

|-------|--------------------------|-------|----|-------|-------|--|--|--|

| 13 ir | 13 inch reel 7 inch reel |       |    |       |       |  |  |  |

|       | Min                      | Max   |    | Min   | Max   |  |  |  |

| Di    | 328.0                    | 332.0 | Di | 178.0 | 181.5 |  |  |  |

| Wo    |                          | 22.4  | Wo |       | 22.4  |  |  |  |

| Wi    | 16.4                     | 18.4  | Wi | 16.3  | 18.4  |  |  |  |

| Hu    | 98.5                     | 104.0 | Hu | 60.0  | 62.0  |  |  |  |

| Hh    | 16.4                     | 17.4  | Hh | 16.2  | 17.8  |  |  |  |

| Sw    | 1.5                      | 2.5   | Sw | 1.5   | 2.5   |  |  |  |

| Hd    | 12.8                     | 13.5  | Hd | 12.8  | 13.4  |  |  |  |

Note: Wo and Wi measured at hub

Tolerance

+/- 0.1

+/- 0.2

+/- 0.1

+/- 0.1

+/- 0.1

+/- 0.1

+/- 0.1

+/- 0.1

+/- 0.1

+/- 0.1

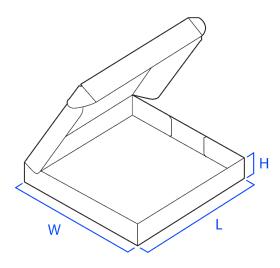

### Tape and Reel Box Dimensions

#### **Outside dimensions (mm)**

| 13 i | inch reel 7 i |       |   | nch reel 7 inch reel |       |  |  |

|------|---------------|-------|---|----------------------|-------|--|--|

|      | Min           | Max   |   | Min                  | Max   |  |  |

| W    | 197.0         | 203.5 | W | 337.0                | 342.0 |  |  |

| L    | 204.0         | 218.5 | L |                      | 355.0 |  |  |

| Н    |               | 32.0  | Н | 50.0                 | 53.0  |  |  |

#### www.gansystems.com

Important Notice – Unless expressly approved in writing by an authorized representative of GaN Systems, GaN Systems components are not designed, authorized or warranted for use in lifesaving, life sustaining, military, aircraft, or space applications, nor in products or systems where failure or malfunction may result in personal injury, death, or property or environmental damage. The information given in this document shall not in any event be regarded as a guarantee of performance. GaN Systems hereby disclaims any or all warranties and liabilities of any kind, including but not limited to warranties of non-infringement of intellectual property rights. All other brand and product names are trademarks or registered trademarks of their respective owners. Information provided herein is intended as a guide only and is subject to change without notice. The information contained herein or any use of such information does not grant, explicitly, or implicitly, to any party any patent rights, licenses, or any other intellectual property rights. GaN Systems standard terms and conditions apply. All rights reserved.

© 2009-2020 GaN Systems Inc.