#### **Features**

- Maximum 3A Low-Dropout Voltage Regulator

- Ultra Low Dropout Voltage

Typically 220mV at 3A Output Current

- High Output Accuracy over Line, Load and Temperature

- Build-In Soft-Start

- Excellent startup under load from 0 to 3A

- Power-On-Reset Monitoring on Both V<sub>DD</sub> and V<sub>IN</sub> Pins

- Power-OK Output function

- Foldback over Current Protection and Thermal shutdown

- 0.1µA (typ) Shutdown Supply Current

- Low ESR Output Capacitor(Multi-layer Chip Capacitors (MLCC)) Applicable

- Vout Pull Low Resistance when Disable

- PSOP-8. TDFN10-3x3

- Green Product (RoHS, Lead-Free, Halogen-Free Compliant)

## **Applications**

- Notebook PC Applications

- Motherboard Applications

- Low Voltage Logic Supplies

- Microprocessor and Chipset Supplies

- Graphic Cards

- Cordless phones

## **General Description**

The GS7103 can deliver up to 3A of continuous output current with a typical dropout voltage of only 260mV using internal n-channel MOSFETs. The linear regulator uses a separate VDD supply to power the control circuitry and drive the Internal n-channel MOSFETs. The output voltage is adjustable from 0.8V to the voltage that is very close to  $V_{\text{IN}}$ .

The GS7103 allows the use of low-ESR ceramic capacitor as low as 10uF. Moreover the IC provide good performance on both line transient response and load transient response.

The GS7103 provides foldback over current limit and thermal shutdown to prevent the linear regulator from damage. Built-in soft-start minimizes stress on the input power source by reducing capacitive inrush current on start-up. During start-up, POK remain low until the output reaches 92% of its rating value.

The GS7103 is available in PSOP-8 package or TDFN10-3x3 package.

This document is GStek's confidential information. Anyone having confidential obligation to GStek shall keep this document confidential. Any unauthorized disclosure or use beyond authorized purpose will be considered as violation of confidentiality and criminal and civil liability will be asserted.

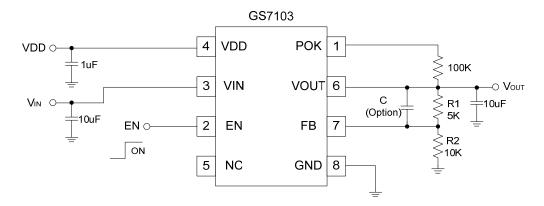

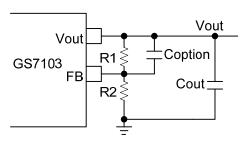

# **Typical Application**

Figure 1 Typical Application of GS7103

## **Function Block Diagram** VIN 6 VOUT 3 **VDD POR** 4 **OCP** 7 FB Error Amplifie Soft OTP **POK** Start ΕN 2 **GND** 8 Delay 400K 92%\*VREF

Figure 2 Function Block Diagram

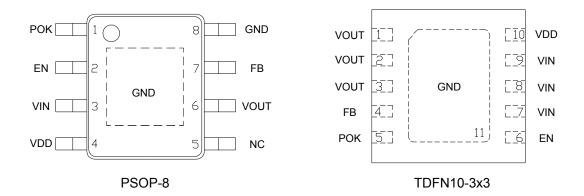

# **Pin Configuration**

**Pin Descriptions**

| Pin N  | lo.        | Name | I/O type | Pin Function                                                                                                                                                       |

|--------|------------|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PSOP-8 | TDFN10-3x3 | Name | i/O type | Pili Fullction                                                                                                                                                     |

| 1      | 5          | POK  | 9        | Open drain output. Setting high impedance once V <sub>OUT</sub> reaches 92% of its rating voltage                                                                  |

| 2      | 6          | EN   |          | Chip Enable (active high). The device will be shutdown if this pin is left open.                                                                                   |

| 3      | 7,8,9      | VIN  |          | Input Voltage. Large bulk capacitance should be placed closely to this pin. A 10µF ceramic capacitor is recommended at this pin.                                   |

| 4      | 10         | VDD  | I        | Supply voltage for control circuit. A 3V to 5V supply voltage for control circuit is recommended and supply voltage should be 1.5V higher than the output voltage. |

| 5      |            | NC   |          | Not connected                                                                                                                                                      |

| 6      | 1,2,3      | VOUT | 0        | Output Voltage. The power output of the device.                                                                                                                    |

| 7      | 4          | FB   | I        | Feedback Voltage. This pin is connected to the center tap of an external resistor divider network to set the output voltage as V <sub>OUT</sub> = 0.8(R1+R2)/R2.   |

| 8      | 11         | GND  |          | Ground.                                                                                                                                                            |

Rev.:1.6 3 JUN-16

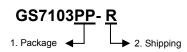

# **Ordering Information**

| No | Item     | Contents                         |

|----|----------|----------------------------------|

| 1  | Package  | SO: PSOP-8(B)                    |

| 2  | Shipping | TD: TDFN10-3x3<br>R: Tape & Reel |

Example: GS7103 PSOP-8(B) Tape & Reel ordering information is "GS7103SO-R"

**Absolute Maximum Rating (Note 1)**

| Parameter                                           | Symbol                    | Limits                     | Units |

|-----------------------------------------------------|---------------------------|----------------------------|-------|

|                                                     |                           |                            |       |

| Supply Voltage                                      | V <sub>IN</sub>           | -0.3 < V <sub>IN</sub> < 6 | V     |

| Control Voltage                                     | VDD                       | -0.3 < V <sub>DD</sub> < 6 | V     |

| Output Voltage                                      | Vout                      | -0.3 < V <sub>OUT</sub> <5 | V     |

| Package Power Dissipation at $T_A \leq 25^{\circ}C$ | PD_PSOP-8                 | 1333                       | mW    |

| Package Power Dissipation at $T_A \le 25^{\circ}C$  | P <sub>D_TDFN10-3x3</sub> | 1670                       | mW    |

| Junction Temperature                                | TJ                        | - 45 ~ 150                 | °C    |

| Storage Temperature                                 | 7 T <sub>STG</sub>        | - 65 ~ 150                 | °C    |

| Lead Temperature (Soldering) 10S                    | $T_{LEAD}$                | 260                        | °C    |

| ESD (Human Body Mode) (Note 2)                      | V <sub>ESD_HBM</sub>      | 2K                         | V     |

| ESD (Machine Mode) (Note 2)                         | $V_{ESD\_MM}$             | 200                        | V     |

# **Thermal Information (Note 3)**

| Parameter                              | Symbol                           | Limits | Units |

|----------------------------------------|----------------------------------|--------|-------|

| Thermal Resistance Junction to Ambient | $\theta_{\text{JA\_PSOP-8}}$     | 75     | °C/W  |

| Thermal Resistance Junction to Case    | $\theta_{\text{JC\_PSOP-8}}$     | 12     | °C/W  |

| Thermal Resistance Junction to Ambient | $\theta_{\text{JA\_TDFN10-3x3}}$ | 60     | °C/W  |

| Thermal Resistance Junction to Case    | $\theta_{\text{JC\_TDFN10-3x3}}$ | 5      | °C/W  |

**Recommend Operating Condition (Note 4)**

| Parameter            | Symbol   | Limits                              | Units |

|----------------------|----------|-------------------------------------|-------|

| Supply Voltage       | $V_{IN}$ | $1.0 < V_{IN} < Min\{5.2, V_{DD}\}$ | V     |

| Control Voltage      | $V_{DD}$ | $3.0 < V_{DD} < 5.5$                | V     |

| Junction Temperature | $T_J$    | - 40 ~ 125                          | °C    |

| Ambient Temperature  | $T_A$    | - 40 ~ 85                           | °C    |

## **Electrical Characteristics**

$(V_{IN}=V_{OUT}+0.5V, V_{EN}=V_{DD}=5V, C_{IN}=C_{OUT}=10uF, T_A=T_J=25^{\circ}C)$

| Parameter                                  | Symbol                             | Conditions                                                                                                        | Min.  | Тур. | Max.                          | Units |

|--------------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------|------|-------------------------------|-------|

| Supply Voltage Section                     |                                    |                                                                                                                   |       |      |                               |       |

| V <sub>DD</sub> Operation Voltage<br>Range | $V_{DD}$                           | V <sub>DD</sub> Input Range, V <sub>OUT</sub> =V <sub>REF</sub>                                                   | 3.0   |      | 5.5                           | V     |

| V <sub>IN</sub> Operation Voltage<br>Range | V <sub>IN</sub>                    | V <sub>IN</sub> Input Range, V <sub>OUT</sub> V <sub>REF</sub>                                                    | 1.0   |      | Min{5.2<br>,V <sub>DD</sub> } | V     |

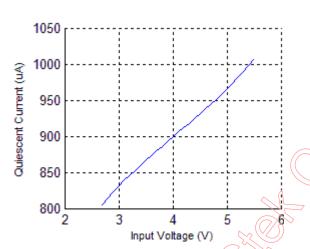

| Quiescent current                          | IQ                                 | V <sub>DD</sub> =V <sub>IN</sub> =V <sub>EN</sub> =5V,I <sub>OUT</sub> =0A,<br>V <sub>OUT</sub> =V <sub>REF</sub> |       | 1.0  | 1.5                           | mA    |

| VDD Input current                          | I <sub>VDD</sub>                   | V <sub>DD</sub> =V <sub>IN</sub> =V <sub>EN</sub> =5V, O <sub>UT</sub> =0A, V <sub>OUT</sub> =V <sub>REF</sub>    |       | 1.0  | 1.5                           | mA    |

| Control Input Current in Shutdown          | I <sub>VDD_SD</sub>                | V <sub>DD</sub> =V <sub>IN</sub> =5.0V, I <sub>OUT</sub> =0A,<br>V <sub>EN</sub> =0V                              |       | 0.1  | 2                             | uA    |

| V <sub>DD</sub> POR Threshold              | $V_{DDRTH}$                        |                                                                                                                   | 2.4   | 2.7  | 3                             | V     |

| V <sub>DD</sub> POR Hysteresis             | /                                  |                                                                                                                   | 0.15  | 0.2  |                               | V     |

| V <sub>IN</sub> POR Threshold              | V <sub>INRTH</sub>                 |                                                                                                                   | 0.55  | 0.75 | 0.95                          | V     |

| V <sub>IN</sub> POR Hysteresis             |                                    |                                                                                                                   | 0.13  | 0.20 |                               | V     |

| Output Voltage                             | _                                  |                                                                                                                   | -     |      |                               |       |

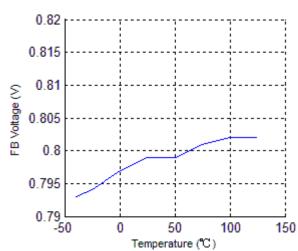

| Reference Voltage                          | $V_{REF}$                          | I <sub>OUT</sub> =1mA, V <sub>OUT</sub> =V <sub>REF</sub>                                                         | 0.784 | 8.0  | 0.816                         | V     |

| Output Voltage<br>Accuracy                 |                                    |                                                                                                                   | -2.0  |      | +2.0                          | %     |

| Line Regulation (V <sub>DD</sub> )         | $\triangle \ V_{\text{LINE\_VDD}}$ | V <sub>DD</sub> =4V to 5V, I <sub>OUT</sub> =1mA,<br>V <sub>OUT</sub> =V <sub>REF</sub> , V <sub>IN</sub> =2V     |       | 0.03 | 0.2                           | %     |

| Line Regulation (V <sub>IN</sub> )         | △ V <sub>LINE_IN</sub>             | $V_{IN}$ =1.2V to 5V, $I_{OUT}$ =1mA, $V_{OUT}$ = $V_{REF}$                                                       |       | 0.01 | 0.1                           | %     |

| Load Regulation (Note 5)                   | $\triangle V_{\text{LOAD}}$        | I <sub>OUT</sub> =1mA to 3 A, V <sub>OUT</sub> =V <sub>REF</sub>                                                  |       | 0.1  | 1.5                           | %     |

| V <sub>OUT</sub> Pull Low<br>Resistance    |                                    | V <sub>DD</sub> =V <sub>IN</sub> =5.0V, V <sub>EN</sub> =0V                                                       |       | 130  |                               | Ω     |

Rev.:1.6 5 JUN-16

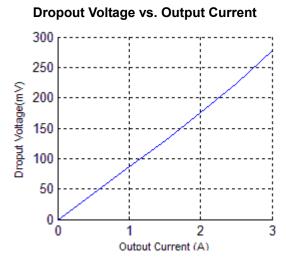

| Dropout Voltage                          |                       |                          |                                                            |     |     |     |    |

|------------------------------------------|-----------------------|--------------------------|------------------------------------------------------------|-----|-----|-----|----|

| Dropout Voltage                          |                       | V                        | V <sub>OUT</sub> =V <sub>REF</sub> , I <sub>OUT</sub> =2A  |     | 160 | 200 | mV |

| (Note 6)                                 |                       | $V_{DROP}$               | V <sub>OUT</sub> = V <sub>REF</sub> , I <sub>OUT</sub> =3A |     | 220 | 290 | mV |

| Protection                               |                       |                          |                                                            |     |     |     |    |

| Current Lim                              | it                    | ILIM                     | $V_{DD}=V_{IN}=V_{EN}=5V$ , $V_{OUT}=V_{REF}$              |     | 4   |     | Α  |

| Short Circui                             | t Current             | I <sub>FOLDBACK</sub>    | V <sub>OUT</sub> <0.2V                                     |     | 100 |     | mA |

| Thermal Sh<br>Temperature                |                       | T <sub>SD</sub>          | T <sub>J</sub> Rising                                      |     | 150 |     | °C |

| Thermal Shutdown<br>Returned Temperature |                       |                          |                                                            |     | 100 |     | °C |

| Enable                                   |                       | -                        | <b>◇</b> .                                                 | ON  |     |     |    |

| EN                                       | Logic-Low<br>Voltage  |                          | V <sub>DD</sub> =5V                                        |     |     | 0.7 | V  |

| Threshold                                | Logic-High<br>Voltage |                          | V <sub>DD</sub> =5V                                        | 1.4 |     |     | V  |

| EN Input Bia                             | as Current            | I <sub>EN</sub>          | V <sub>EN</sub> =5V                                        |     | 12  | 20  | uA |

| Power OK                                 |                       |                          |                                                            |     |     |     |    |

| POK Rising Threshold                     |                       | V <sub>REF</sub> Rising  |                                                            | 92  |     | %   |    |

| POK Hysteresis                           |                       | V <sub>REF</sub> falling |                                                            | 8   |     | %   |    |

| POK Sink Capability                      |                       | I <sub>PGOOD</sub> =1mA  |                                                            | 0.2 | 0.4 | V   |    |

| POK Delay                                |                       |                          | -40°C ~125°C                                               |     | 1.3 |     | mS |

- **Note 1.** Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

- **Note 2.** Devices are ESD sensitive. Handling precaution recommended.

- Note 3.  $\theta_{JA}$  is measured in the natural convection at  $T_A$ =25°C on a high effective thermal conductivity test board (4 Layers, 2S2P) of JEDEC 51-7 thermal measurement standard. The case point of  $\theta_{JC}$  is on the expose pad for PSOP-8 package.

- **Note 4.** The device is not guaranteed to function outside its operating conditions.

- **Note 5.** Regulation is measured at constant junction temperature by using a 2ms current pulse. Devices are tested for load regulation in the load range from 1mA to 3A.

- **Note 6.** The Dropout voltage is defined as  $V_{\text{IN}}$ - $V_{\text{OUT}}$ , which is measured when  $V_{\text{OUT}}$  is  $0.98*V_{\text{OUT}(\text{NORMAL})}$ . The Dropout voltage is measured at constant junction temperature by using a 2ms current pulse.

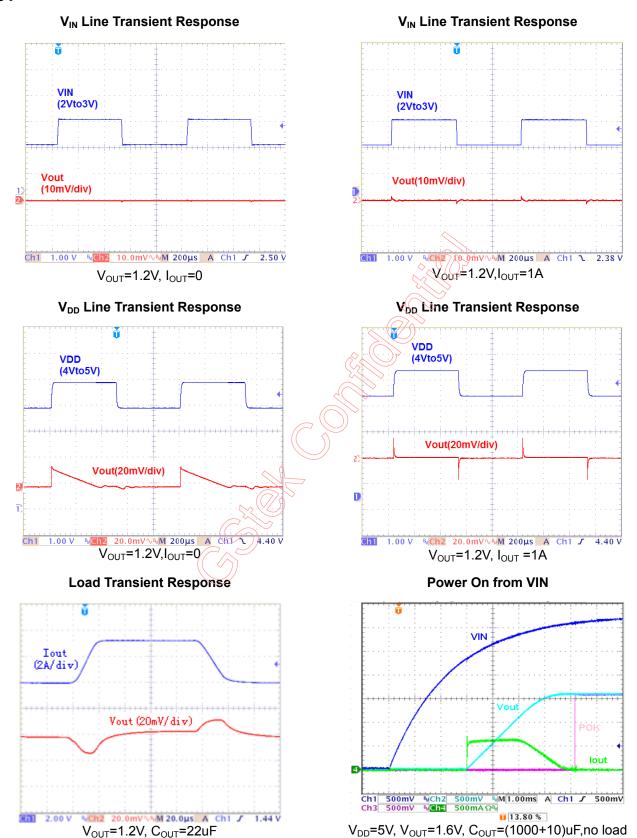

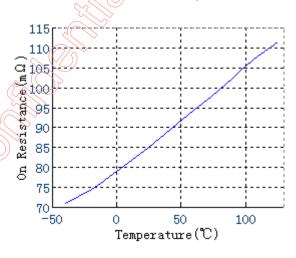

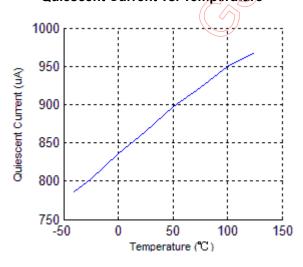

## **Typical Characteristics**

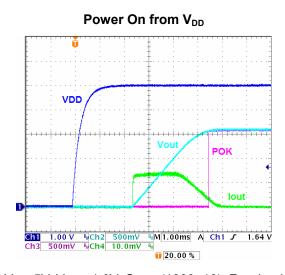

$V_{\text{DD}}\text{=}5\text{V},\,V_{\text{OUT}}\text{=}1.6\text{V},\,C_{\text{OUT}}\text{=}(1000\text{+}10)\text{uF,no load}$

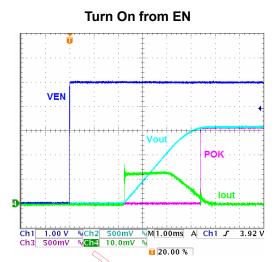

$V_{EN}$ =5V,  $V_{OUT}$ =1.6V,  $C_{OUT}$ =(1000+10)uF,no load

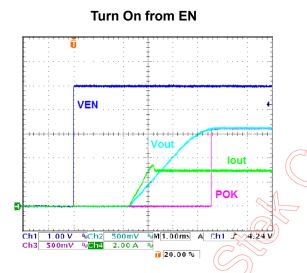

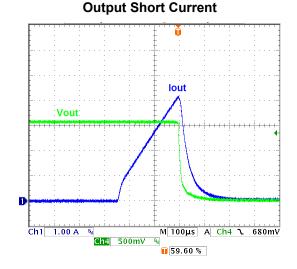

V<sub>EN</sub>=5V, V<sub>OUT</sub>=1.6V, C<sub>OUT</sub>=10uF, load =3A

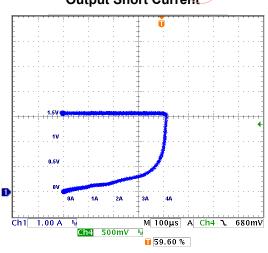

Output Short Current

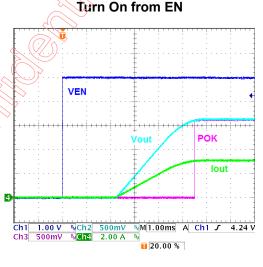

$V_{EN}$ =5V,  $V_{OUT}$ =1.6V,  $C_{OUT}$ =10uF,  $R_{load}$  =0.5

# Shutdown Current vs. Input Voltage 1 0.8 0.6 0.4 0.2 3 4 5 6

On Resistance vs. Temperature

Input Voltage (V)

### **Quiescent Current vs. Temperature**

FB Voltage vs. Temperature

Rev.:1.6 9 JUN-16

## **Application Information**

#### **Enable**

The GS7103 has a dedicated enable pin(EN). When the EN pin is in the logic low ( $V_{EN}$ <0.6V), the regulator will be turned off, reducing the supply current to less than 1uA.

When the EN pin is in the logic high ( $V_{EN}>1.4V$ ), the regulator will be turned on and undergoes a new soft-start cycle. Left open, the EN pin is pulled down by a internal resistor to shut down the regulator.

#### Power-on-Reset

The GS7103 features a power-on-reset control through monitor both input voltages to prevent wrong operations. Only after the two supply voltages exceed their rising POR threshold voltages, the regulator is to be initiated and starts up.

#### POK

The POK pin is an open-drain output, and can be connects to  $V_{\text{OUT}}$  or other rail through an external pull-up resistor. As the output voltage arrives 92% of normal output voltage, an internal delay function starts to perform a delay time and then output the POK pin high to indicate the output is OK. As the output voltage falls below the falling Power-OK threshold or one of the two supply voltages falls below it's falling POR threshold, the POK pin will output low immediately without a delay time.

#### **Build-In Soft-Start**

An internal soft-start function controls rise rate of the output voltage to limit the current surge at start-up. The typical soft-start interval is about 3mS.

#### **Current Limit**

The GS7103 contains a foldback over current protection function. It allows the output current to reach the maximum value of 4A. Then further decreases in the load resistance reduce both the load current and the load voltage. The main advantage of foldback limiting is less power dissipation in the pass transistor under shorted-load conditions. During startup, the current limit value is set to a high value, thus GS7103 can operate in full load condition. After startup, the current limit value is set to a normal value, so the pass transistor can be protected well.

#### Thermal-Shutdown Protection

Thermal Shutdown protects GS7103 from excessive power dissipation. If the die temperature exceeds 150°C, the pass transistor is shut off. 50°C of hysteresis prevents the regulator from turning on until the die temperature drops to 100°C.

#### **Output Capacitor selection**

The GS7103 is designed to employ ceramic output capacitors as low as 10uF; if employ EL output capacitor as large as 1000uF, feedback resistance(Rbottom) should be larger than 100K ohm(Table 2). Place the capacitors physically as close as possible to the device with wide and direct PCB traces. Capacitor ESR should be less than 50mohm.

|         | Cout   | Rbottom |

|---------|--------|---------|

| Ceramic | ≥10uF  | ≥0.1KΩ  |

| EL      | 1000uF | ≥100KΩ  |

Table 1 Cout capacitor vs. Rbottom resistance

#### **Feedback Network**

Figure 3 shows the feedback network. The suggested design procedure is to choose R2=10K $\Omega$  and then calculate R1 using the following formula: R1=( $V_{OUT}$  /  $V_{REF}$  -1)\*R2.

Figure 3 Feedback Network

C<sub>OPTION</sub> can improve transient response, and recommend value as follow:

| V <sub>OUT</sub> | R1            | $C_{OPTION}$ |  |

|------------------|---------------|--------------|--|

| 0.8V ~ 1.6V      | 0 ~ 10 KΩ     | 470pF~1nF    |  |

| 1.6V ~ 2.4V      | 10 ΚΩ ~ 20 ΚΩ | 100pF~500pF  |  |

| 2.4V ~ 3.6V      | 20 ΚΩ ~ 30 ΚΩ | 20pF~300pF   |  |

Table 2 R1 vs. C<sub>OPTION</sub>

#### **Input Capacitor selection**

Bypass VIN to ground with a 10uF or greater capacitor. Bypass VDD to ground with a 1uF capacitor for normal operation in most applications. Ceramic, tantalum or aluminum electrolytic capacitors may be selected for input capacitor. However ceramic capacitors are recommended due to their significant cost and space savings. Place the capacitors physically as close as possible to the device with wide and direct PCB traces.

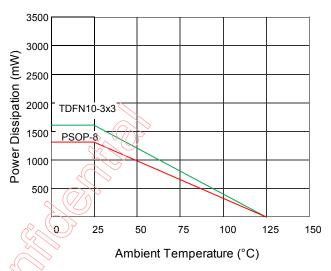

### **Power Dissipation and Layout Considerations**

Although internal thermal limiting function is integrated in GS7103, continuously keeping the junction near the thermal shutdown temperature may possibly affect device reliability. For continuous operation, it is highly recommended to

keep the junction temperature below the maximum operation junction temperature 125°C for maximum reliability.

The power dissipation definition in device is:

$$P_D = (V_{IN} - V_{OUT}) \times I_{OUT} + V_{DD} \times I_{Q}$$

The maximum power dissipation can be calculated as:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

Where  $T_{J(MAX)}$  is the maximum operation junction temperature 125°C,  $T_A$  is the ambient temperature and the  $\theta_{JA}$  is the junction to ambient thermal resistance.

The thermal resistance  $\theta_{JA}$  for PSOP-8 package is 75°C/W on the standard JEDEC 51-7 (4 layers, 2S2P) thermal test board. The copper thickness is 2oz. The maximum power dissipation at  $T_A$  = 25°C can be calculated by following formula:

$$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (75^{\circ}C/W) = 1.33W$$

(SOP-8 Exposed Pad on the minimum layout)

The thermal resistance  $\theta_{JA}$  for TDFN10-3x3 package is 60°C/W on the standard JEDEC 51-7 (4 layers, 2S2P) thermal test board. The maximum power dissipation at  $T_A = 25$ °C can be calculated by following formula:

$$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (60^{\circ}C/W) = 1.67W$$

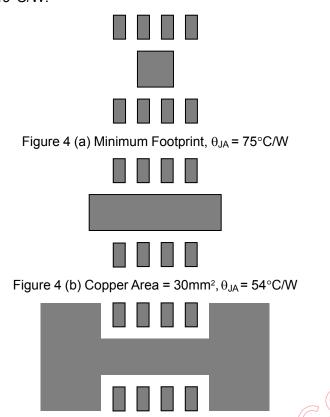

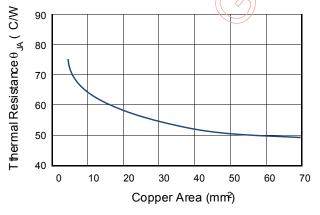

The thermal resistance  $\theta_{JA}$  of PSOP-8 is determined by the package design and the PCB design. Copper plane under the exposed pad is an effective heat sink and is useful for improving thermal conductivity. As shown in Figure 3, the amount of copper area to which the PSOP-8 is mounted affects thermal performance. When mounted to the standard PSOP-8 pad (Figure 4.a),  $\theta_{JA}$  is 75°C/W. Adding copper area of pad under the PSOP-8 Figure 4.b) reduces the  $\theta_{JA}$  to 54°C/W. Even further, increasing the copper area

of pad to 70mm2 (Figure 4.c) reduces the  $\theta_{JA}$  to 49°C/W.

Figure 4 (c) Copper Area =  $70 \text{mm}^2$ ,  $\theta_{JA} = 49 ^{\circ} \text{C/W}^1$

Figure 4  $\theta_{JA}$  vs. Different Cooper Area Layout Design And Figure 4 shows a curve for the  $\theta_{JA}$  of the PSOP-8 package for different copper area sizes using a typical PCB with 2oz copper in still air.

Figure 5  $\theta_{JA}$  vs. Copper Area

The maximum power dissipation depends on operating ambient temperature or fixed  $T_{J(MAX)}$  and thermal resistance  $\theta_{JA}$ . For GS7103 packages, the Figure 5 of derating curves allows the designer to see the effect of rising ambient temperature on the maximum power allowed.

Figure 6 Derating Curve for Packages

Rev.:1.6 12 JUN-16

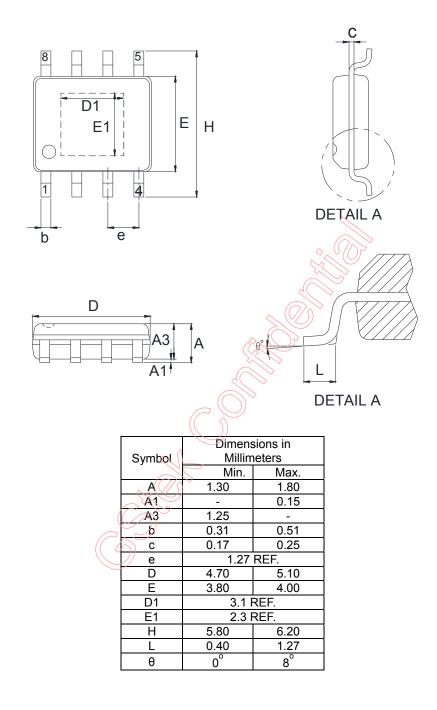

# Package Dimensions, PSOP-8(B)

#### Note:

Min.: Minimum dimension specified.

Max.: Maximum dimension specified.

3. REF.: Reference. Normal/Regular dimension specified for reference.

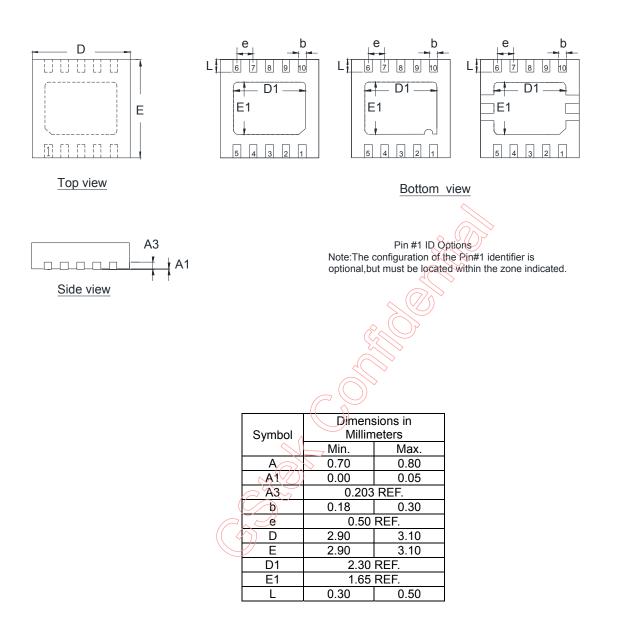

## Package Dimensions, TDFN10-3x3

#### Note:

- 1. Min.: Minimum dimension specified.

- 2. Max.: Maximum dimension specified.

- 3. REF.: Reference. Normal/Regular dimension specified for reference.

Green Solution Technology Co.,LTD.

Please read the notice stated in this preamble carefully before Admission e accessing any contents of the document attached. Admission of GStek's statement therein is presumed once the document is released to the receiver.

Notice:

Firstly, GREEN SOLUTION CO., LTD. (GStek) reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its information herein without notice.. And the aforesaid information does not form any part or parts of any quotation or contract between GStek and the information receiver.

Further, no responsibility is assumed for the usage of the aforesaid information. GStek makes no representation that the interconnect of its circuits as described herein will not infringe on exiting or future patent rights and other intellectual property rights, nor do the descriptions contained herein express or imply that any licenses under any GStek patent right, copyright, mask work right, or other GStek intellectual property right relating to any combination, machine, or process in which GStek products or services are used.

Besides, the product in this document is not designed for use in life support appliances, devices, or systems where malfunction of this product can reasonably be expected to result in personal injury. GStek customers' using or selling this product for use in such applications shall do so at their own risk and agree to fully indemnify GStek for any damage resulting from such improper use or sale.

At last, the information furnished in this document is the property of GStek and shall be treated as highly confidentiality; any kind of distribution, disclosure, copying, transformation or use of whole or parts of this document without duly authorization from GStek by prior written consent is strictly prohibited. The receiver shall fully compensate GStek without any reservation for any losses thereof due to its violation of GStek's confidential request. The receiver is deemed to agree on GStek's confidential request therein suppose that said receiver receives this document without making any expressly opposition. In the condition that aforesaid opposition is made, the receiver shall return this document to GStek immediately without any delay.